UNITV Interrupt structure of 8086 Vector interrupt table

UNIT-V Interrupt structure of 8086. Vector interrupt table. Interrupt service routines. Introduction to DOS and BIOS interrupts. 8259 PIC Architecture and interfacing. cascading of interrupt controller.

An interrupt is an external or internal signal that breaks the normal sequence of execution of instructions, diverts its execution to some other program called “Interrupt Service Routine (ISR). At the end of each instruction cycle the 8086 checks to see if any interrupts have been requested. After executing ISR, the control is transferred back again to the main program which was being executed at the time of interruption. Nested interrupts. In 8086, there are two interrupts pins: 1. NMI 2. INTR NMI : -- Non Maskable Interrupt input pin which means that any interrupt request at NMI input cannot to masked or disabled by any means. INTR: -- It can be masked using the Interrupt Flag (IF).

If more than one type of INTR interrupt occurs at a time, then an external chip called programmable interrupt controller is required to handle them. (eg: 8259 interrupt controller). There are two types of interrupts 1. External interrupts These interrupts are generated by external devices i. e out side the processor (uing NMI, INTR pins). Eg: Keyboard interrupt. 1. Internal interrupts It is generated internally by the process circuit or by the execution of an interrupt instruction. Eg: INT instruction, overflow interrupt, divide by zero. At the end of each instruction cycle, the 8086 checks to see if any interrupts

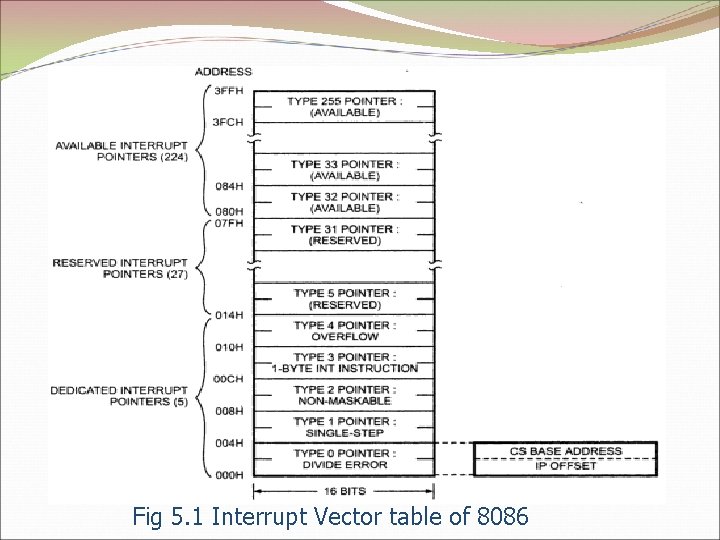

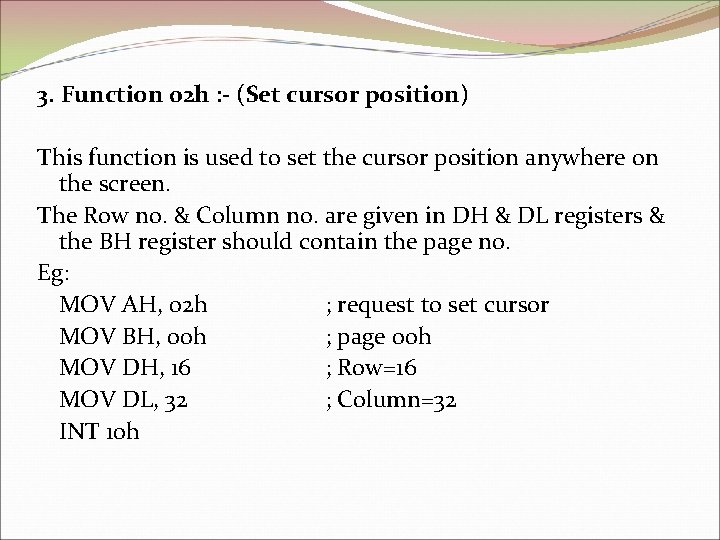

8086 Interrupt Vector Table The first 1 Kbyte of memory of 8086 (00000 to 003 FF) is set aside as a table for storing the starting addresses of Interrupt Service Procedures (ISP). Since 4 -bytes are required for storing starting addresses of ISPs, the table can hold 256 Interrupt procedures. The starting address of an ISP is often called the Interrupt Vector or Interrupt Pointer. Therefore the table is referred as Interrupt Vector Table. In this table, IP value is put in as low word of the vector & CS is put in high vector.

Fig 5. 1 Interrupt Vector table of 8086

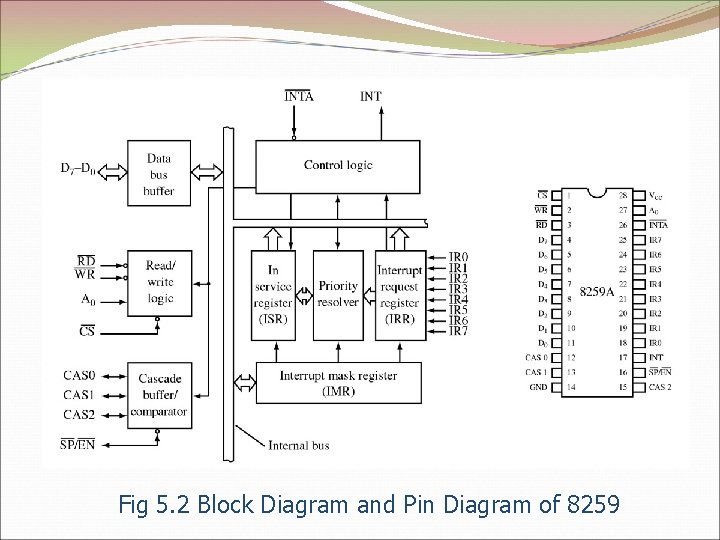

Fig 5. 2 Block Diagram and Pin Diagram of 8259

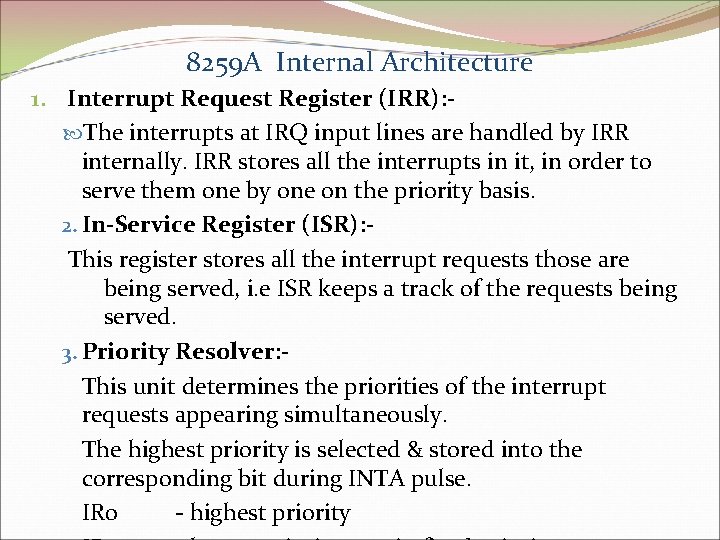

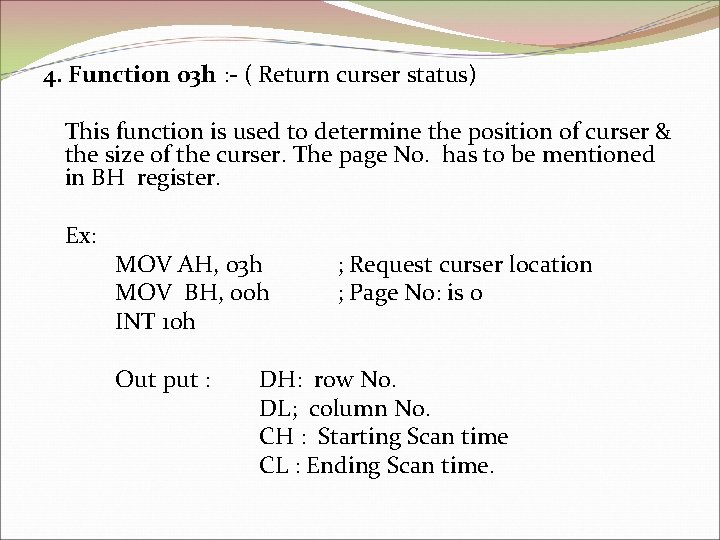

8259 A Internal Architecture 1. Interrupt Request Register (IRR): The interrupts at IRQ input lines are handled by IRR internally. IRR stores all the interrupts in it, in order to serve them one by one on the priority basis. 2. In-Service Register (ISR): This register stores all the interrupt requests those are being served, i. e ISR keeps a track of the requests being served. 3. Priority Resolver: This unit determines the priorities of the interrupt requests appearing simultaneously. The highest priority is selected & stored into the corresponding bit during INTA pulse. IR 0 - highest priority

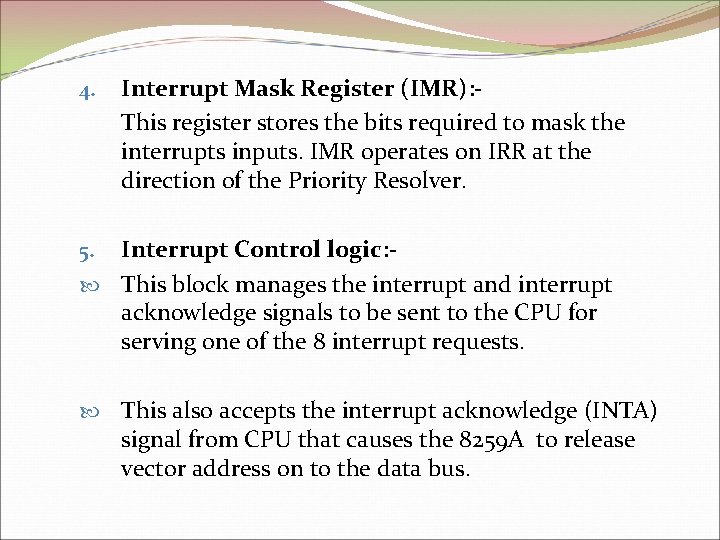

4. Interrupt Mask Register (IMR): This register stores the bits required to mask the interrupts inputs. IMR operates on IRR at the direction of the Priority Resolver. Interrupt Control logic: This block manages the interrupt and interrupt acknowledge signals to be sent to the CPU for serving one of the 8 interrupt requests. 5. This also accepts the interrupt acknowledge (INTA) signal from CPU that causes the 8259 A to release vector address on to the data bus.

6. Data Bus Buffer: - This Tri-state bidirectional buffer interfaces internal 8259 A bus the microprocessor data bus. Control words, status & vector information pass through data buffer during read or write operations. 7. Read/Write Control logic: - This circuit accepts and decodes commands from the CPU. This block also allows the status of the 8259 A to be transferred on to the data bus.

8. Cascade Buffer/Comparator: - This block stores & compares the IDs of all the 8259 As used in the system. The 3 I/O pins CAS 0 – CAS 2 are outputs when the 8259 A is used as a master. The same pins used as inputs when it is in the slave mode. 8259 A in master mode, sends the ID of the interrupting slave device on these lines. In slave, will send its pre-programmed vector address on the data bus during the next INTA pulse.

Interrupt Sequence in an 8086 system 1. One or more IR lines are raised high that set corresponding IRR bits. 2. 8259 A resolves priority and sends an INT signal to CPU. 3. The CPU acknowledges with INTA pulse. 4. Upon receiving an INTA signal from the CPU, the highest priority ISR bit is set and the corresponding IRR bit is reset. The 8259 A does not drive data bus during this period.

5. The 8086 will initiate a second INTA pulse. During this period 8259 A releases an 8 -bit pointer on to data bus from where it is read by the CPU. 6. This completes the interrupt cycle. The ISR bit is reset at the end of the second INTA pulse if automatic end of interrupt (AEOI) mode is programmed. Otherwise ISR bit remains set until an appropriate EOI command is issued at the end of interrupt subroutine.

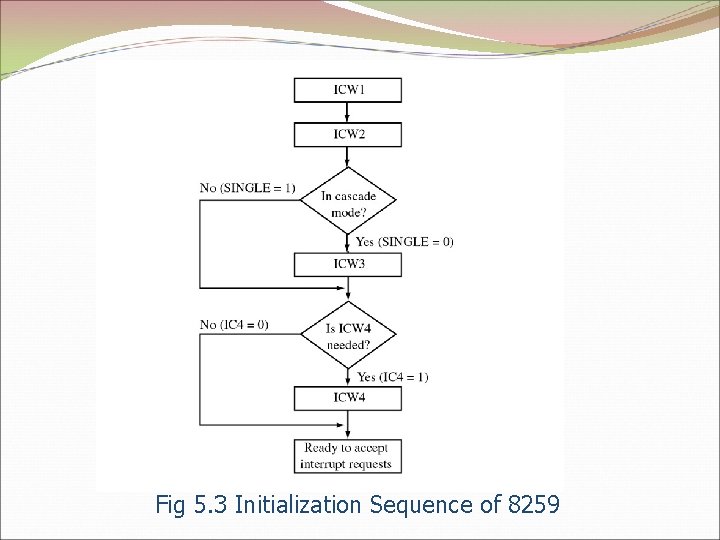

Command Words of 8259 A The command words of 8259 A are classified in two groups 1. Initialization Command Words (ICWs) 2. Operation Command Words (OCWs) Initialization Command Words (ICWs): Before starts functioning, the 8259 A must be initialized by writing two to four command words into the respective command word registers. These are called as Initialization Command Words (ICWs). If A 0 =0 and D 4=1, the control word is recognized as ICW 1. It contains the control bits for edge/level triggered mode, single/cascade mode, call address interval and whether ICW 4 is required or not, etc. If A 0 =1, the control word is recognized as ICW 2. Ø It stores details regarding interrupt vector addresses.

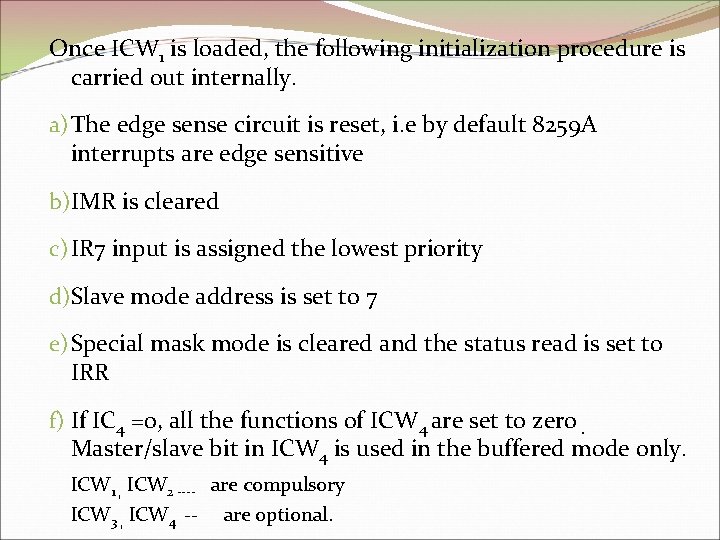

Once ICW 1 is loaded, the following initialization procedure is carried out internally. a) The edge sense circuit is reset, i. e by default 8259 A interrupts are edge sensitive b)IMR is cleared c) IR 7 input is assigned the lowest priority d)Slave mode address is set to 7 e) Special mask mode is cleared and the status read is set to IRR f) If IC 4 =0, all the functions of ICW 4 are set to zero. Master/slave bit in ICW 4 is used in the buffered mode only. ICW 1 , ICW 2 ---- are compulsory ICW 3 , ICW 4 -- are optional.

Fig 5. 3 Initialization Sequence of 8259

A 0 D 7 D 6 0 A 7 A 6 D 5 A 5 D 4 1 D 3 LTIM D 2 ADI D 1 D 0 SNGL IC 4 1=ICW 4 Needed 0= No ICW 4 Needed A 7 -A 5 of interrupt vector address MCs 80/85 mode only Don’t care to 8086 1=Level triggered 0= Edge triggered 1=Single 0= Cascaded Call Address Interval 1=Interval of 4 bytes 0= Interval of 8 bytes ADI=1 for 8086 based system Fig 5. 4 Initialization Command Word 1 (ICW 1) of 8259

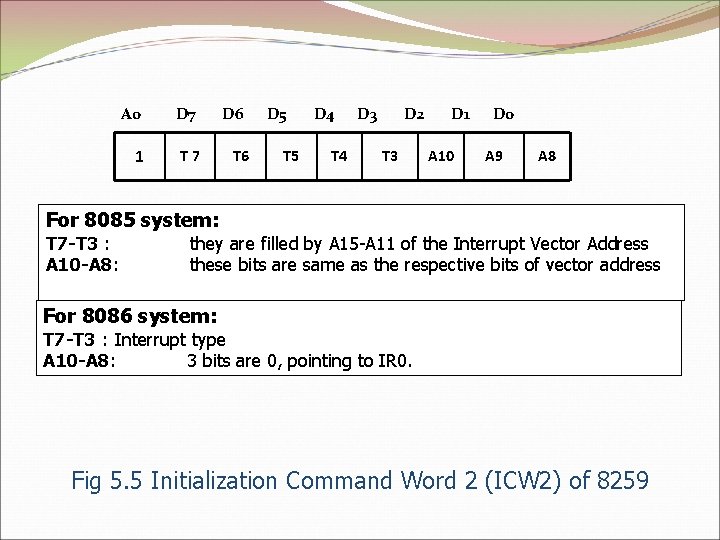

A 0 D 7 D 6 1 T 7 T 6 D 5 T 5 D 4 T 4 D 3 D 2 T 3 D 1 A 10 D 0 A 9 A 8 For 8085 system: T 7 -T 3 : A 10 -A 8: they are filled by A 15 -A 11 of the Interrupt Vector Address these bits are same as the respective bits of vector address For 8086 system: T 7 -T 3 : Interrupt type A 10 -A 8: 3 bits are 0, pointing to IR 0. Fig 5. 5 Initialization Command Word 2 (ICW 2) of 8259

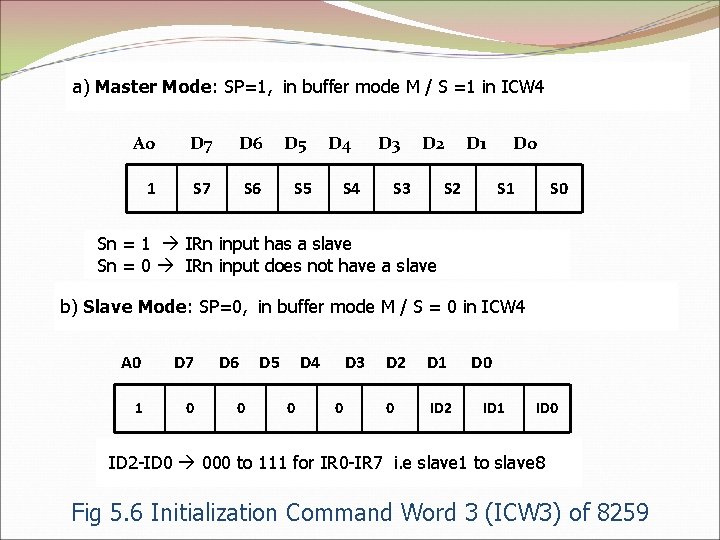

a) Master Mode: SP=1, in buffer mode M / S =1 in ICW 4 A 0 D 7 D 6 D 5 1 S 7 S 6 S 5 D 4 S 4 D 3 D 2 S 3 D 1 S 2 D 0 S 1 S 0 Sn = 1 IRn input has a slave Sn = 0 IRn input does not have a slave b) Slave Mode: SP=0, in buffer mode M / S = 0 in ICW 4 A 0 D 7 1 0 D 6 0 D 5 D 4 0 D 3 0 D 2 D 1 0 ID 2 D 0 ID 1 ID 0 ID 2 -ID 0 000 to 111 for IR 0 -IR 7 i. e slave 1 to slave 8 Fig 5. 6 Initialization Command Word 3 (ICW 3) of 8259

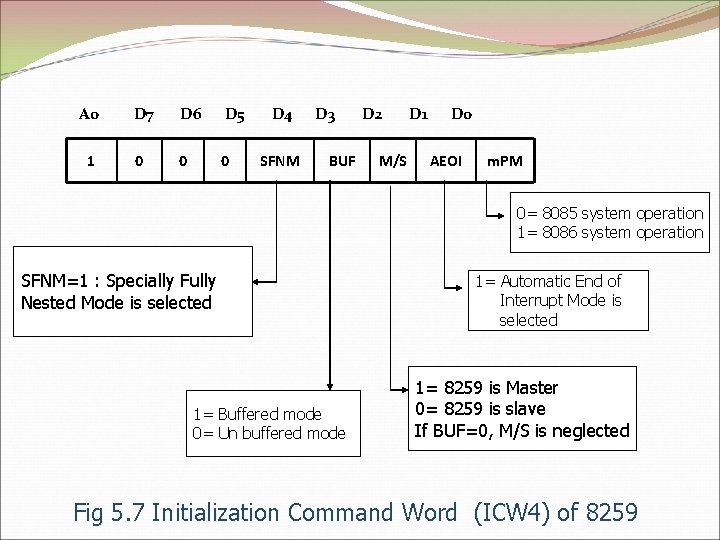

A 0 D 7 D 6 D 5 1 0 0 0 D 4 SFNM D 3 BUF D 2 M/S D 1 D 0 AEOI m. PM 0= 8085 system operation 1= 8086 system operation SFNM=1 : Specially Fully Nested Mode is selected 1= Buffered mode 0= Un buffered mode 1= Automatic End of Interrupt Mode is selected 1= 8259 is Master 0= 8259 is slave If BUF=0, M/S is neglected Fig 5. 7 Initialization Command Word (ICW 4) of 8259

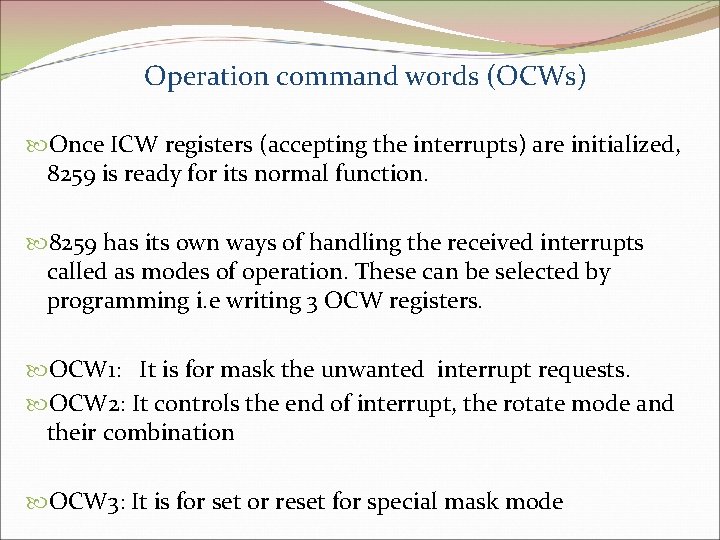

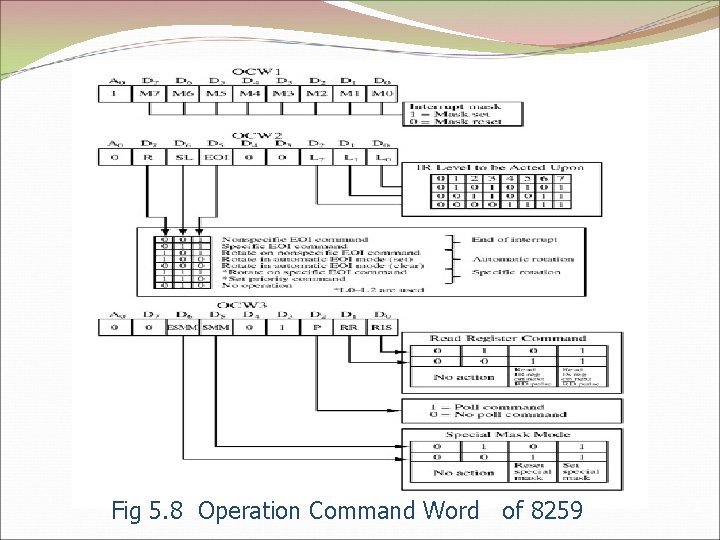

Operation command words (OCWs) Once ICW registers (accepting the interrupts) are initialized, 8259 is ready for its normal function. 8259 has its own ways of handling the received interrupts called as modes of operation. These can be selected by programming i. e writing 3 OCW registers. OCW 1: It is for mask the unwanted interrupt requests. OCW 2: It controls the end of interrupt, the rotate mode and their combination OCW 3: It is for set or reset for special mask mode

Fig 5. 8 Operation Command Word of 8259

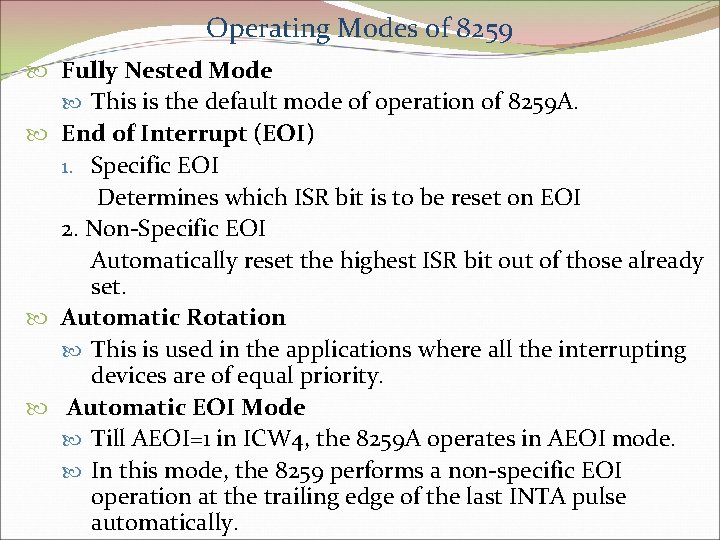

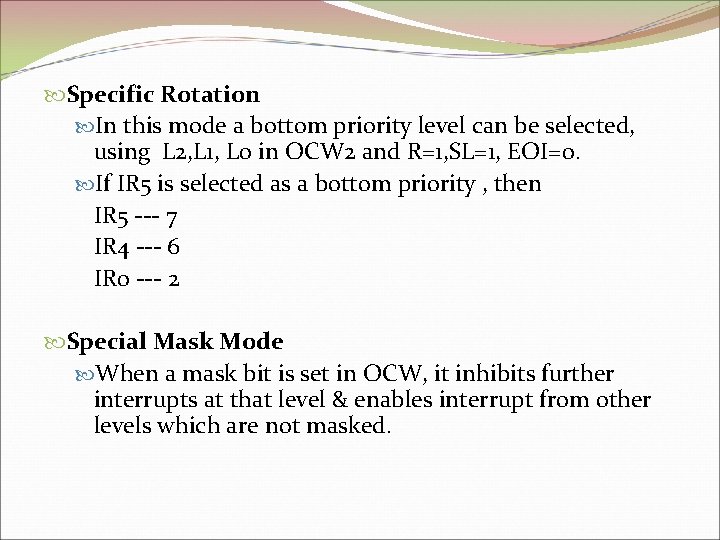

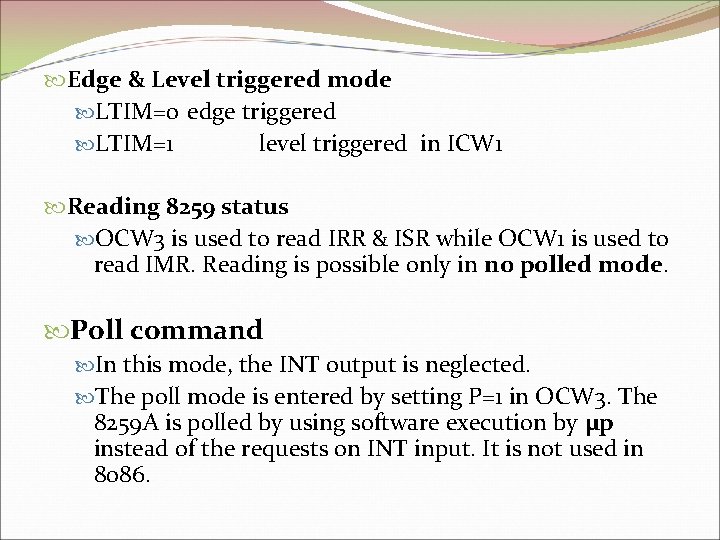

Operating Modes of 8259 Fully Nested Mode This is the default mode of operation of 8259 A. End of Interrupt (EOI) 1. Specific EOI Determines which ISR bit is to be reset on EOI 2. Non-Specific EOI Automatically reset the highest ISR bit out of those already set. Automatic Rotation This is used in the applications where all the interrupting devices are of equal priority. Automatic EOI Mode Till AEOI=1 in ICW 4, the 8259 A operates in AEOI mode. In this mode, the 8259 performs a non-specific EOI operation at the trailing edge of the last INTA pulse automatically.

Specific Rotation In this mode a bottom priority level can be selected, using L 2, L 1, L 0 in OCW 2 and R=1, SL=1, EOI=0. If IR 5 is selected as a bottom priority , then IR 5 --- 7 IR 4 --- 6 IR 0 --- 2 Special Mask Mode When a mask bit is set in OCW, it inhibits further interrupts at that level & enables interrupt from other levels which are not masked.

Edge & Level triggered mode LTIM=0 edge triggered LTIM=1 level triggered in ICW 1 Reading 8259 status OCW 3 is used to read IRR & ISR while OCW 1 is used to read IMR. Reading is possible only in no polled mode. Poll command In this mode, the INT output is neglected. The poll mode is entered by setting P=1 in OCW 3. The 8259 A is polled by using software execution by µp instead of the requests on INT input. It is not used in 8086.

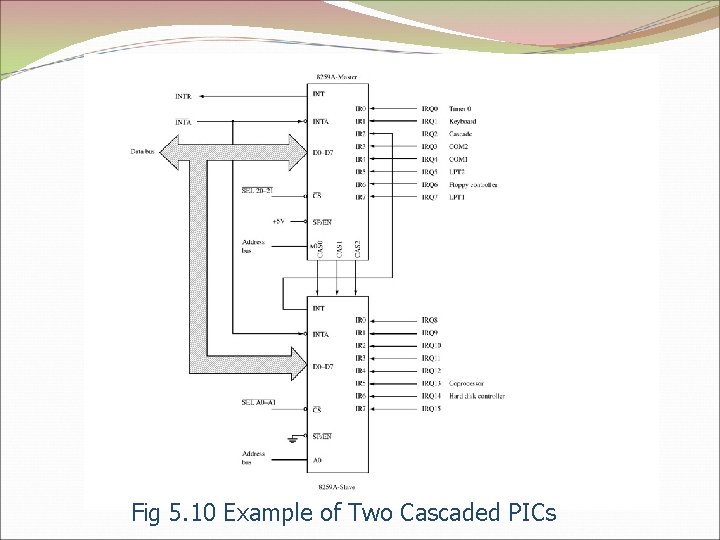

Special Fully Nested Mode (SFNM) This mode is used in more complicated systems, where cascading is used and the priority has to be programmed in the master using ICW 4. In this mode the master interrupts the µp only when the interrupt device has a higher or the same priority than the one currently being served. Buffered Mode When the 8259 A is used in the systems in which bus driving buffers are used on data buses (e. g. cascade systems) the problem of enabling the buffers arises. The 8259 A sends a buffer enable signal on SP / EN pin whenever data is placed on the bus. Cascade Mode The master controls the slaves using CAS 0 -CAS 2 which act as chip select inputs for slave. In this mode, the slave INT output are connected with master IR inputs. EOI issued twice one for master other for slave.

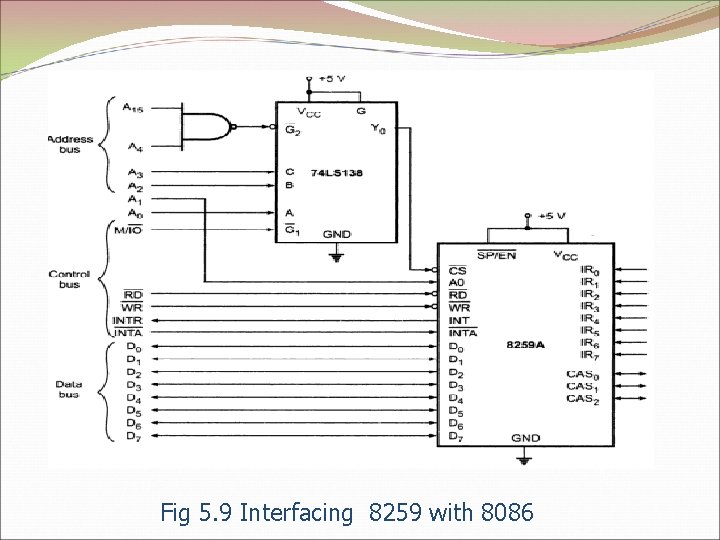

Fig 5. 9 Interfacing 8259 with 8086

Fig 5. 10 Example of Two Cascaded PICs

Interfacing and Programming 8259 Problem: Show 8259 A interfacing connections with 8086 at the address 07 x. Write an ALP to initialize the 8259 A in single level triggered mode, with call address interval of 4, non-buffered, no special fully nested mode. Then set the 8259 A to operate with IR 6 masked, IR 4 as bottom priority level, with special EOI mode. Set special mask mode of 8259 A. Read IRR and ISR into registers BH and BL respectively. IR 0 of 8259 will have type 80 h.

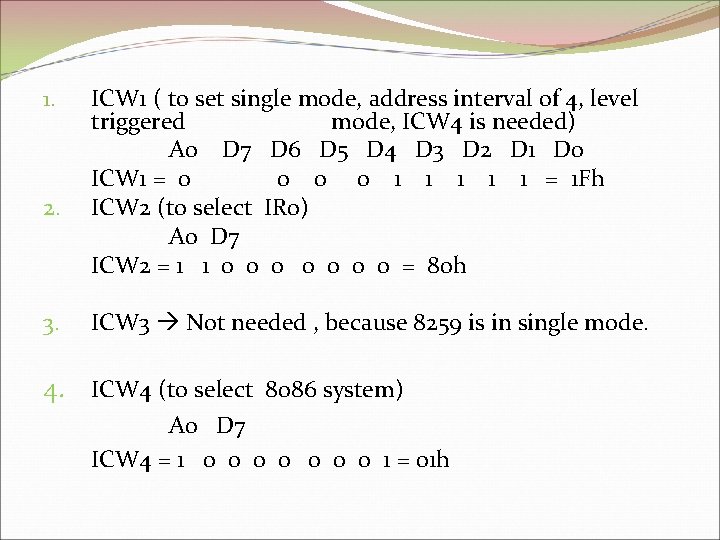

1. 2. 3. ICW 1 ( to set single mode, address interval of 4, level triggered mode, ICW 4 is needed) A 0 D 7 D 6 D 5 D 4 D 3 D 2 D 1 D 0 ICW 1 = 0 0 1 1 1 = 1 Fh ICW 2 (to select IR 0) A 0 D 7 ICW 2 = 1 1 0 0 0 0 = 80 h ICW 3 Not needed , because 8259 is in single mode. 4. ICW 4 (to select 8086 system) A 0 D 7 ICW 4 = 1 0 0 0 0 1 = 01 h

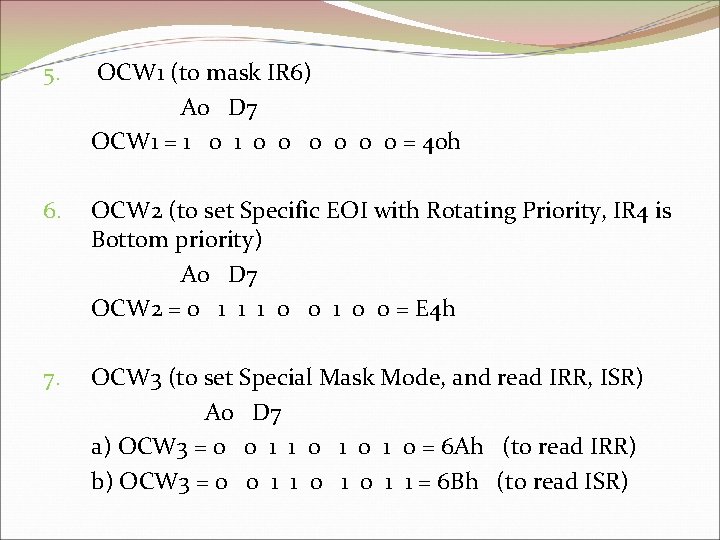

5. OCW 1 (to mask IR 6) A 0 D 7 OCW 1 = 1 0 0 0 0 = 40 h 6. OCW 2 (to set Specific EOI with Rotating Priority, IR 4 is Bottom priority) A 0 D 7 OCW 2 = 0 1 1 1 0 0 = E 4 h 7. OCW 3 (to set Special Mask Mode, and read IRR, ISR) A 0 D 7 a) OCW 3 = 0 0 1 1 0 1 0 = 6 Ah (to read IRR) b) OCW 3 = 0 0 1 1 = 6 Bh (to read ISR)

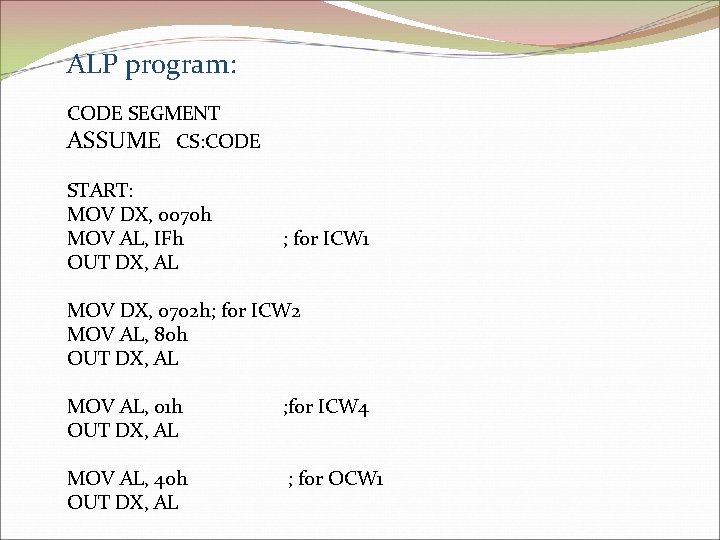

ALP program: CODE SEGMENT ASSUME CS: CODE START: MOV DX, 0070 h MOV AL, IFh OUT DX, AL ; for ICW 1 MOV DX, 0702 h; for ICW 2 MOV AL, 80 h OUT DX, AL MOV AL, 01 h OUT DX, AL ; for ICW 4 MOV AL, 40 h OUT DX, AL ; for OCW 1

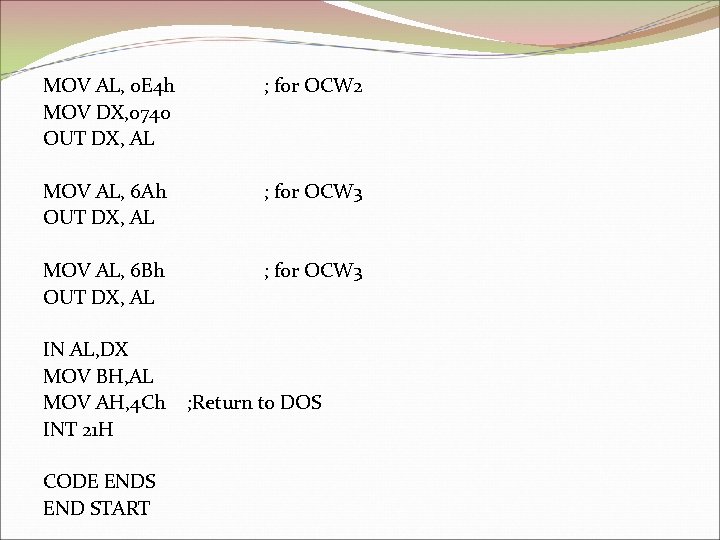

MOV AL, 0 E 4 h MOV DX, 0740 OUT DX, AL ; for OCW 2 MOV AL, 6 Ah OUT DX, AL ; for OCW 3 MOV AL, 6 Bh OUT DX, AL ; for OCW 3 IN AL, DX MOV BH, AL MOV AH, 4 Ch INT 21 H CODE ENDS END START ; Return to DOS

DOS & BIOS Interrupts I. INT 16 h : - for Keyboard Input These interrupts include reading a character from keyboard & getting the status of the keyboard. 1. Function 10 h: - (Read keyboard character) This standard keyboard operation checks the keyboard buffer for an entered character. If none is present, it waits for the use to press a key. If a character is present, the ASCII code of the key is returned to AL & its scan code to AH register.

Eg: MOV AH, 10 h INT 16 h CMP AL, ‘Y’ JE Enter The key pressed is not shown on the screen. 2. Function 11 h: - (Determine if character is present) If the character is present in the keyboard buffer, this operation clears the ZF returns the character to AL & its scan code to AH & character remains in the buffer. If no character is present, the operation sets the ZF & does not wait for a key like the function 10 h.

II. INT 10 h : - for Video Services BIOS INT 10 h supports many services to facilitate 1. Function 00 h : - (Set video mode) A video made scan be text mode or graphics mode. The generally used video mode is 25 rows X 80 columns, color, text mode. To set a mode we have to load function code in to AH & mode number into AL. Ex: MOV AH, 00 h ; loading function code MOV AL, 03 h ; standard color text. INT 10 h ; call interrupt service routine.

2. Function 05 h : - ( select active page) Function 05 h lets you select the page that is to be displayed in text or graphics made. We can create new pages & request alternating between pages Eg: MOV AH, 05 H ; Request active page MOV AL , 00 h ; page 0 is selected INT 10 h

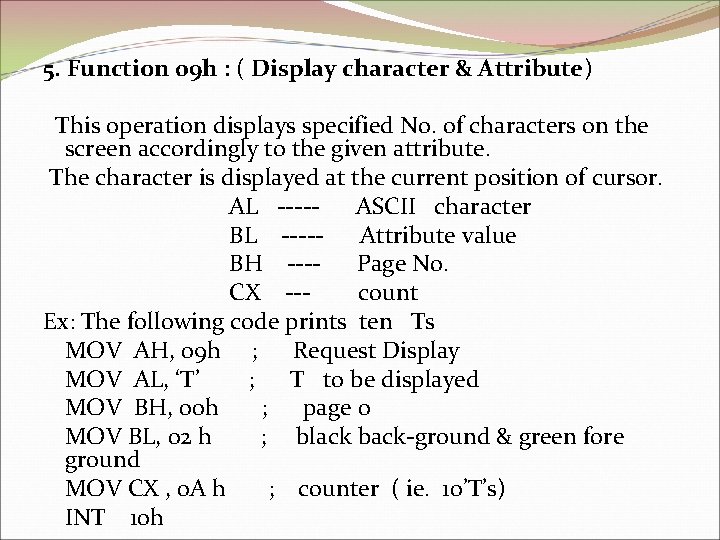

3. Function 02 h : - (Set cursor position) This function is used to set the cursor position anywhere on the screen. The Row no. & Column no. are given in DH & DL registers & the BH register should contain the page no. Eg: MOV AH, 02 h ; request to set cursor MOV BH, 00 h ; page 00 h MOV DH, 16 ; Row=16 MOV DL, 32 ; Column=32 INT 10 h

4. Function 03 h : - ( Return curser status) This function is used to determine the position of curser & the size of the curser. The page No. has to be mentioned in BH register. Ex: MOV AH, 03 h MOV BH, 00 h INT 10 h Out put : ; Request curser location ; Page No: is 0 DH: row No. DL; column No. CH : Starting Scan time CL : Ending Scan time.

5. Function 09 h : ( Display character & Attribute) This operation displays specified No. of characters on the screen accordingly to the given attribute. The character is displayed at the current position of cursor. AL ----ASCII character BL ----Attribute value BH ---Page No. CX --count Ex: The following code prints ten Ts MOV AH, 09 h ; Request Display MOV AL, ‘T’ ; T to be displayed MOV BH, 00 h ; page 0 MOV BL, 02 h ; black back-ground & green fore ground MOV CX , 0 A h ; counter ( ie. 10’T’s) INT 10 h

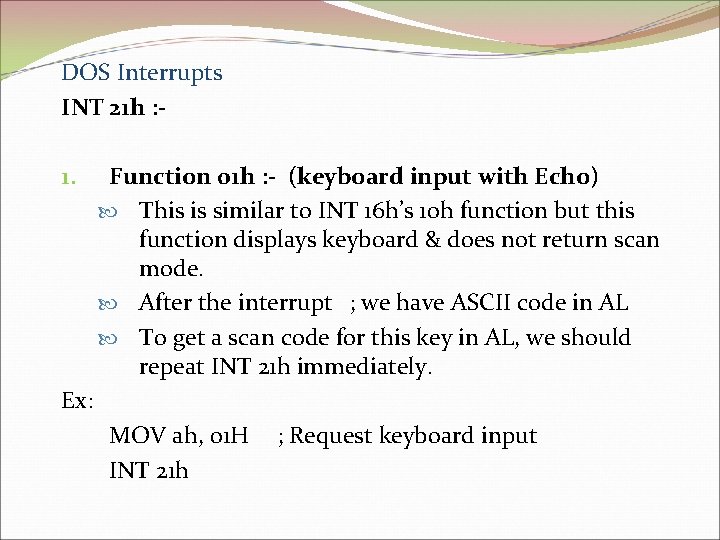

DOS Interrupts INT 21 h : 1. Function 01 h : - (keyboard input with Echo) This is similar to INT 16 h’s 10 h function but this function displays keyboard & does not return scan mode. After the interrupt ; we have ASCII code in AL To get a scan code for this key in AL, we should repeat INT 21 h immediately. Ex: MOV ah, 01 H INT 21 h ; Request keyboard input

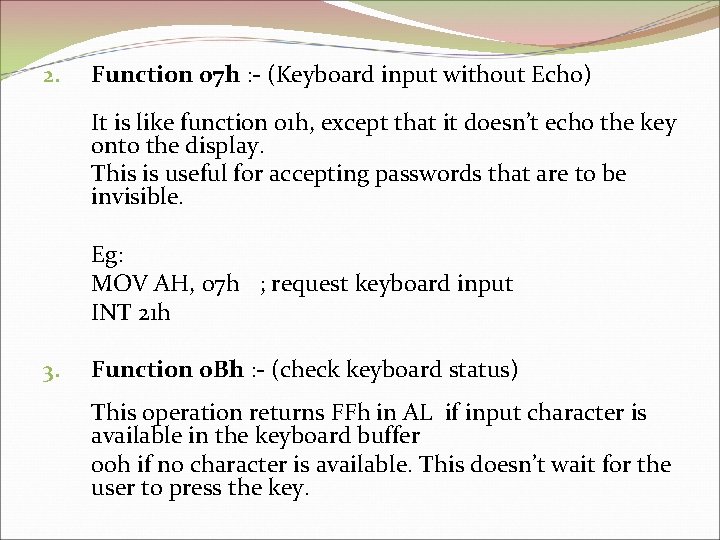

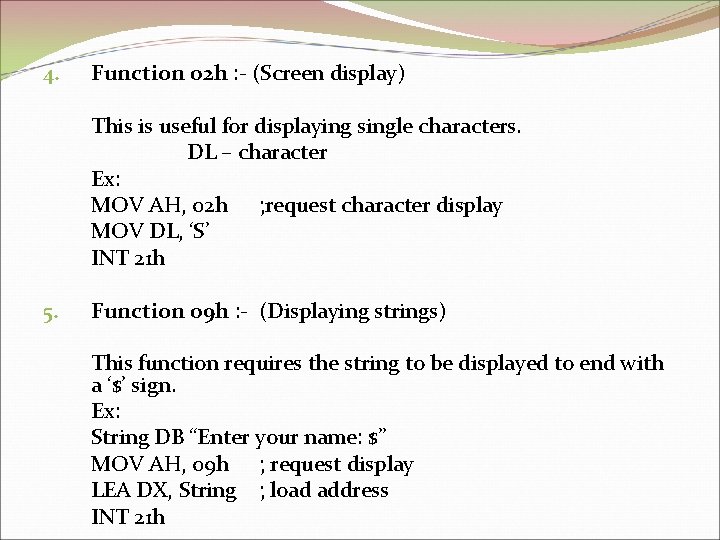

2. Function 07 h : - (Keyboard input without Echo) It is like function 01 h, except that it doesn’t echo the key onto the display. This is useful for accepting passwords that are to be invisible. Eg: MOV AH, 07 h ; request keyboard input INT 21 h 3. Function 0 Bh : - (check keyboard status) This operation returns FFh in AL if input character is available in the keyboard buffer 00 h if no character is available. This doesn’t wait for the user to press the key.

4. Function 02 h : - (Screen display) This is useful for displaying single characters. DL – character Ex: MOV AH, 02 h ; request character display MOV DL, ‘S’ INT 21 h 5. Function 09 h : - (Displaying strings) This function requires the string to be displayed to end with a ‘$’ sign. Ex: String DB “Enter your name: $” MOV AH, 09 h ; request display LEA DX, String ; load address INT 21 h

- Slides: 42