Hardware Verification Group Introduction Prof Sofiene Tahar Department

- Slides: 34

Hardware Verification Group: Introduction Prof. Sofiene Tahar Department of Electrical and Computer Engineering Concordia University Montreal, Quebec, CANADA

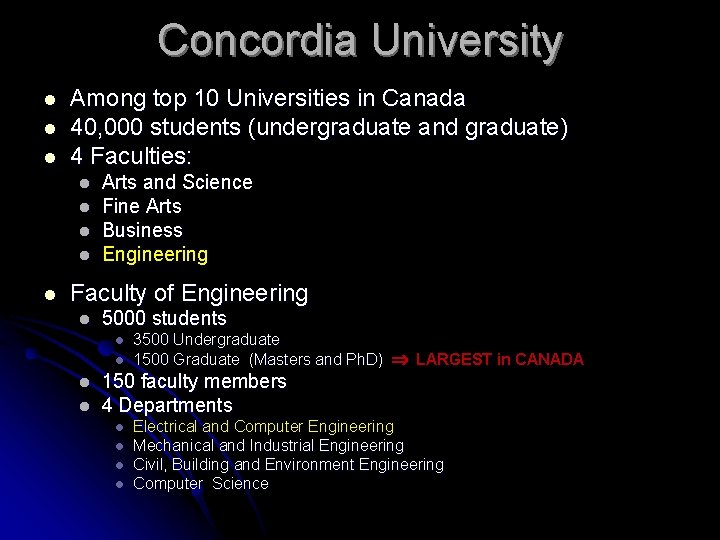

Concordia University l l l Among top 10 Universities in Canada 40, 000 students (undergraduate and graduate) 4 Faculties: l l l Arts and Science Fine Arts Business Engineering Faculty of Engineering l 5000 students l l 3500 Undergraduate 1500 Graduate (Masters and Ph. D) Þ LARGEST in CANADA 150 faculty members 4 Departments l l Electrical and Computer Engineering Mechanical and Industrial Engineering Civil, Building and Environment Engineering Computer Science

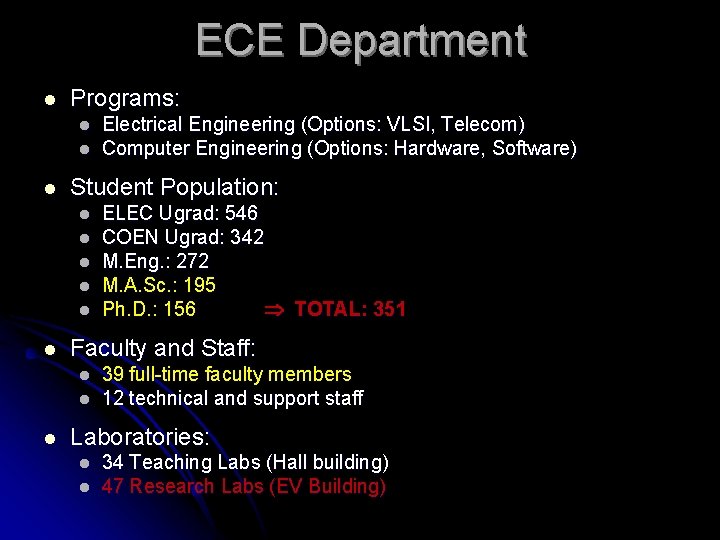

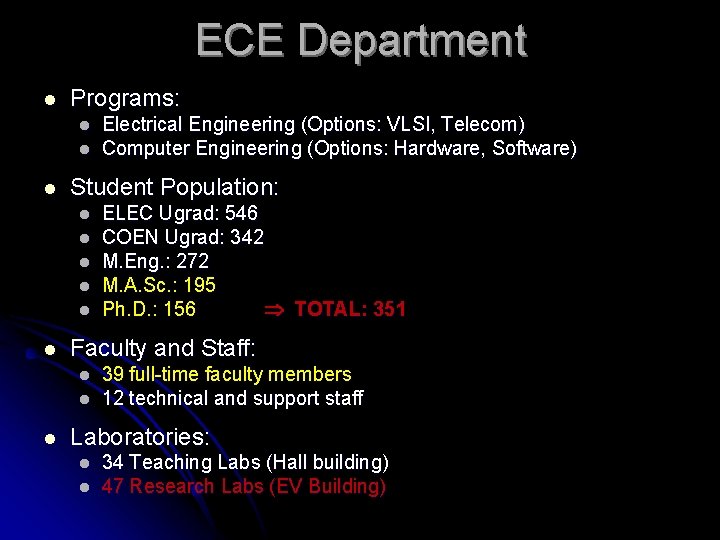

ECE Department l Programs: l l l Student Population: l l l ELEC Ugrad: 546 COEN Ugrad: 342 M. Eng. : 272 M. A. Sc. : 195 Ph. D. : 156 Þ TOTAL: 351 Faculty and Staff: l l l Electrical Engineering (Options: VLSI, Telecom) Computer Engineering (Options: Hardware, Software) 39 full-time faculty members 12 technical and support staff Laboratories: l l 34 Teaching Labs (Hall building) 47 Research Labs (EV Building)

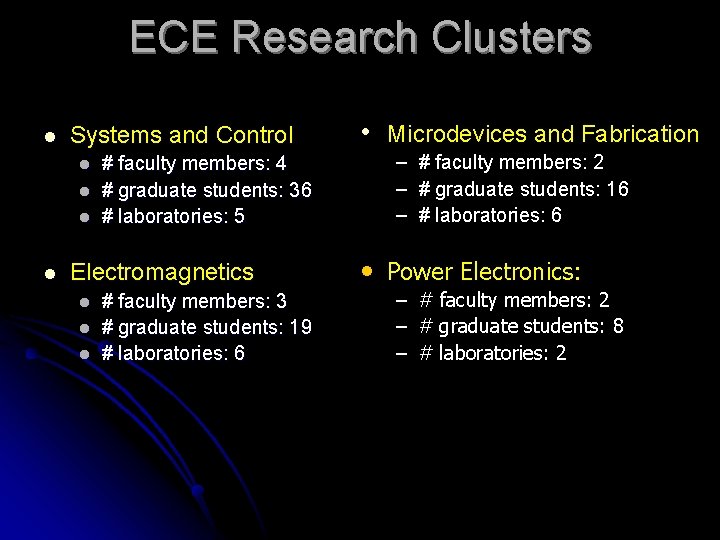

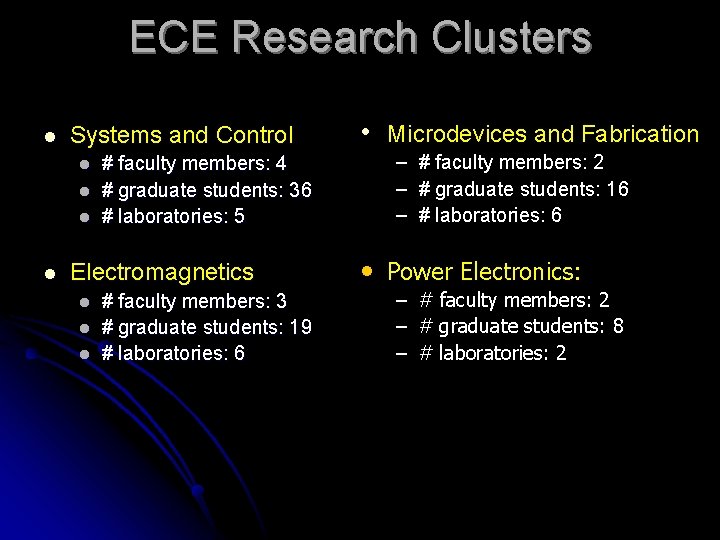

ECE Research Clusters l Systems and Control l l # faculty members: 4 # graduate students: 36 # laboratories: 5 Electromagnetics l l l # faculty members: 3 # graduate students: 19 # laboratories: 6 • Microdevices and Fabrication – – – # faculty members: 2 # graduate students: 16 # laboratories: 6 • Power Electronics: – – – # faculty members: 2 # graduate students: 8 # laboratories: 2

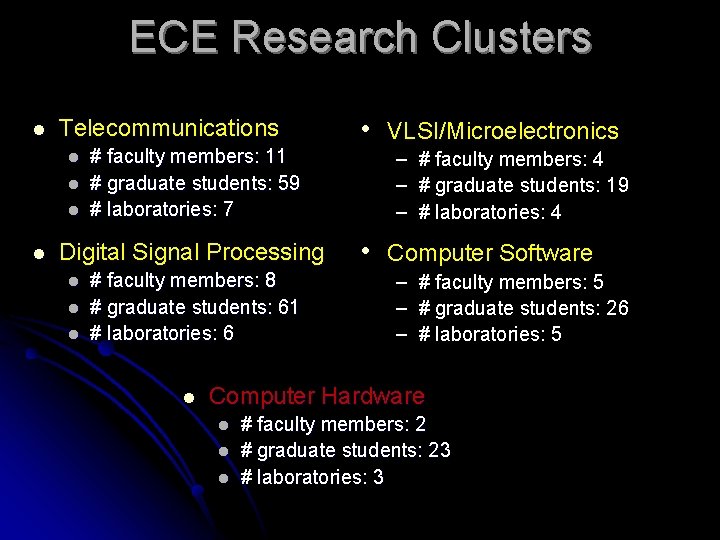

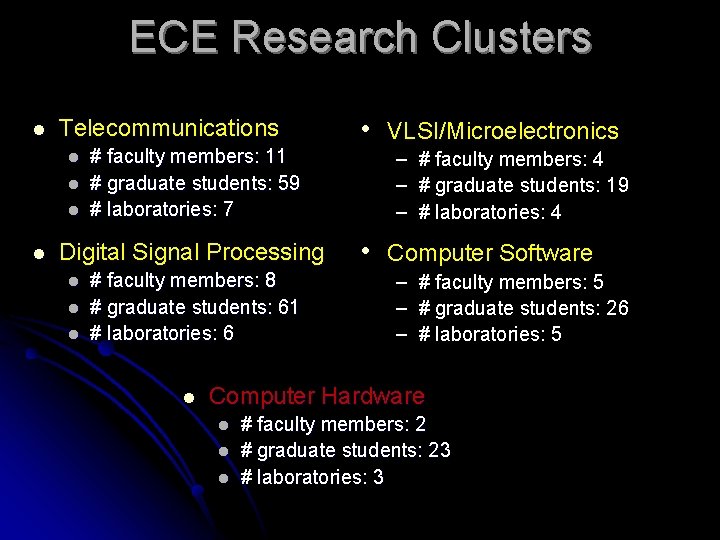

ECE Research Clusters l Telecommunications l l # faculty members: 11 # graduate students: 59 # laboratories: 7 Digital Signal Processing l l l # faculty members: 8 # graduate students: 61 # laboratories: 6 l • VLSI/Microelectronics – # faculty members: 4 – # graduate students: 19 – # laboratories: 4 • Computer Software – # faculty members: 5 – # graduate students: 26 – # laboratories: 5 Computer Hardware l l l # faculty members: 2 # graduate students: 23 # laboratories: 3

8

Design Challenges 9

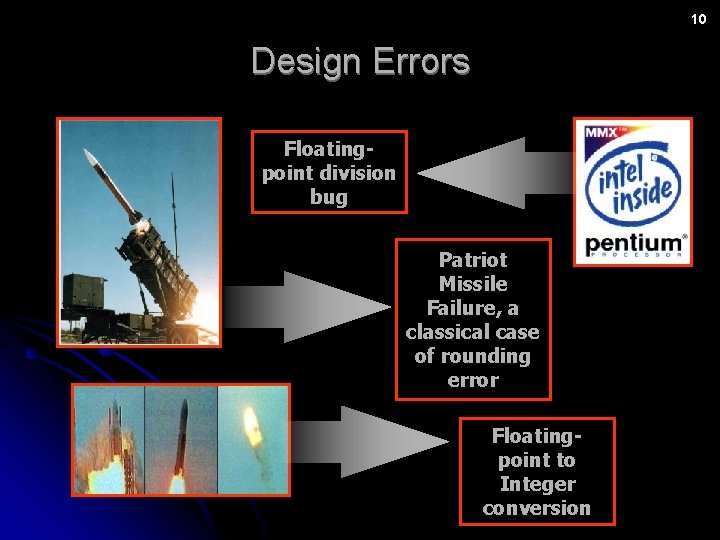

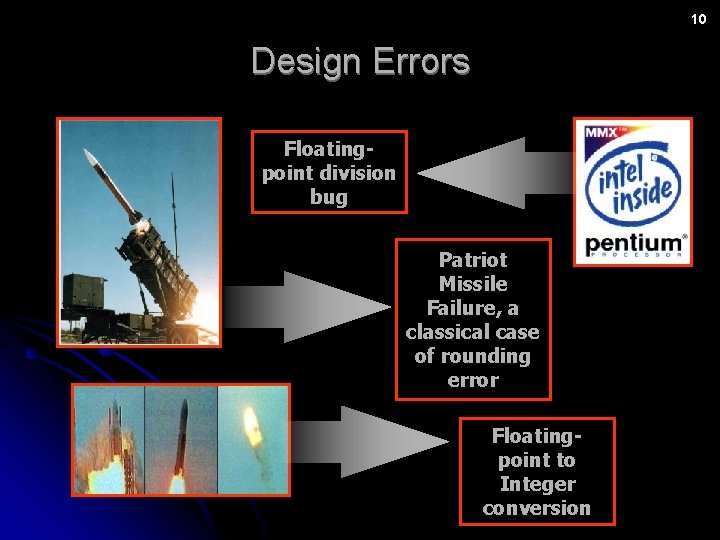

10 Design Errors Floatingpoint division bug Patriot Missile Failure, a classical case of rounding error Floatingpoint to Integer conversion

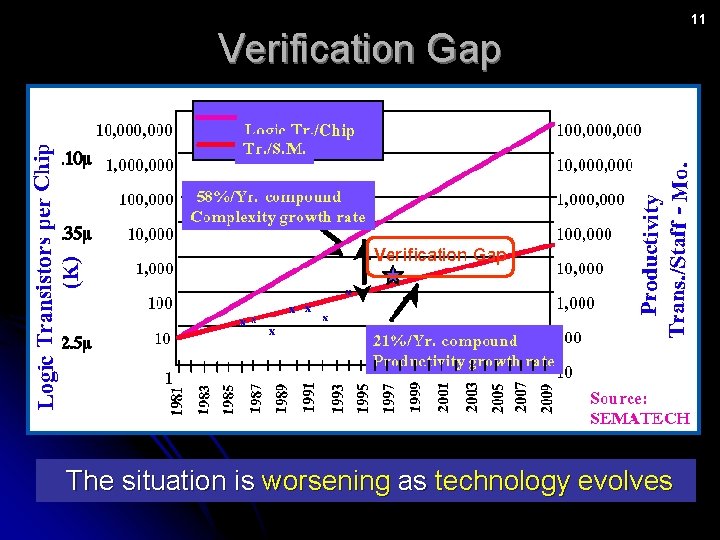

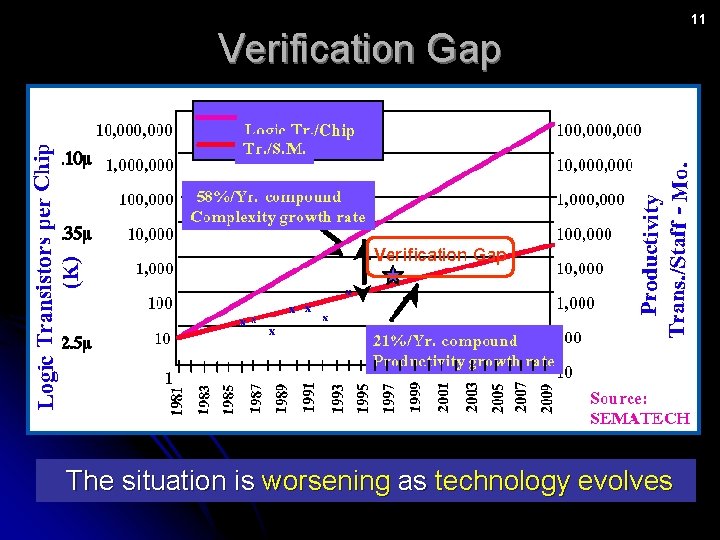

Verification Gap The situation is worsening as technology evolves 11

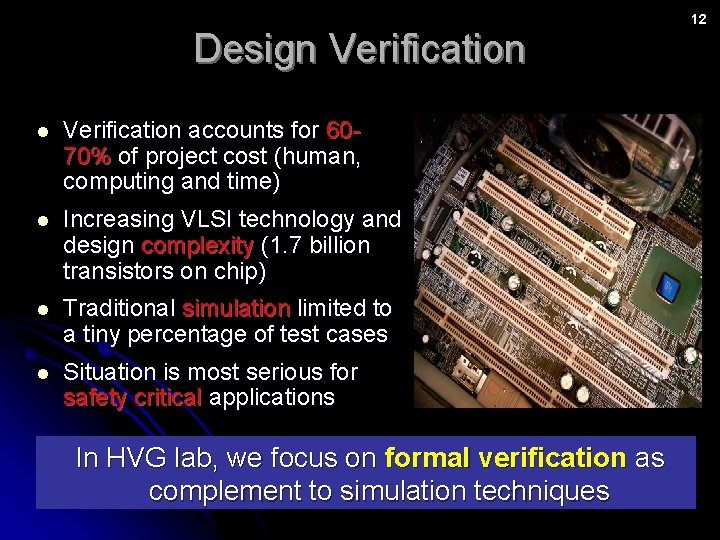

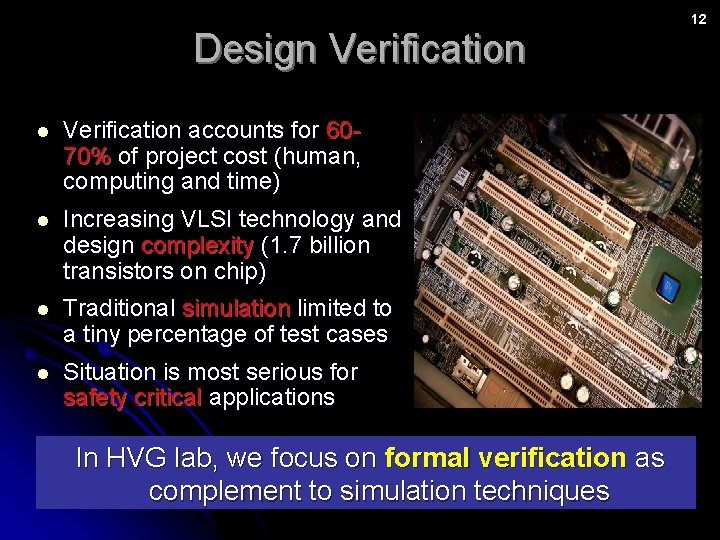

Design Verification l Verification accounts for 6070% of project cost (human, computing and time) l Increasing VLSI technology and design complexity (1. 7 billion transistors on chip) l Traditional simulation limited to a tiny percentage of test cases l Situation is most serious for safety critical applications In HVG lab, we focus on formal verification as complement to simulation techniques 12

13 Who are we? • Hardware Verification Group (HVG) founded in 1996 by Prof. Sofiene Tahar • Recognized as University Research Unit in 2007 • Mission: develop Methodologies, Algorithms and Tools for Formal Verification of Hardware and Embedded Systems • Currently composed of 25 researchers Faculty 3 Postdoc 2 Ph. D 11 Master’s 9

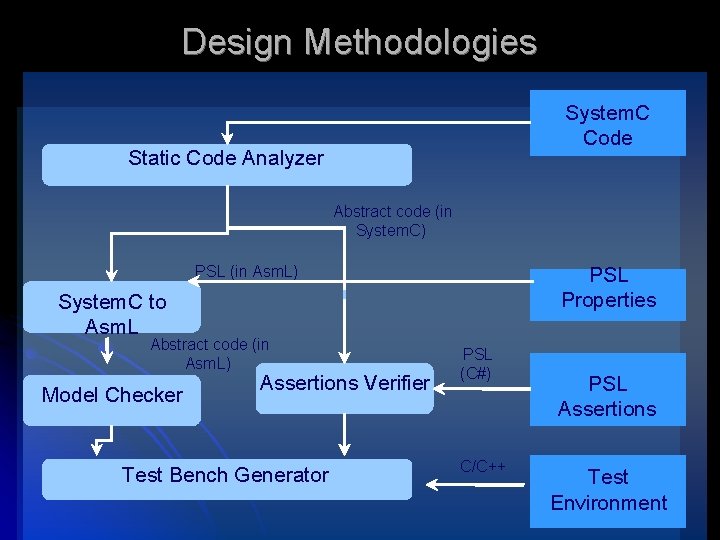

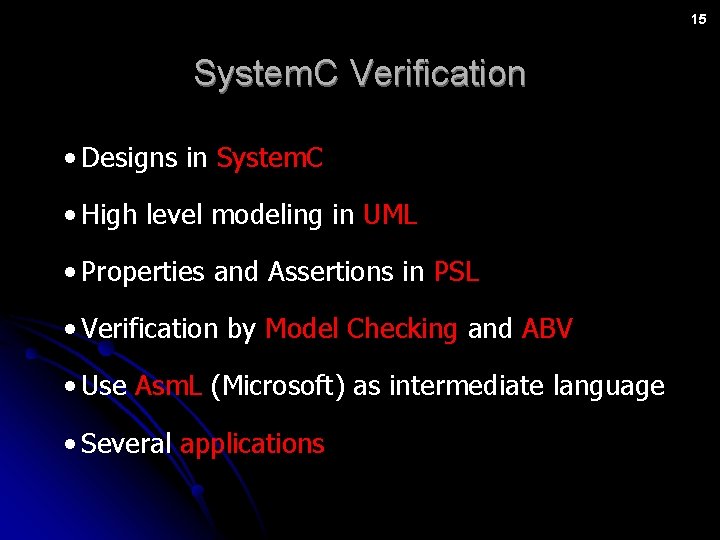

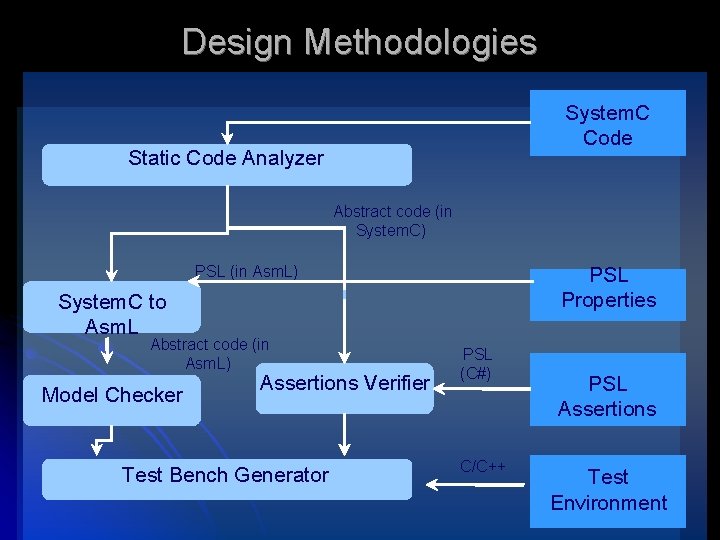

Design Methodologies System. C Code Static Code Analyzer Abstract code (in System. C) PSL (in Asm. L) PSL Properties System. C to Asm. L Abstract code (in Asm. L) Model Checker Assertions Verifier Test Bench Generator PSL (C#) C/C++ PSL Assertions Test Environment

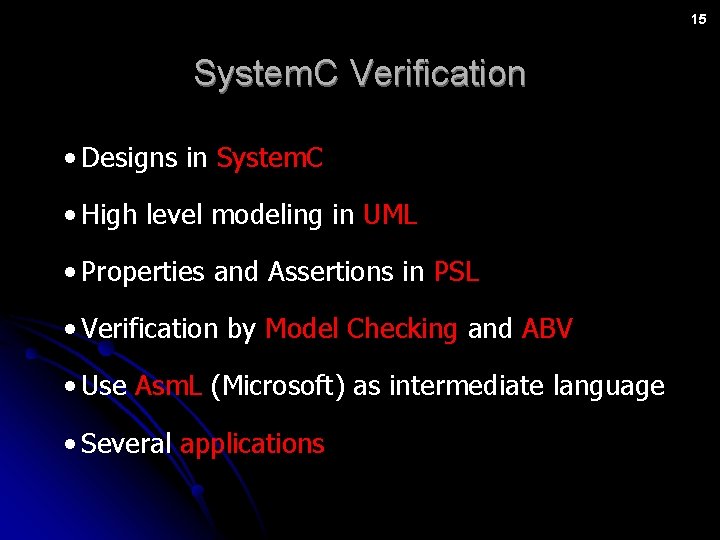

15 System. C Verification • Designs in System. C • High level modeling in UML • Properties and Assertions in PSL • Verification by Model Checking and ABV • Use Asm. L (Microsoft) as intermediate language • Several applications

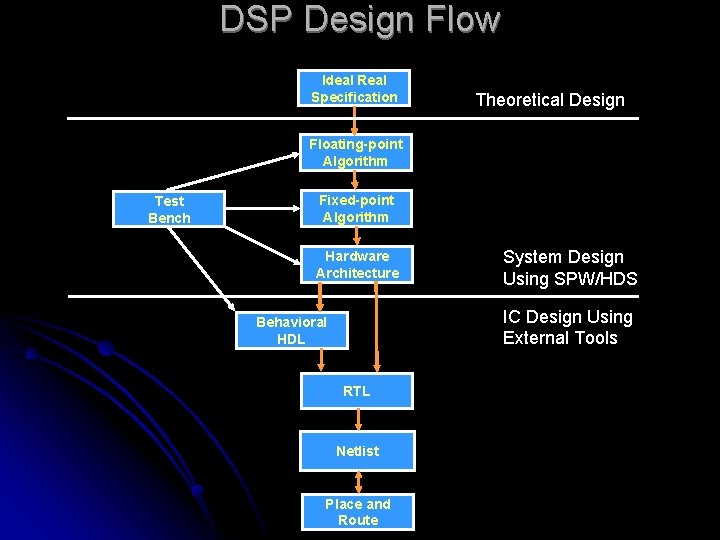

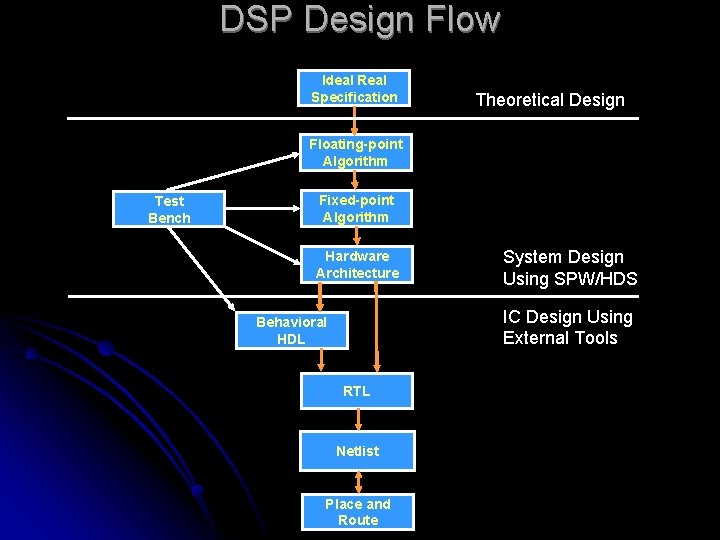

DSP Design Flow Ideal Real Specification Theoretical Design Floating-point Algorithm Test Bench Fixed-point Algorithm Hardware Architecture System Design Using SPW/HDS IC Design Using External Tools Behavioral HDL RTL Netlist Place and Route

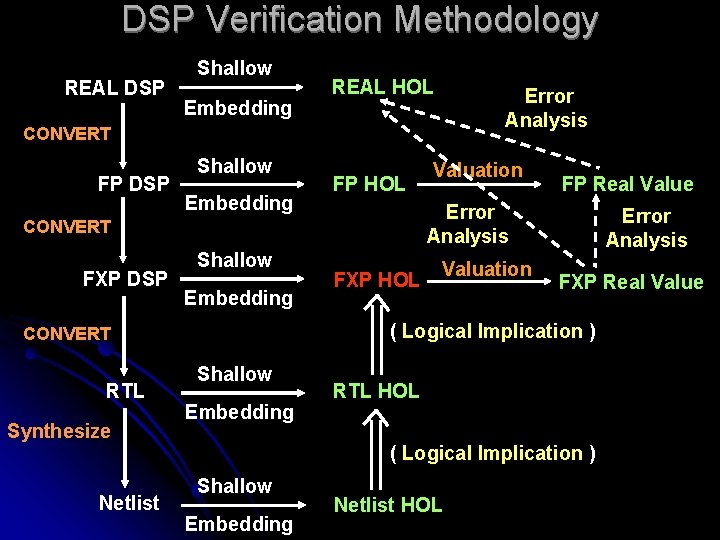

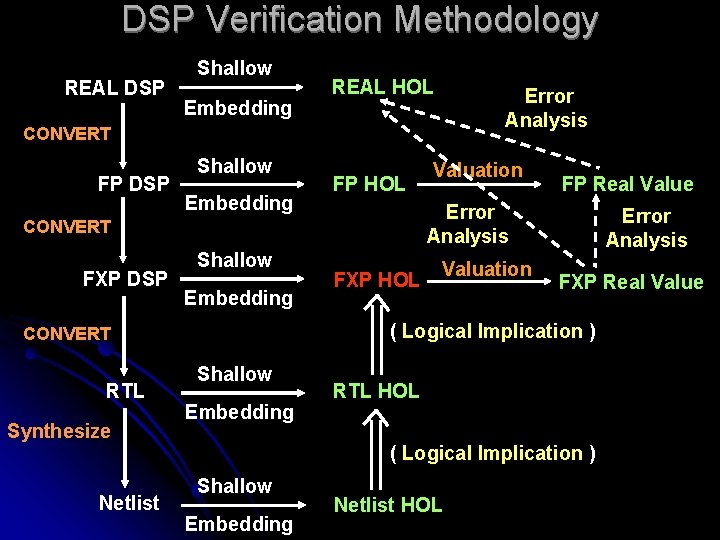

DSP Verification Methodology REAL DSP Shallow Embedding REAL HOL Error Analysis CONVERT FP DSP Shallow Embedding FP HOL FXP DSP Embedding Synthesize Netlist FXP HOL Valuation Error Analysis FXP Real Value ( Logical Implication ) CONVERT RTL FP Real Value Error Analysis CONVERT Shallow Valuation Shallow Embedding RTL HOL ( Logical Implication ) Shallow Embedding Netlist HOL

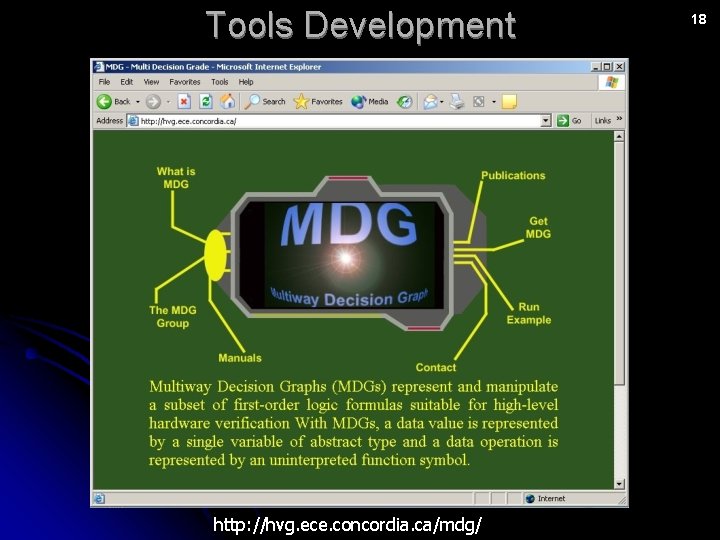

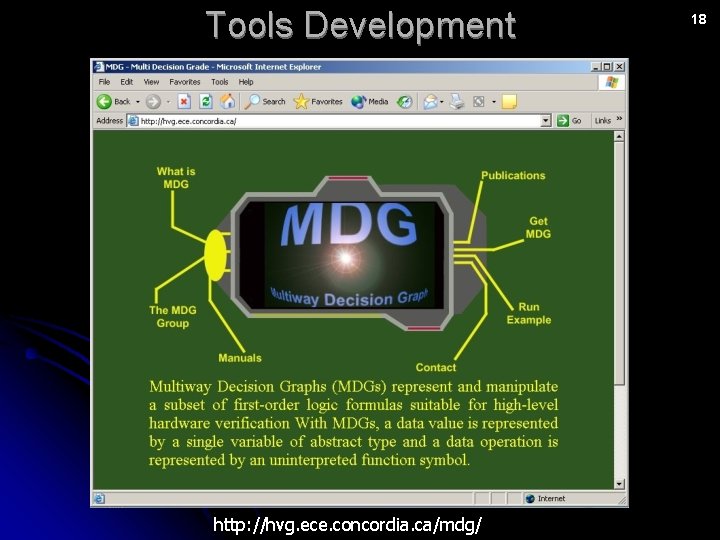

Tools Development http: //hvg. ece. concordia. ca/mdg/ 18

19 Applications (in collaboration with Industry) • Digital Signal Processors verification using HOL (Analog Devices). • ATM switch verification (Nortel Networks). • SONET Protocol verification using MDG (PMC-Sierra) • Telecom block system verification using Formal. Check (PMC-Sierra). • Formal Verification of IEEE FPU using HOL (Intel). • Cryptographic protocols verification (SRI). • Wi. Max modem verification (STMicroelectronics) • Mobile network load and content testing (Ericsson) • ….

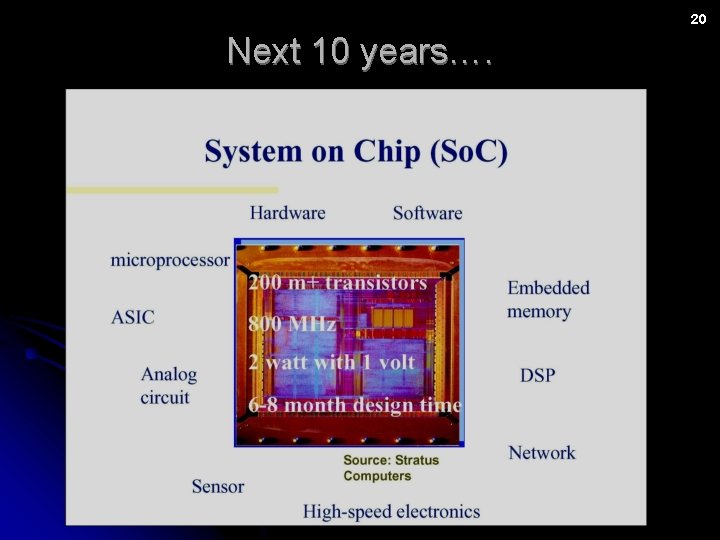

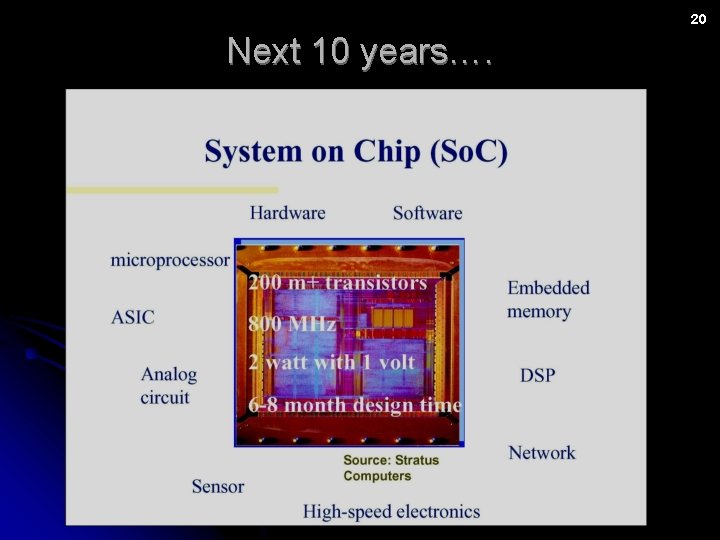

20 Next 10 years….

21 Open Research Projects System-on-a-Chip Verification of Probabilistic Systems Verification of Security Systems Verification of Analog and Mixed Signal Systems Verification of Optical Systems Multiway Decision Graphs Verification Applications (with industry)

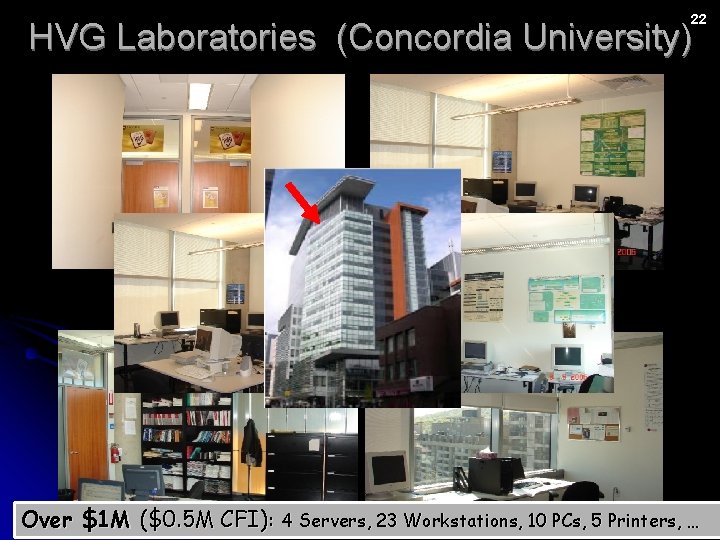

22 HVG Laboratories (Concordia University) Over $1 M ($0. 5 M CFI): 4 Servers, 23 Workstations, 10 PCs, 5 Printers, …

23 Research Funding

24 Industrial Partners Amirix

25 Academic Partners

HVG Stars: Behzad Akbarpour 26 First time in Concordia history l 2006 Best Engineering Ph. D in Canada l 2006 Best Ph. D in Engineering and Sciences in Quebec l 2006 Faculty Best Ph. D Thesis Award l Research Assoc. at Cambridge University, UK

HVG Stars: Amr Abdel-Hamid 27

HVG Stars: Osman Hasan 28 First time in HVG history l Ph. D Thesis ranked in 2008 First in Engineering and second in University l Named Valedictorian for the graduating class of 2008 l Ph. D. Thesis published as a Book by the German VDM Publisher l Work interested NASA!! l Assistant Professor at SEECS, NUST, Pakistan

29 HVG Home Page

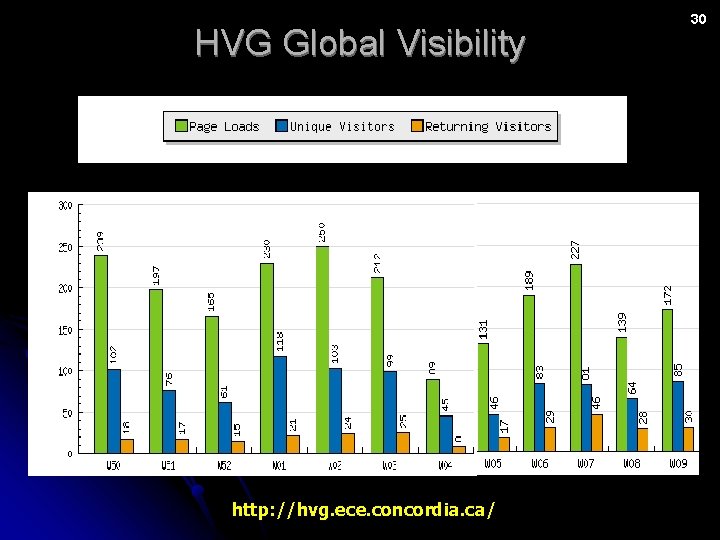

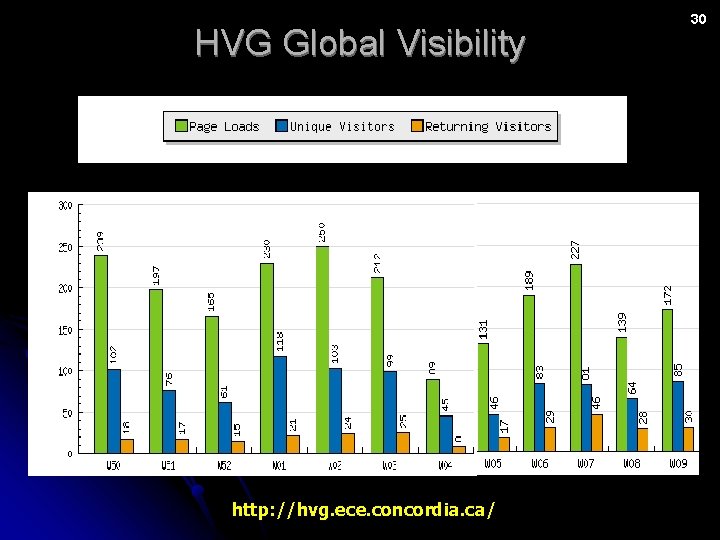

HVG Global Visibility http: //hvg. ece. concordia. ca/ 30

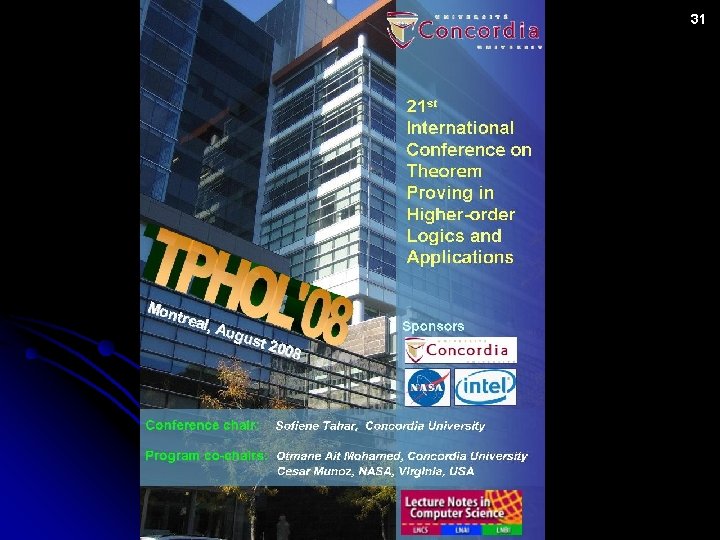

31

32

For more information please refer to: http: //hvg. ece. concordia. ca/ For any further details, please send your questions and comments to: Sofiène Tahar tahar@ece. concordia. ca Thanks!