Invited Tutorial Analog Mixed Signal Verification Kevin D

- Slides: 59

Invited Tutorial: Analog & Mixed Signal Verification Kevin D Jones kdj@acm. org

An Apology I owe you (collectively) an apology! Paper accompanying this talk is not in proceedings Kevin D. Jones Rambus Inc.

Overview • • • Audience Calibration Digital and Analog The Analog Design (& Verification) Process Mixed mode Design (& Verification) Process Formal Verification of A(MS) Systems An Analog Example The State of the Art A Mixed Mode Example Open Problems - A Challenge Summary and Conclusions 3

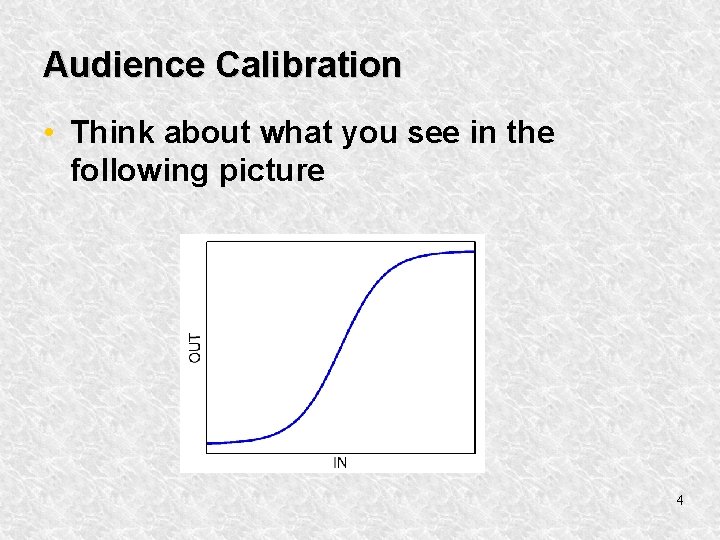

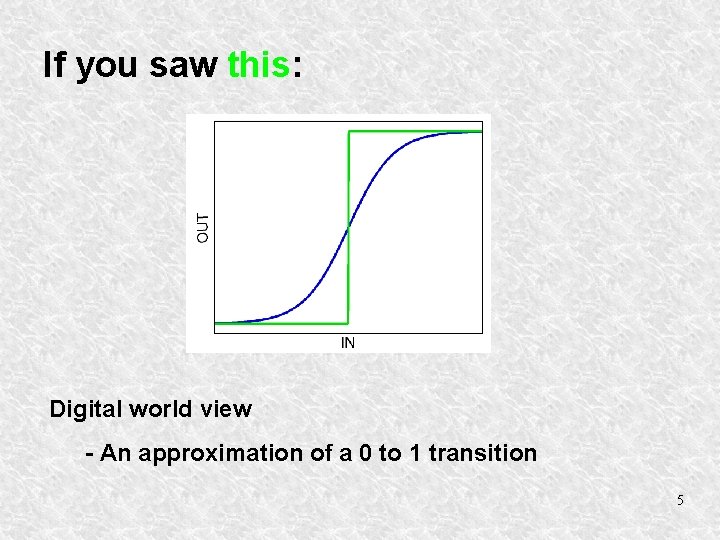

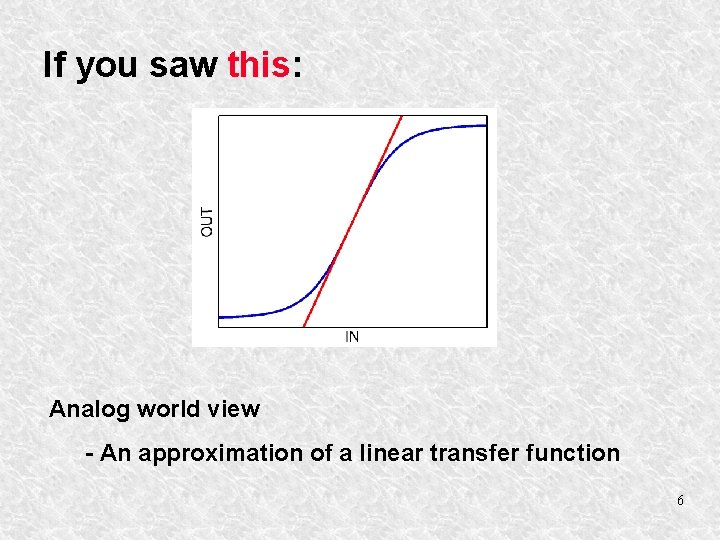

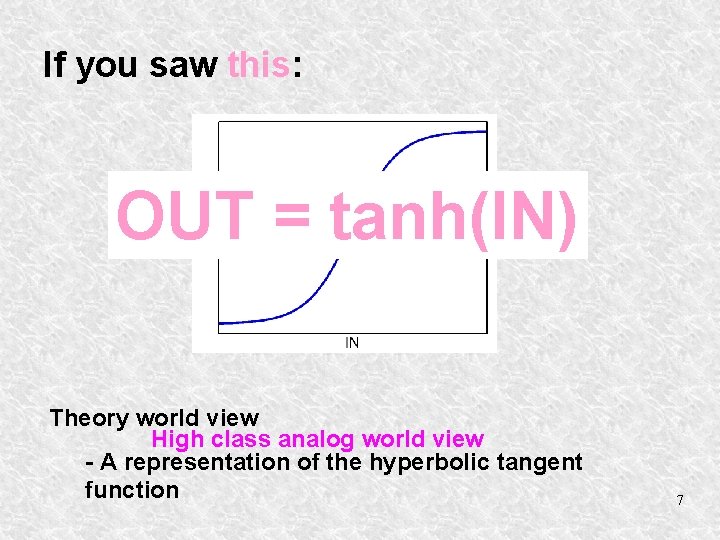

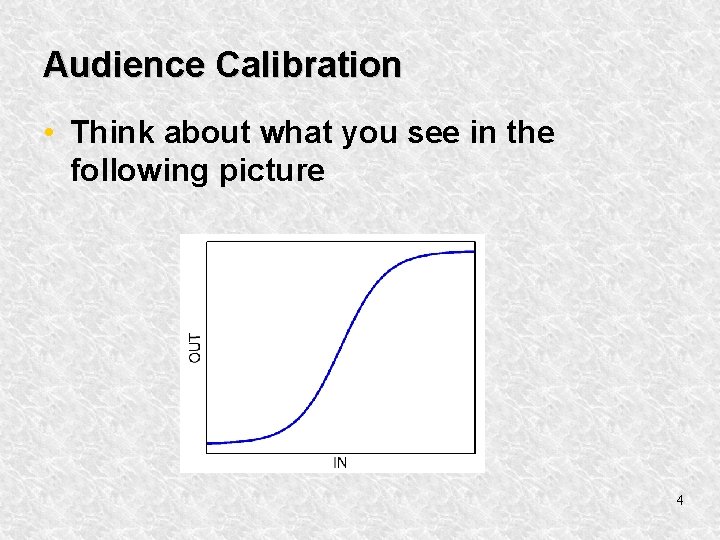

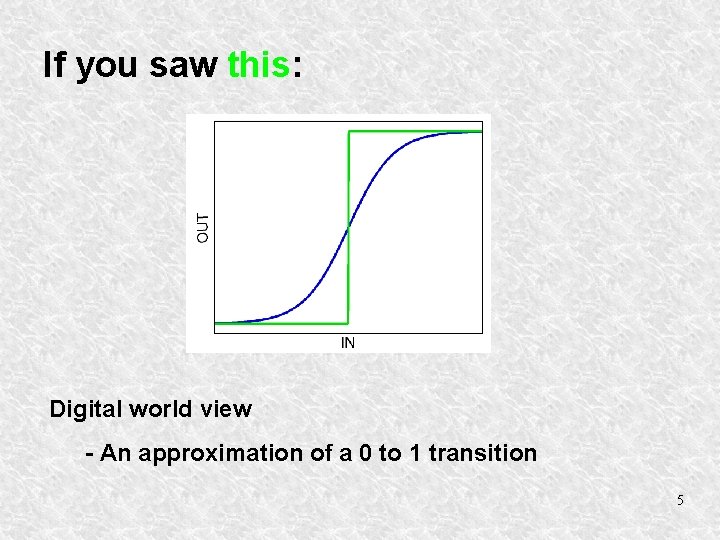

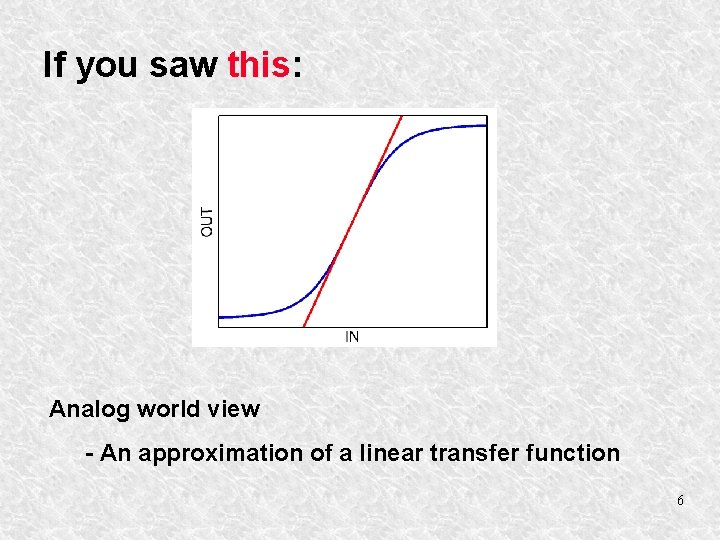

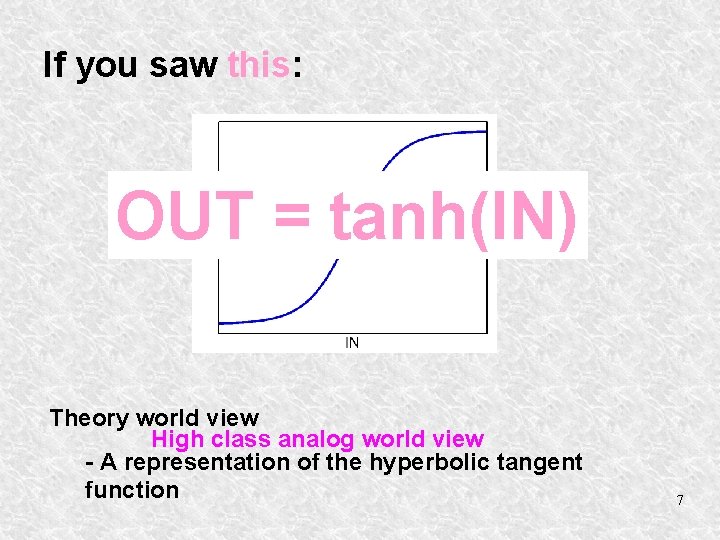

Audience Calibration • Think about what you see in the following picture 4

If you saw this: Digital world view - An approximation of a 0 to 1 transition 5

If you saw this: Analog world view - An approximation of a linear transfer function 6

If you saw this: OUT = tanh(IN) Theory world view High class analog world view - A representation of the hyperbolic tangent function 7

Digital and Analog • Different worlds • Think differently • Different mindset, tools, approaches • Occasionally forced to coexist in mixed signal designs • My assumptions for this audience: • People understand digital design and verification • Analog is the novel part • Main focus on the “front end” 8

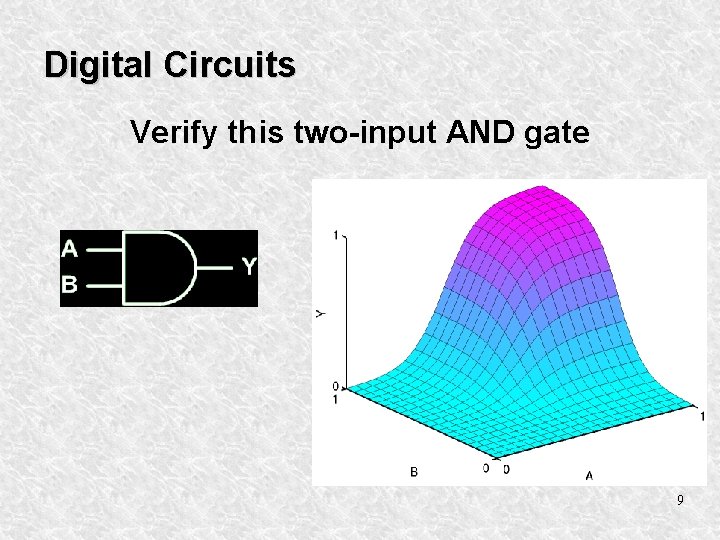

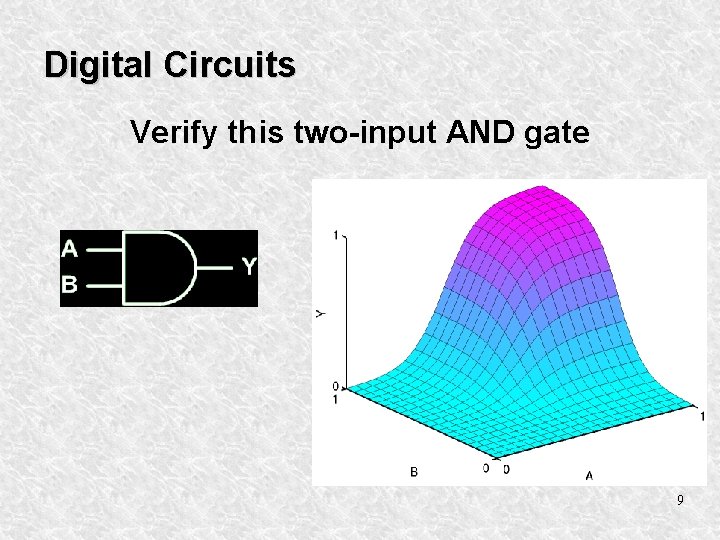

Digital Circuits Verify this two-input AND gate 9

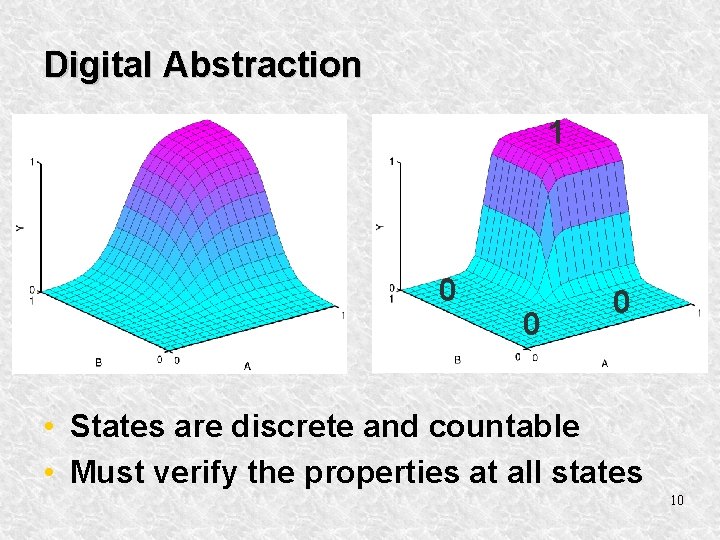

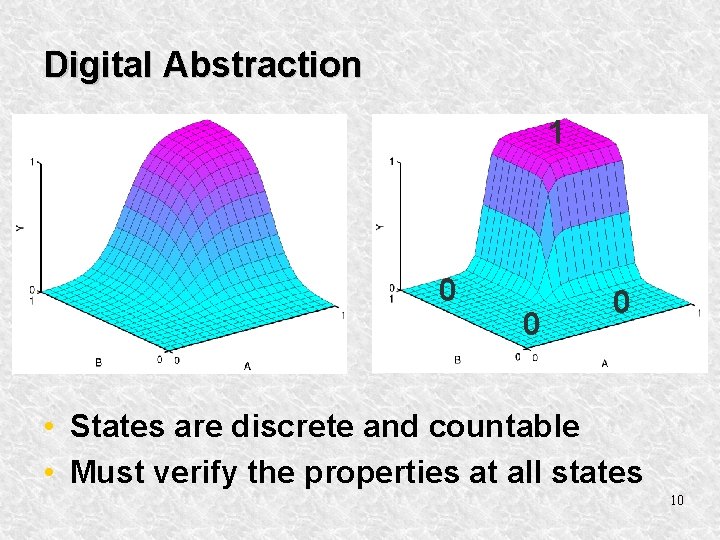

Digital Abstraction 1 0 0 0 • States are discrete and countable • Must verify the properties at all states 10

Digital Verification • Practice today: (Exhaustive) Simulation • Directed pseudo-random simulation • Coverage based • Formal methods • BDD based exhaustive state analysis • Symbolic simulation • Tools: Specman, System. Verilog, Equivalence Checkers, Model Checkers, Theorem Provers, … • Quite tractable for Formal Methods and lots 11 of research has been done

Analog Circuits Verify this op-amp 12

Aside: AMS Verification is becoming a Significant Problem • More and more systems have analog components • In recent DAC Keynote, Justin Ratner pointed out the world is fundamentally analog • Fast becoming a leading cause of So. C failure 13

Analog Design (& Verification) Process 14

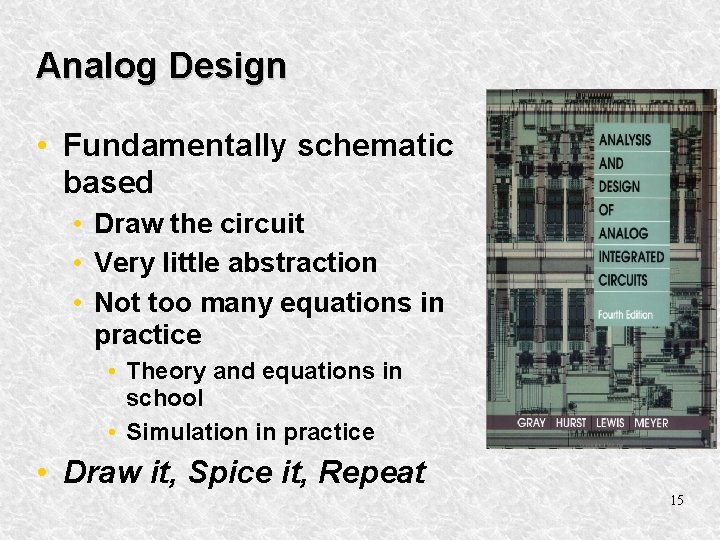

Analog Design • Fundamentally schematic based • Draw the circuit • Very little abstraction • Not too many equations in practice • Theory and equations in school • Simulation in practice • Draw it, Spice it, Repeat 15

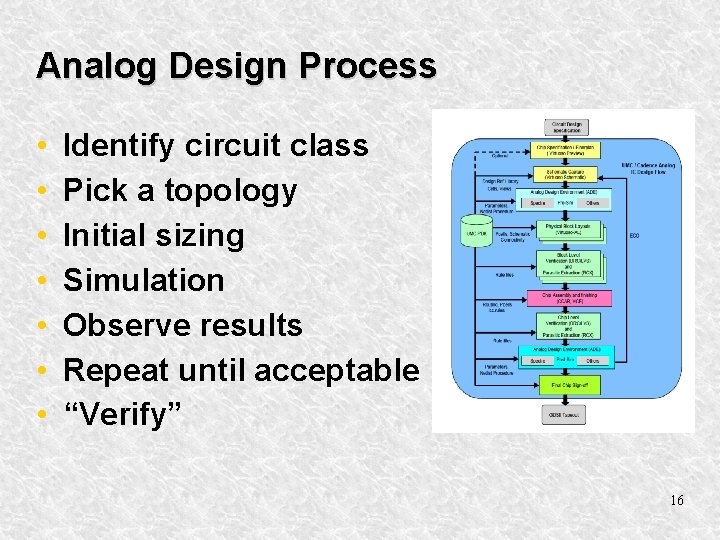

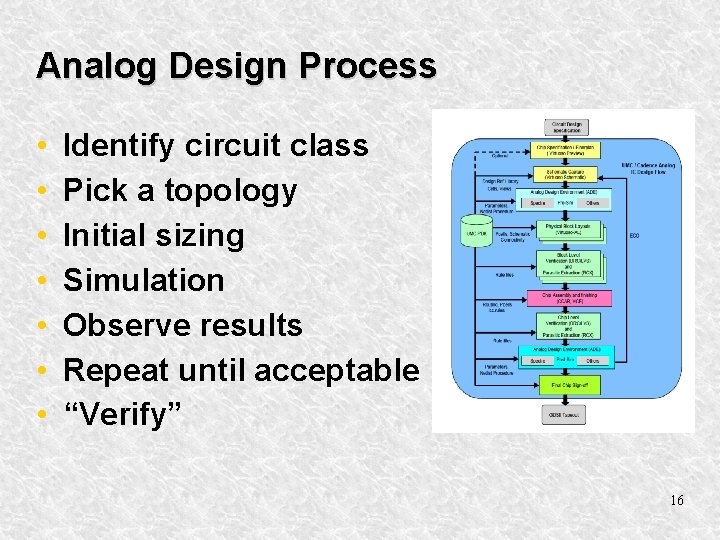

Analog Design Process • • Identify circuit class Pick a topology Initial sizing Simulation Observe results Repeat until acceptable “Verify” 16

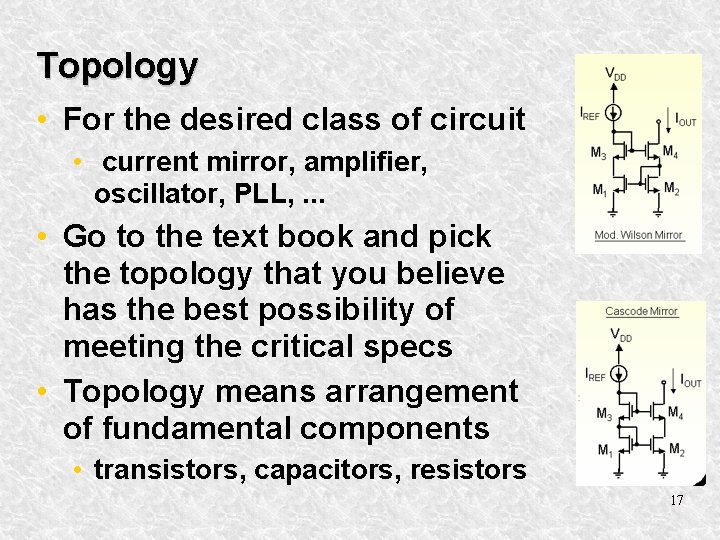

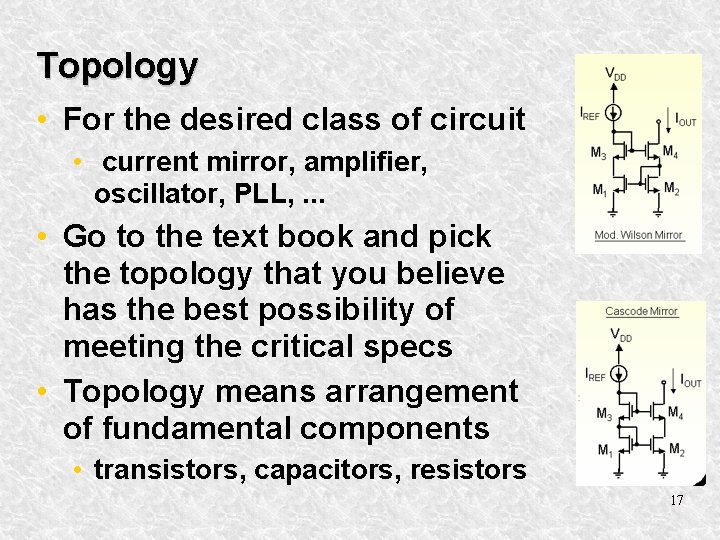

Topology • For the desired class of circuit • current mirror, amplifier, oscillator, PLL, . . . • Go to the text book and pick the topology that you believe has the best possibility of meeting the critical specs • Topology means arrangement of fundamental components • transistors, capacitors, resistors 17

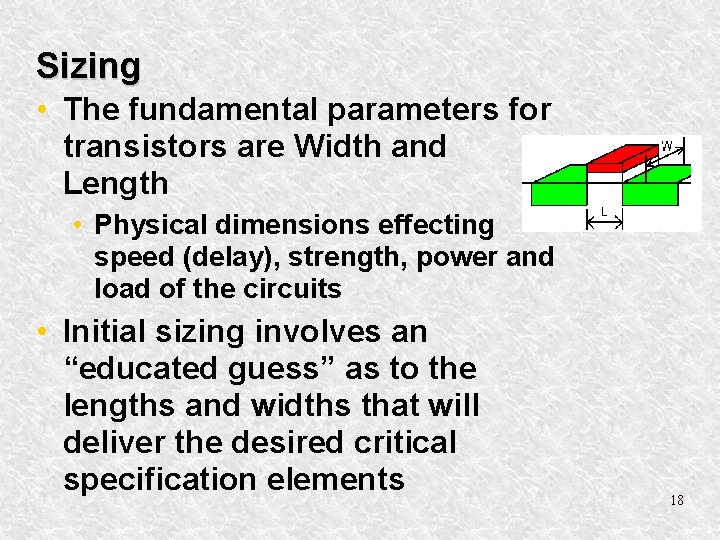

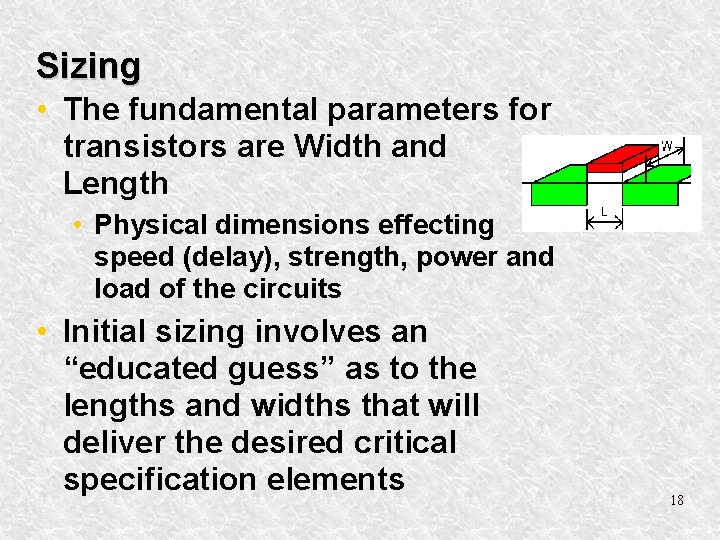

Sizing • The fundamental parameters for transistors are Width and Length • Physical dimensions effecting speed (delay), strength, power and load of the circuits • Initial sizing involves an “educated guess” as to the lengths and widths that will deliver the desired critical specification elements 18

Simulation • Unlike the digital world, simulation is a fundamental part of the design process • many parameters are unknown until after simulation • SPICE • DC-analysis • AC-analysis • Transient 19

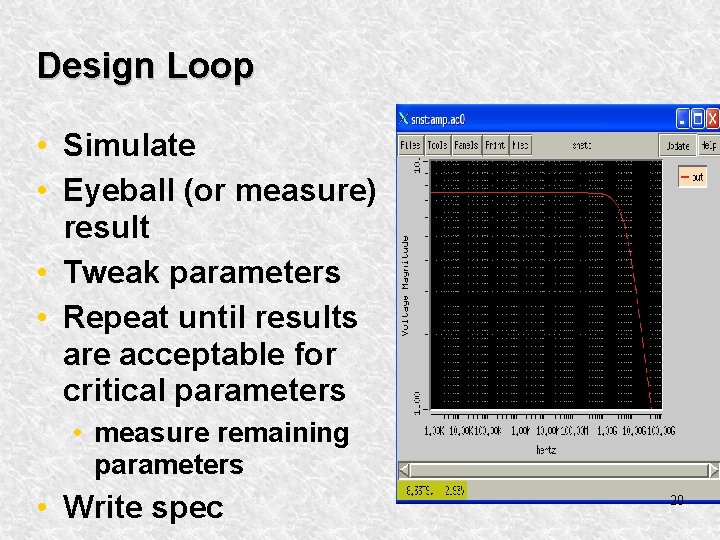

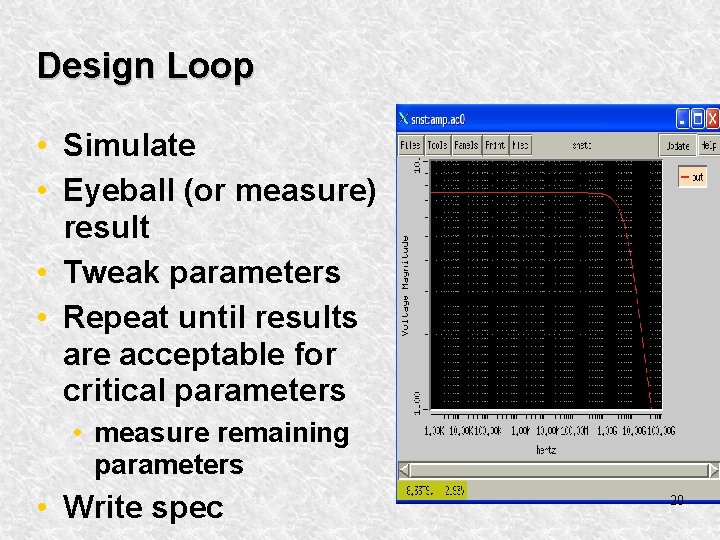

Design Loop • Simulate • Eyeball (or measure) result • Tweak parameters • Repeat until results are acceptable for critical parameters • measure remaining parameters • Write spec 20

Aside: Fancier Tools • Cadence Neocircuit • Automates the sizing loop • Reduces the human effort • Very expensive in terms of machine effort 21

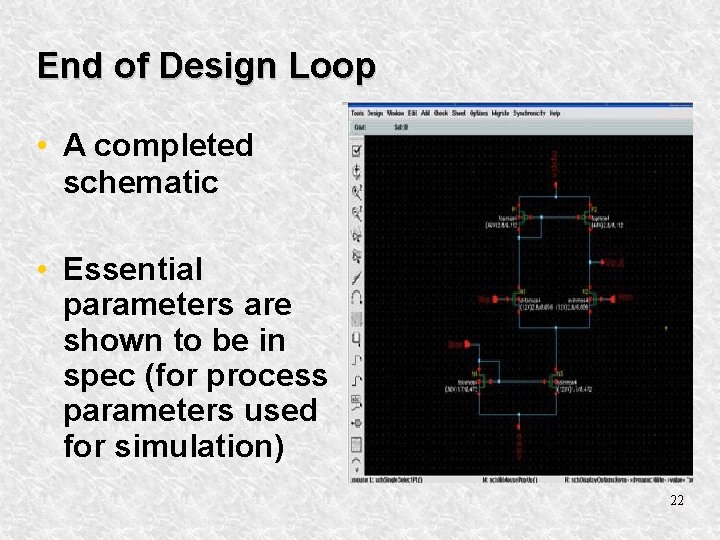

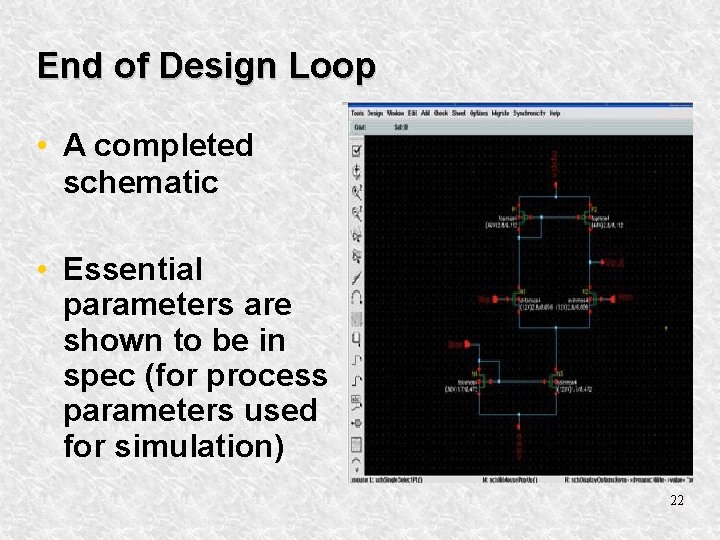

End of Design Loop • A completed schematic • Essential parameters are shown to be in spec (for process parameters used for simulation) 22

Verification of Analog Circuits • Transistor level models • Circuit simulator (Spice) • • DC simulation AC simulation Parameter sweeping Statistical variation (Monte Carlo) • Tools: SPICE (HSPICE, PSPICE, Spectre, eldo, …) • Transient (time based) simulation is very expensive • Simulation inputs based on designers’ understanding/experience/intuition • i. e. verification is the same as design simulation 23

Verification • No real notion of verification as a separate process using different tools and approaches • Design is exercised not verified • Everything is based on simulation • Analog Verification today is roughly equivalent to Digital Verification in 1990 24

Statistical Verification • Monte Carlo simulation • simulators support statistical variation of certain input parameters • Hits some variant spaces • classical “corners”, random variation • Very expensive • Each simulation may take a long time • Overall result is as strong as the number of simulations 25

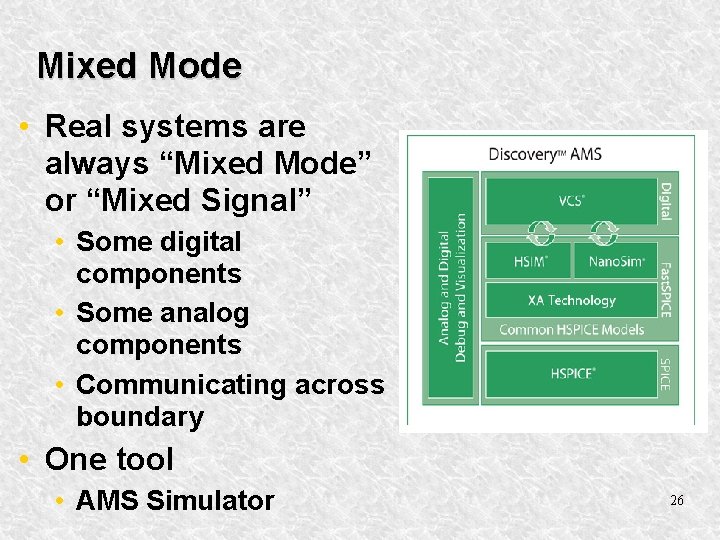

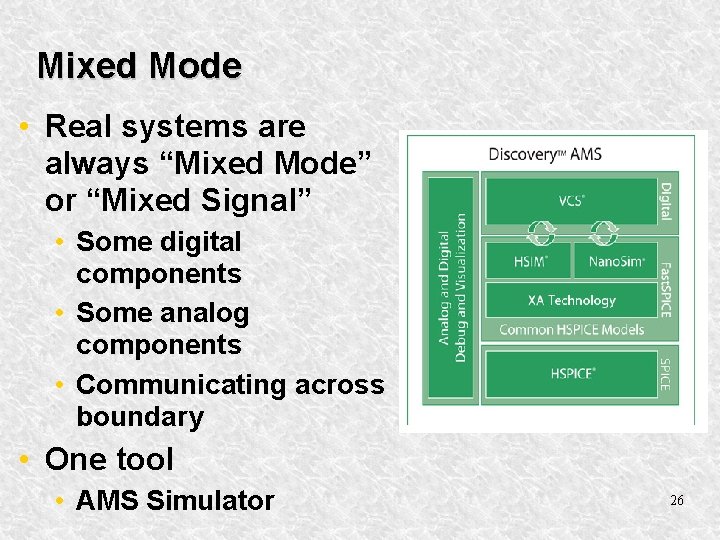

Mixed Mode • Real systems are always “Mixed Mode” or “Mixed Signal” • Some digital components • Some analog components • Communicating across boundary • One tool • AMS Simulator 26

Verification (should) != Simulation • 25+ Years of research in verification of digital systems has shown that simulation is not a sufficient tool for verification • For analog systems, this is even more true since (transient/time based) simulation is very expensive • Look for an abstraction that allows analysis 27

Linear Abstraction • Choose an Operating Point • Apply small-signal perturbations to the OP ( A, B) • Derive the relation Y = · A + · B • “Linearizing the system at the OP” • If - it’s an op-amp with gain | | 28

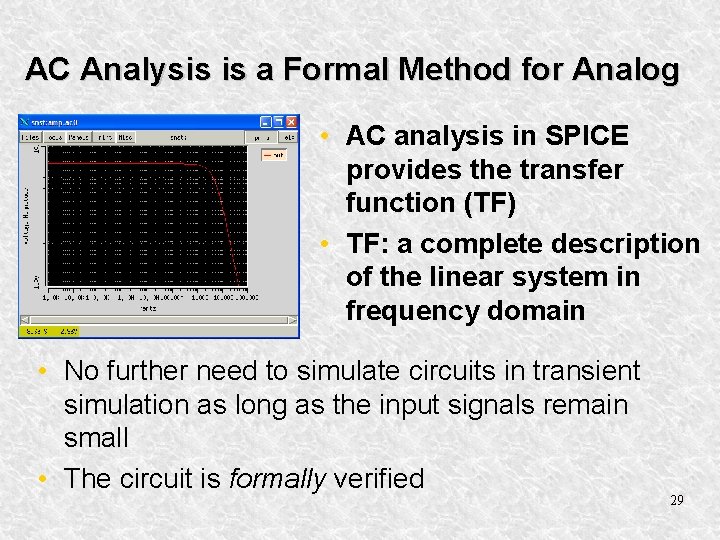

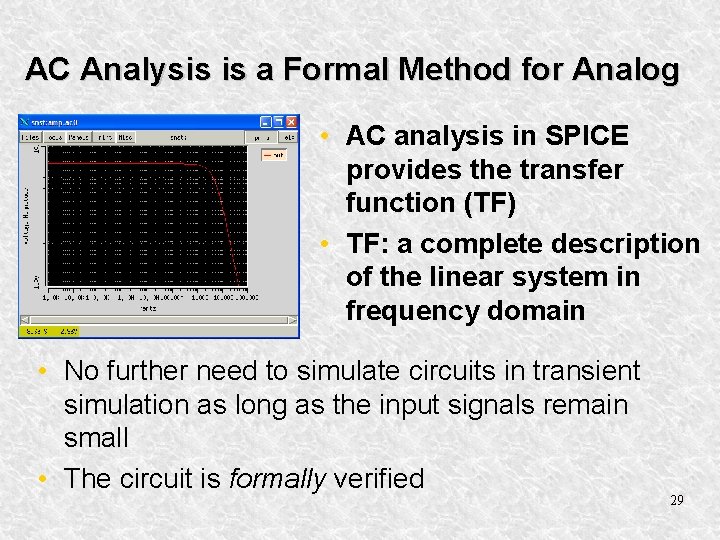

AC Analysis is a Formal Method for Analog • AC analysis in SPICE provides the transfer function (TF) • TF: a complete description of the linear system in frequency domain • No further need to simulate circuits in transient simulation as long as the input signals remain small • The circuit is formally verified 29

Non-linear Domains • The “formal” techniques for analog circuits work very well in linear domains • Many (most) circuits are not linear in the voltage or current domains • PLLs are obviously very non-linear in V • All the simulator AC analysis tools work in V or I • This seems to imply they are not useful 30 for most circuits!

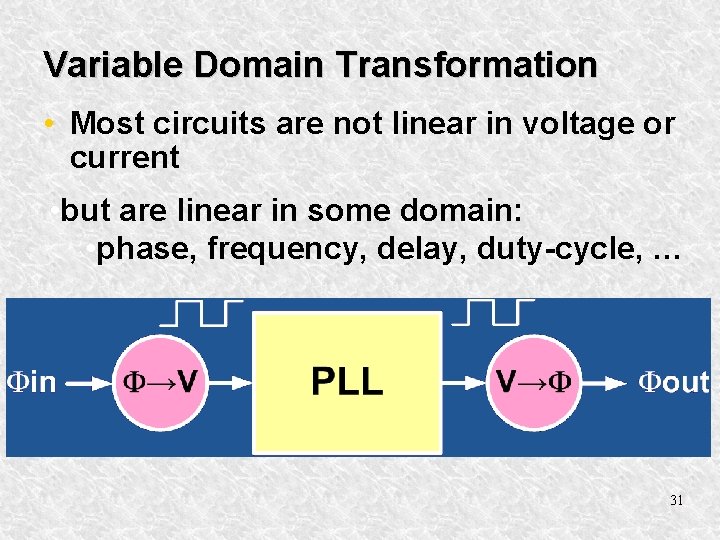

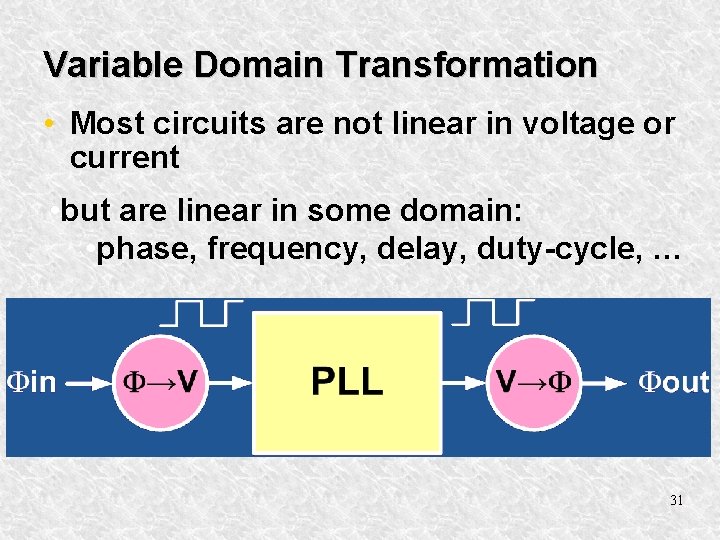

Variable Domain Transformation • Most circuits are not linear in voltage or current • but are linear in some domain: • phase, frequency, delay, duty-cycle, … 31

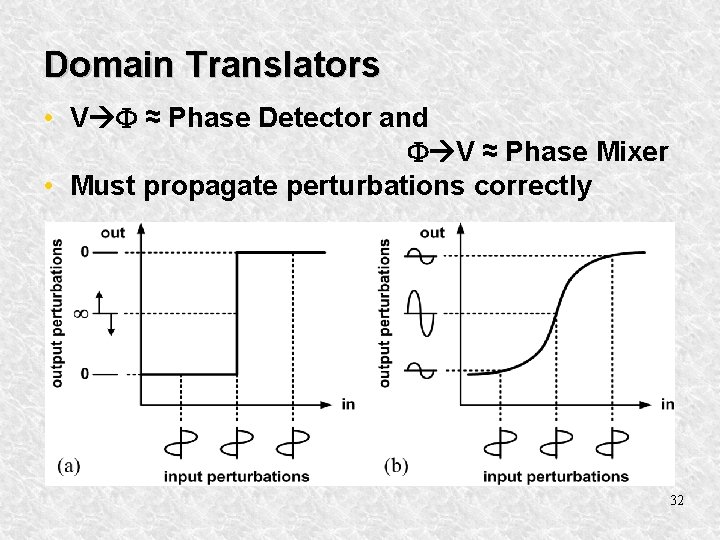

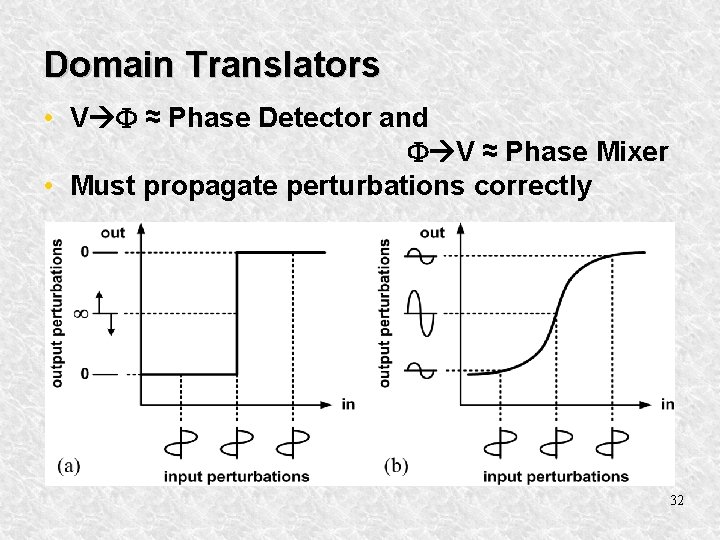

Domain Translators • V ≈ Phase Detector and V ≈ Phase Mixer • Must propagate perturbations correctly 32

Domain Transformation gives “FV” • Use domain translators to map the linear domain to V or I • Verilog-A is a good vehicle for developing translators • Perform analysis in this domain using AC analysis tools • Use inverse translator to map back to original linear domain for results • All the benefits of linearity together with all the benefits of V/I AC simulation techniques • A “classic” analog approach to Formal 33 Verification

Limitation of Linear Analysis • Linear methods verify only LOCAL properties • Most circuits are nonlinear • Must make sure that the circuit does operate at the assumed OP 34

Bugs in Analog/MS Systems • Parametric bugs • E. g. Jitter too high • The usual focus of designers effort • Requires better models and simulation techniques for improvement • Functional bugs • E. g. PLL doesn’t lock! • Very difficult to find due to long simulation times and large spaces 35

An Example from the “Real world” • The example is extracted from an actual design failure • Some issues were only found in measurement of fabricated test chips • The design was validated as well as any analog designs are in practice today • The scale of the example is reduced to make it approachable from an academic perspective but all of the issues are still present 36

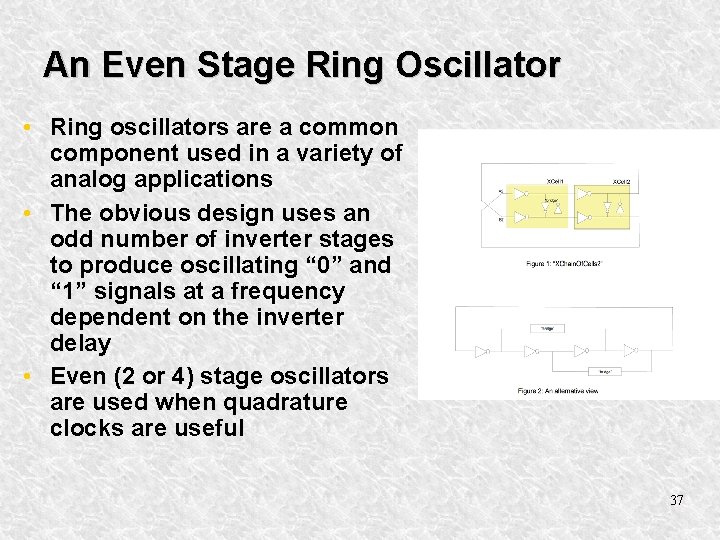

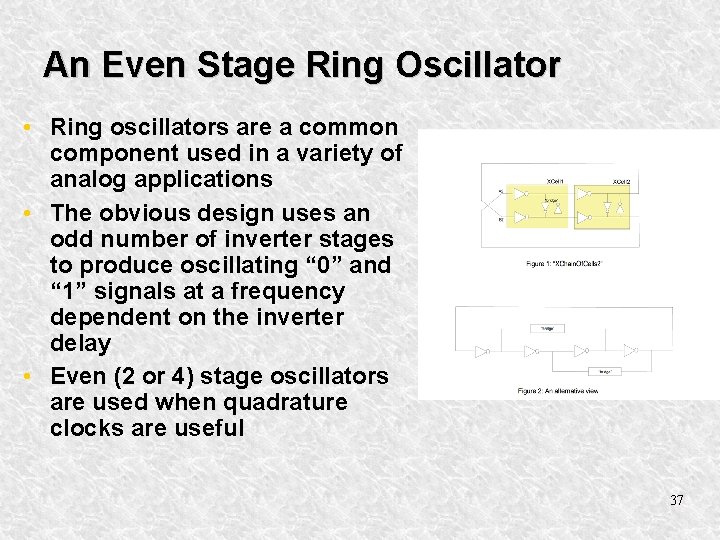

An Even Stage Ring Oscillator • Ring oscillators are a common component used in a variety of analog applications • The obvious design uses an odd number of inverter stages to produce oscillating “ 0” and “ 1” signals at a frequency dependent on the inverter delay • Even (2 or 4) stage oscillators are used when quadrature clocks are useful 37

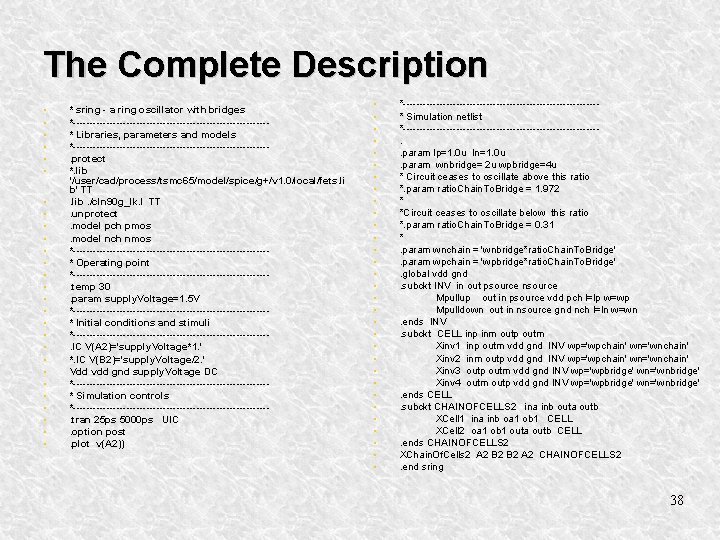

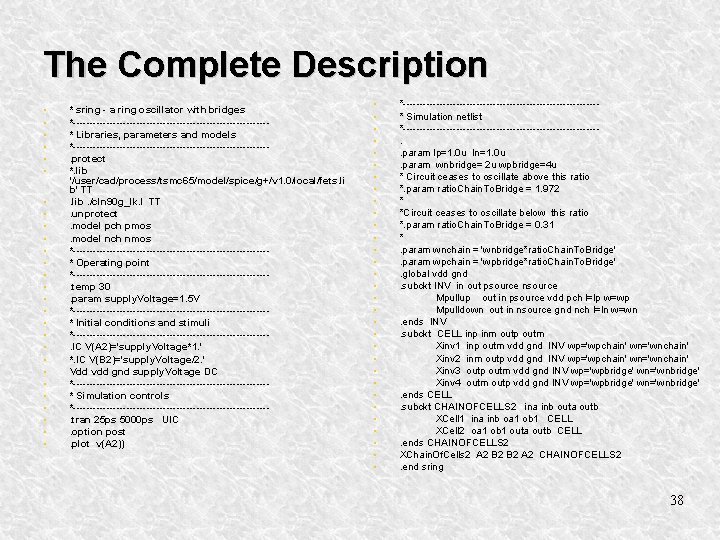

The Complete Description • • • • • • • * sring - a ring oscillator with bridges *-----------------------------* Libraries, parameters and models *-----------------------------. protect *. lib '/user/cad/process/tsmc 65/model/spice/g+/v 1. 0/local/fets. li b' TT. lib. /cln 90 g_lk. l TT. unprotect. model pch pmos. model nch nmos *-----------------------------* Operating point *-----------------------------. temp 30. param supply. Voltage=1. 5 V *-----------------------------* Initial conditions and stimuli *-----------------------------. IC V(A 2)='supply. Voltage*1. ' *. IC V(B 2)='supply. Voltage/2. ' Vdd vdd gnd supply. Voltage DC *-----------------------------* Simulation controls *-----------------------------. tran 25 ps 5000 ps UIC. option post. plot v(A 2)) • • • • • • • • *-----------------------------* Simulation netlist *-----------------------------. . param lp=1. 0 u ln=1. 0 u. param wnbridge= 2 u wpbridge=4 u * Circuit ceases to oscillate above this ratio *. param ratio. Chain. To. Bridge = 1. 972 * *Circuit ceases to oscillate below this ratio *. param ratio. Chain. To. Bridge = 0. 31 *. param wnchain = 'wnbridge*ratio. Chain. To. Bridge'. param wpchain = 'wpbridge*ratio. Chain. To. Bridge'. global vdd gnd. subckt INV in out psource nsource Mpullup out in psource vdd pch l=lp w=wp Mpulldown out in nsource gnd nch l=ln w=wn. ends INV. subckt CELL inp inm outp outm Xinv 1 inp outm vdd gnd INV wp='wpchain' wn='wnchain' Xinv 2 inm outp vdd gnd INV wp='wpchain' wn='wnchain' Xinv 3 outp outm vdd gnd INV wp='wpbridge' wn='wnbridge' Xinv 4 outm outp vdd gnd INV wp='wpbridge' wn='wnbridge'. ends CELL. subckt CHAINOFCELLS 2 ina inb outa outb XCell 1 ina inb oa 1 ob 1 CELL XCell 2 oa 1 ob 1 outa outb CELL. ends CHAINOFCELLS 2 XChain. Of. Cells 2 A 2 B 2 A 2 CHAINOFCELLS 2. end sring 38

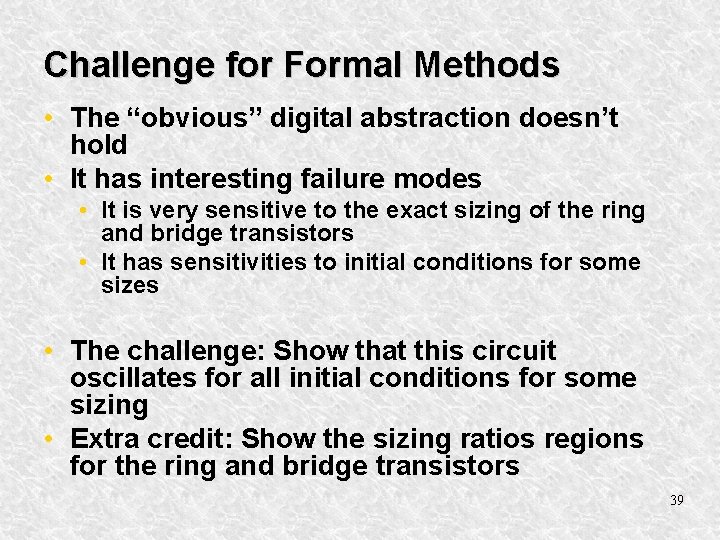

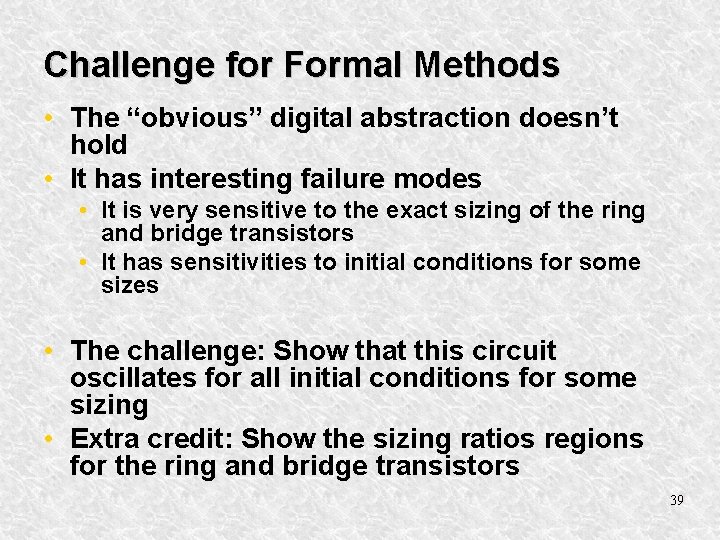

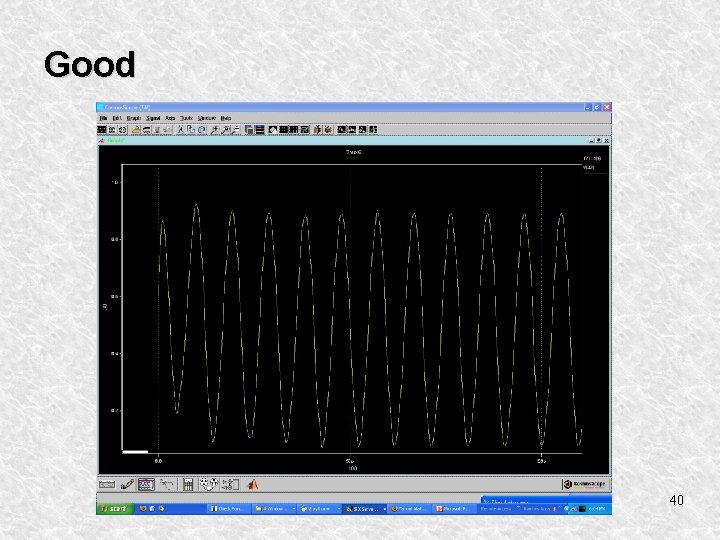

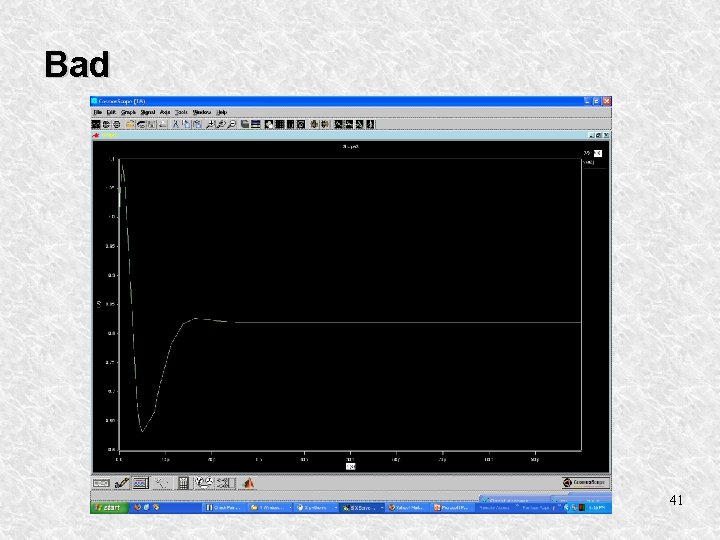

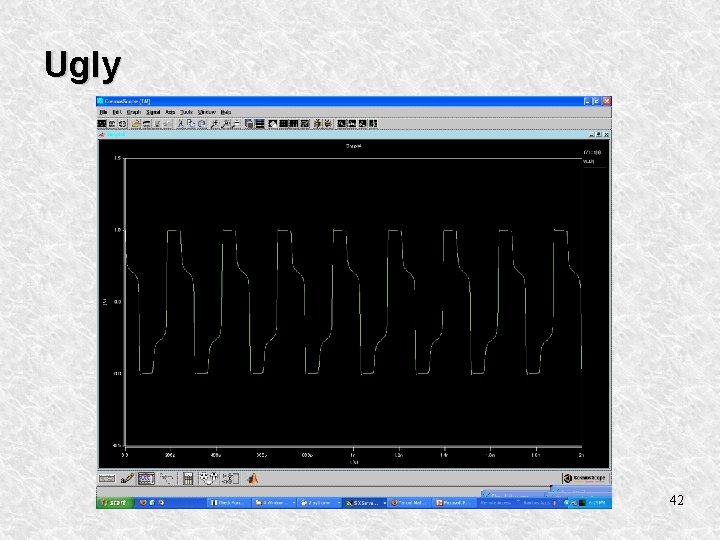

Challenge for Formal Methods • The “obvious” digital abstraction doesn’t hold • It has interesting failure modes • It is very sensitive to the exact sizing of the ring and bridge transistors • It has sensitivities to initial conditions for some sizes • The challenge: Show that this circuit oscillates for all initial conditions for some sizing • Extra credit: Show the sizing ratios regions for the ring and bridge transistors 39

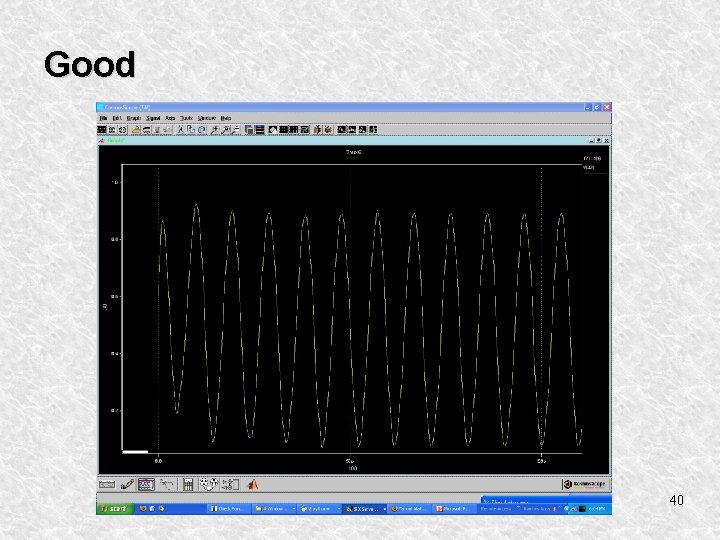

Good 40

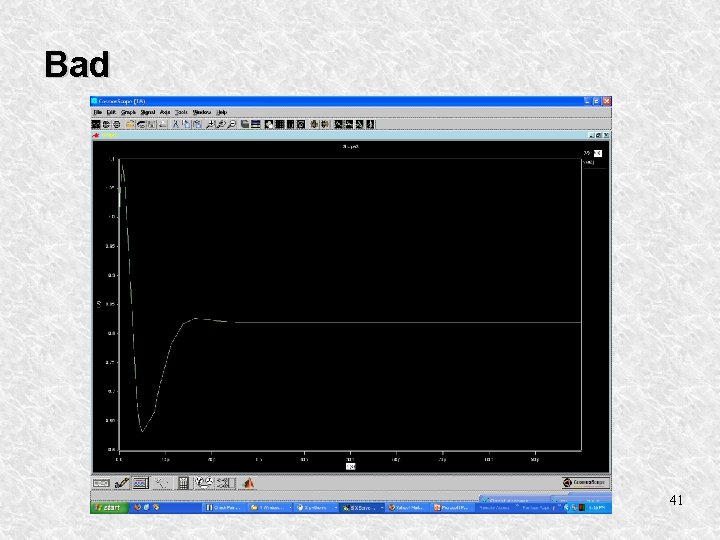

Bad 41

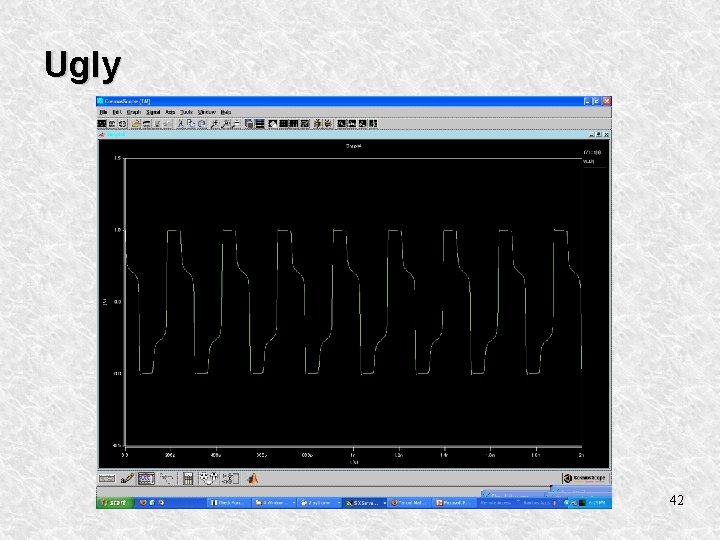

Ugly 42

Some Formal Approaches • The ESRO example has been tackled by a number of different groups • Methods used differ dramatically • Recent publication in FAC 08 and surrounding conferences • Following section gives an overview of a variety of approaches to this problem and some other noteworthy approaches on a similar scale 43

Stability analysis • UBC • “Pencil and paper” approach • Use monotonicity of fundamental components to find DC equilibria, VT derivative to analyse stability • Unstable => no DC steady state => no lock up • GLSVLSI 2008 44

i. Spice • CBL • Formulate example as an SMT problem using arithmetic intervals as underlying theory • Proves properties based on DC, Transient and PSS simulations • Shows regions of stability • FAC 2008 45

Discrete Abstraction • University of Frankfurt • Divide continuous space into discrete regions for model checking • Analog specification language • DATE 08 46

Petri Net Models • University of Utah • Translating AMS circuits into LHPN • Using this model as a basis for both BDD and SMT model checking • FAC 08 47

Hybrid Automata • Verimag • Using dense time automata to model behaviors of analog circuits • Analog assertions and monitors • FMCAD 04, FAC 08 48

Reachability Analysis • CMU • Forward and backward reachability analysis on overapproximated partitions • DATE 06 49

Bond Graph Abstraction • Concordia • Abstract the properties of analog circuits into a representation based on Bond Graphs • Constraint solving to reason about safety and reachability properties • FAC 08 50

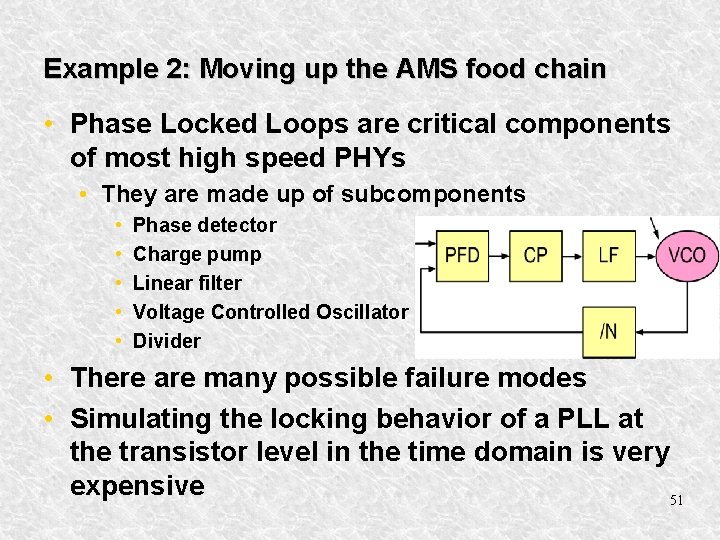

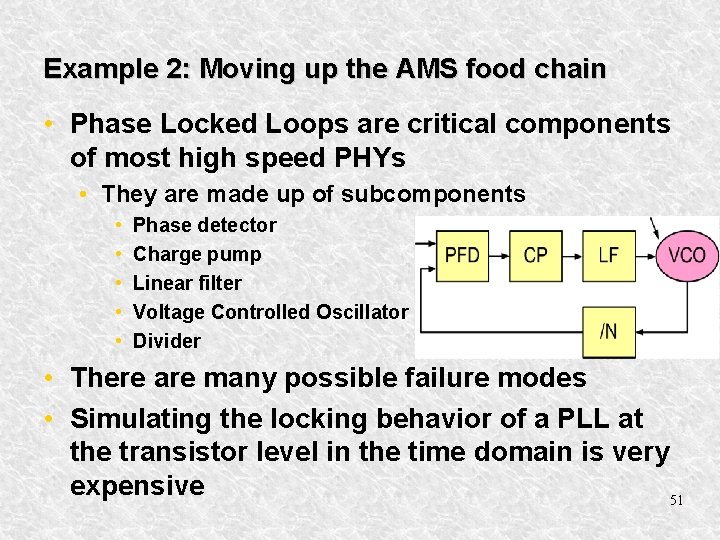

Example 2: Moving up the AMS food chain • Phase Locked Loops are critical components of most high speed PHYs • They are made up of subcomponents • • • Phase detector Charge pump Linear filter Voltage Controlled Oscillator Divider • There are many possible failure modes • Simulating the locking behavior of a PLL at the transistor level in the time domain is very expensive 51

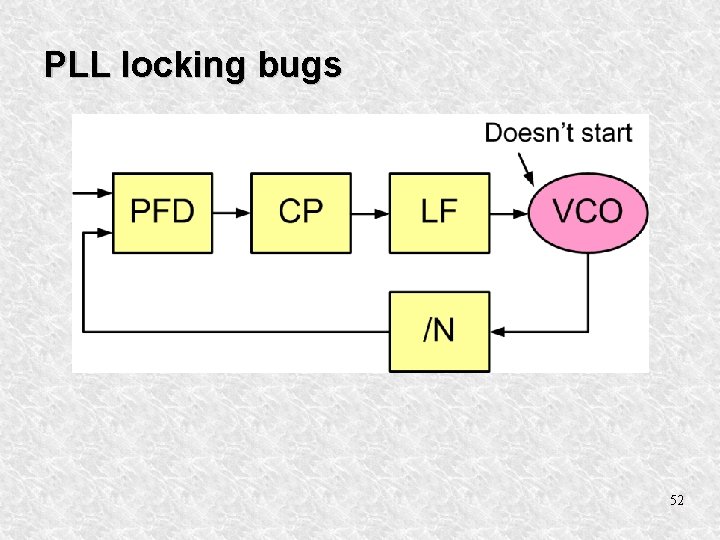

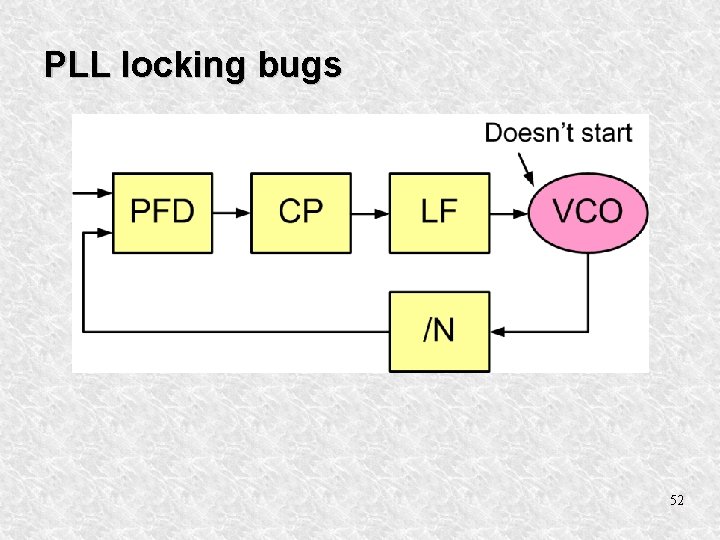

PLL locking bugs 52

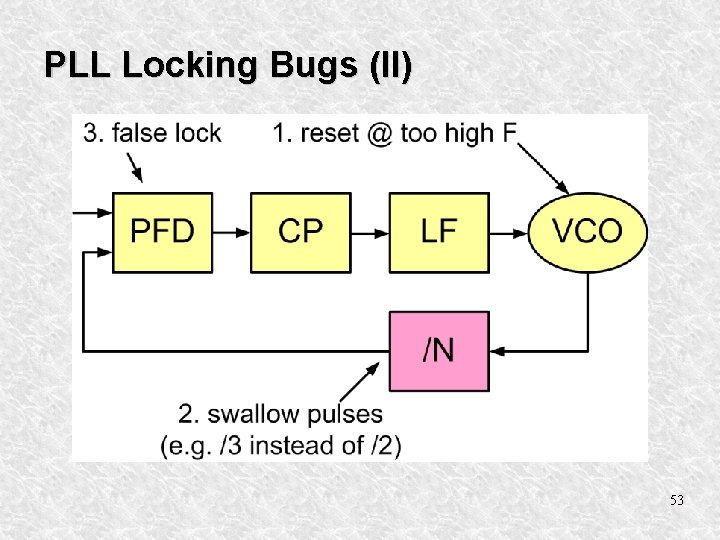

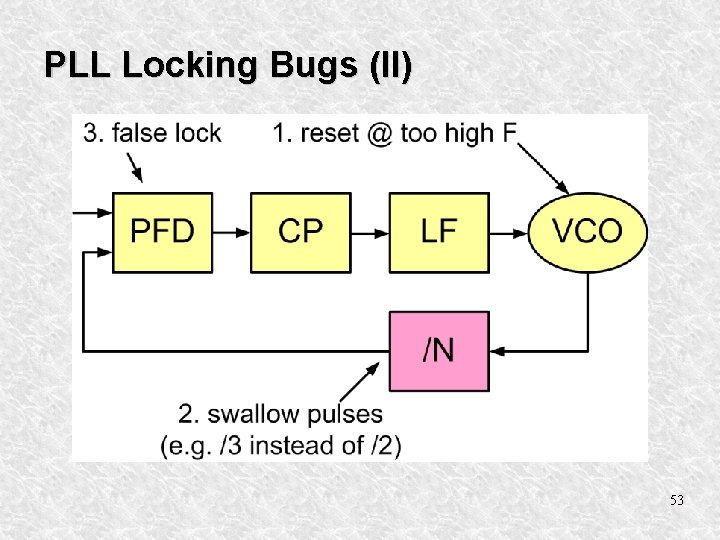

PLL Locking Bugs (II) 53

PLL Locking Bugs (IV) 54

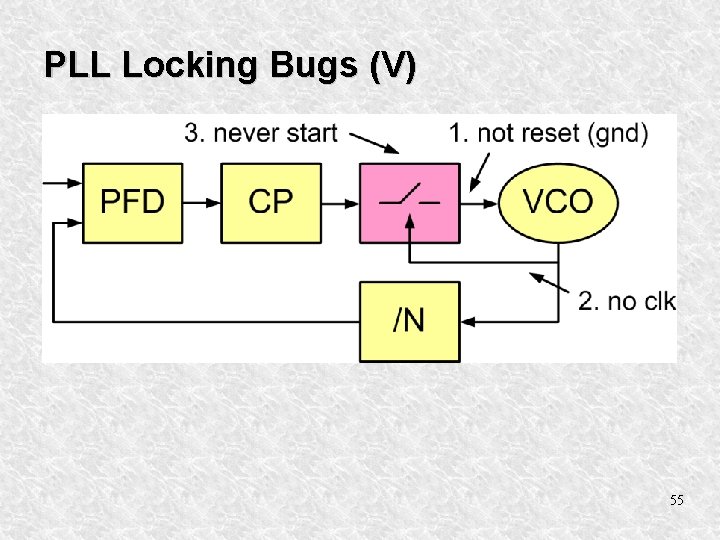

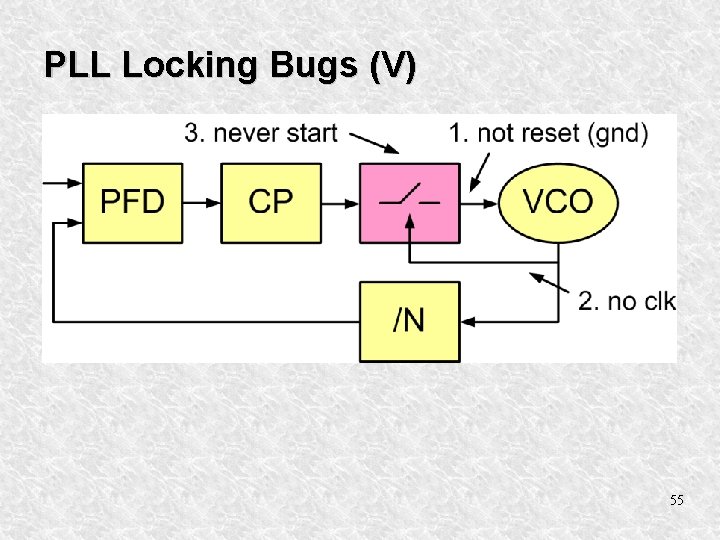

PLL Locking Bugs (V) 55

A Verification Nightmare • Individual components can be wrong • Individual components can be fine but assumptions between components can be wrong • Most of these issues are not visible if we assume “correct initialization” i. e. we start simulation from a locked state, as we do for most parametric simulation • It takes a very (very, …) long time to simulate, using sufficiently accurate models, from any arbitrary initial state to reach lock • Bugs like these make it through to production 56

Open Analog Problems (A Challenge) • Avoiding transient simulation • Establishing that operating point assumptions are valid • Establishing that all initial conditions result in correct behavior • Dealing with non-linearity • Good candidates for FM approaches 57

Conclusions and Future Work • Analog and digital are different • Different mindsets, different tools, different problems • There are problems in the analog space that are really looking for solutions • Different points of view yield valuable approaches • The FV community is just beginning to come to grips with this problem =>Lots of interesting opportunities • We can provide “realistic” examples to interested parties • Some are small, representative and tractable • If any one really wants it, we have a software → digital → analog → physics problem (ms → ns → ps → fs) in a 20 GB SERDES system 58

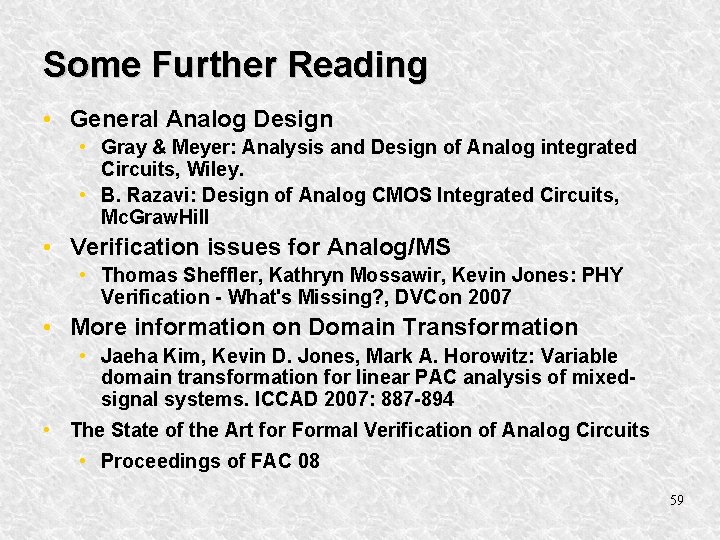

Some Further Reading • General Analog Design • Gray & Meyer: Analysis and Design of Analog integrated Circuits, Wiley. • B. Razavi: Design of Analog CMOS Integrated Circuits, Mc. Graw. Hill • Verification issues for Analog/MS • Thomas Sheffler, Kathryn Mossawir, Kevin Jones: PHY Verification - What's Missing? , DVCon 2007 • More information on Domain Transformation • Jaeha Kim, Kevin D. Jones, Mark A. Horowitz: Variable domain transformation for linear PAC analysis of mixedsignal systems. ICCAD 2007: 887 -894 • The State of the Art for Formal Verification of Analog Circuits • Proceedings of FAC 08 59