FPCCD VTX Overview Yasuhiro Sugimoto KEK 20141218 JSPS

- Slides: 14

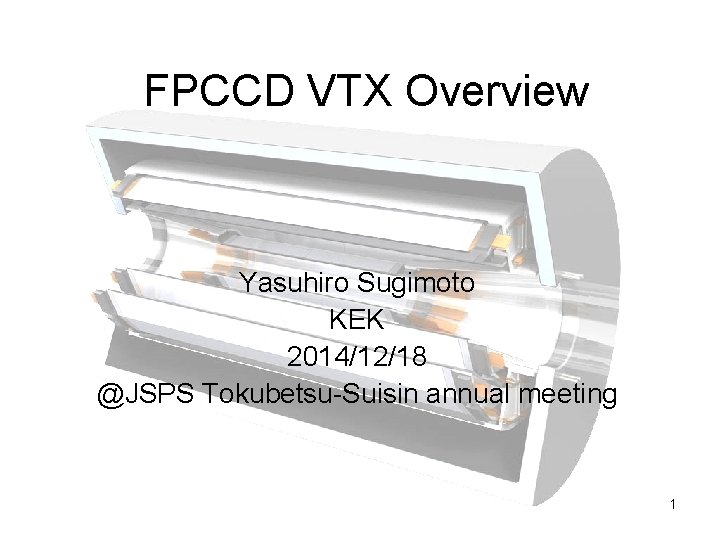

FPCCD VTX Overview Yasuhiro Sugimoto KEK 2014/12/18 @JSPS Tokubetsu-Suisin annual meeting 1

Outline • • • FPCCD sensor R&D Beam test Readout electronics CO 2 cooling FY 2015 plan 2

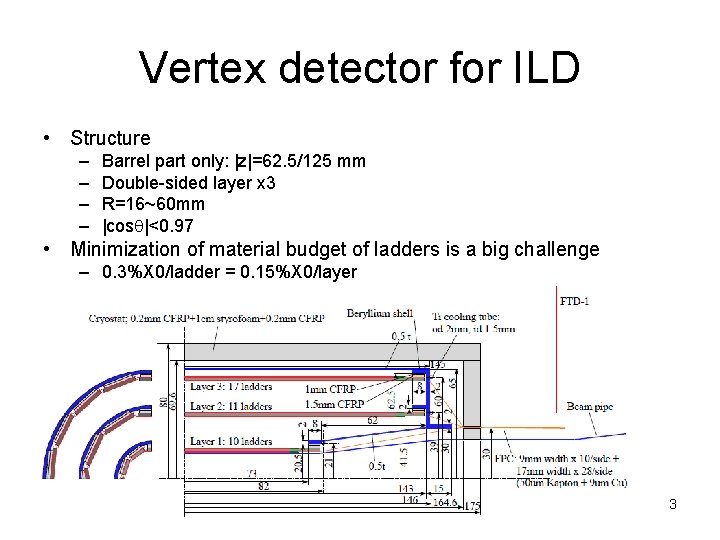

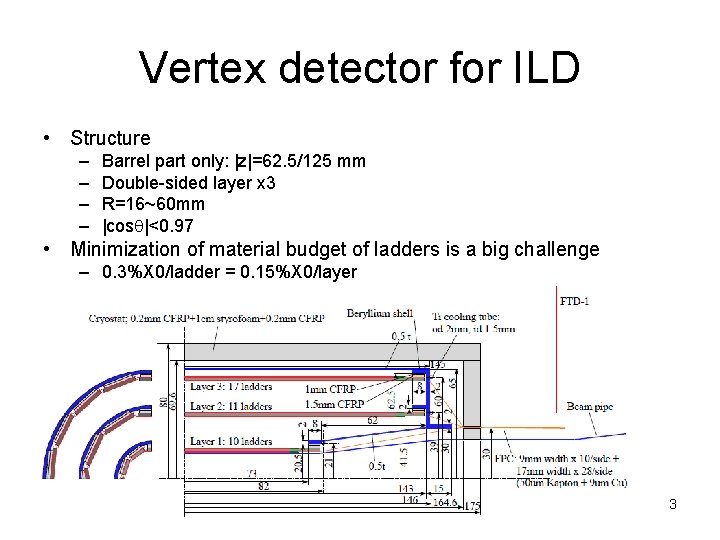

Vertex detector for ILD • Structure – – Barrel part only: |z|=62. 5/125 mm Double-sided layer x 3 R=16~60 mm |cosq|<0. 97 • Minimization of material budget of ladders is a big challenge – 0. 3%X 0/ladder = 0. 15%X 0/layer 3

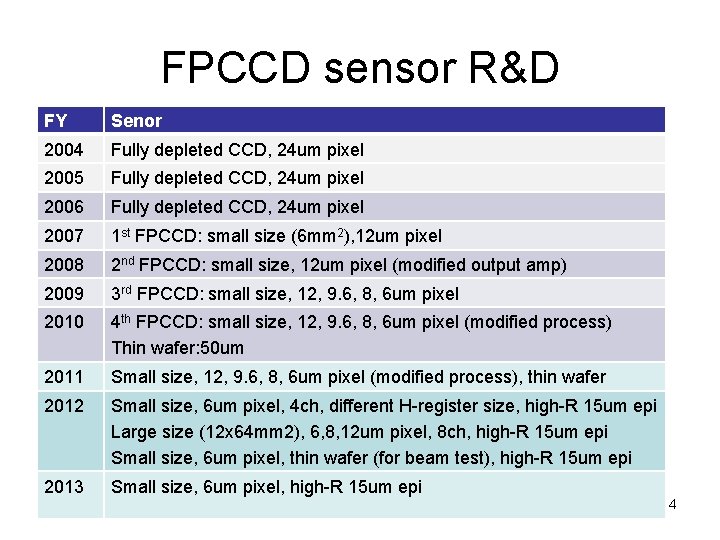

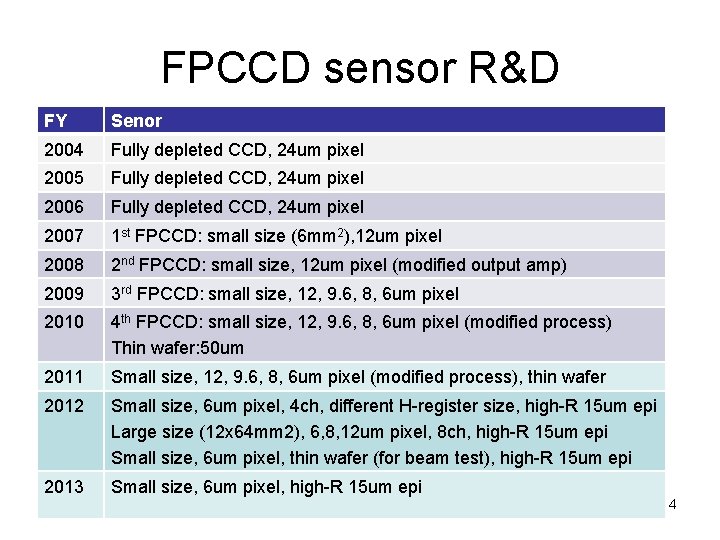

FPCCD sensor R&D FY Senor 2004 Fully depleted CCD, 24 um pixel 2005 Fully depleted CCD, 24 um pixel 2006 Fully depleted CCD, 24 um pixel 2007 1 st FPCCD: small size (6 mm 2), 12 um pixel 2008 2 nd FPCCD: small size, 12 um pixel (modified output amp) 2009 3 rd FPCCD: small size, 12, 9. 6, 8, 6 um pixel 2010 4 th FPCCD: small size, 12, 9. 6, 8, 6 um pixel (modified process) Thin wafer: 50 um 2011 Small size, 12, 9. 6, 8, 6 um pixel (modified process), thin wafer 2012 Small size, 6 um pixel, 4 ch, different H-register size, high-R 15 um epi Large size (12 x 64 mm 2), 6, 8, 12 um pixel, 8 ch, high-R 15 um epi Small size, 6 um pixel, thin wafer (for beam test), high-R 15 um epi 2013 Small size, 6 um pixel, high-R 15 um epi 4

FPCCD sensor R&D • Original plan for sensor R&D in FY 2014 – Small size 5 um pixel • Achievement – It was found that developing 5 um pixel CCD is difficult for HPK • Too big technical challenge which requires cost and manpower – Packaged prototypes with mixed size pixel (12, 9. 6, 8, 6 um) and high-R 15 um epi: Same format as FY 2011 small prototype but with different epitaxial layer 5

FPCCD sensor R&D • Test of sensors using beta/X-ray source – Systematic study of FPCCD property is mandatory • Dark current as a function of temperature / pixelsize / irradiation • Energy resolution for 5. 9 ke. V X-ray • Charge transfer inefficiency as a function of various parameters • etc. – Some of the achievements will be reported by Tino and Ito-san 6

Beam test • Neutron damage test at CYRIC – Two CCD sample were irradiated by neutron beam at CYRIC of Tohoku University – Detail will be reported by Ishikawa-san and Ito-san • MIP beam test with ~1 Ge. V/c pion at J-PARC has not been done because the hadron-hall is not available yet • Design of electron test beam line at KEK AR (South experimental hall) up to ~4. 5 Ge. V is being carried out 7

Readout electronics • Development of new clock driver and interface board – 3 -level clock to reduce power consumption – Interface board for the new clock drivers – Detail will be reported later 8

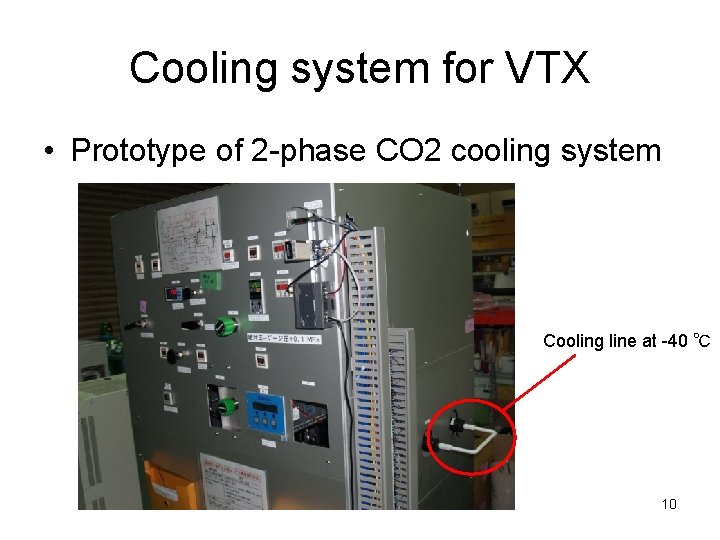

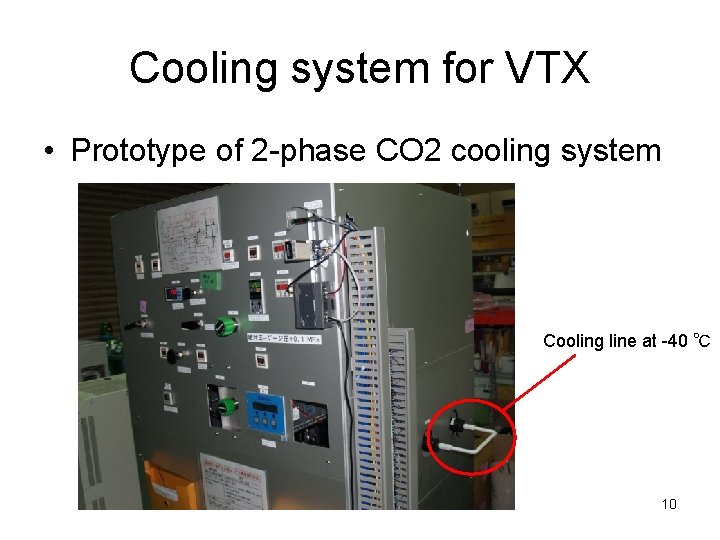

Cooling system for VTX • R&D of 2 -phase CO 2 cooling is being carried out for FPCCD VTX (and TPC) using another funding • A prototype of circulating cooling system using a gas compressor has been constructed – Cooling temperature: between − 40℃ and +15℃ – The system has been tested, and we demonstrated that it can achieve the design cooling temperature 9

Cooling system for VTX • Prototype of 2 -phase CO 2 cooling system Cooling line at -40 ℃ 10

FY 2015 plan (tentative) • FPCCD sensors – Small prototypes with same format as before – Systematic study of FPCCD property should be continued • Ladder R&D – Mechanical ladder structure • Original idea: Carbon foam (RVC) core sandwiched by CFRP sheets Risk of carbon powder • All CFRP structure seems better • Electronics R&D – Readout speed of 10 Mpix/s • So far, stable readout of 2. 5 Mpix/s (25 MHz clock) has been achieved • Our goal is 10 Mpix/s • We have to find out the problem, and make improved readout system – Bare chip test board with similar structure to ladder • CFRP base + Kapton FPC + bare chips 11

Backup slides 12

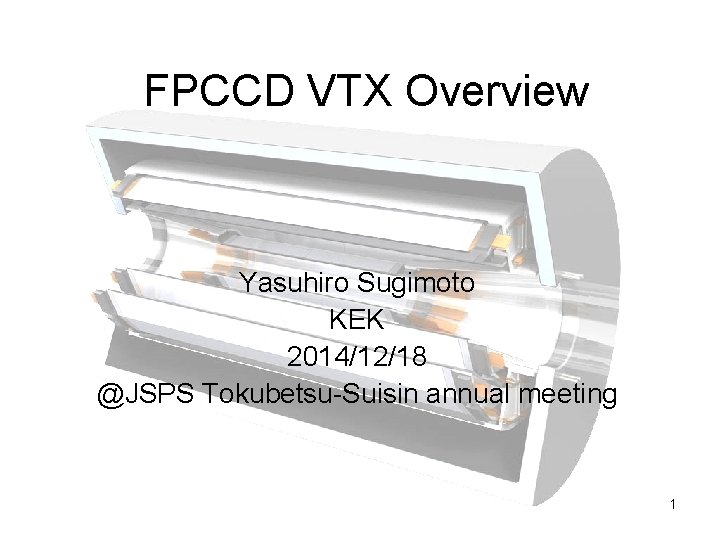

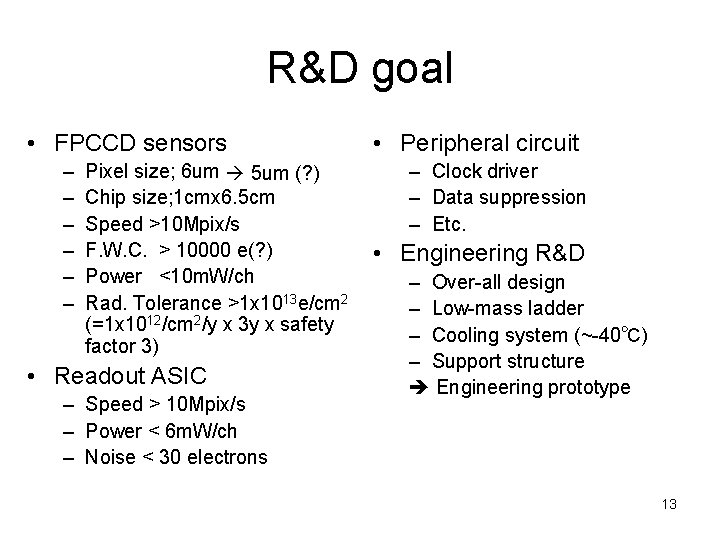

R&D goal • FPCCD sensors – – – Pixel size; 6 um 5 um (? ) Chip size; 1 cmx 6. 5 cm Speed >10 Mpix/s F. W. C. > 10000 e(? ) Power <10 m. W/ch Rad. Tolerance >1 x 1013 e/cm 2 (=1 x 1012/cm 2/y x 3 y x safety factor 3) • Readout ASIC – Speed > 10 Mpix/s – Power < 6 m. W/ch – Noise < 30 electrons • Peripheral circuit – Clock driver – Data suppression – Etc. • Engineering R&D – Over-all design – Low-mass ladder – Cooling system (~-40℃) – Support structure Engineering prototype 13

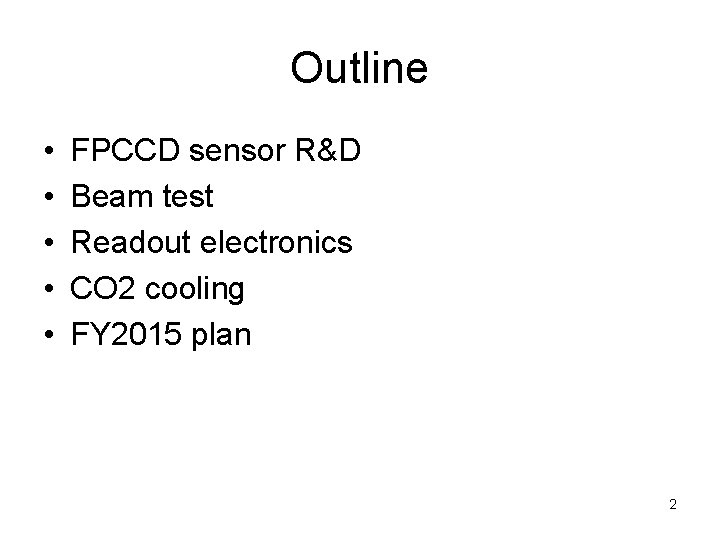

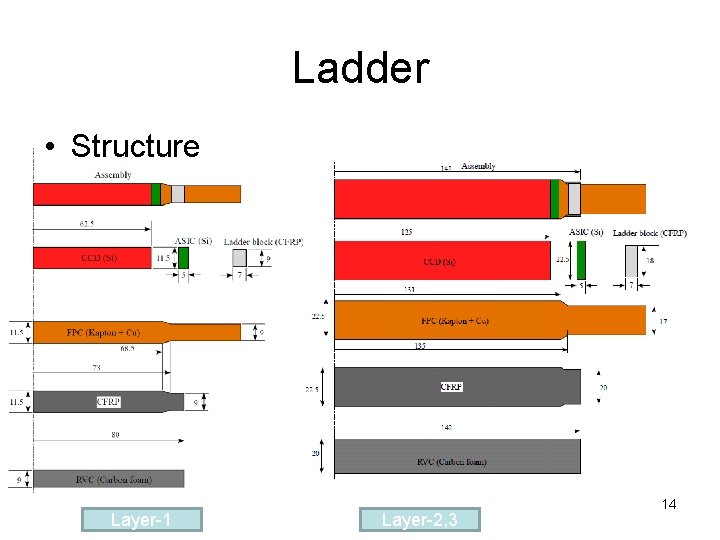

Ladder • Structure Layer-1 Layer-2, 3 14