Final Workshop of CDC 2002 2007 Tallinn Brotherhood

Final Workshop of CDC 2002 -2007 Tallinn, Brotherhood of the Blackheads, 21 – 22 January 2008 A multi-layer research and training platform for system-on-chip testing: Hardware, Software and Web Interface Artur Jutman Department of Computer Engineering Tallinn. Dept. University of Technology Tallinn University Estonia of Technology Estonia

A multi-layer research and training platform for system-on-chip testing Outline üIntroduction and motivation üDifferent layers of the platform üHW tools üPC-based tools üWeb interface üE-Learning tools üConclusions and discussion 2

A multi-layer research and training platform for system-on-chip testing Motivation üCutting Edge Research −Needs custom developed algorithms and/or tools üPh. D Students −Need to run their experiments üUndergraduate Students −Need introduction to the topic üDepartment −Needs training materials and research 3

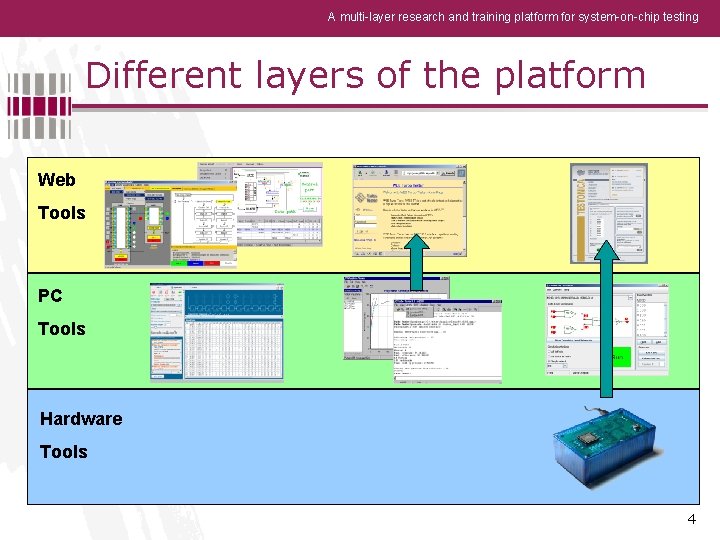

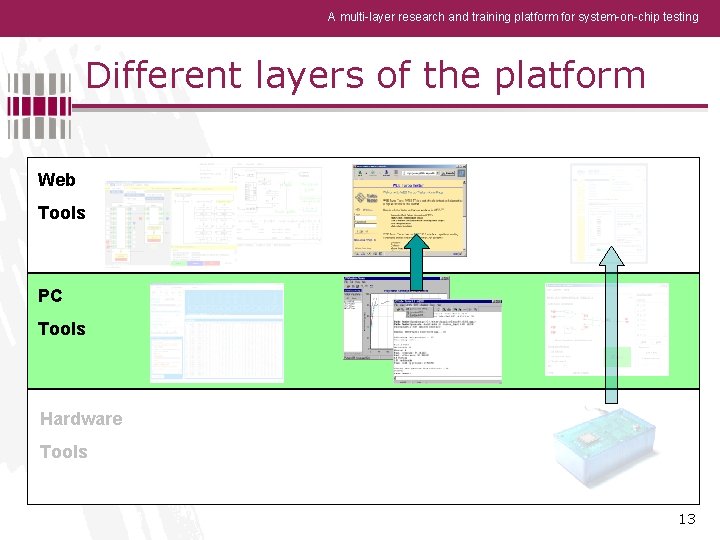

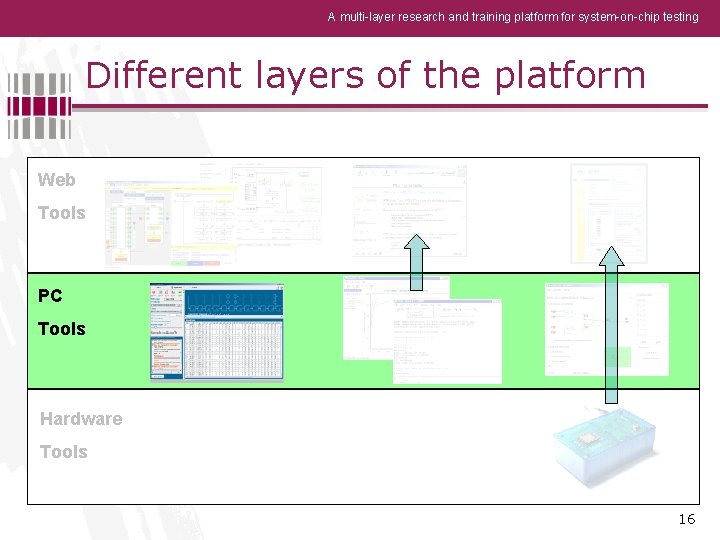

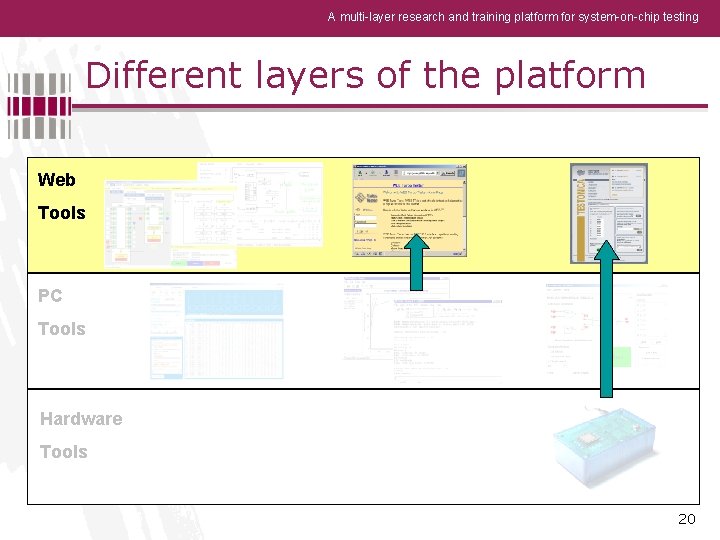

A multi-layer research and training platform for system-on-chip testing Different layers of the platform Web Tools PC Tools Hardware Tools 4

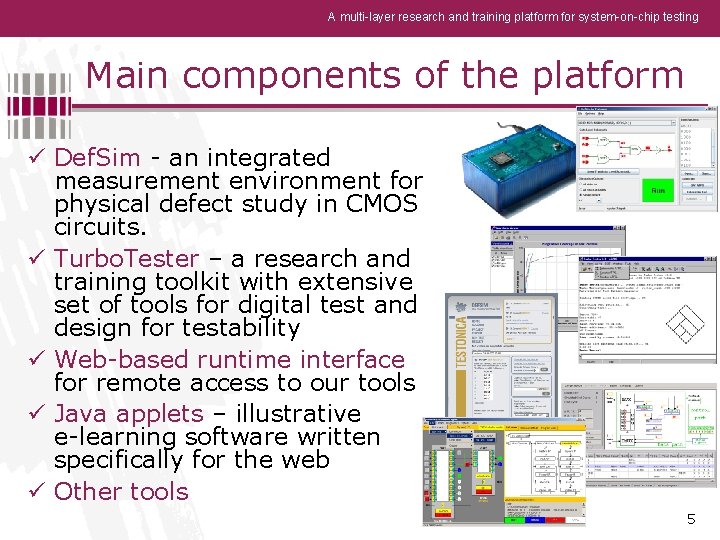

A multi-layer research and training platform for system-on-chip testing Main components of the platform ü Def. Sim - an integrated measurement environment for physical defect study in CMOS circuits. ü Turbo. Tester – a research and training toolkit with extensive set of tools for digital test and design for testability ü Web-based runtime interface for remote access to our tools ü Java applets – illustrative e-learning software written specifically for the web ü Other tools 5

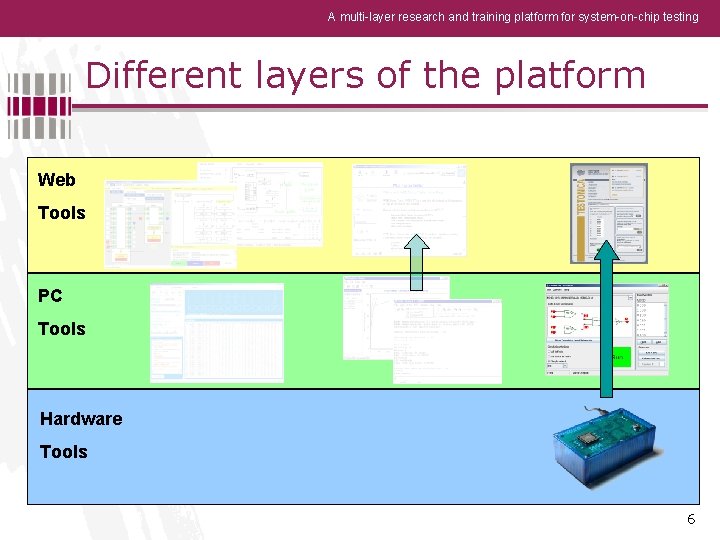

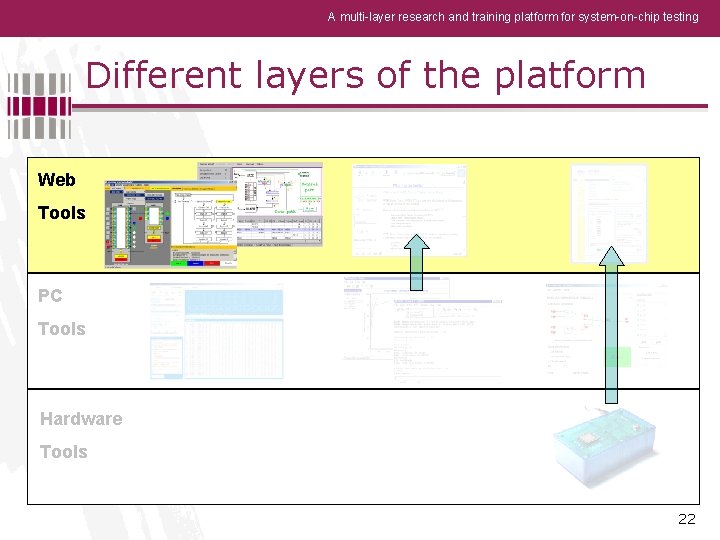

A multi-layer research and training platform for system-on-chip testing Different layers of the platform Web Tools PC Tools Hardware Tools 6

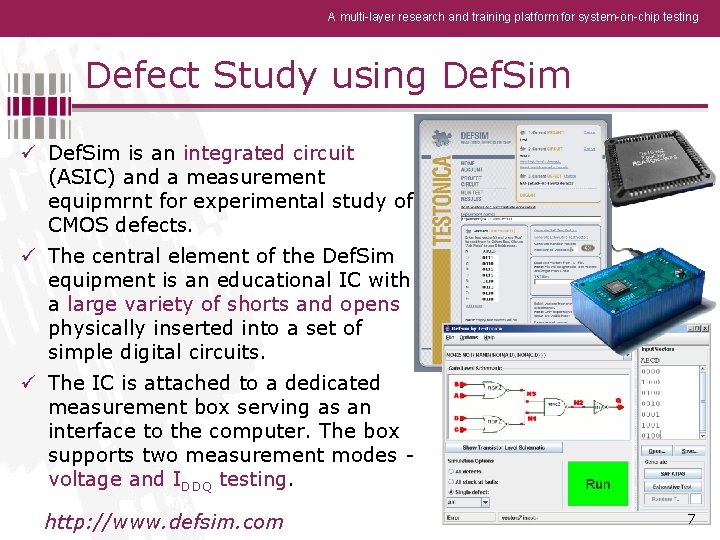

A multi-layer research and training platform for system-on-chip testing Defect Study using Def. Sim ü Def. Sim is an integrated circuit (ASIC) and a measurement equipmrnt for experimental study of CMOS defects. ü The central element of the Def. Sim equipment is an educational IC with a large variety of shorts and opens physically inserted into a set of simple digital circuits. ü The IC is attached to a dedicated measurement box serving as an interface to the computer. The box supports two measurement modes voltage and IDDQ testing. http: //www. defsim. com 7

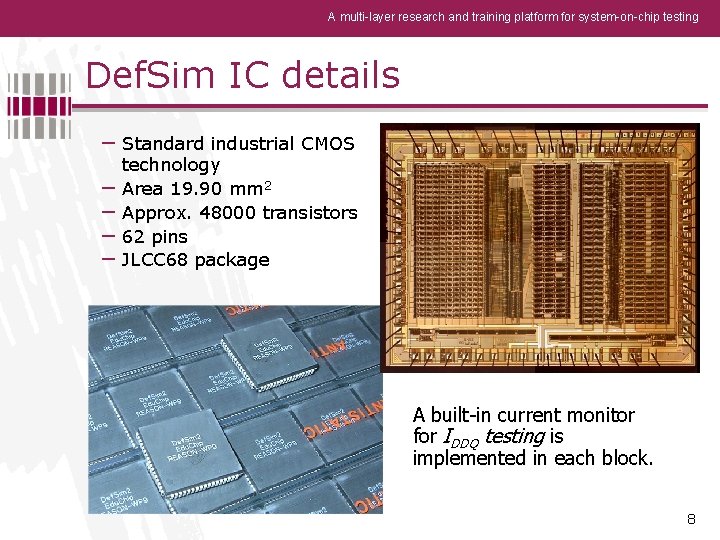

A multi-layer research and training platform for system-on-chip testing Def. Sim IC details − Standard industrial CMOS technology − Area 19. 90 mm 2 − Approx. 48000 transistors − 62 pins − JLCC 68 package A built-in current monitor for IDDQ testing is implemented in each block. 8

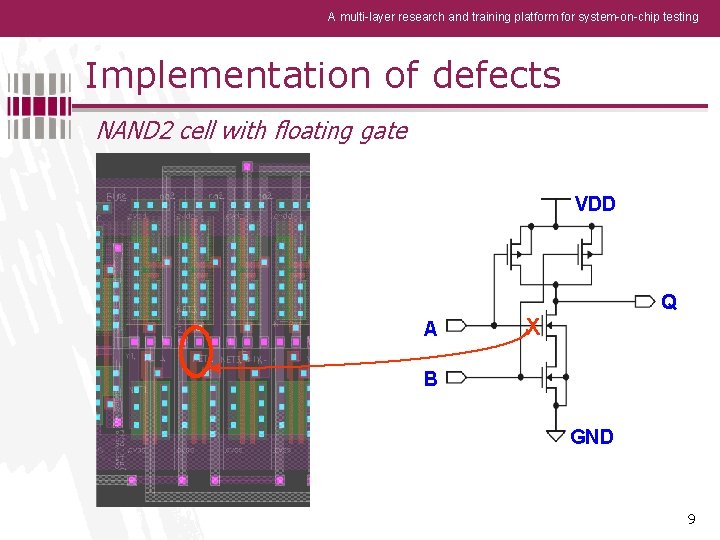

A multi-layer research and training platform for system-on-chip testing Implementation of defects NAND 2 cell with floating gate VDD A Q X B GND 9

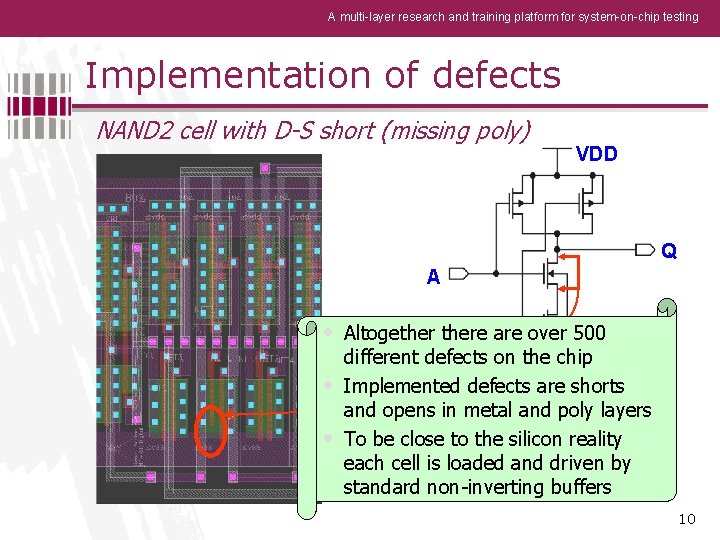

A multi-layer research and training platform for system-on-chip testing Implementation of defects NAND 2 cell with D-S short (missing poly) VDD Q A • Altogether. Bthere are over 500 • • different defects on the chip Implemented defects are GND shorts and opens in metal and poly layers To be close to the silicon reality each cell is loaded and driven by standard non-inverting buffers 10

A multi-layer research and training platform for system-on-chip testing Def. Sim in the classroom ü With Def. Sim you can ü Observe the truth table of correct circuit ü Observe the truth table of defective circuit ü Obtain defect/fault tables for all specific defects ü Define test patterns automatically or manually ü Activate IDDQ and voltage measurements ü Study behavior of bridging and open faults ü Study and compare different fault models 11

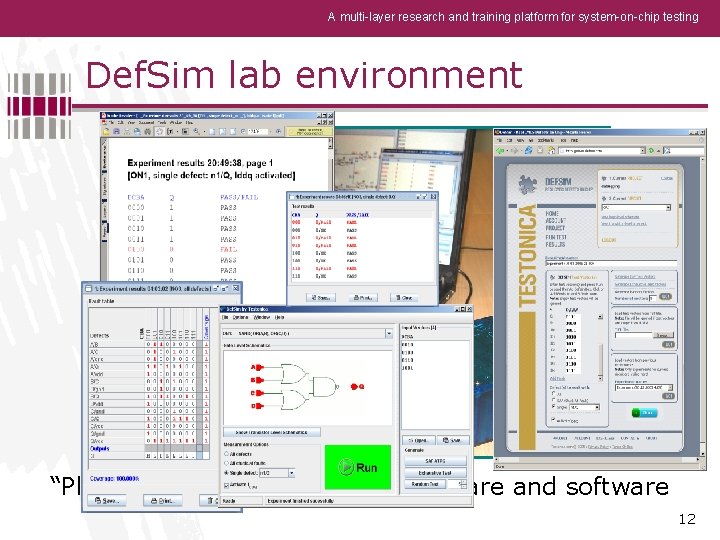

A multi-layer research and training platform for system-on-chip testing Def. Sim lab environment “Plug and Play” – dedicated hardware and software 12

A multi-layer research and training platform for system-on-chip testing Different layers of the platform Web Tools PC Tools Hardware Tools 13

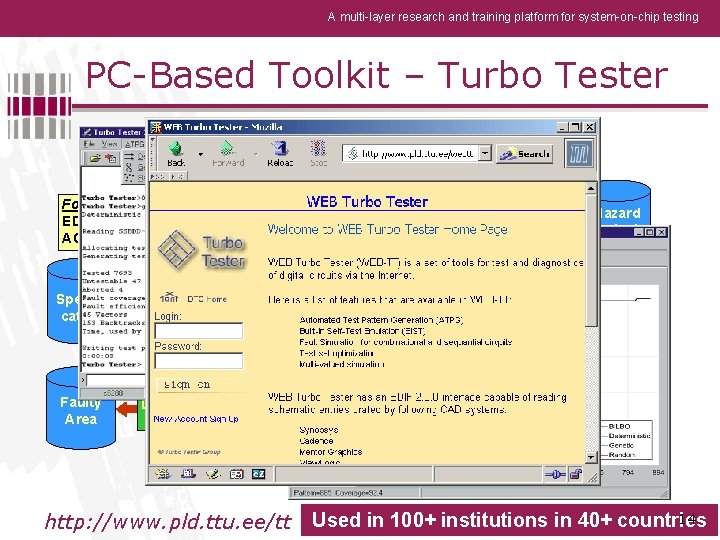

A multi-layer research and training platform for system-on-chip testing PC-Based Toolkit – Turbo Tester Formats: EDIF AGM Specification Faulty Area Levels: Gate Macro RTL Algorithms: Deterministic Random Genetic Design Circuits: Combinational Sequential Test Generators BIST Emulator Design Error Diagnosis Methods: BILBO CSTP Hybrid http: //www. pld. ttu. ee/tt Test Set Optimizer Multivalued Simulator Hazard Analysis Data Logic Simulator Fault Table Defect Library Fault models: Stuck-at faults Physical defects 14 Used in 100+ institutions in 40+ countries

A multi-layer research and training platform for system-on-chip testing Turbo Tester: Basic Facts ü Freeware ü Downloadable via the Web ü Windows, Linux, UNIX/Solaris ü EDIF design interface ü ATPGs, BIST, simulators, test compaction ü Provides homogeneous environment for research and training 15

A multi-layer research and training platform for system-on-chip testing Different layers of the platform Web Tools PC Tools Hardware Tools 16

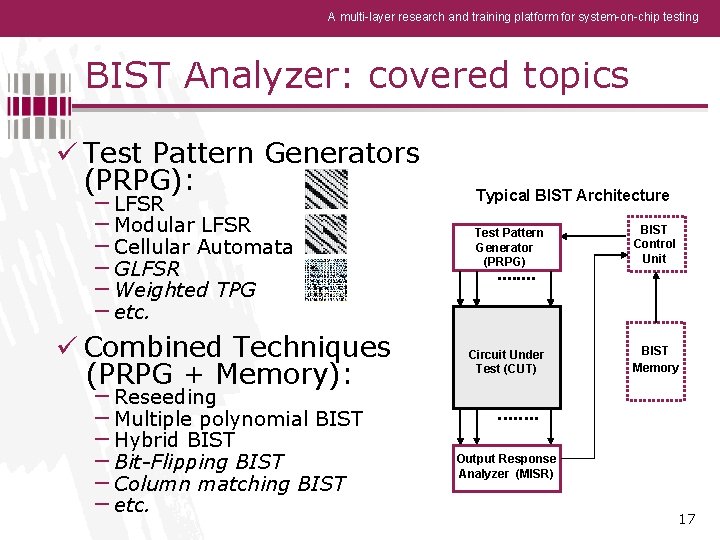

A multi-layer research and training platform for system-on-chip testing BIST Analyzer: covered topics ü Test Pattern Generators (PRPG): − LFSR − Modular LFSR − Cellular Automata − GLFSR − Weighted TPG − etc. ü Combined Techniques (PRPG + Memory): − Reseeding − Multiple polynomial BIST − Hybrid BIST − Bit-Flipping BIST − Column matching BIST − etc. Typical BIST Architecture Test Pattern Generator (PRPG) BIST Control Unit Circuit Under Test (CUT) BIST Memory . . . . Output Response Analyzer (MISR) 17

A multi-layer research and training platform for system-on-chip testing BIST Analyzer: covered topics • Embedded generators (PRPG) and their properties • PRPG optimization methodologies and algorithms • Combined BIST solutions (PRPG+memory) • Fault detection and diagnosis in BIST 18

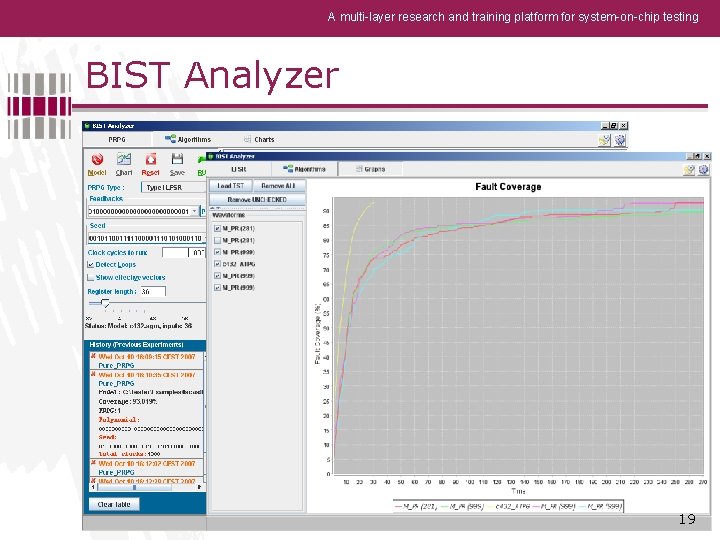

A multi-layer research and training platform for system-on-chip testing BIST Analyzer 19

A multi-layer research and training platform for system-on-chip testing Different layers of the platform Web Tools PC Tools Hardware Tools 20

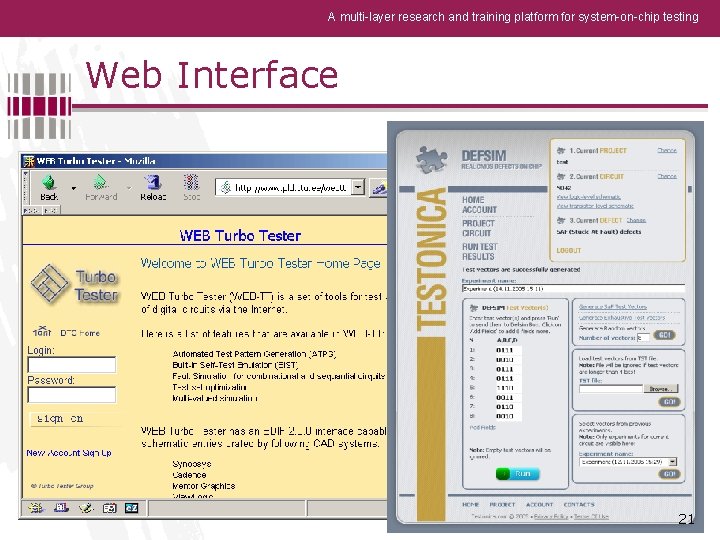

A multi-layer research and training platform for system-on-chip testing Web Interface 21

A multi-layer research and training platform for system-on-chip testing Different layers of the platform Web Tools PC Tools Hardware Tools 22

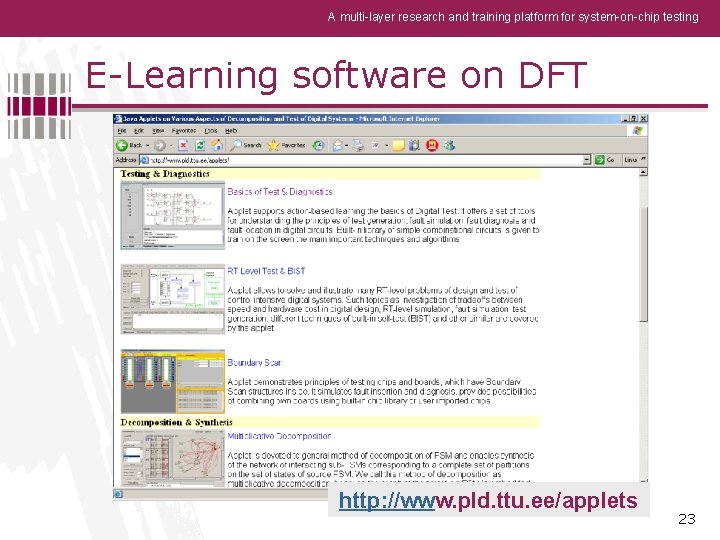

A multi-layer research and training platform for system-on-chip testing E-Learning software on DFT http: //www. pld. ttu. ee/applets 23

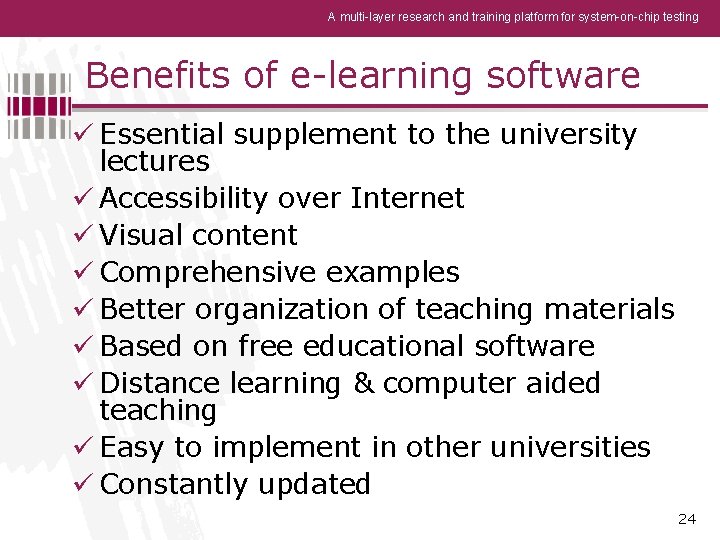

A multi-layer research and training platform for system-on-chip testing Benefits of e-learning software ü Essential supplement to the university lectures ü Accessibility over Internet ü Visual content ü Comprehensive examples ü Better organization of teaching materials ü Based on free educational software ü Distance learning & computer aided teaching ü Easy to implement in other universities ü Constantly updated 24

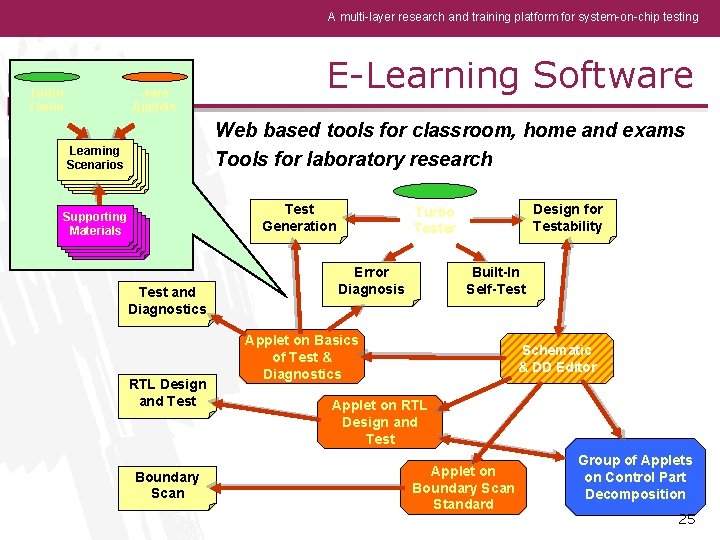

A multi-layer research and training platform for system-on-chip testing Turbo Tester Java Applets E-Learning Software Web based tools for classroom, home and exams Tools for laboratory research Scenario 12 Learning Scenario 34 Scenario Test Error Scenarios Built-Infor Design Generation Diagnosis Self-Testability Test Generation Scenario 12 Supporting Scenario 34 Scenario Test Error Materials Built-Infor Design Generation Diagnosis Self-Testability Test and Diagnostics RTL Design and Test Boundary Scan Design for Testability Turbo Tester Built-In Self-Test Error Diagnosis Applet on Basics of Test & Diagnostics Schematic & DD Editor Applet on RTL Design and Test Applet on Boundary Scan Standard Group of Applets on Control Part Decomposition 25

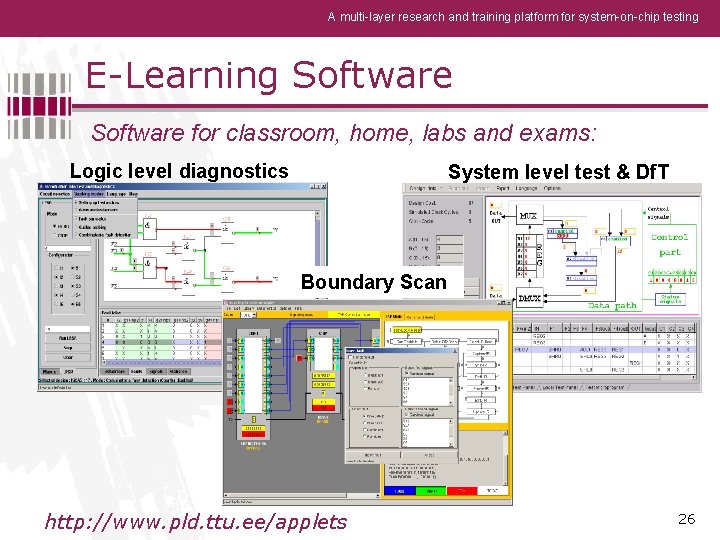

A multi-layer research and training platform for system-on-chip testing E-Learning Software for classroom, home, labs and exams: Logic level diagnostics System level test & Df. T Boundary Scan http: //www. pld. ttu. ee/applets 26

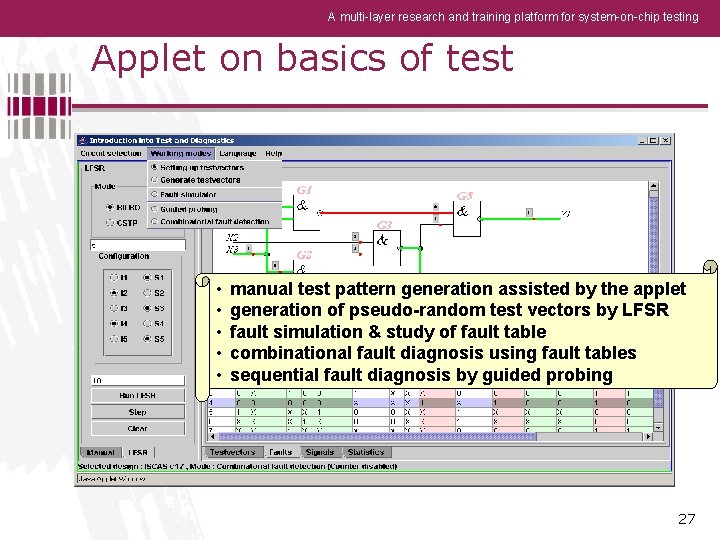

A multi-layer research and training platform for system-on-chip testing Applet on basics of test • • • manual test pattern generation assisted by the applet generation of pseudo-random test vectors by LFSR fault simulation & study of fault table combinational fault diagnosis using fault tables sequential fault diagnosis by guided probing 27

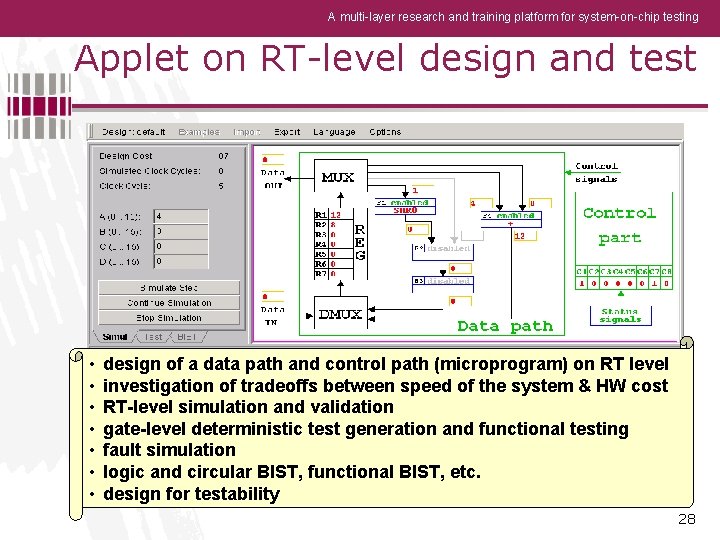

A multi-layer research and training platform for system-on-chip testing Applet on RT-level design and test • • design of a data path and control path (microprogram) on RT level investigation of tradeoffs between speed of the system & HW cost RT-level simulation and validation gate-level deterministic test generation and functional testing fault simulation logic and circular BIST, functional BIST, etc. design for testability 28

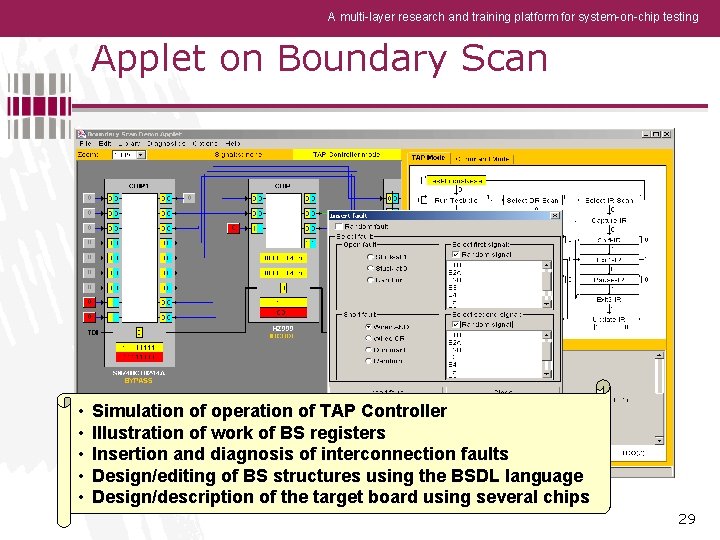

A multi-layer research and training platform for system-on-chip testing Applet on Boundary Scan • • • Simulation of operation of TAP Controller Illustration of work of BS registers Insertion and diagnosis of interconnection faults Design/editing of BS structures using the BSDL language Design/description of the target board using several chips 29

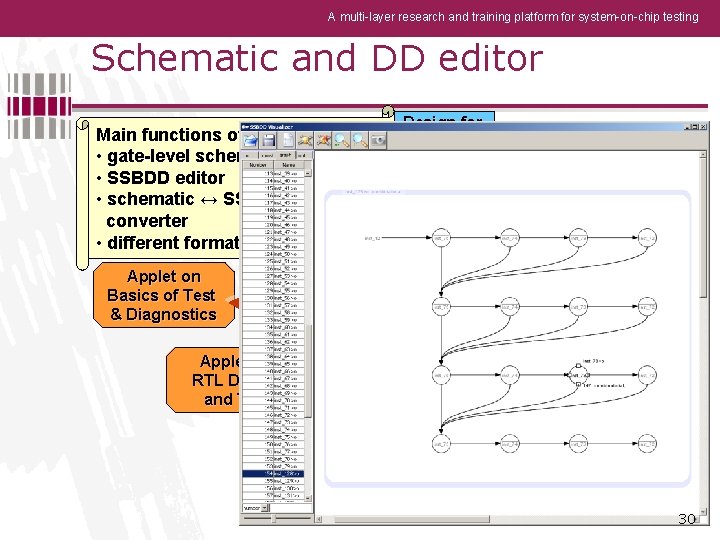

A multi-layer research and training platform for system-on-chip testing Schematic and DD editor Main functions of the applet are: • gate-level schematic editor • SSBDD editor • schematic ↔ SSBDD on-the-fly converter • different format reader/converter Applet on Basics of Test & Diagnostics AGM, GIF An applet targeted at binding all the applets and the Turbo Tester Schematic & DD Editor AGM, DWG AGM, GIF Applet on RTL Design and Test Design for Testability AGM Applet on Boundary Scan Standard Supported interface formats are: AGM DWG VHDL GIF EDIF? Post. Script? 30

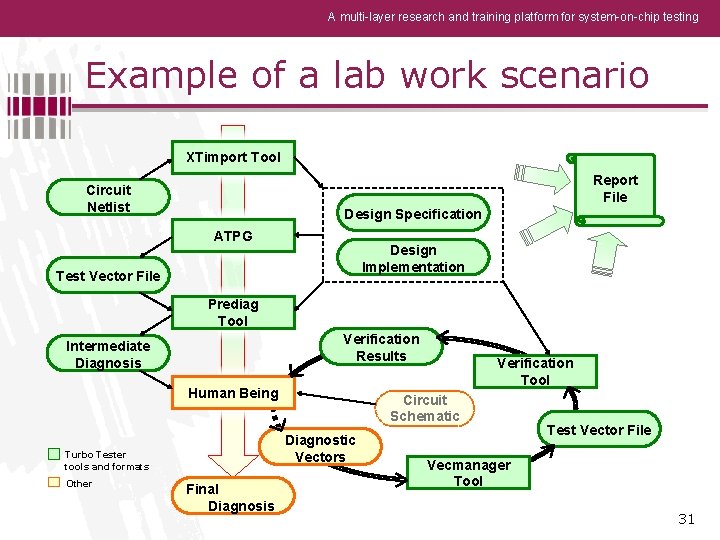

A multi-layer research and training platform for system-on-chip testing Example of a lab work scenario XTimport Tool Report File Circuit Netlist Design Specification ATPG Design Implementation Test Vector File Prediag Tool Verification Results Intermediate Diagnosis Human Being Other Circuit Schematic Diagnostic Vectors Turbo Tester tools and formats Final Diagnosis Verification Tool Test Vector File Vecmanager Tool 31

A multi-layer research and training platform for system-on-chip testing Conclusions & Discussion The main features of the platform: • Research engine + training software • Layered structure • HW and SW components • Remote access • Distance learning and e-learning • Computer-aided teaching • Freeware 32

A multi-layer research and training platform for system-on-chip testing Our Tools on the Web The Turbo Tester home page http: //www. pld. ttu. ee/tt/ The Turbo Tester web-server page http: //www. pld. ttu. ee/webtt/ Def. Sim home page http: //www. defsim. com Java applets home page http: //www. pld. ttu. ee/applets/ 33

- Slides: 33