EKT 124 3 DIGITAL ELEKTRONIC 1 CHAPTER 3

- Slides: 21

EKT 124 / 3 DIGITAL ELEKTRONIC 1 CHAPTER 3 Counters (cont. )

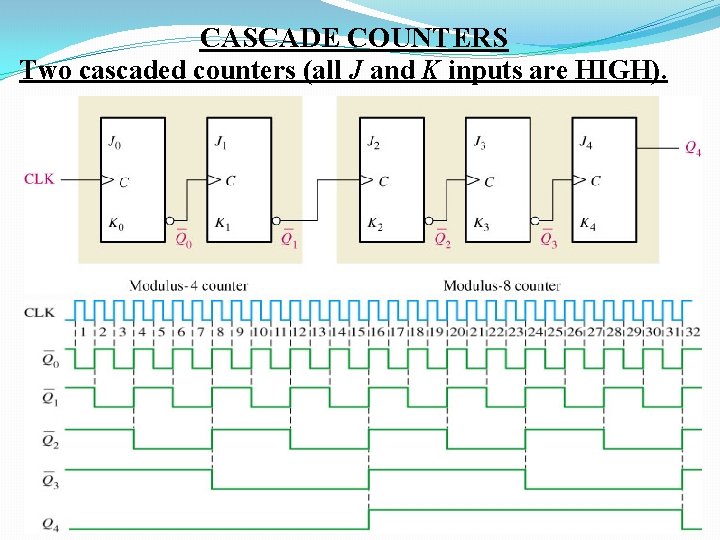

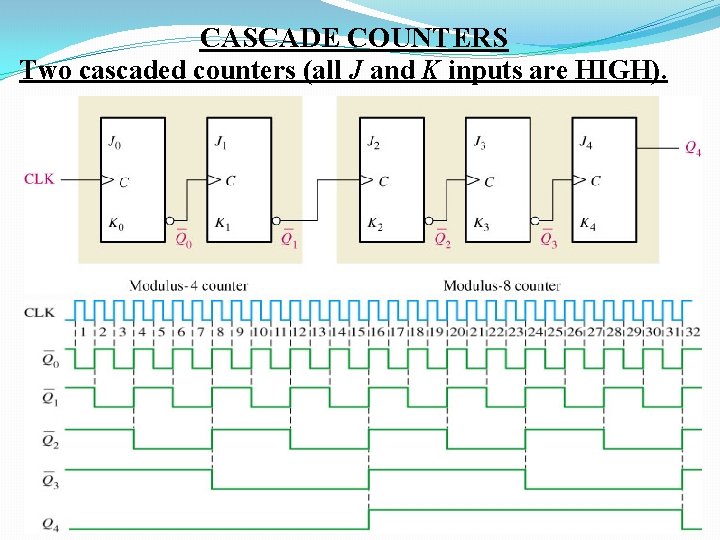

CASCADE COUNTERS Two cascaded counters (all J and K inputs are HIGH).

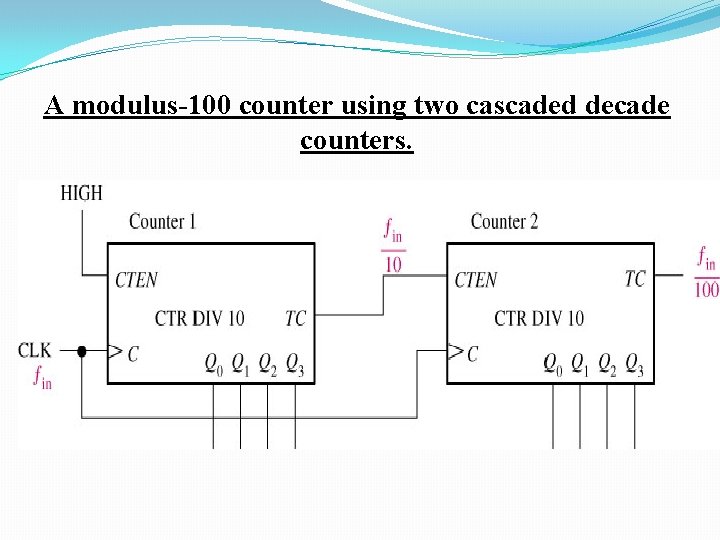

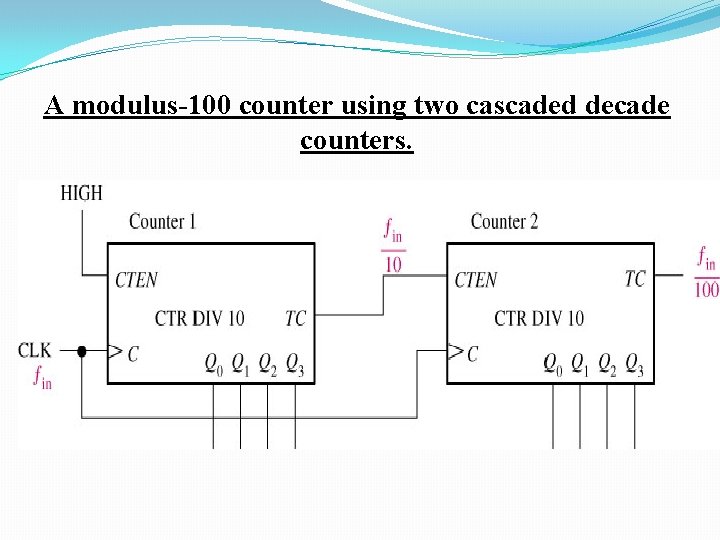

A modulus-100 counter using two cascaded decade counters.

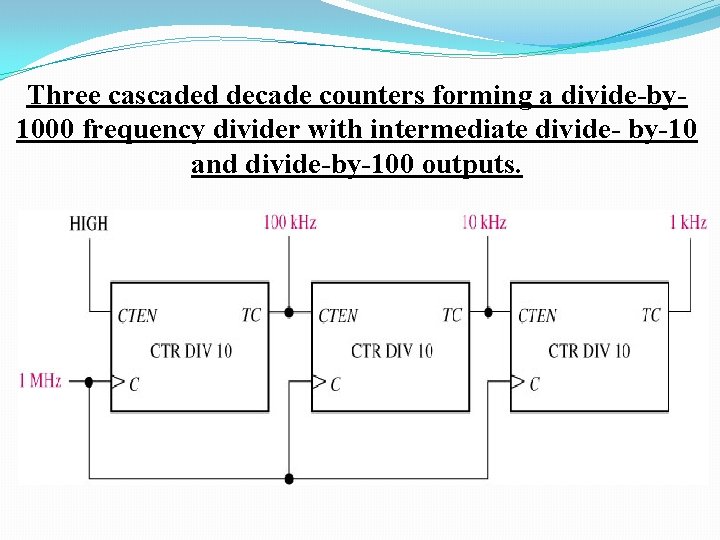

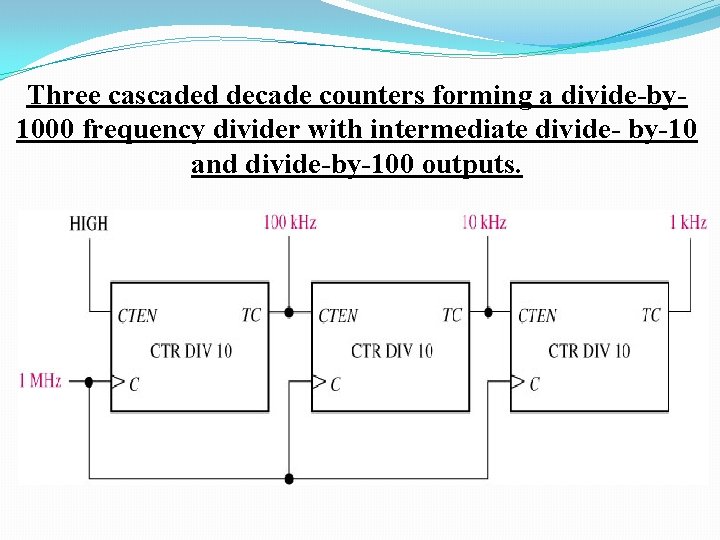

Three cascaded decade counters forming a divide-by 1000 frequency divider with intermediate divide- by-10 and divide-by-100 outputs.

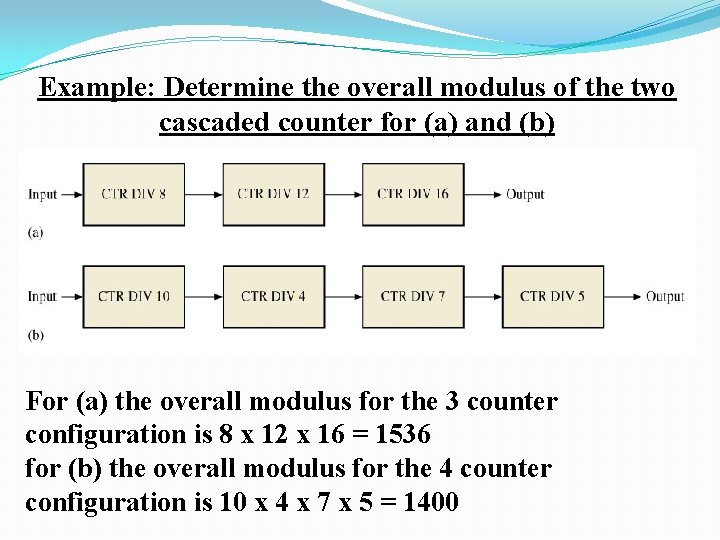

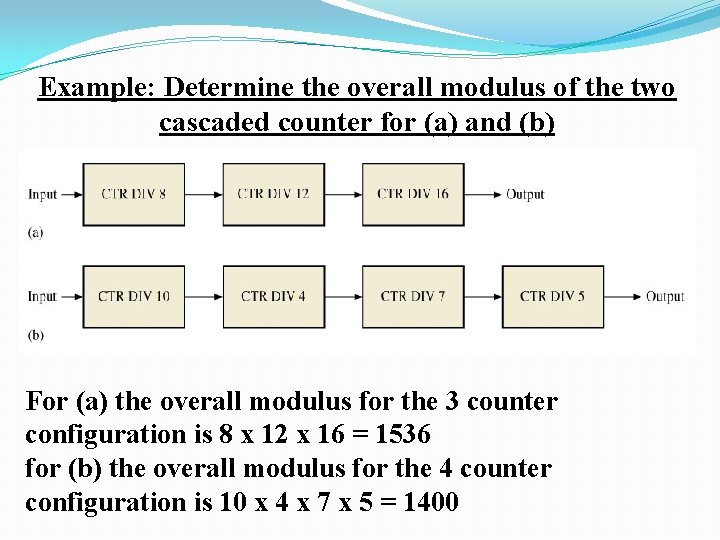

Example: Determine the overall modulus of the two cascaded counter for (a) and (b) For (a) the overall modulus for the 3 counter configuration is 8 x 12 x 16 = 1536 for (b) the overall modulus for the 4 counter configuration is 10 x 4 x 7 x 5 = 1400

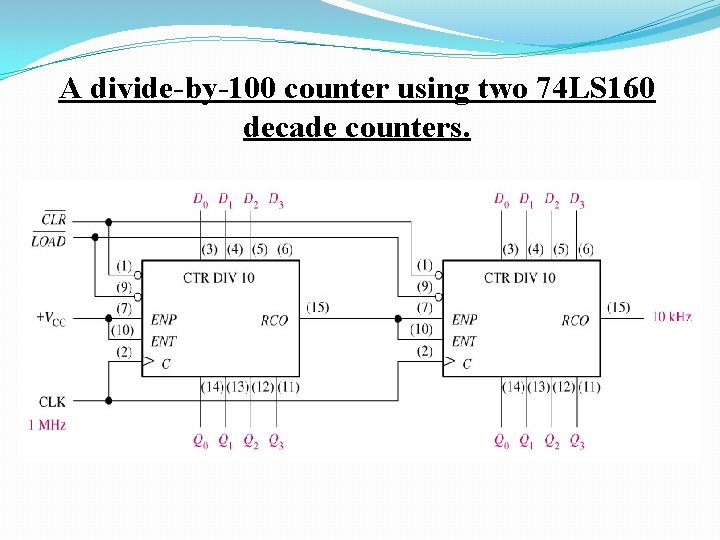

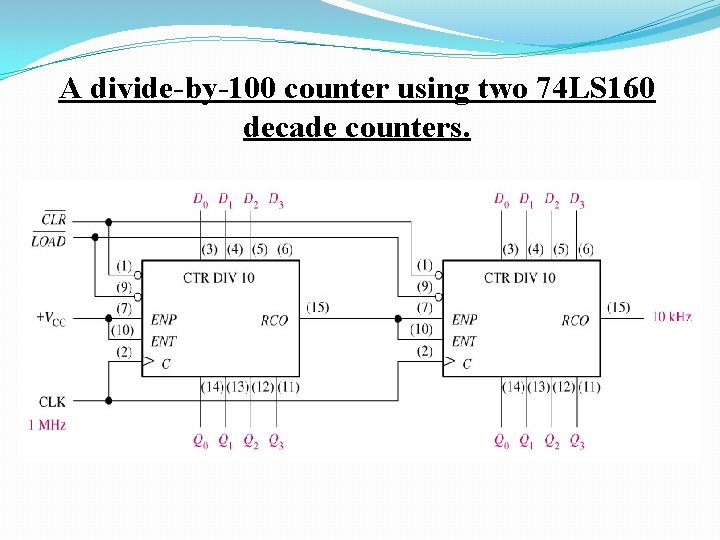

A divide-by-100 counter using two 74 LS 160 decade counters.

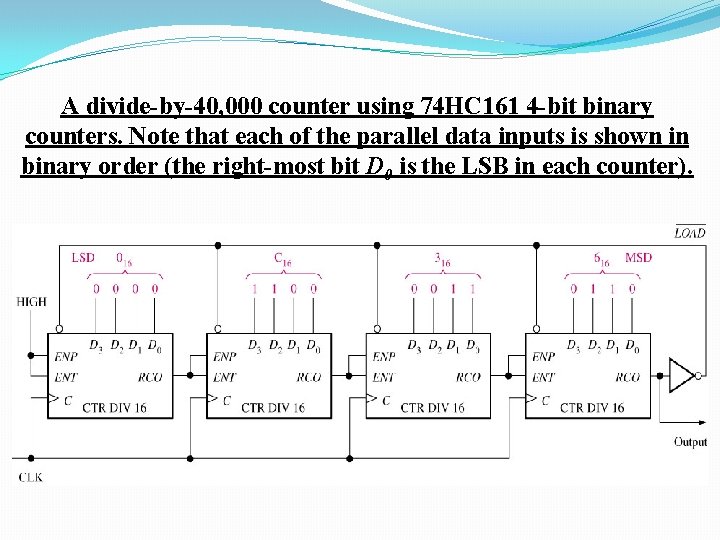

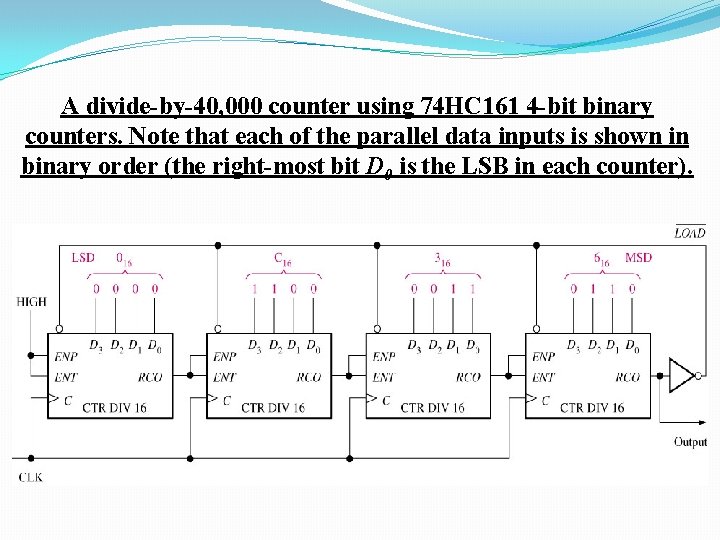

A divide-by-40, 000 counter using 74 HC 161 4 -bit binary counters. Note that each of the parallel data inputs is shown in binary order (the right-most bit D 0 is the LSB in each counter).

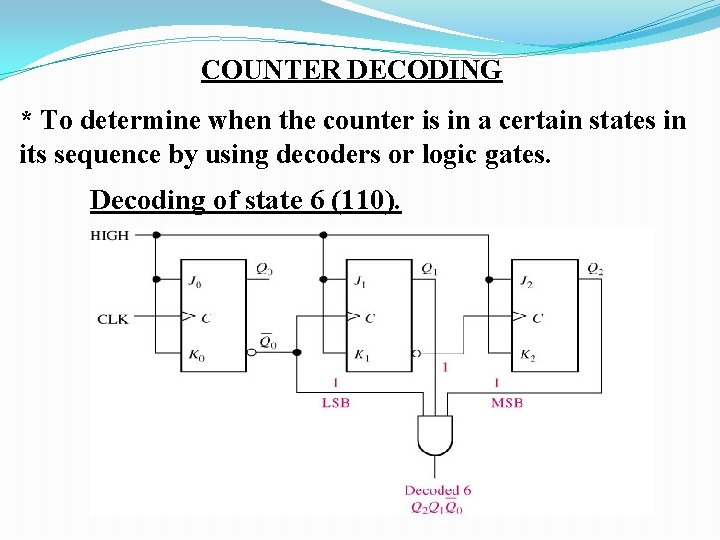

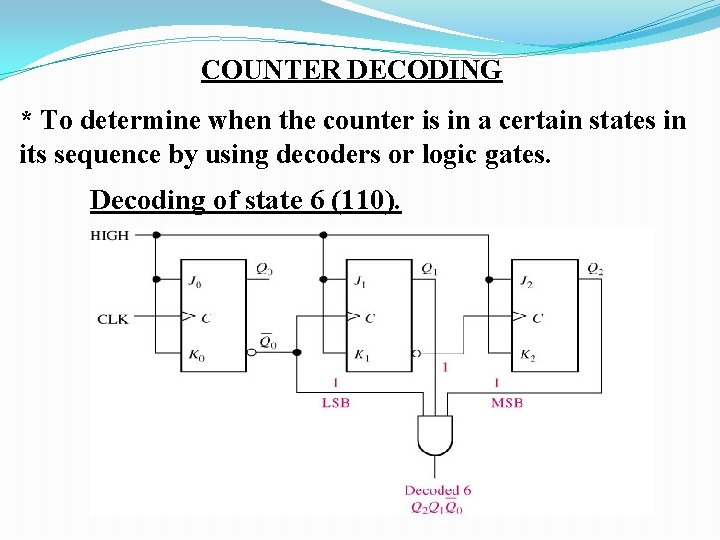

COUNTER DECODING * To determine when the counter is in a certain states in its sequence by using decoders or logic gates. Decoding of state 6 (110).

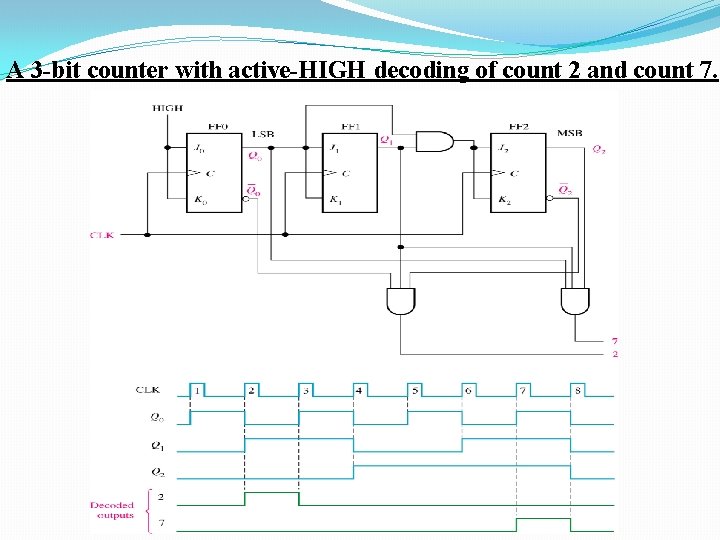

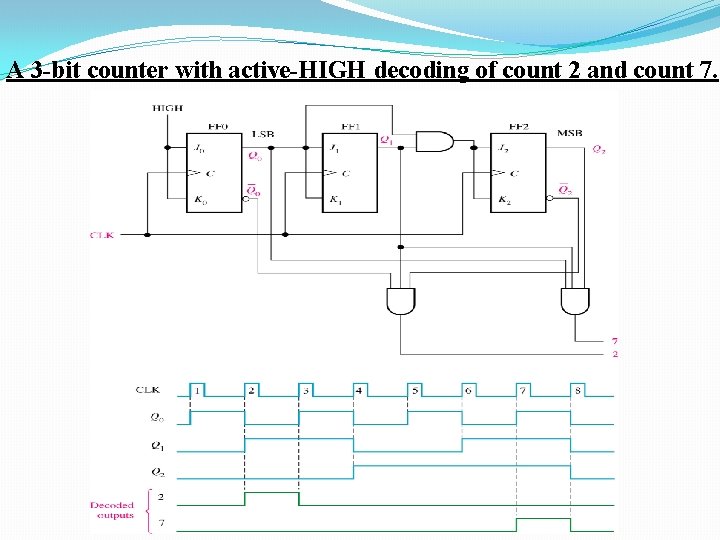

A 3 -bit counter with active-HIGH decoding of count 2 and count 7.

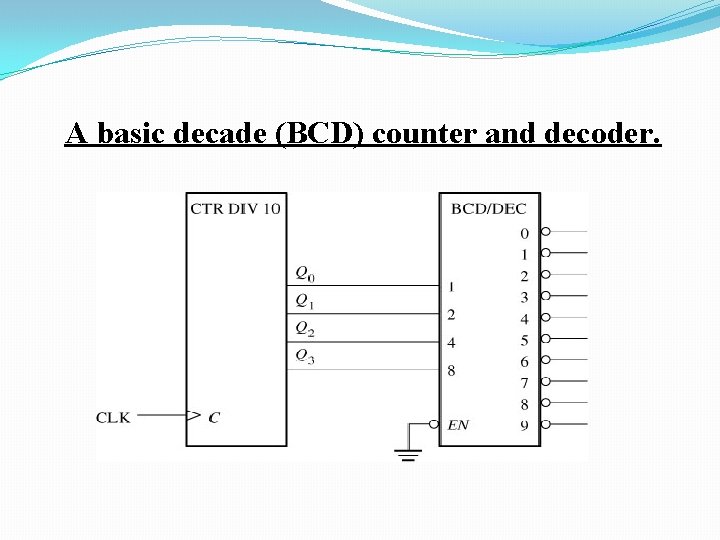

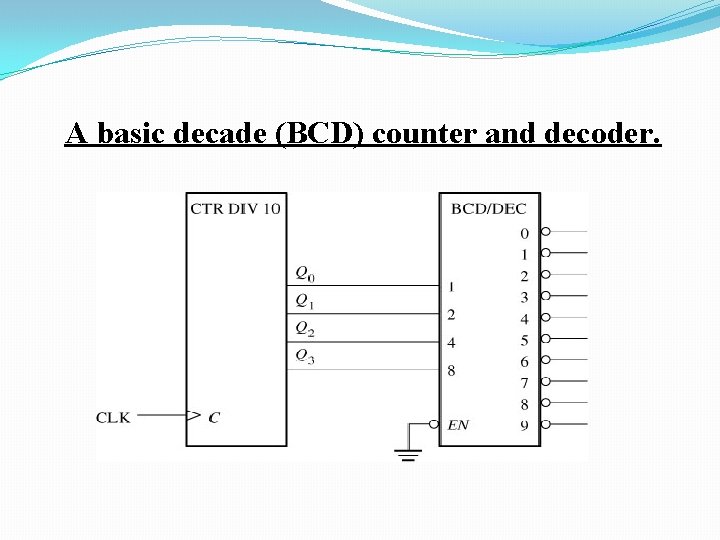

A basic decade (BCD) counter and decoder.

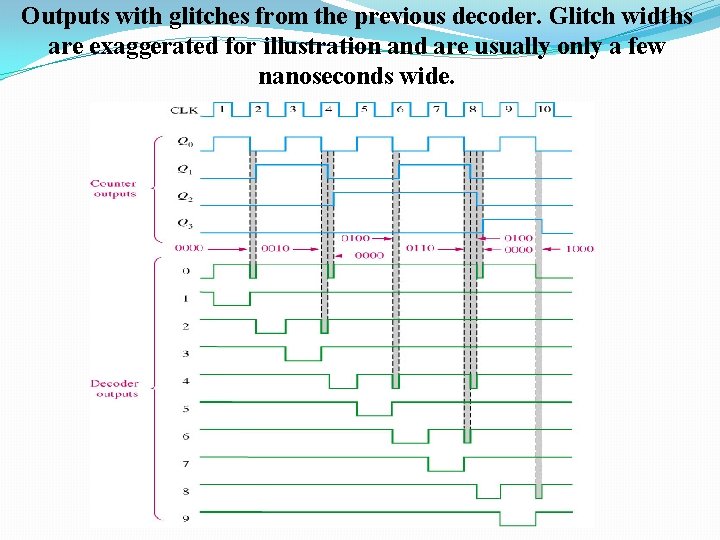

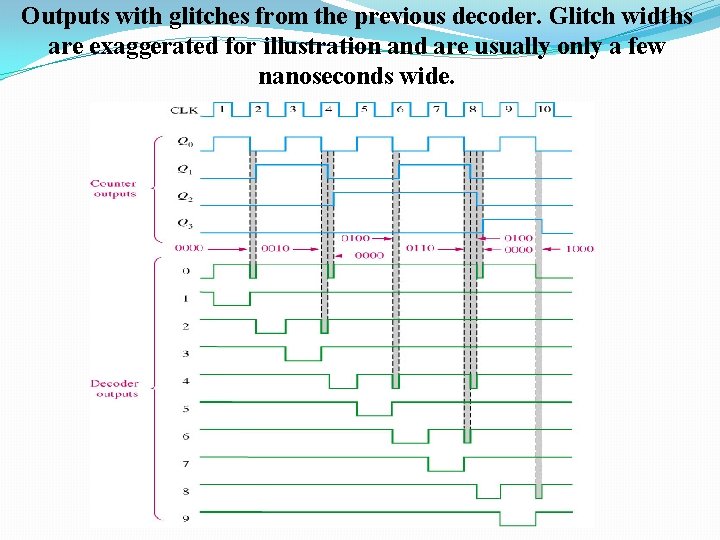

Outputs with glitches from the previous decoder. Glitch widths are exaggerated for illustration and are usually only a few nanoseconds wide.

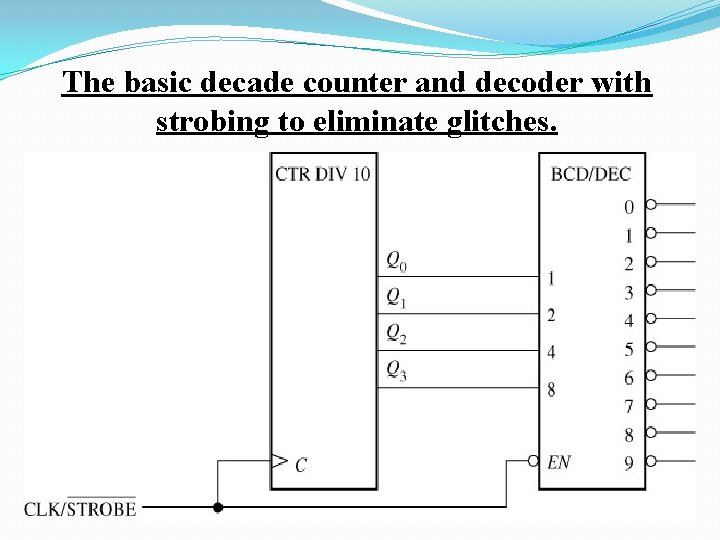

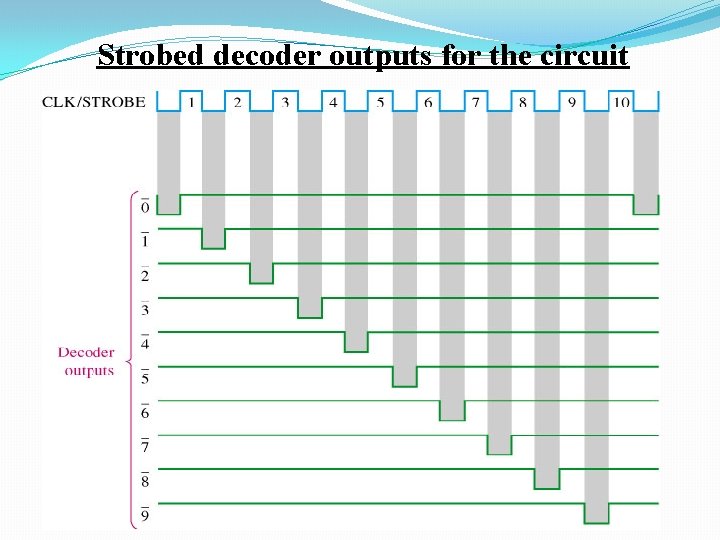

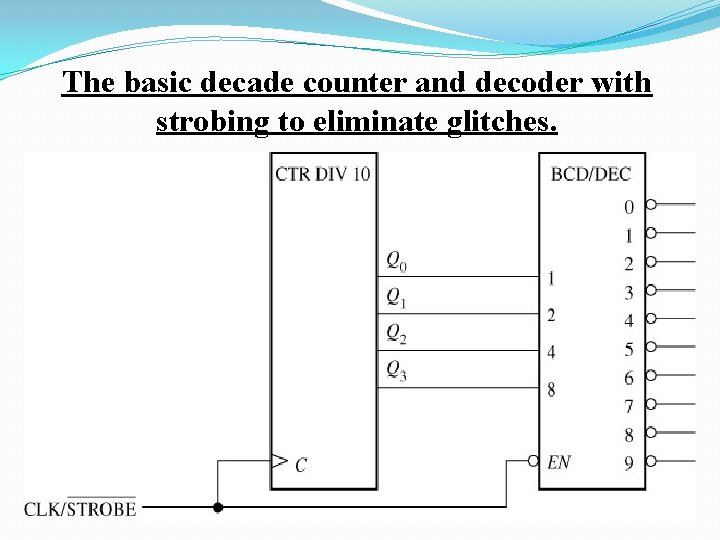

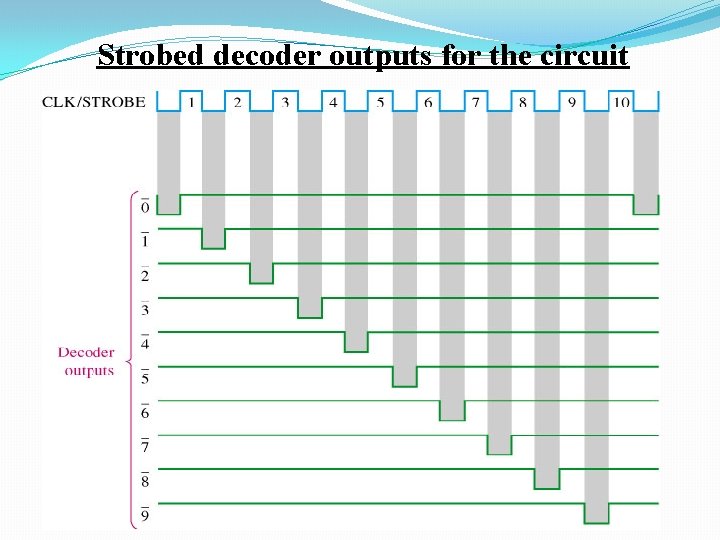

The basic decade counter and decoder with strobing to eliminate glitches.

Strobed decoder outputs for the circuit

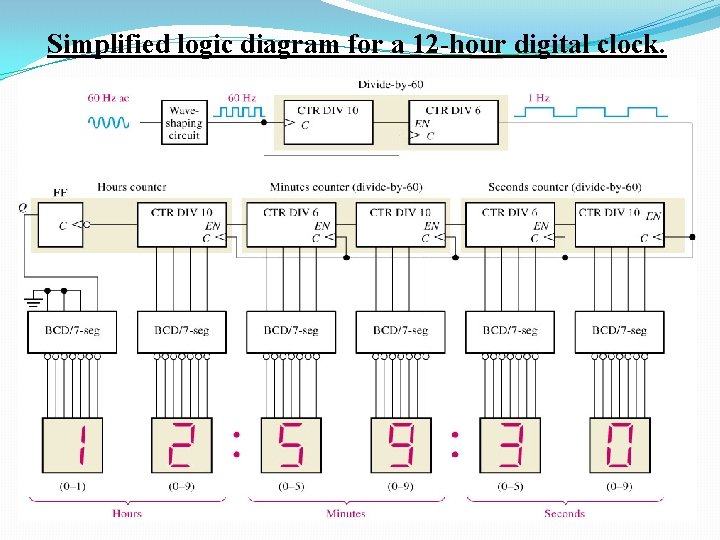

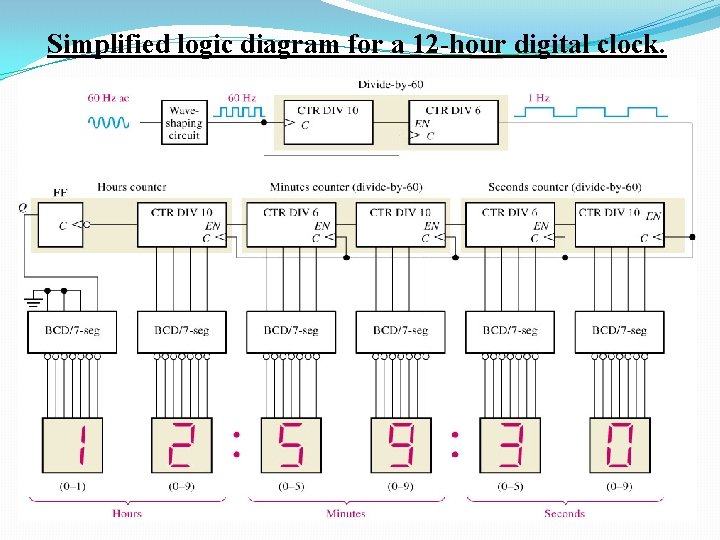

Simplified logic diagram for a 12 -hour digital clock.

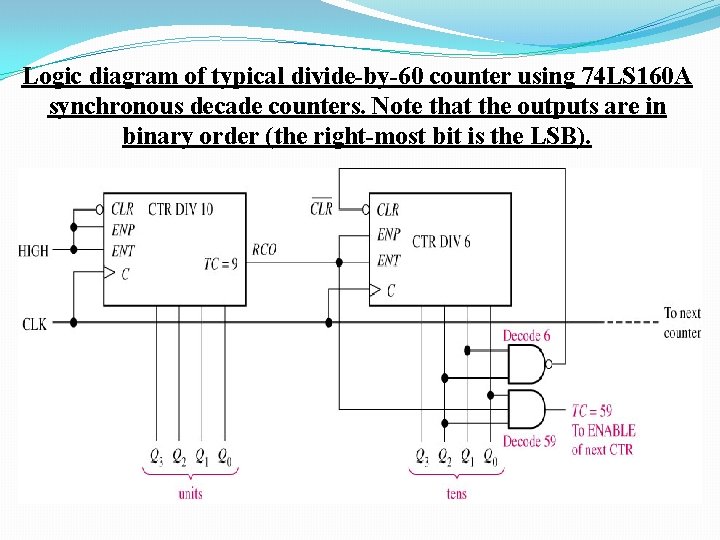

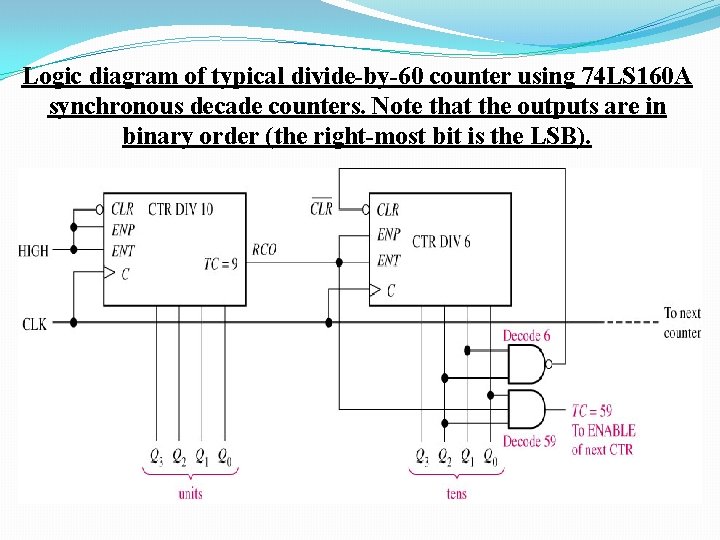

Logic diagram of typical divide-by-60 counter using 74 LS 160 A synchronous decade counters. Note that the outputs are in binary order (the right-most bit is the LSB).

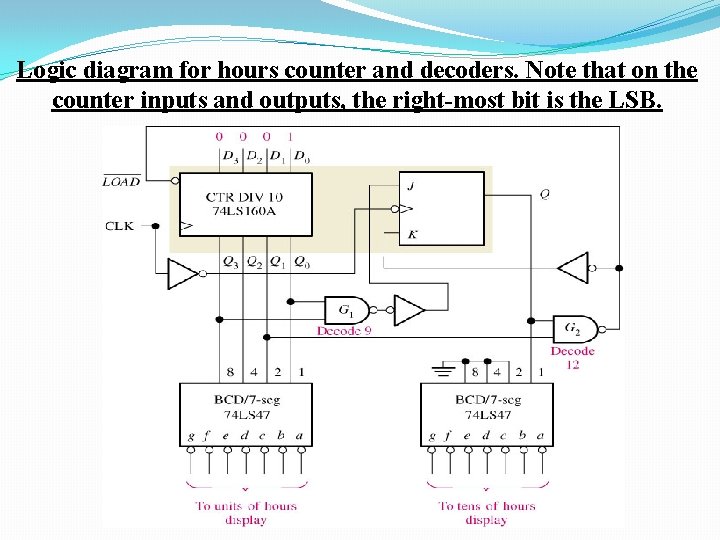

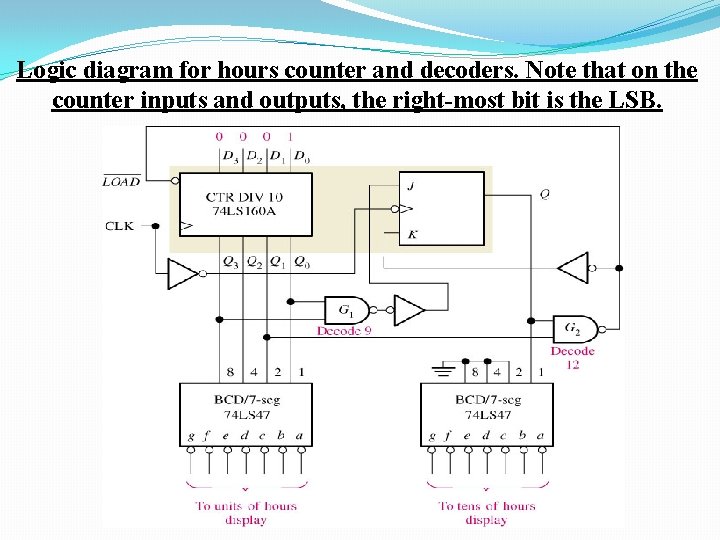

Logic diagram for hours counter and decoders. Note that on the counter inputs and outputs, the right-most bit is the LSB.

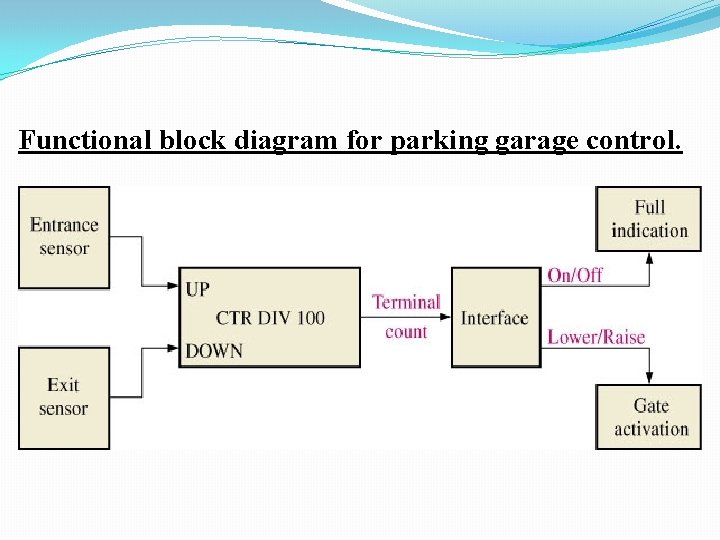

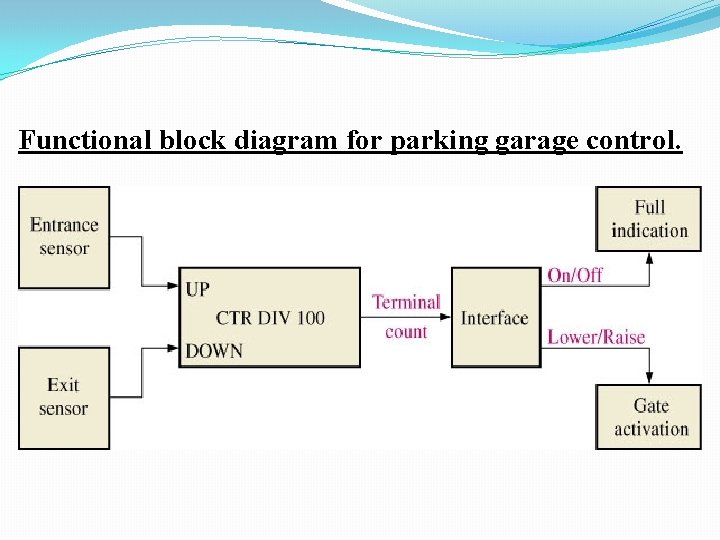

Functional block diagram for parking garage control.

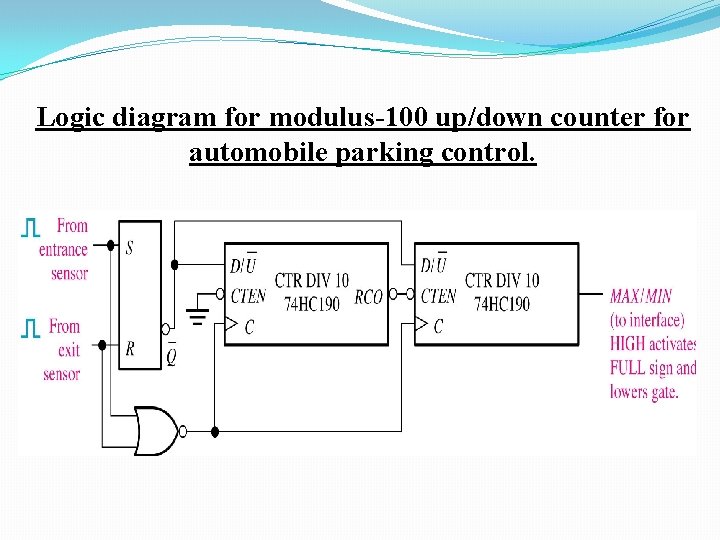

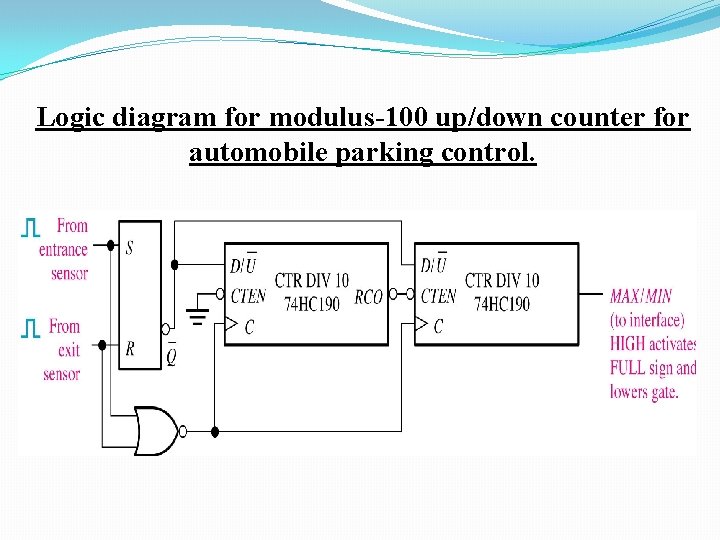

Logic diagram for modulus-100 up/down counter for automobile parking control.

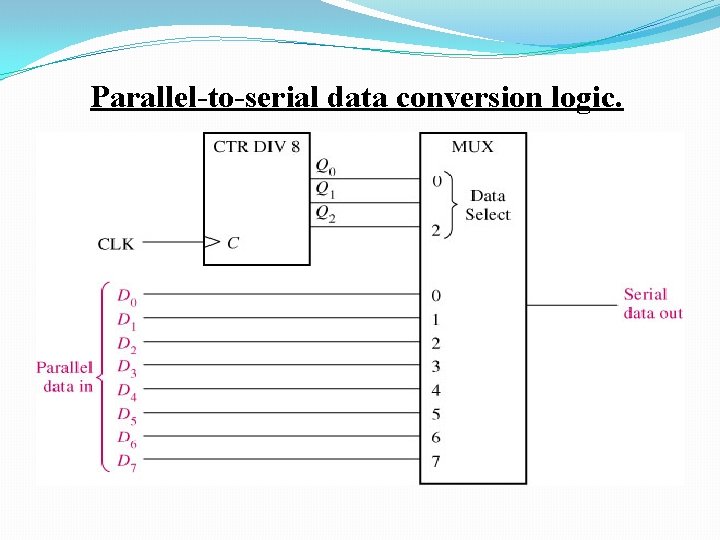

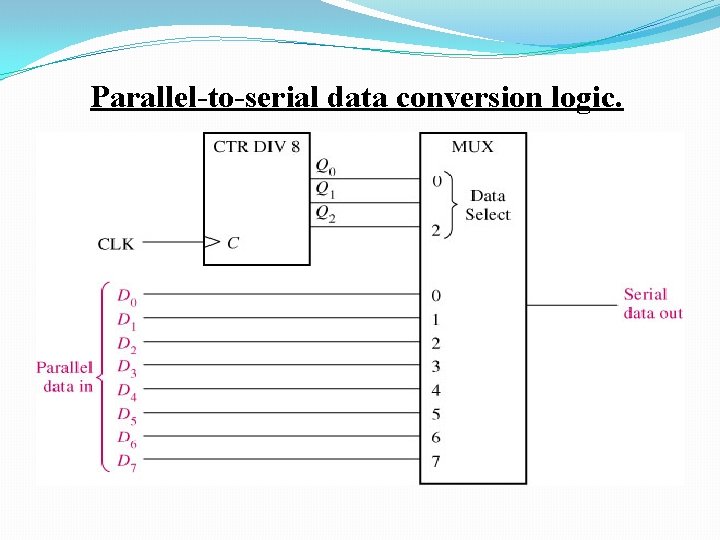

Parallel-to-serial data conversion logic.

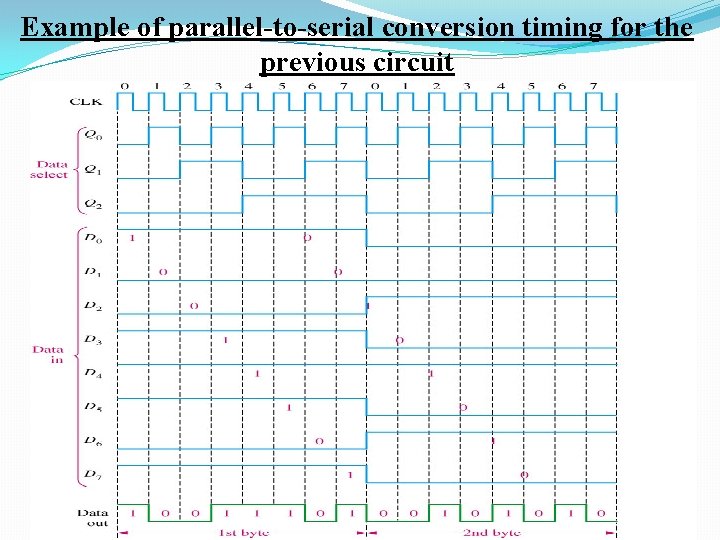

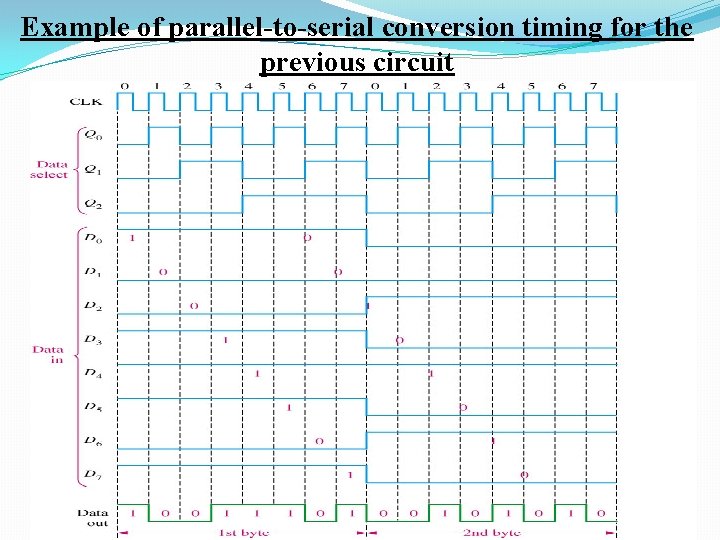

Example of parallel-to-serial conversion timing for the previous circuit

THANK YOU