EEL 49305934 Reconfigurable Computing The stateoftheart Reconfigurable Computing

EEL 4930/5934 Reconfigurable Computing The state-of-the-art Reconfigurable Computing equipment available for this course is made possible by a generous grant from the Rockwell Collins Growth Relationship Grant Program and an equipment/software donation from Nallatech.

Instructors n Dr. Greg Stitt n n n gstitt@ece. ufl. edu http: //www. gstitt. ece. ufl. edu Office Hours: MW 10 am-11 am n n (Benton 323) Also, by appointment

Course Website n 2 sites n n http: //www. gstitt. ece. ufl. edu/courses/eel 4930_5934/ n Linked off my website Web. CT Vista/E-learning n http: //lss. at. ufl. edu/� n n Select e-learning Login with Gator. Link account Used for posting grades, turning in projects Email Policy n When sending an email, include the class name in brackets n e. g. [EEL 5934] Question about project 2

Grading n EEL 4930/5934 Grading: n n n Mid-term 1: 30% (Dates to be announced) Mid-term 2: 30% Labs/Homework: 10% Project: 30% Final grade: curved average of all components 5934 may possibly have different tests and project

Lab Assignments n Linked off main website n n n http: //www. gstitt. ece. ufl. edu/courses/eel 4930_5934/labs/ Intended to familiarize with FPGA boards, VHDL Initial labs will be individual n Will allow groups when using boards

Research Project n Groups n Size to be determined based on enrollment n n Likely 3 -4 per group Topic subject to instructor approval n n Will give examples Good idea - find algorithm in your area, use RC to improve performance n n Imaging processing, bioinformatics, CAD, etc. If interested in research, make an appointment with me n Will try to find a project that will helps towards degree

Reading Material n Textbook: The Design Warrior’s Guide to FPGAs n n n Supplemented by research papers n n n C. Maxfield ISBN: 978 -0750677045 Check class website for daily requirements Will also post slides when used Optional books also listed in syllabus

Prerequisites n You should be familiar with: n n Digital design Architecture n n n Controller+Datapath Memory Hierarchy Pipelining More listed in syllabus Assumes no knowledge of reconfigurable computing

Goals n Understanding of issues related to RC (reconfigurable computing) n n n Detailed investigation of a specific problem n n Architectures Tools Design methodologies Speedup analysis Etc. Research project Publish! n Outstanding projects will be submitted to conferences

Academic Dishonesty n Unless told otherwise, labs and homework assignments must be done individually n n Groups must obtain permission to use larger size n n May be allowed for difficult projects Collaboration is allowed (and encouraged), but within limits n n n All assignments will be checked for cheating Can discuss problems, how to use tools etc. Cannot show code, solutions, etc. Cheating penalties n n First instance - 0 on corresponding assignment Second - 0 for entire class

Attendance Policy n n Attendance is optional, but highly recommended If you are sick, stay at home! n n If obviously sick, you will be asked to leave Missed tests cannot be retaken, except with doctor’s note

What is Reconfigurable Computing? n Reconfigurable computing (RC) is the study of architectures that can adapt (after fabrication) to a specific application or application domain n Involves architecture, design strategies, tool flows, CAD, languages, algorithms

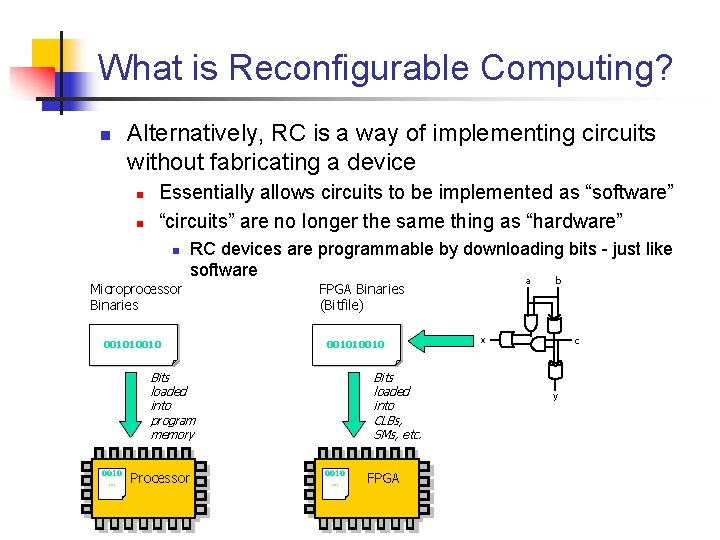

What is Reconfigurable Computing? Alternatively, RC is a way of implementing circuits without fabricating a device n n n Essentially allows circuits to be implemented as “software” “circuits” are no longer the same thing as “hardware” n Microprocessor Binaries RC devices are programmable by downloading bits - just like software a b 001010010 FPGA Binaries (Bitfile) 001010010 Bits loaded into program memory 0010 … Processor Bits loaded into CLBs, SMs, etc. 0010 … FPGA Processor x c y

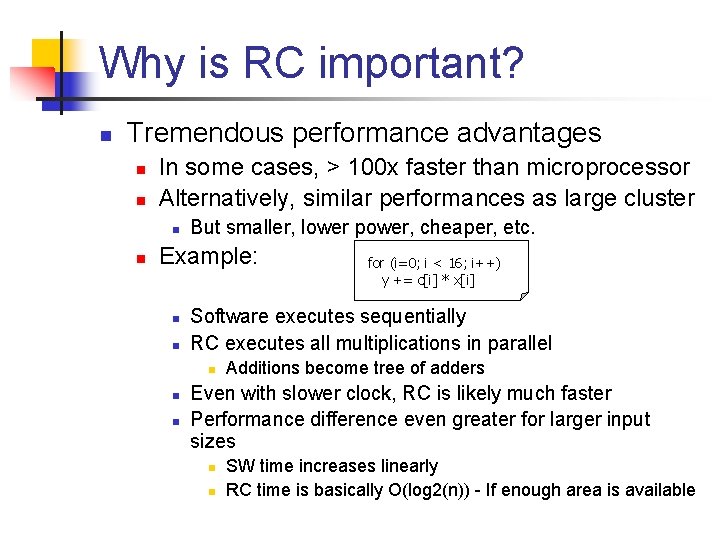

Why is RC important? n Tremendous performance advantages n n In some cases, > 100 x faster than microprocessor Alternatively, similar performances as large cluster n n But smaller, lower power, cheaper, etc. Example: n n Software executes sequentially RC executes all multiplications in parallel n n n for (i=0; i < 16; i++) y += c[i] * x[i] Additions become tree of adders Even with slower clock, RC is likely much faster Performance difference even greater for larger input sizes n n SW time increases linearly RC time is basically O(log 2(n)) - If enough area is available

Reminder n n Lab 0 - ISE Tutorial Read RC survey linked off website

- Slides: 15