EEL 49305934 Reconfigurable Computing The stateoftheart Reconfigurable Computing

EEL 4930/5934 Reconfigurable Computing The state-of-the-art Reconfigurable Computing equipment available for this course is made possible by a generous grant from the Rockwell Collins Growth Relationship Grant Program and an equipment/software donation from Nallatech.

Instructors n Dr. Greg Stitt n n n gstitt@ece. ufl. edu http: //www. gstitt. ece. ufl. edu Office Hours 3 -4 M, W (Benton 323) n n Also, by appointment Dr. Herman Lam n n n hlam@ufl. edu http: //www. hlam. ece. ufl. edu Larsen 225

Course Website n 2 sites n n http: //www. gstitt. ece. ufl. edu/courses/eel 4930_5934/ n Linked off my website Web. CT Vista/E-learning n http: //lss. at. ufl. edu/� n n Select e-learning Login with Gator. Link account Used for posting grades, class discussions Email Policy n When sending an email, include the class name in brackets n n e. g. [EEL 5932] Question about project 2 For emails to entire class, use e-learning n Announcements will be posted both on class website and e-learning site

Grading n EEL 4930/5934 Grading: n n n n Mid-term 1: 20% (Wednesday, October 3) Mid-term 2: 20% (Wednesday, October 31) Final exam: 20% Labs/Homework: 10% Project: 30% Final grade: curved average of all components 5934 will have different tests, homeworks, and project

Lab Assignments n Linked off main website and e-learning n n n http: //www. hlam. ece. ufl. edu/EEL 4930_5934 Labs. Proj/ Intended to familiarize with FPGA boards, VHDL Initials labs will be individual n Will allow groups when using boards

Research Project n Groups n Size to be determined based on enrollment n n Likely 2 -3 per group Topic subject to instructor approval n n Will give examples Good idea - find algorithm in your area, use RC to improve performance n n Imaging processing, bioinformatics, CAD, etc. If interested in research, make an appointment with me n Will try to find a project that will helps towards degree

Reading Material n Textbook: The Design Warrior’s Guide to FPGAs n n n Supplemented by research papers n n n C. Maxfield ISBN: 978 -0750677045 Check class website for daily requirements Will also post slides when used Optional books also listed in syllabus

Prerequisites n n Digital design Architecture n n n Controller/Datapath Memory Heirarchy Pipelining More listed in syllabus Assumes no knowledge of reconfigurable computing

Goals n n Understanding of issues related to RC (reconfigurable computing) Detailed investigation of a specific problem n n Project/Research Paper Publish! n Best submissions will be submitted

Academic Dishonesty n Unless told otherwise, labs and homework assignments must be done individually n n Groups must obtain permission to use larger size n n May be allowed for difficult projects Collaboration is allowed (and encouraged), but within limits n n n All assignments will be checked for cheating Can discuss problems, how to use tools etc. Cannot show code, solutions, etc. Cheating penalties n n First instance - 0 on corresponding assignment Second - 0 for entire class

Attendance Policy n n Attendance is optional, but highly recommended If you are sick, stay at home! n n If obviously sick, you will be asked to leave Missed tests cannot be retaken, except with doctor’s note

What is Reconfigurable Computing? n Reconfigurable computing (RC) is the study of architectures that can adapt (after fabrication) to a specific application or application domain n Involves architecture, design strategies, tool flows, CAD, languages, algorithms

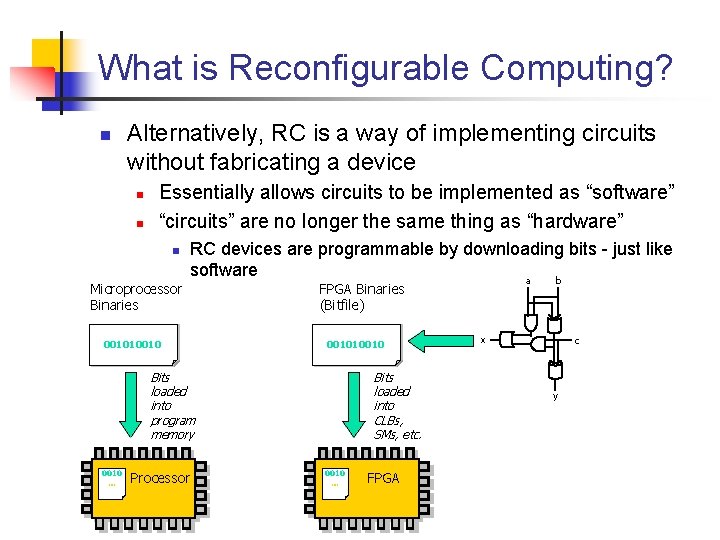

What is Reconfigurable Computing? Alternatively, RC is a way of implementing circuits without fabricating a device n n n Essentially allows circuits to be implemented as “software” “circuits” are no longer the same thing as “hardware” n Microprocessor Binaries RC devices are programmable by downloading bits - just like software a b 001010010 FPGA Binaries (Bitfile) 001010010 Bits loaded into program memory 0010 … Processor Bits loaded into CLBs, SMs, etc. 0010 … FPGA Processor x c y

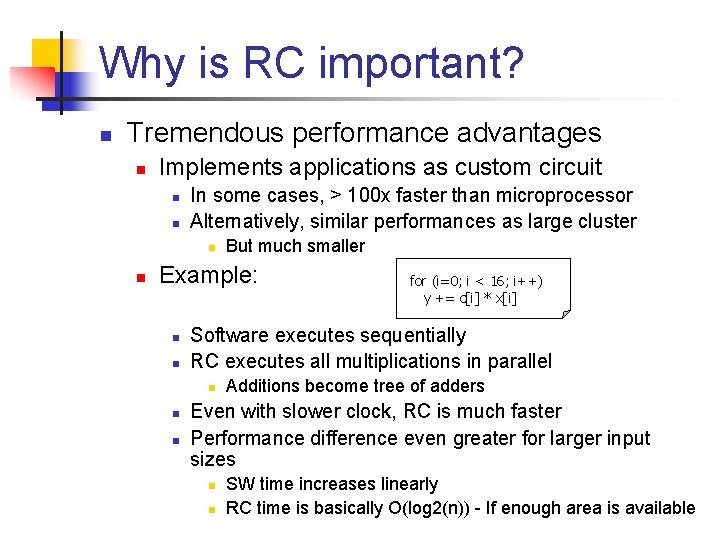

Why is RC important? n Tremendous performance advantages n Implements applications as custom circuit n n In some cases, > 100 x faster than microprocessor Alternatively, similar performances as large cluster n n But much smaller Example: n n Software executes sequentially RC executes all multiplications in parallel n n n for (i=0; i < 16; i++) y += c[i] * x[i] Additions become tree of adders Even with slower clock, RC is much faster Performance difference even greater for larger input sizes n n SW time increases linearly RC time is basically O(log 2(n)) - If enough area is available

When should RC be used? n When it provides the cheapest solution n n Generally, depends on volume of devices Total cost = NRE + Volume*unit_cost n NRE: non-recurring engineering cost n n One-time cost involved in creating design Volume: expected units to be sold Unit cost: cost of each individual unit RC is typically more cost effective for low volume devices n n RC: low NRE, high unit cost ASIC: very high NRE, low unit cost

When should RC be used? n When circuit may have to be modified n n n Can’t change ASIC - hardware Can change circuit implemented in FPGA Uses n When standards change n n Codec changes after devices fabricated Allows addition of new features to existing devices “Partial reconfiguration” allows virtual fabric size analagous to virtual memory Without RC n Anything that may have to be reconfigured is implemented in software n Performance loss

RC Markets n Embedded Systems n RC achieves performance close to ASIC, sometimes at much lower cost n n Many embedded systems still use ASIC due to high volume Reconfigurablilty! n n If standards changes, architecture is not fixed Can add new features after production

RC Markets n High-performance computing - HPC n Cray XD-1 n n SGI Altix n n 12 AMD Opterons, FPGAs 64 Itaniums, FPGAs IBM Chameleon n Cell processor, FPGAs

RC Markets n General-purpose computing? ? ? n n Ideal situation: desktop machine/OS uses RC to speedup up all applications Problems n RC can be very fast, but not for all applications n n n Generally requires parallel algorithms Coding constructs used in many applications not appropriate for hardware Subject of tremendous amount of past and likely future research

CHREC n NSF Center for High-Performance Reconfigurable Computing n http: //www. chrec. ufl. edu/

- Slides: 20