ECE Grande ECE 477 Design Review Team 3

- Slides: 29

ECE Grande ECE 477 Design Review Team 3 - Fall 2008

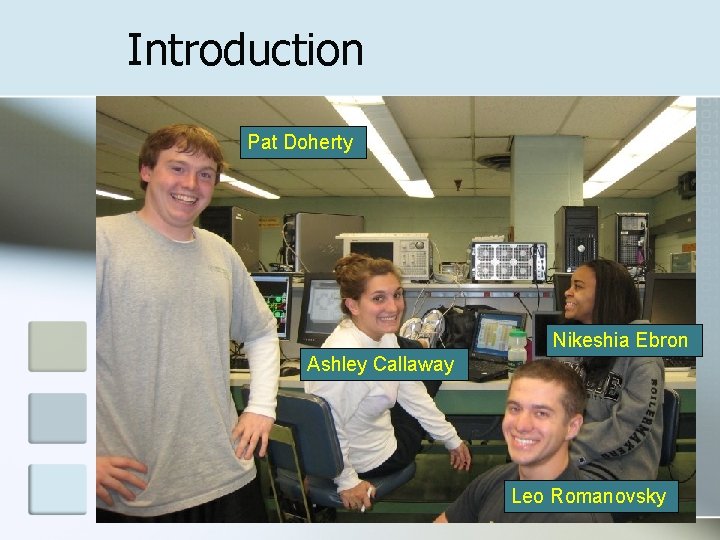

Introduction Ashley Pat Callaway Doherty n Pat Doherty n Nikeshia Ebron n Leo Romanovsky n Nikeshia Ebron Ashley Callaway Leo Romanovsky

Outline Project overview n Project-specific success criteria n Block diagram n Component selection rationale n Packaging design n Schematic and theory of operation n PCB layout n Software design/development status n Project completion timeline n Questions / discussion n

Project Overview n The ECE Grande is a digital poker game table. n All personal player information is digitally stored n The table will consist of 4 player stations n Central community screen to display community information n Web server to display the current game status on a remote computer

Project-Specific Success Criteria I. An ability to authenticate users using an RFID tag II. An ability to transmit/export the current game state via a TCP/IP connection III. An ability to display each player’s information on individual LCD screen and community information on a central screen.

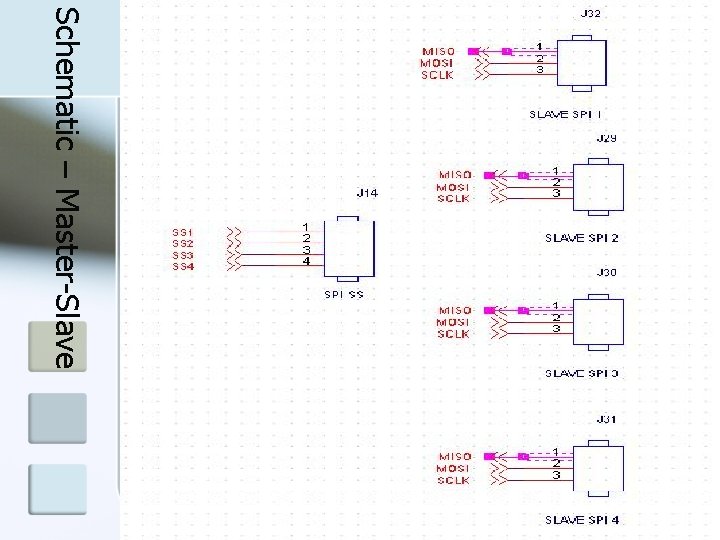

PSSC – cont. IV. An ability to run a multi-player No. Limit Texas Hold’em game. V. An ability to interface with a distributed network of microcontrollers to control graphic LCDs and receive user input.

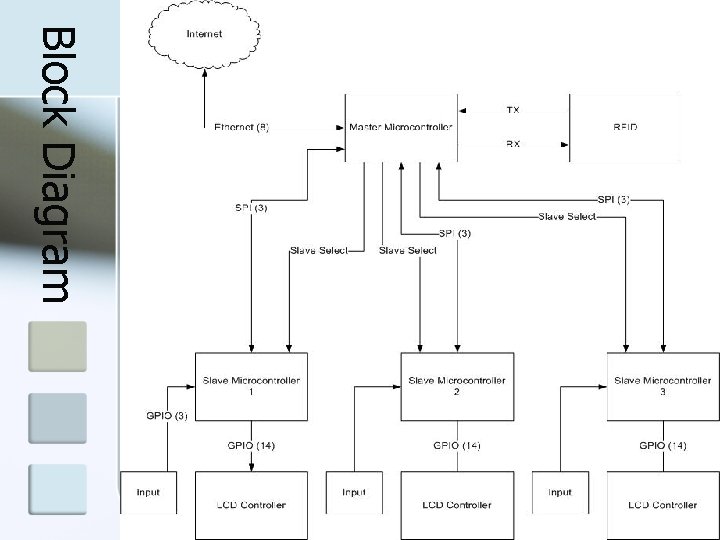

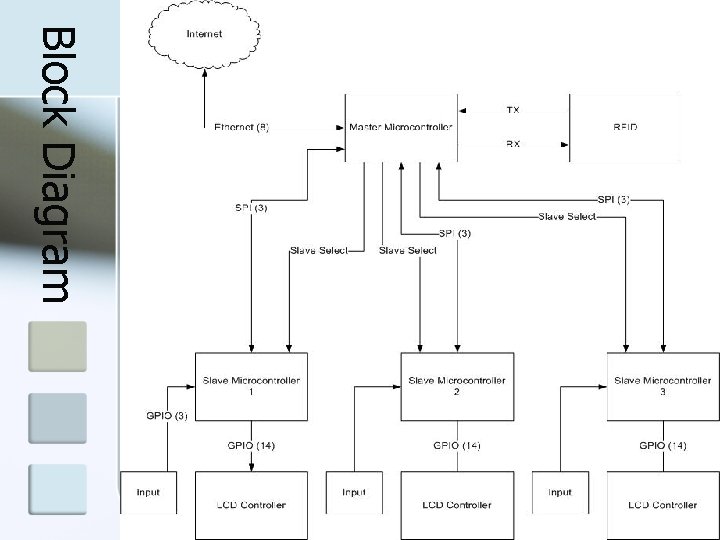

Block Diagram

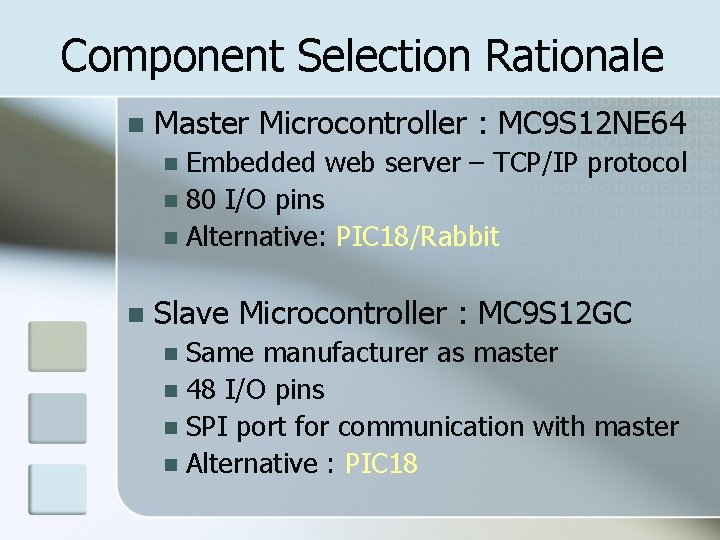

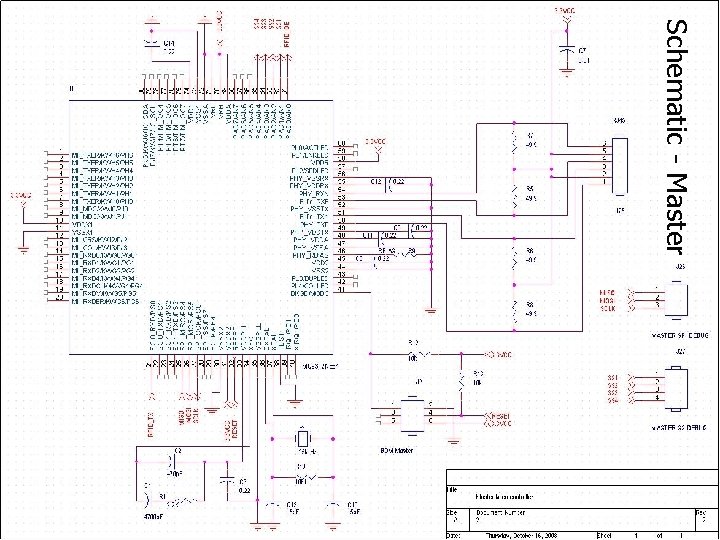

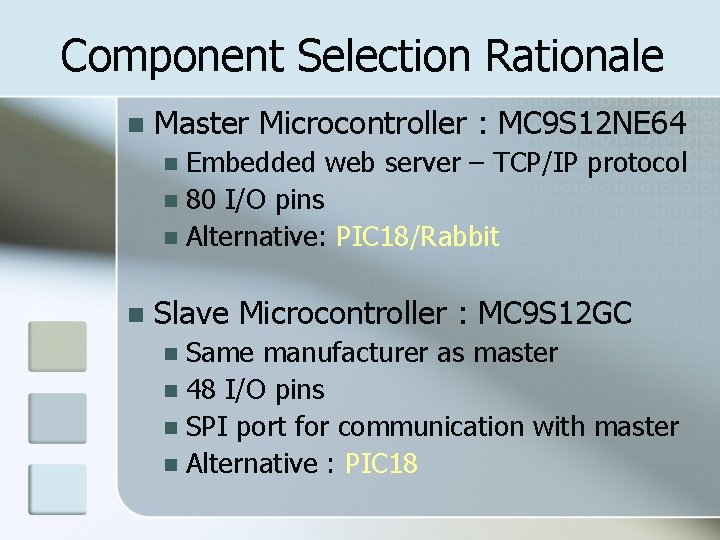

Component Selection Rationale n Master Microcontroller : MC 9 S 12 NE 64 Embedded web server – TCP/IP protocol n 80 I/O pins n Alternative: PIC 18/Rabbit n n Slave Microcontroller : MC 9 S 12 GC Same manufacturer as master n 48 I/O pins n SPI port for communication with master n Alternative : PIC 18 n

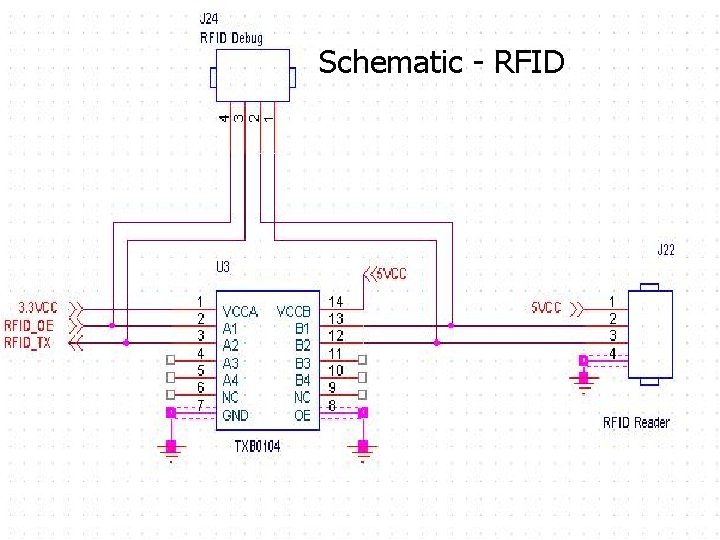

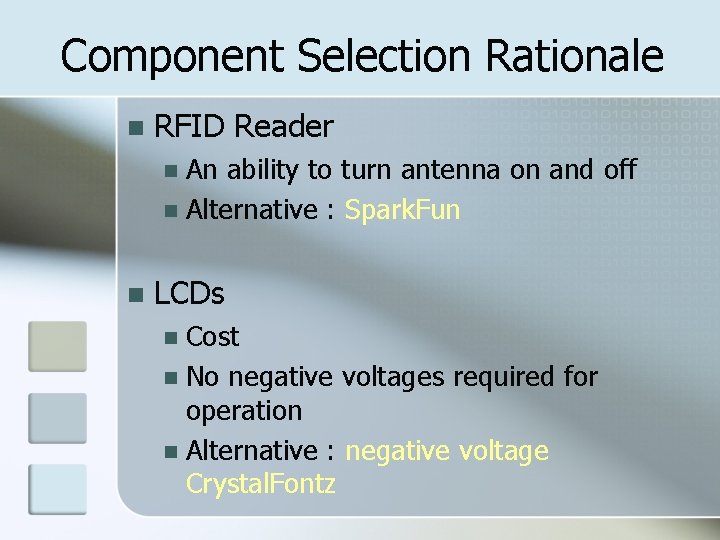

Component Selection Rationale n RFID Reader An ability to turn antenna on and off n Alternative : Spark. Fun n n LCDs Cost n No negative voltages required for operation n Alternative : negative voltage Crystal. Fontz n

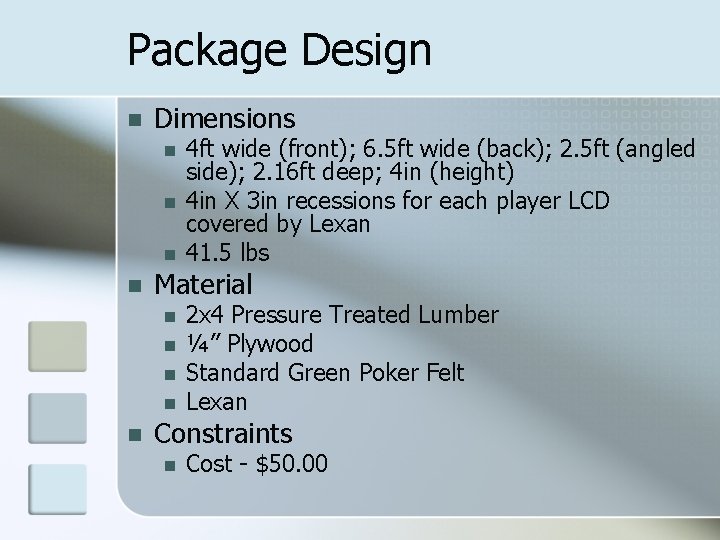

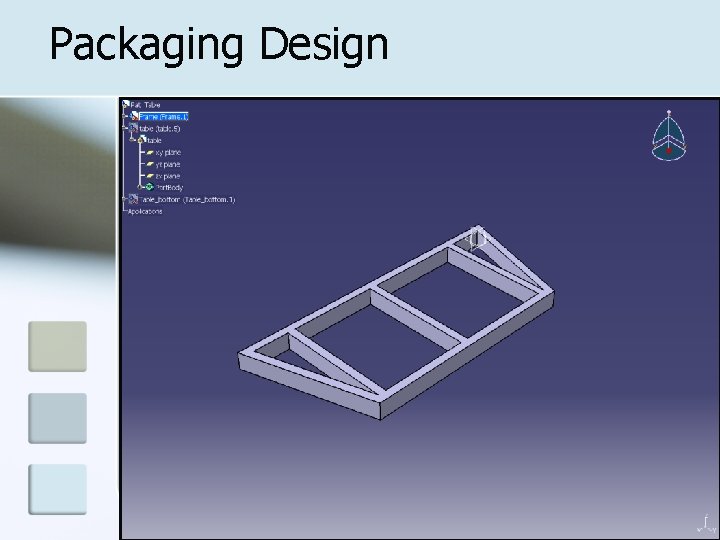

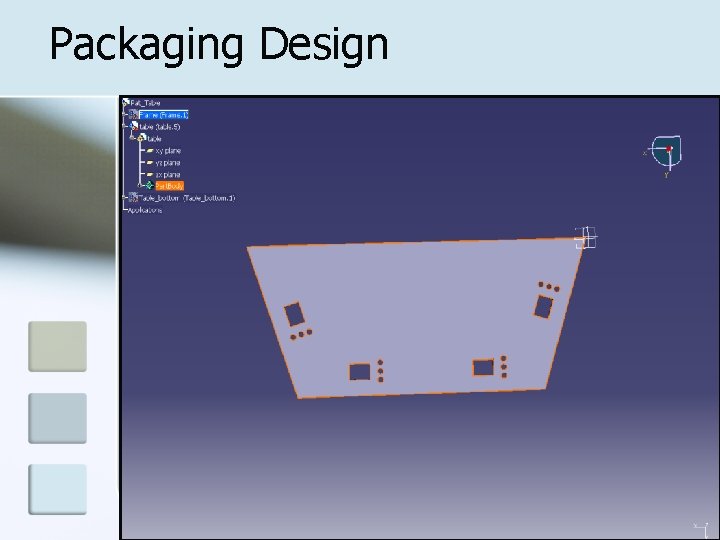

Package Design n Dimensions n n Material n n n 4 ft wide (front); 6. 5 ft wide (back); 2. 5 ft (angled side); 2. 16 ft deep; 4 in (height) 4 in X 3 in recessions for each player LCD covered by Lexan 41. 5 lbs 2 x 4 Pressure Treated Lumber ¼” Plywood Standard Green Poker Felt Lexan Constraints n Cost - $50. 00

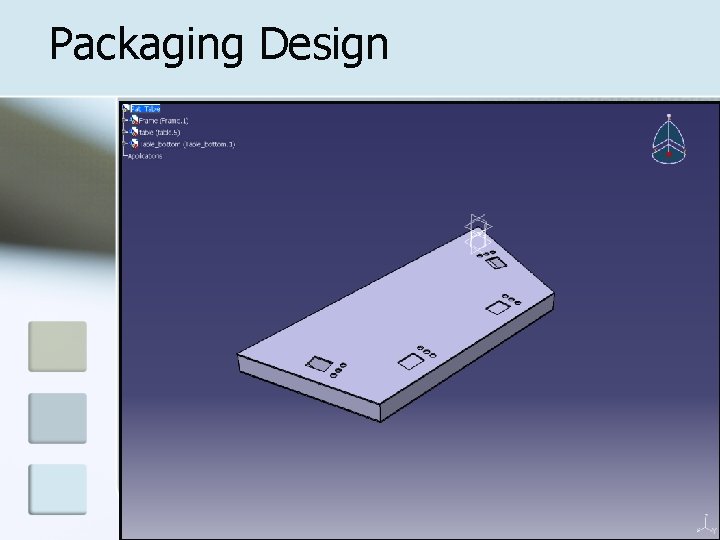

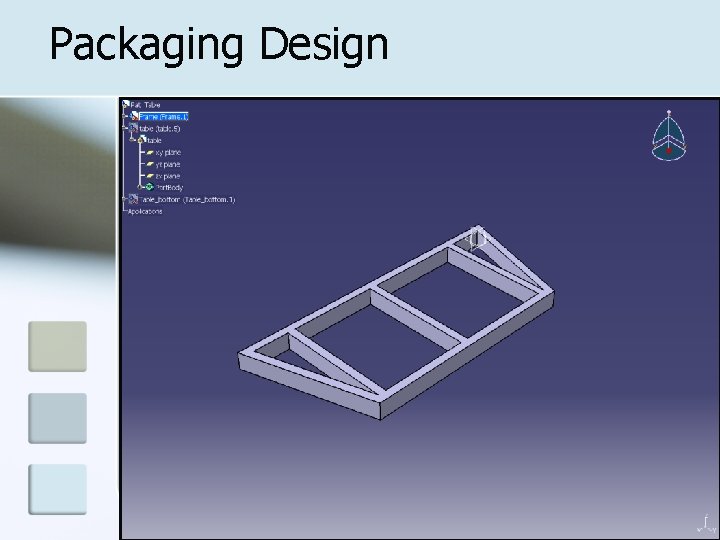

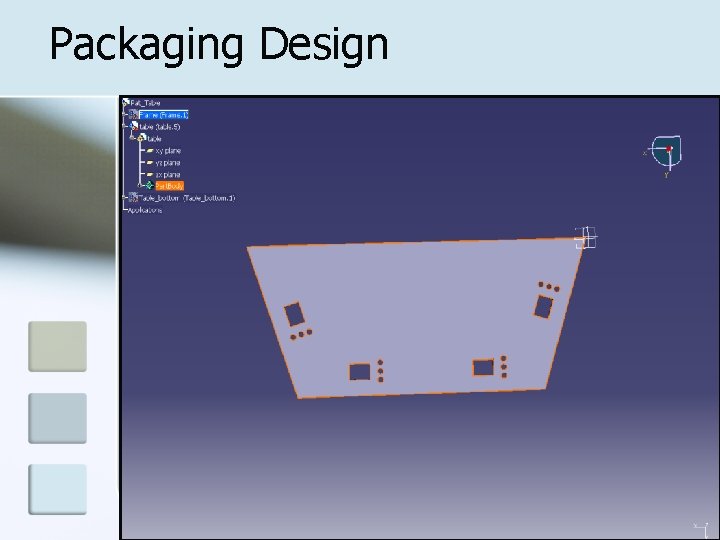

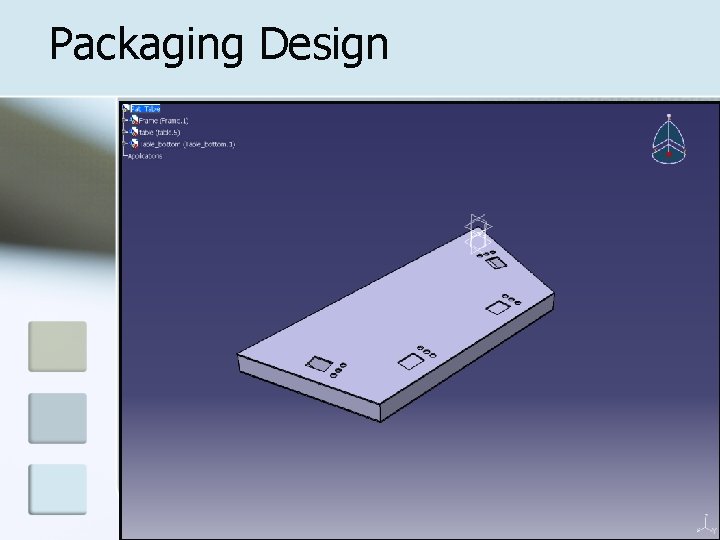

Packaging Design

Packaging Design

Packaging Design

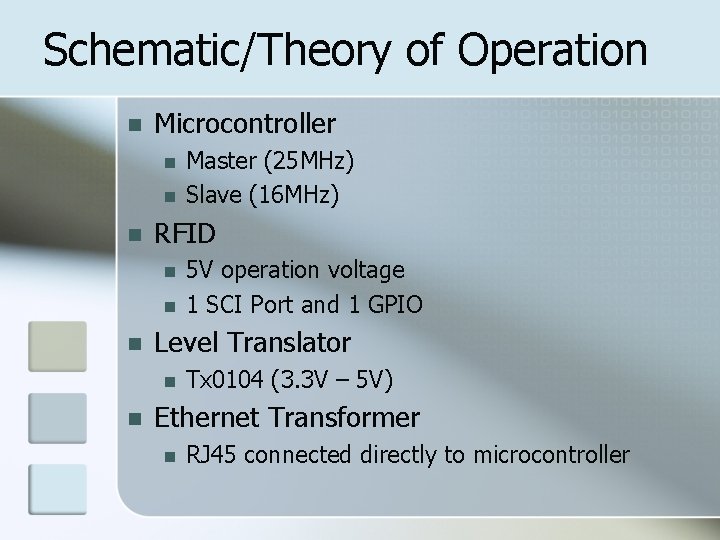

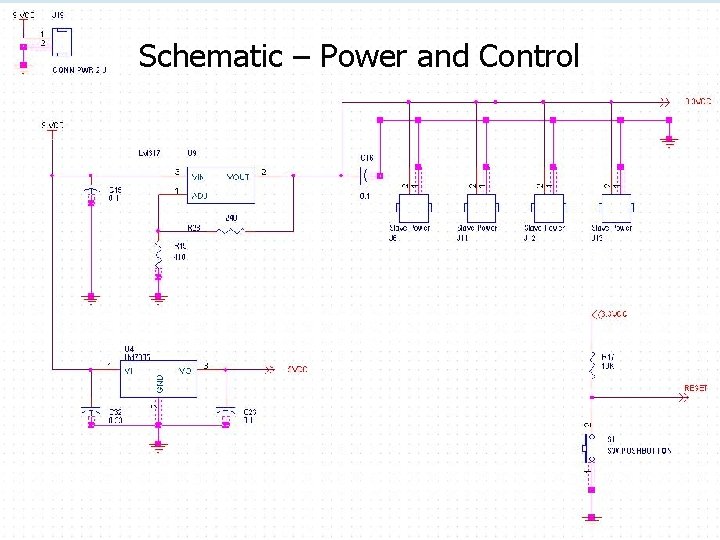

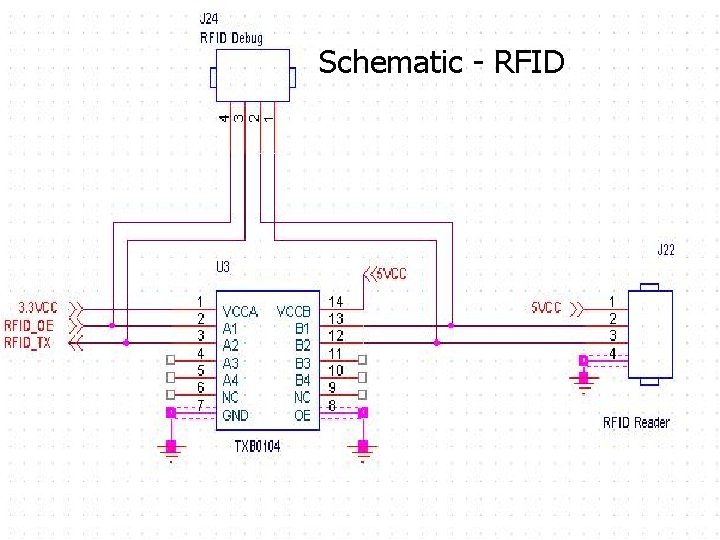

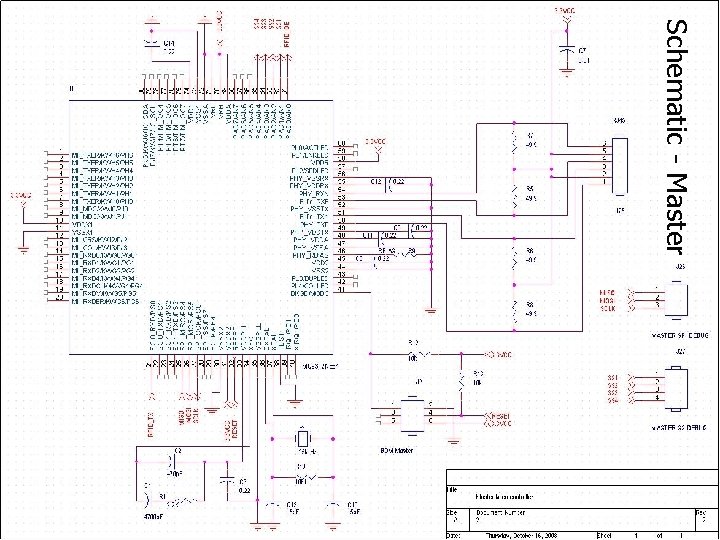

Schematic/Theory of Operation n Microcontroller n n n RFID n n n 5 V operation voltage 1 SCI Port and 1 GPIO Level Translator n n Master (25 MHz) Slave (16 MHz) Tx 0104 (3. 3 V – 5 V) Ethernet Transformer n RJ 45 connected directly to microcontroller

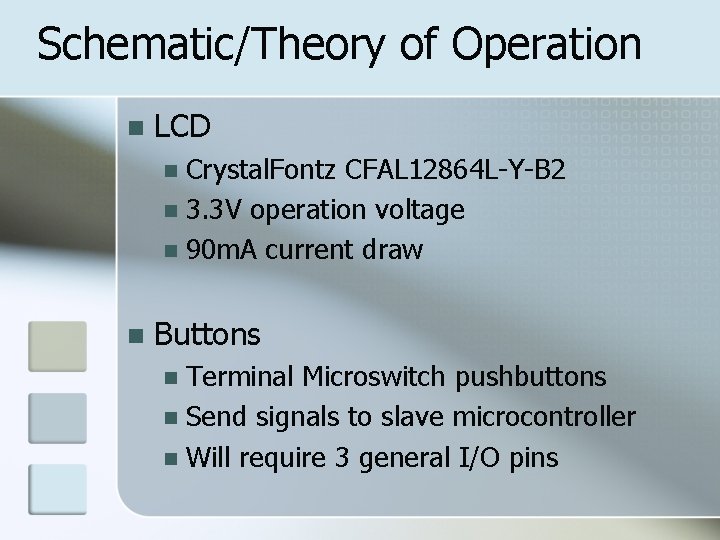

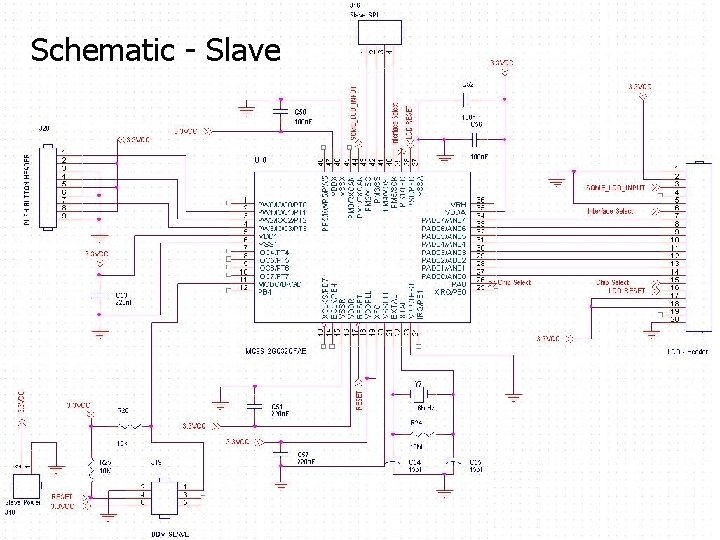

Schematic/Theory of Operation n LCD Crystal. Fontz CFAL 12864 L-Y-B 2 n 3. 3 V operation voltage n 90 m. A current draw n n Buttons Terminal Microswitch pushbuttons n Send signals to slave microcontroller n Will require 3 general I/O pins n

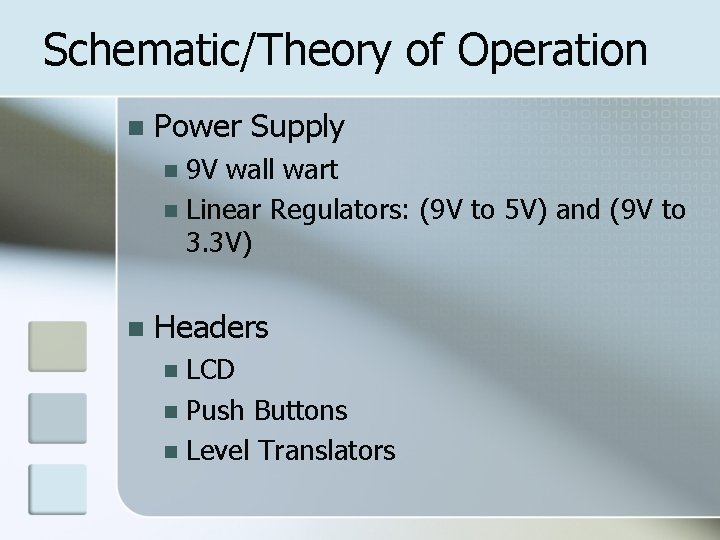

Schematic/Theory of Operation n Power Supply 9 V wall wart n Linear Regulators: (9 V to 5 V) and (9 V to 3. 3 V) n n Headers LCD n Push Buttons n Level Translators n

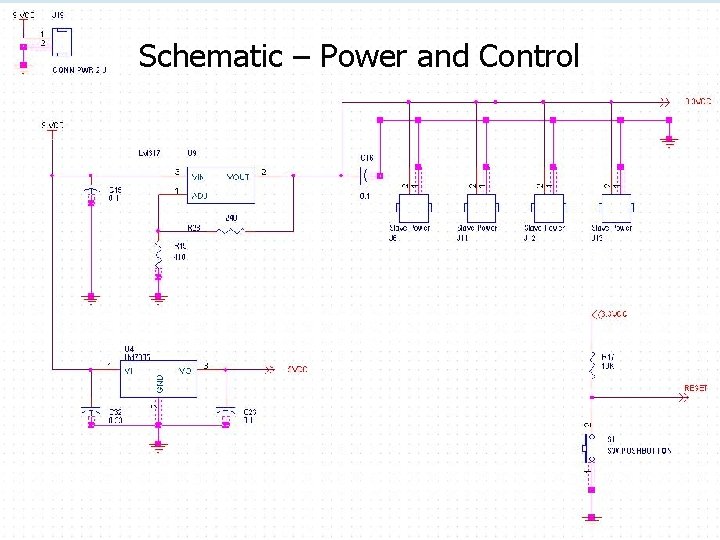

Schematic – Power and Control

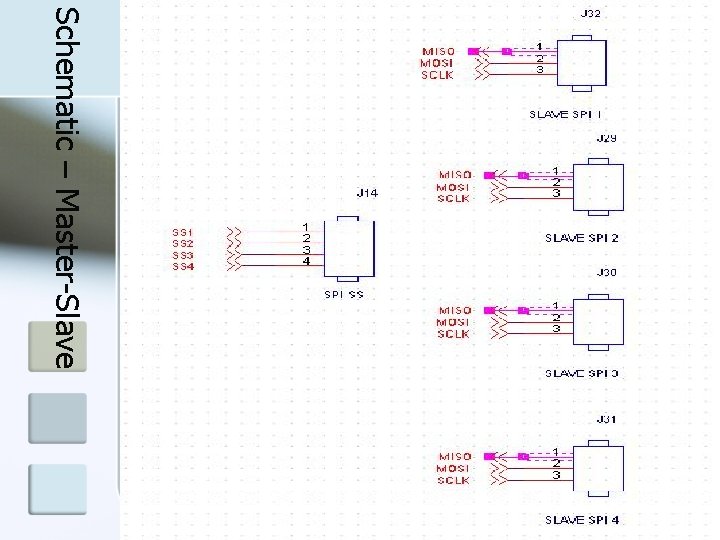

Schematic – Master-Slave

Schematic - RFID

Schematic - Master

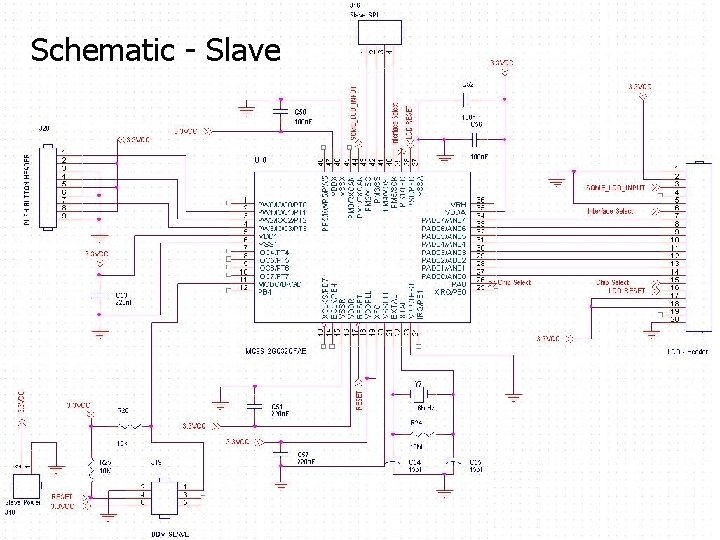

Schematic - Slave

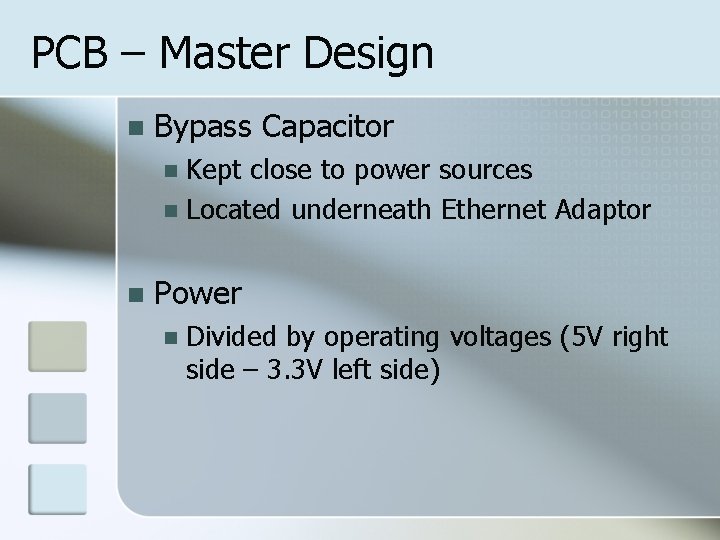

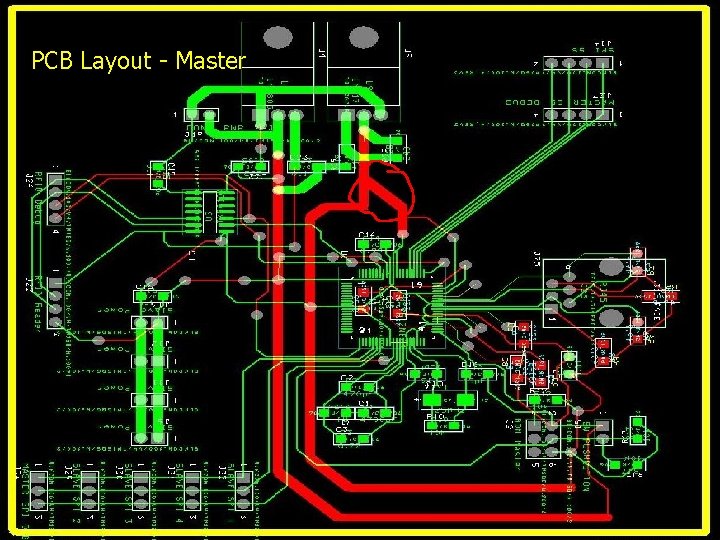

PCB – Master Design n Bypass Capacitor Kept close to power sources n Located underneath Ethernet Adaptor n n Power n Divided by operating voltages (5 V right side – 3. 3 V left side)

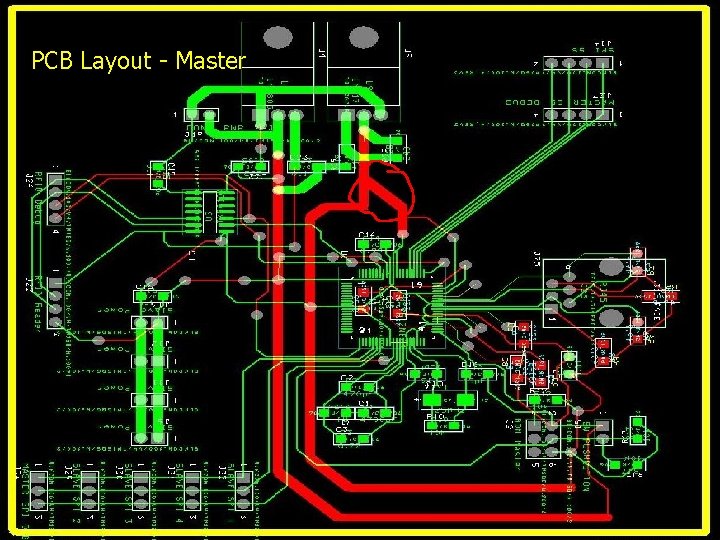

PCB Layout - Master

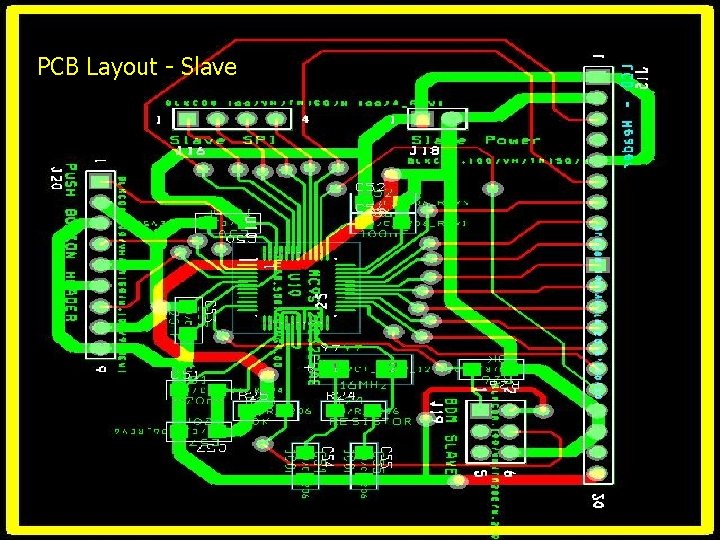

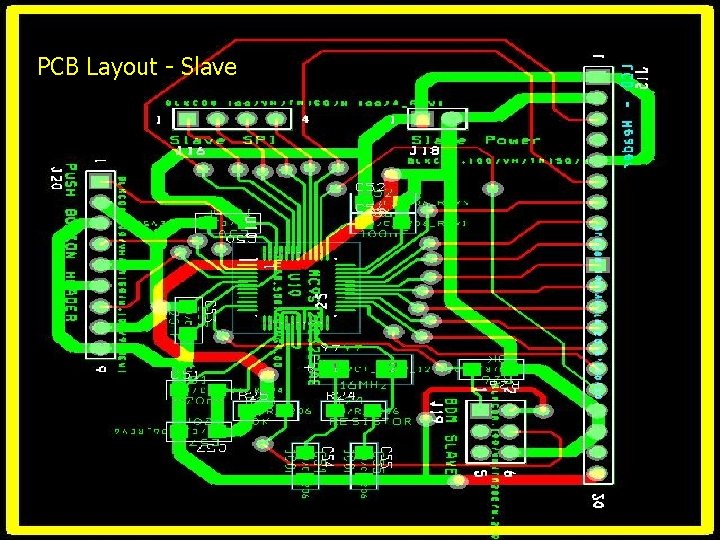

PCB – Slave Design n Bypass Capacitor n n Kept close to power sources Headers n Placed around board edges for easy access

PCB Layout - Slave

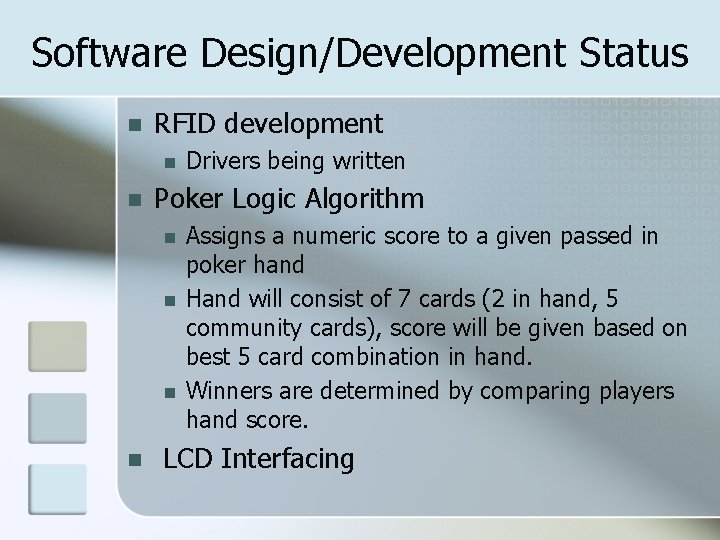

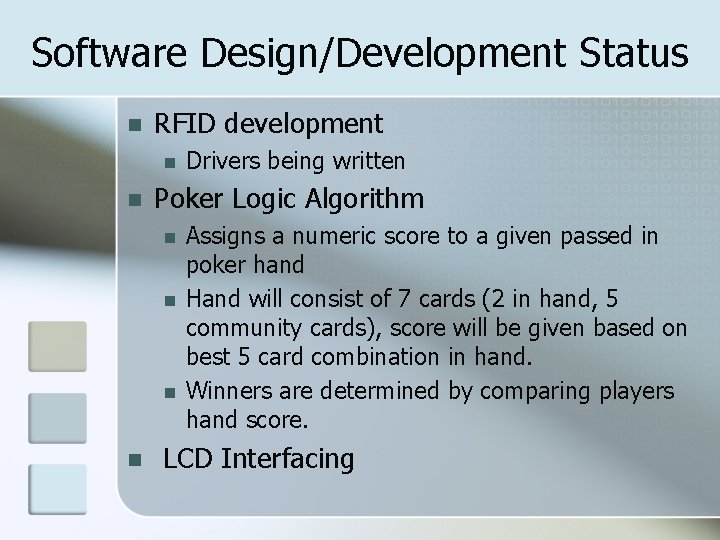

Software Design/Development Status n RFID development n n Poker Logic Algorithm n n Drivers being written Assigns a numeric score to a given passed in poker hand Hand will consist of 7 cards (2 in hand, 5 community cards), score will be given based on best 5 card combination in hand. Winners are determined by comparing players hand score. LCD Interfacing

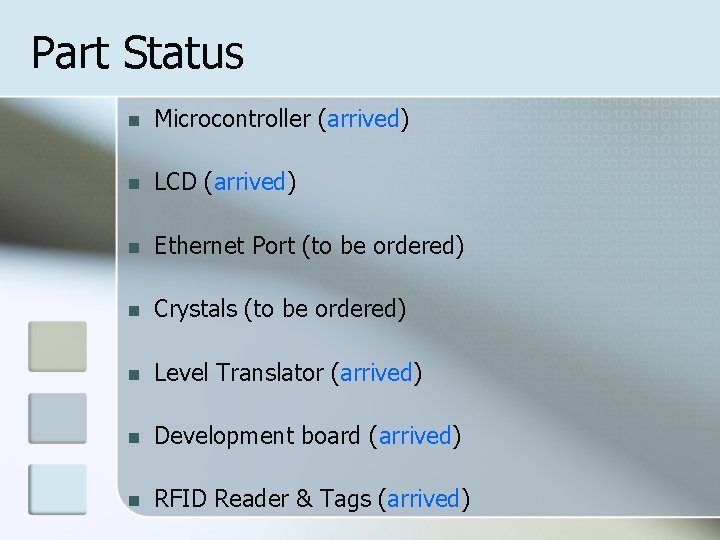

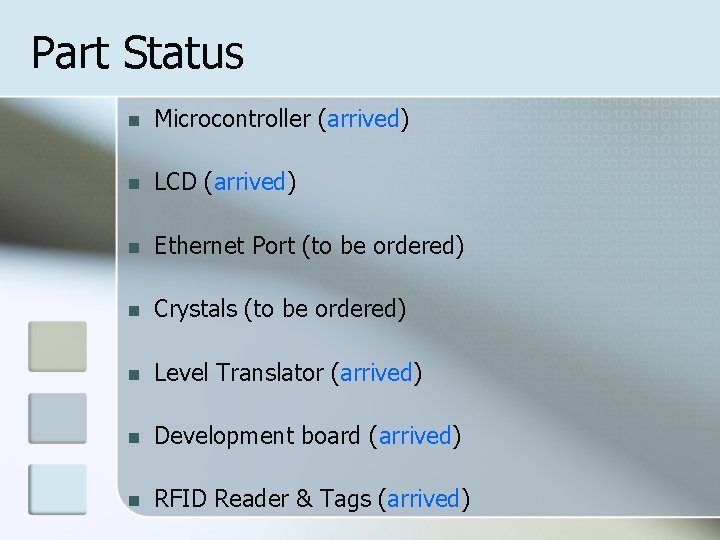

Part Status n Microcontroller (arrived) n LCD (arrived) n Ethernet Port (to be ordered) n Crystals (to be ordered) n Level Translator (arrived) n Development board (arrived) n RFID Reader & Tags (arrived)

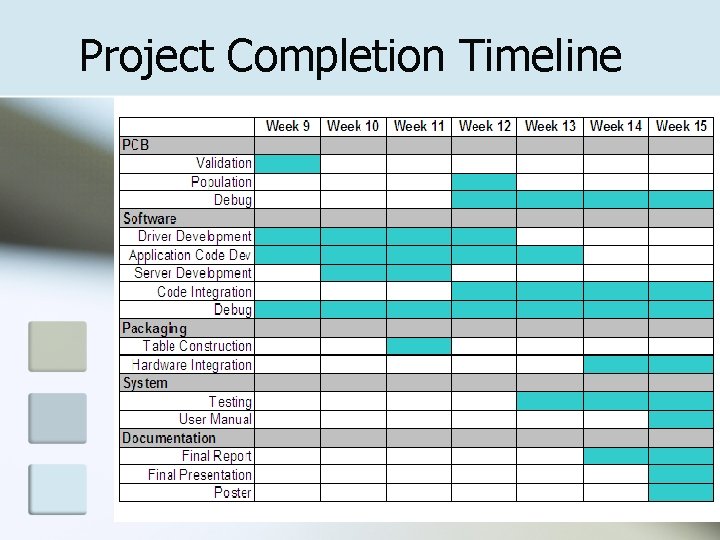

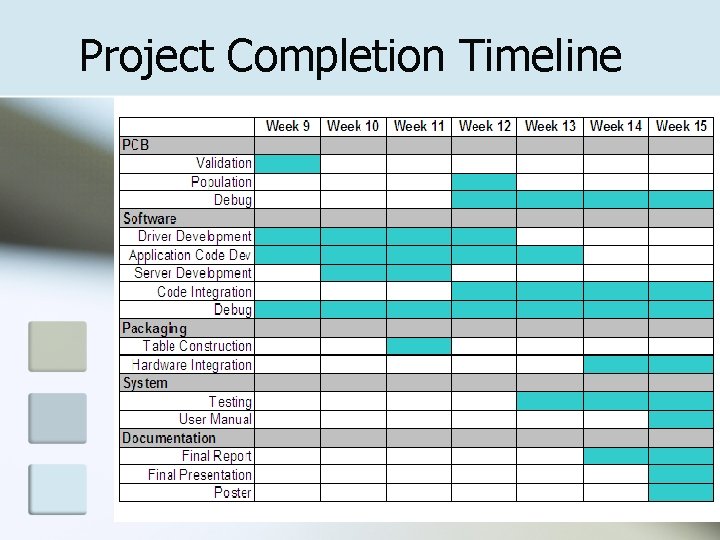

Project Completion Timeline

Questions