ECE 434 Advanced Digital System L 14 Electrical

- Slides: 39

ECE 434 Advanced Digital System L 14 Electrical and Computer Engineering University of Western Ontario

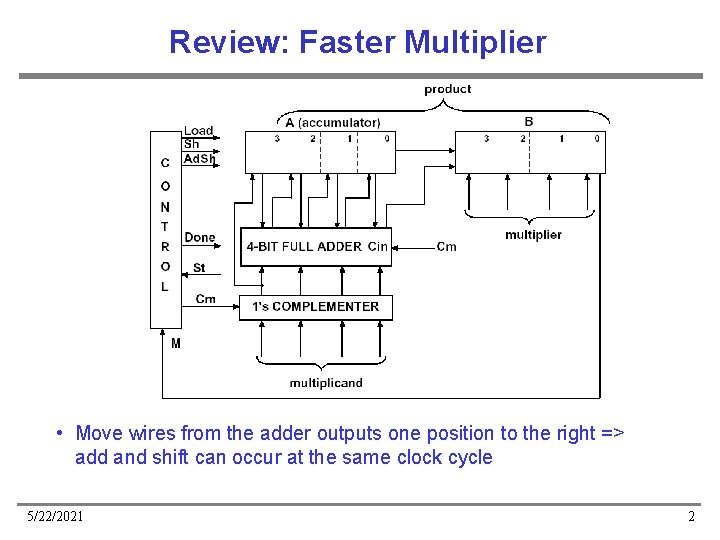

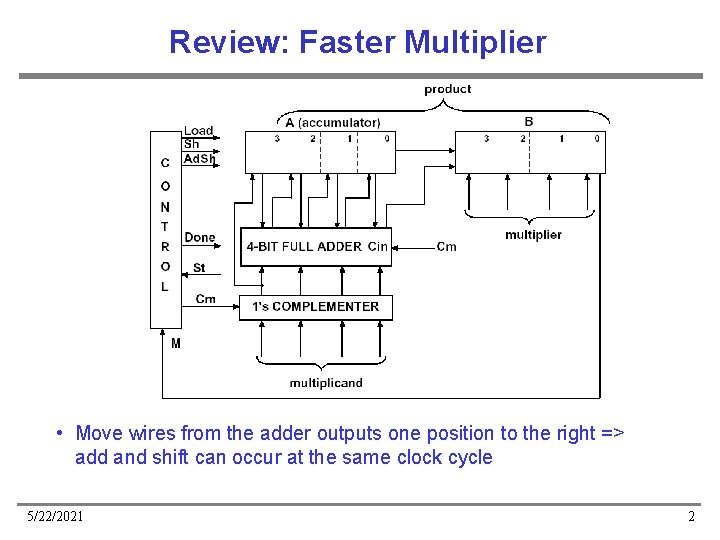

Review: Faster Multiplier • Move wires from the adder outputs one position to the right => add and shift can occur at the same clock cycle 5/22/2021 2

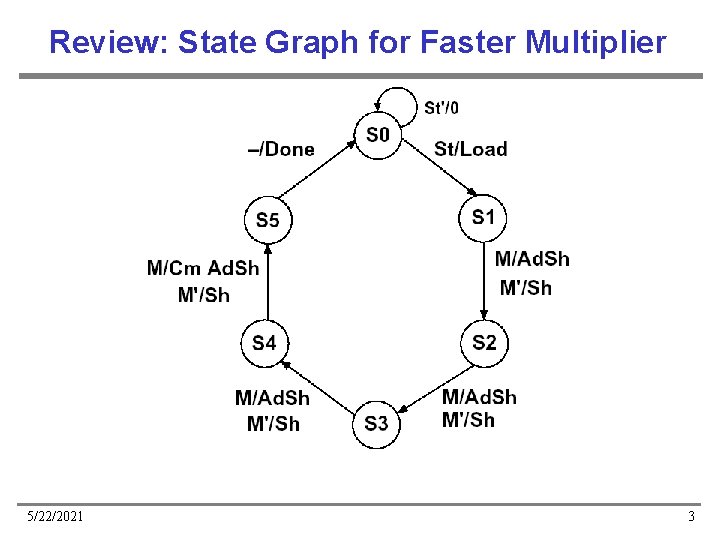

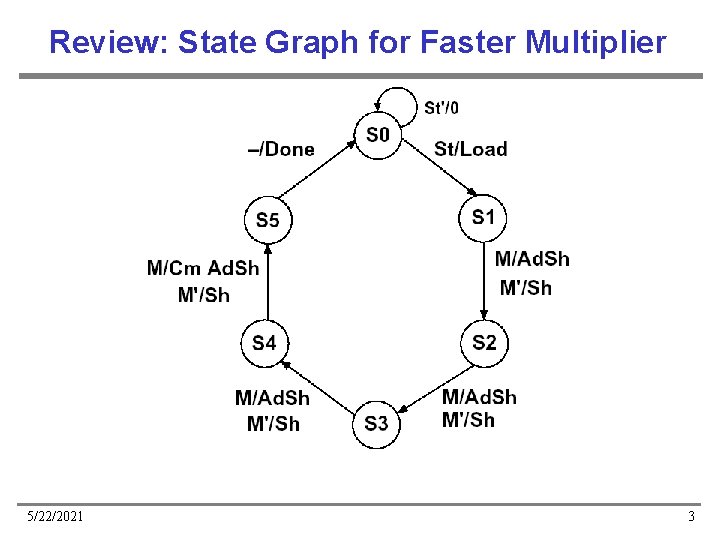

Review: State Graph for Faster Multiplier 5/22/2021 3

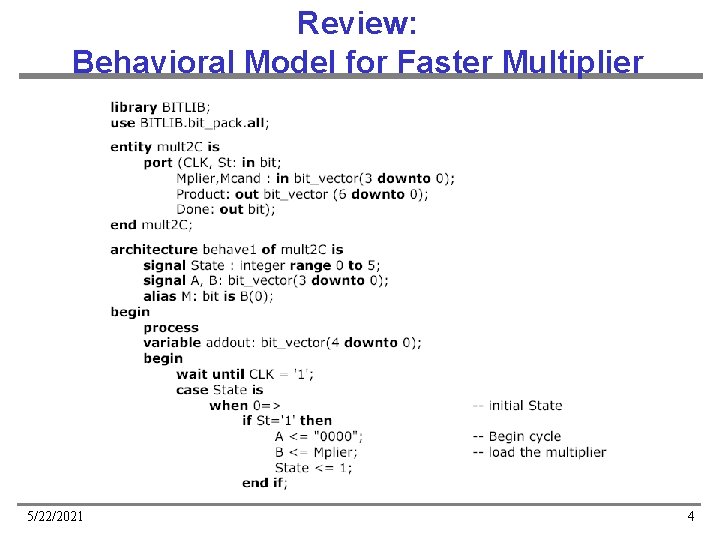

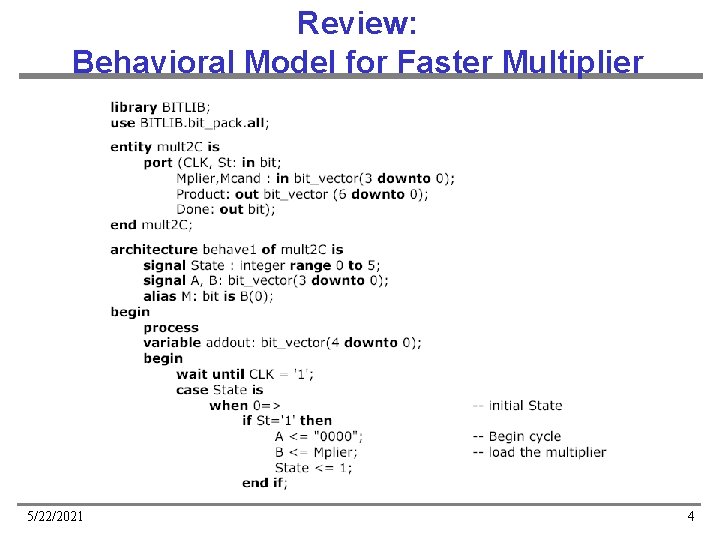

Review: Behavioral Model for Faster Multiplier 5/22/2021 4

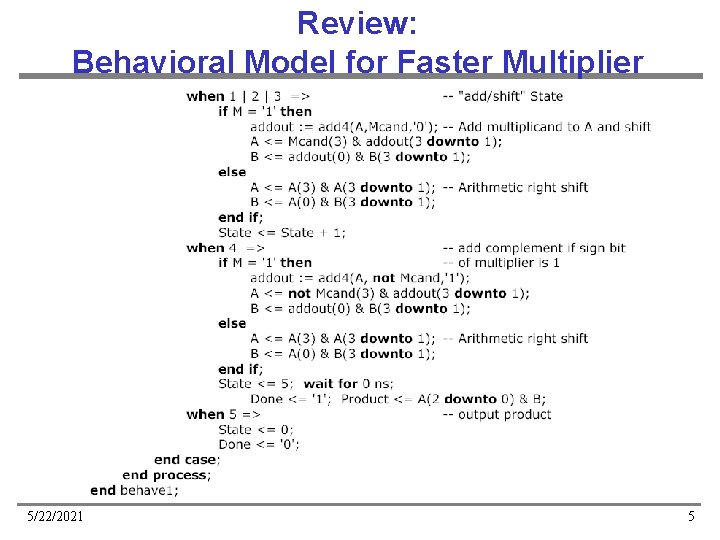

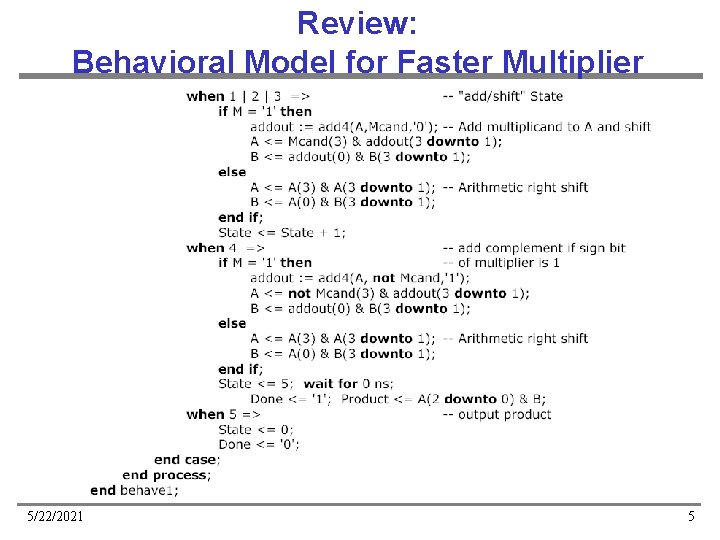

Review: Behavioral Model for Faster Multiplier 5/22/2021 5

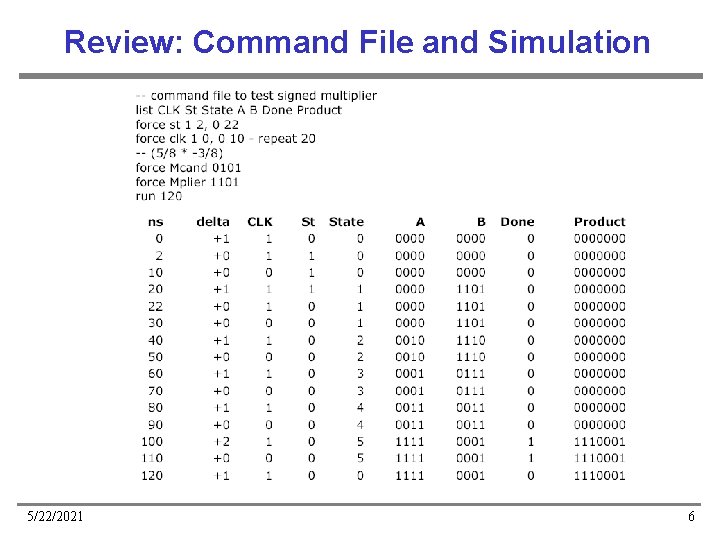

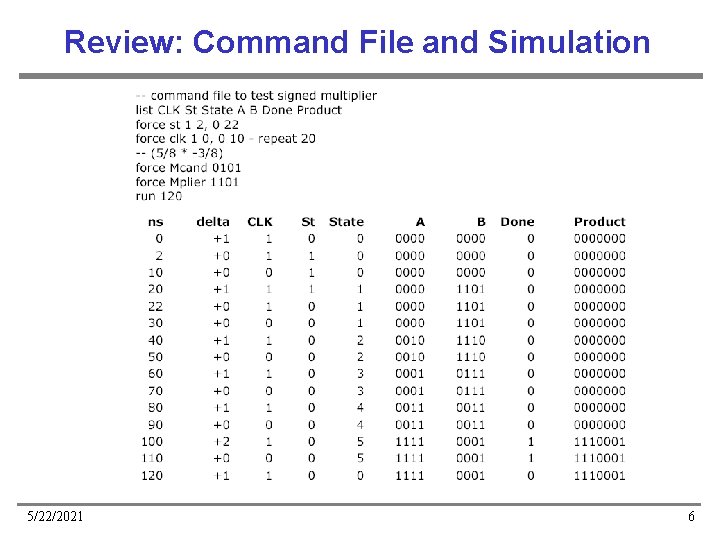

Review: Command File and Simulation 5/22/2021 6

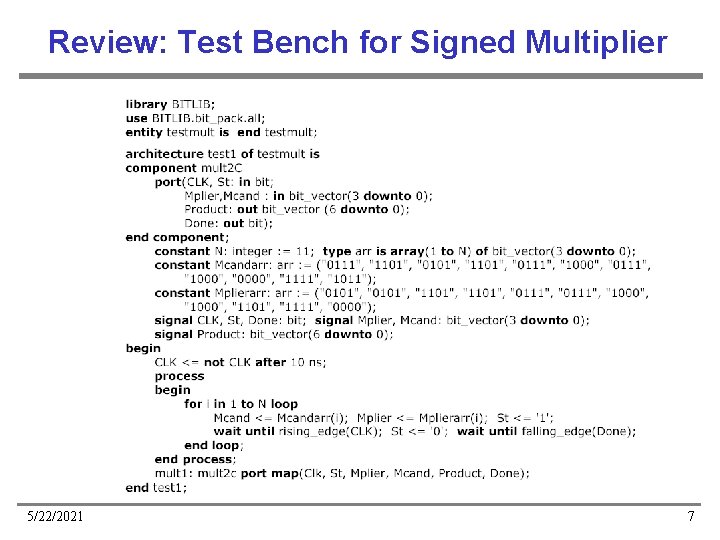

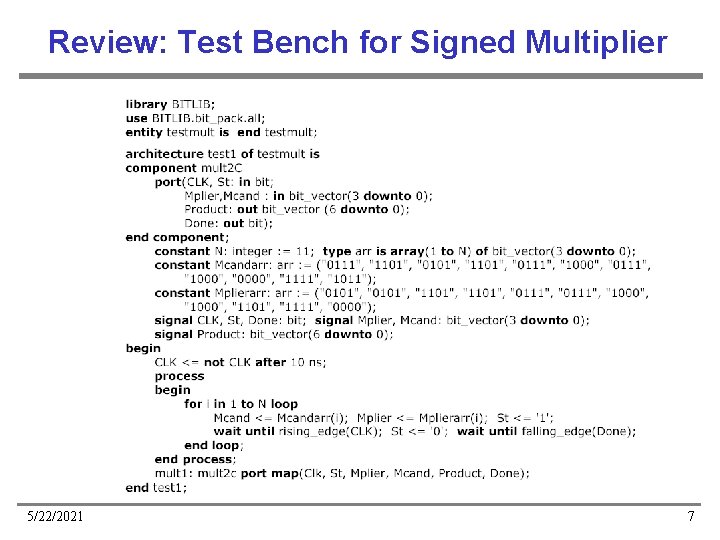

Review: Test Bench for Signed Multiplier 5/22/2021 7

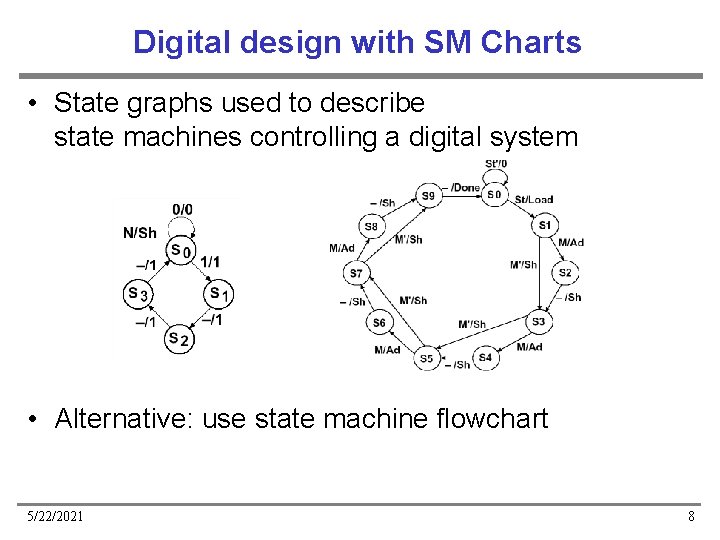

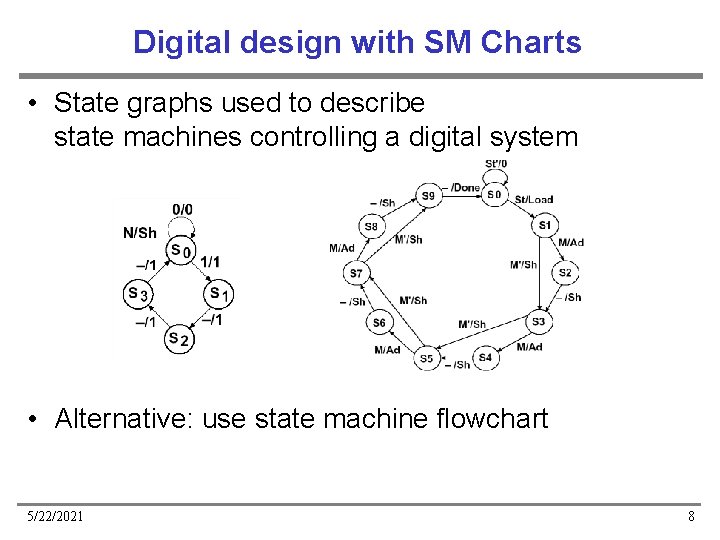

Digital design with SM Charts • State graphs used to describe state machines controlling a digital system • Alternative: use state machine flowchart 5/22/2021 8

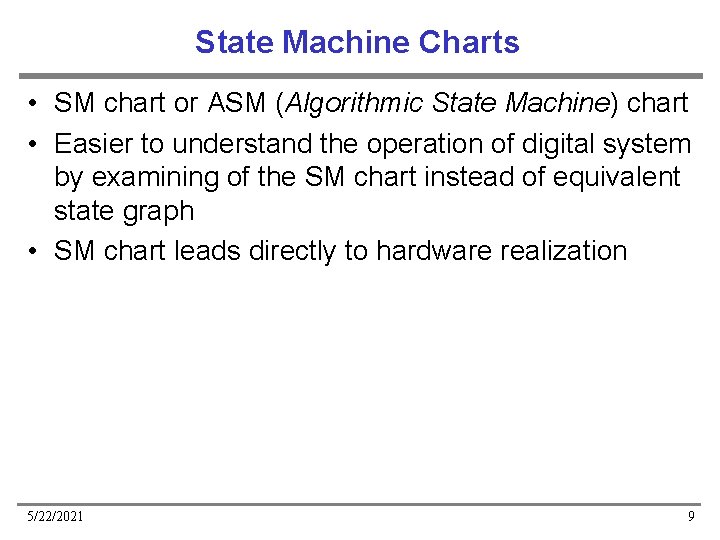

State Machine Charts • SM chart or ASM (Algorithmic State Machine) chart • Easier to understand the operation of digital system by examining of the SM chart instead of equivalent state graph • SM chart leads directly to hardware realization 5/22/2021 9

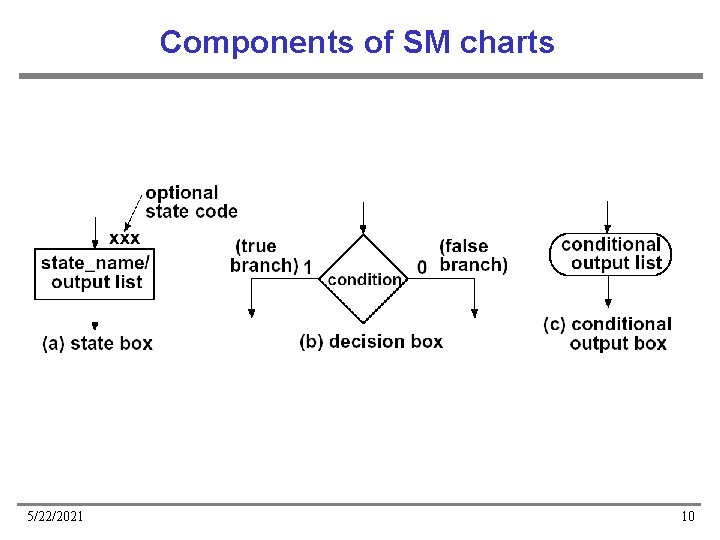

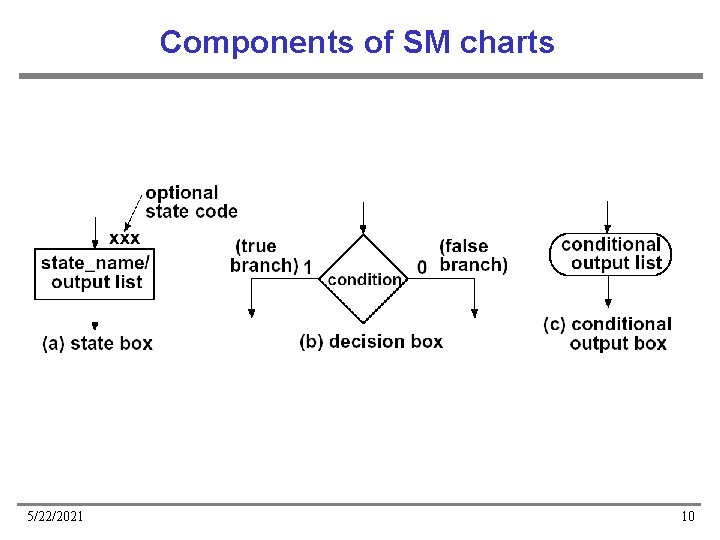

Components of SM charts 5/22/2021 10

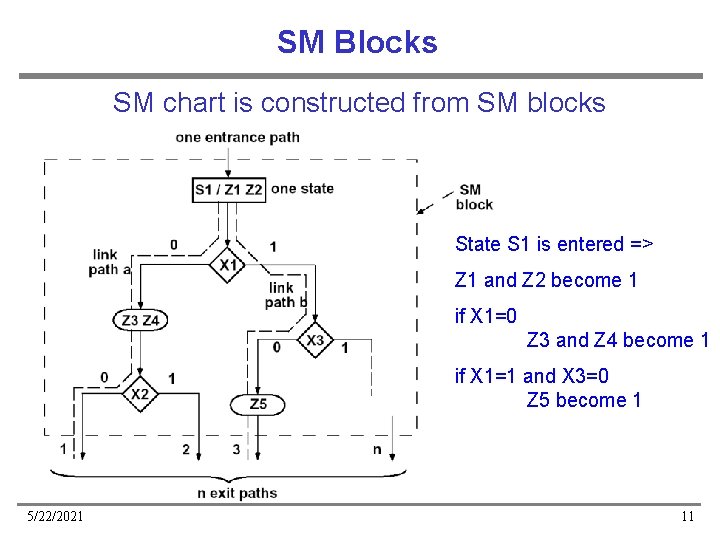

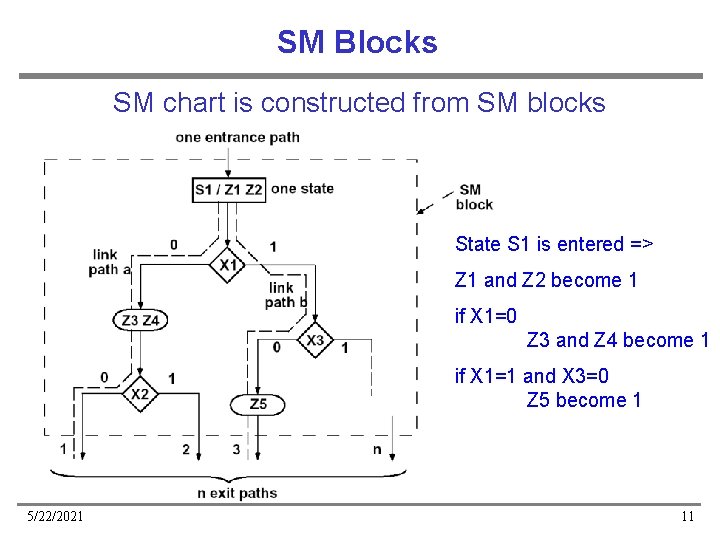

SM Blocks SM chart is constructed from SM blocks State S 1 is entered => Z 1 and Z 2 become 1 if X 1=0 Z 3 and Z 4 become 1 if X 1=1 and X 3=0 Z 5 become 1 5/22/2021 11

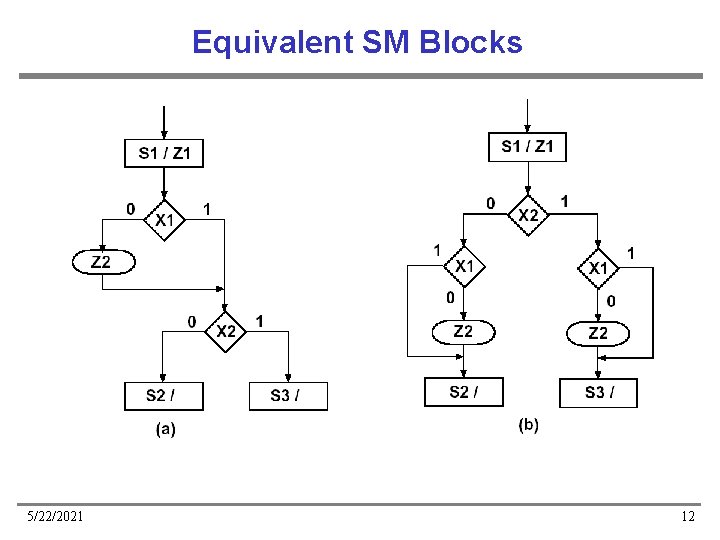

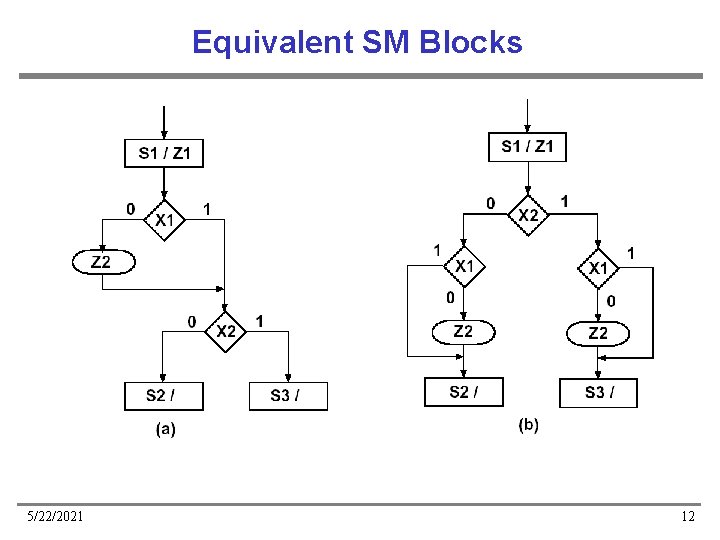

Equivalent SM Blocks 5/22/2021 12

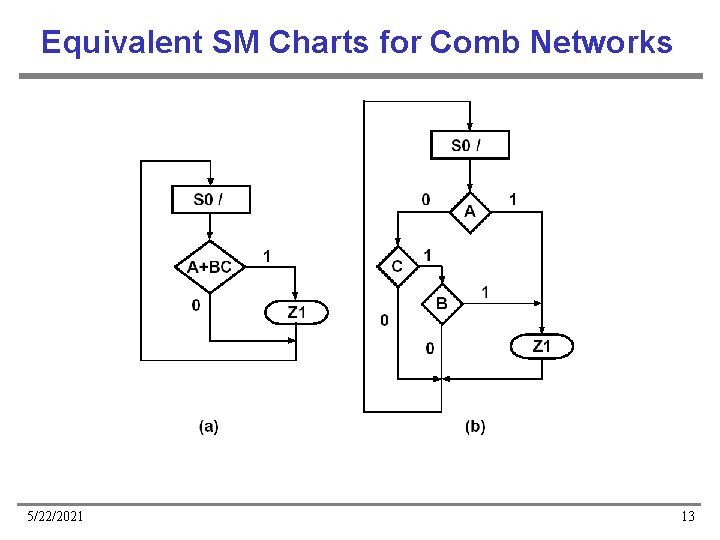

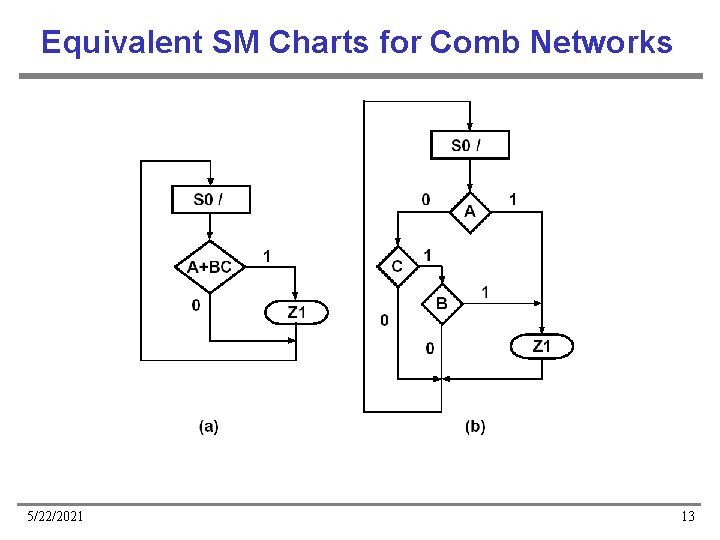

Equivalent SM Charts for Comb Networks 5/22/2021 13

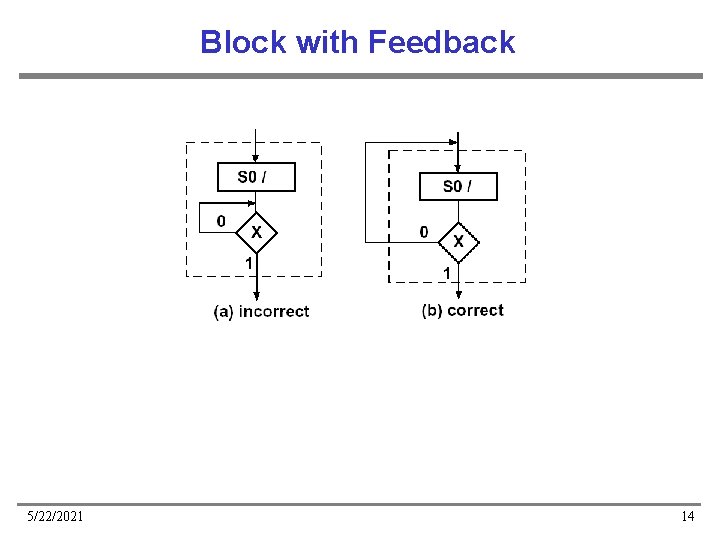

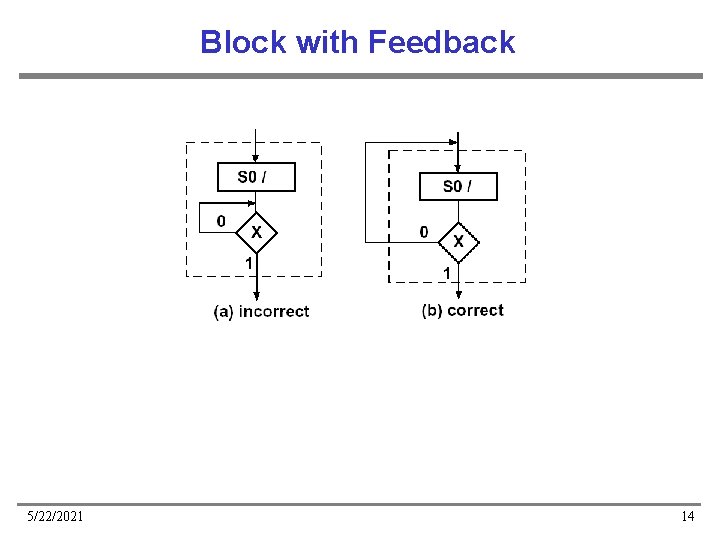

Block with Feedback 5/22/2021 14

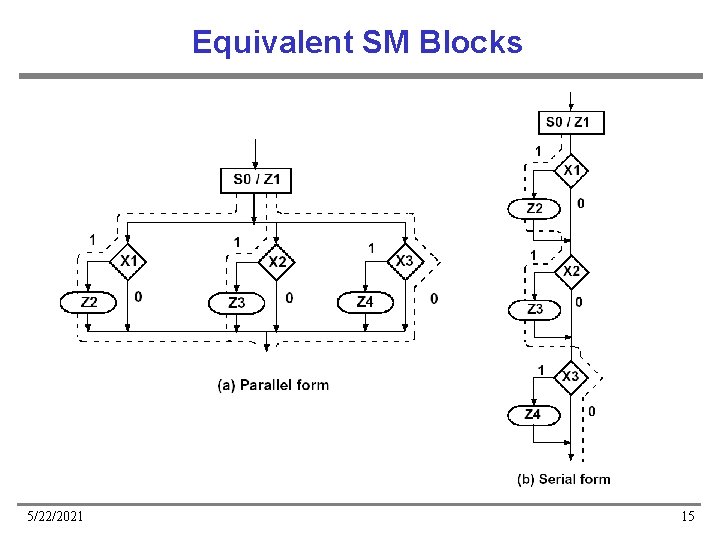

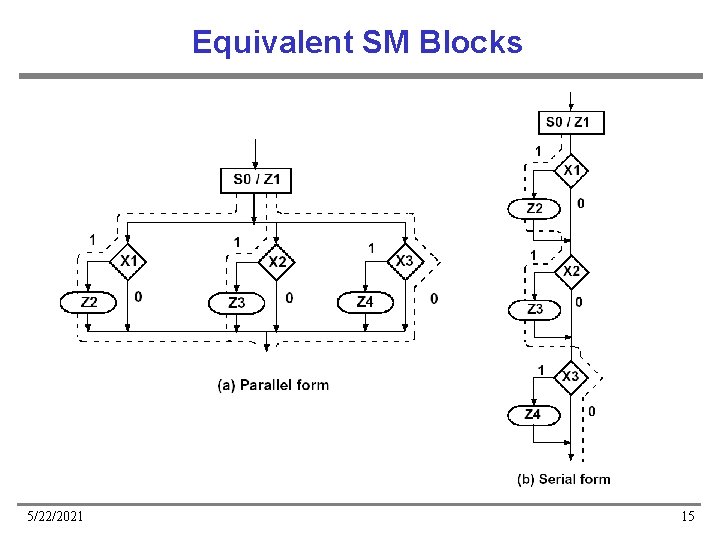

Equivalent SM Blocks 5/22/2021 15

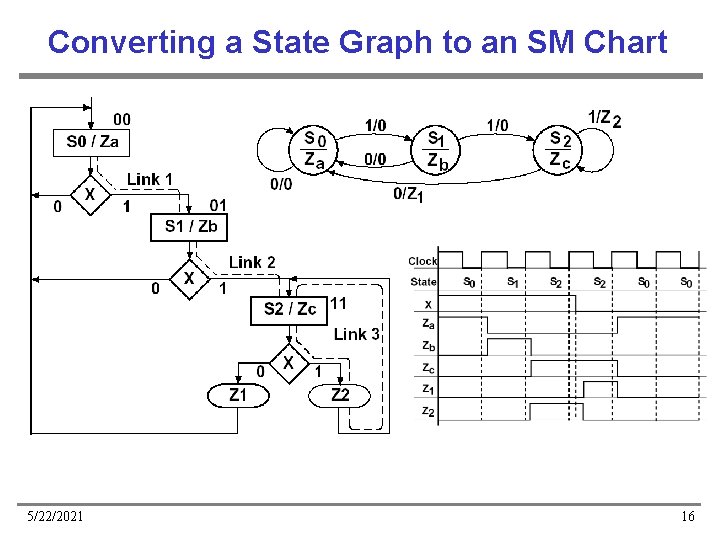

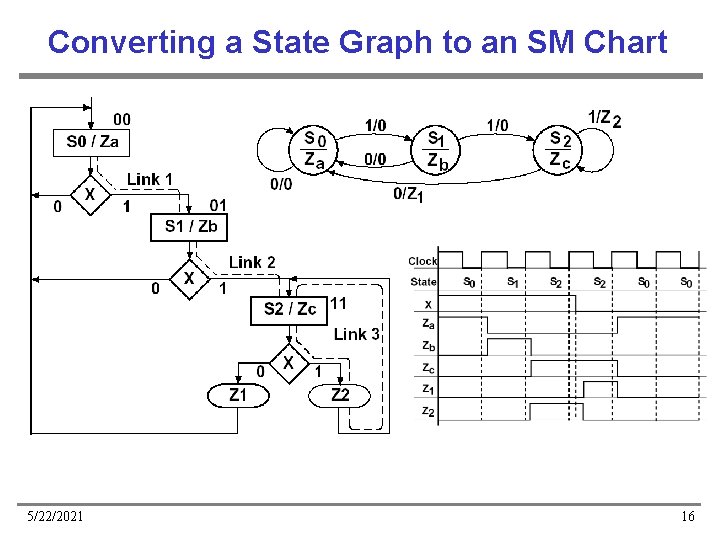

Converting a State Graph to an SM Chart 5/22/2021 16

Derivation of SM Charts • Binary Multiplier • Dice Game 5/22/2021 17

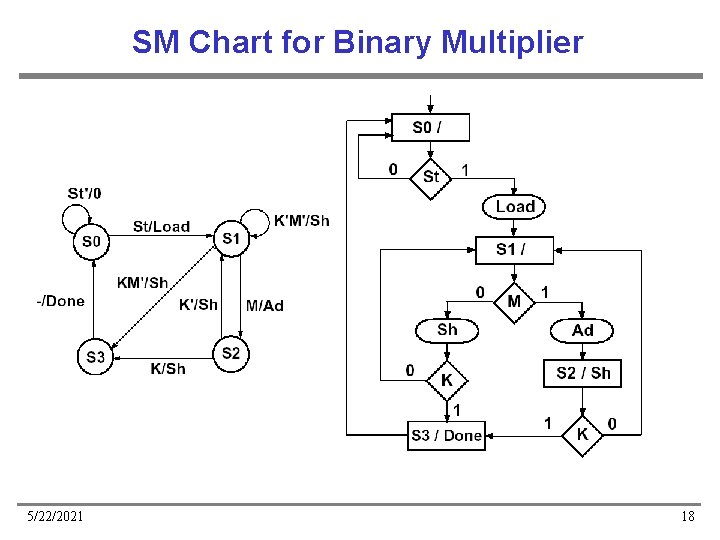

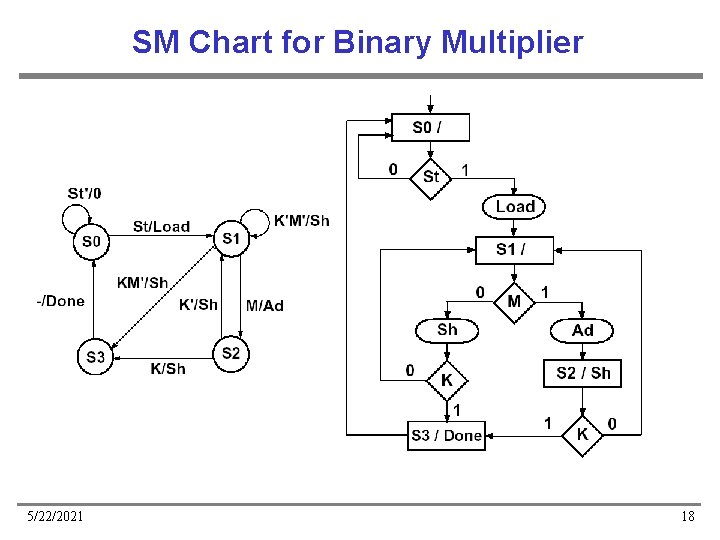

SM Chart for Binary Multiplier 5/22/2021 18

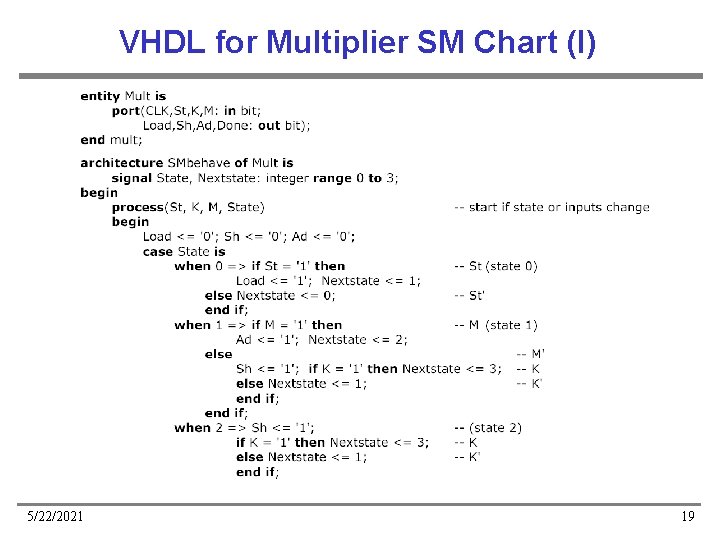

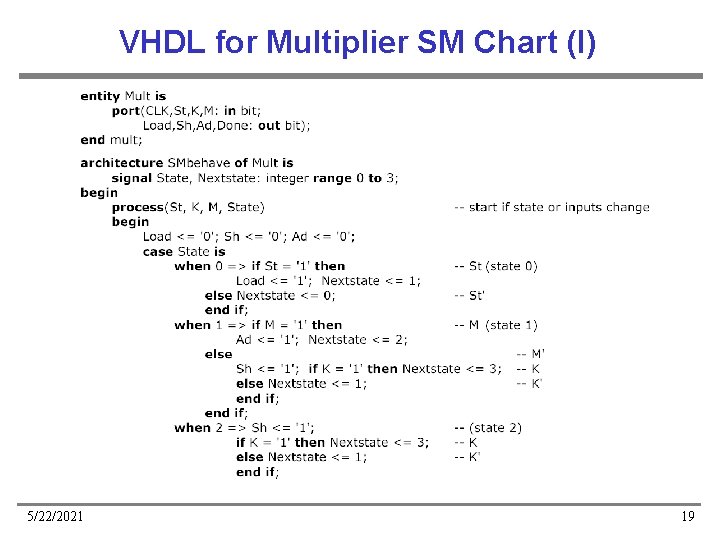

VHDL for Multiplier SM Chart (I) 5/22/2021 19

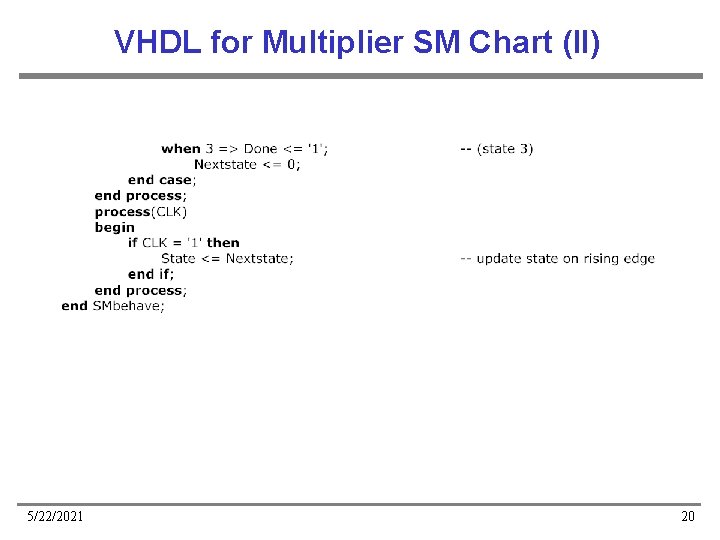

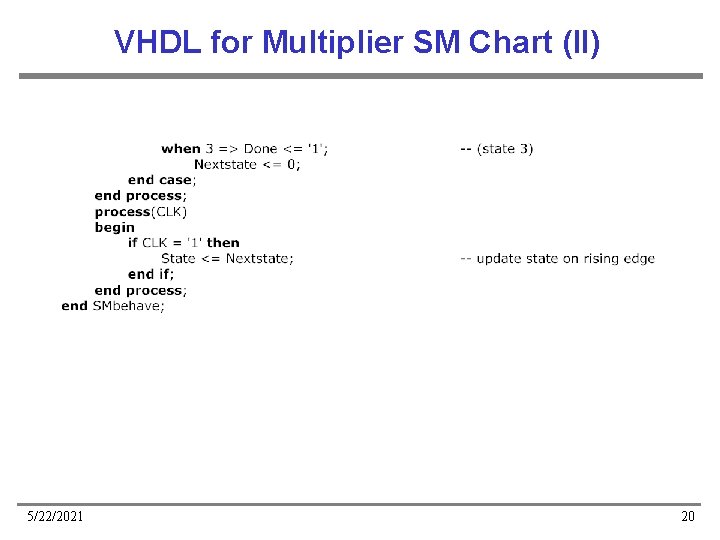

VHDL for Multiplier SM Chart (II) 5/22/2021 20

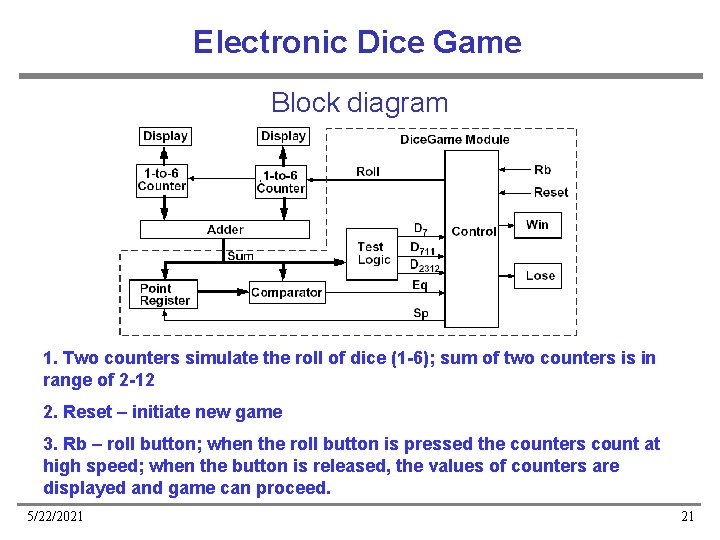

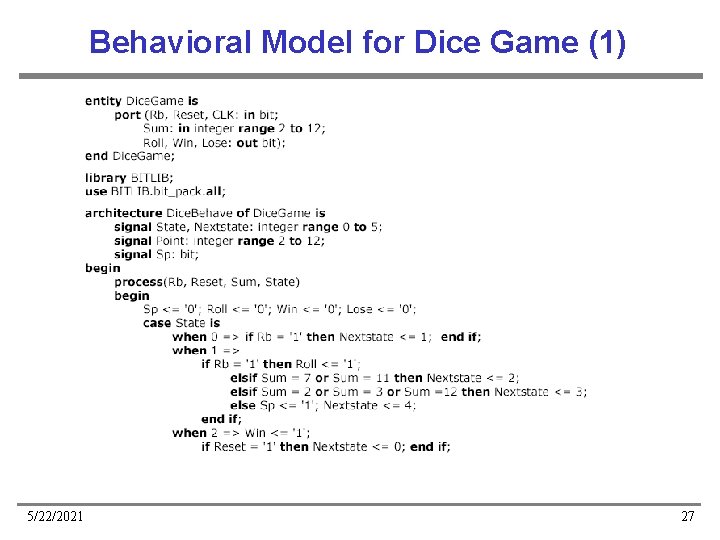

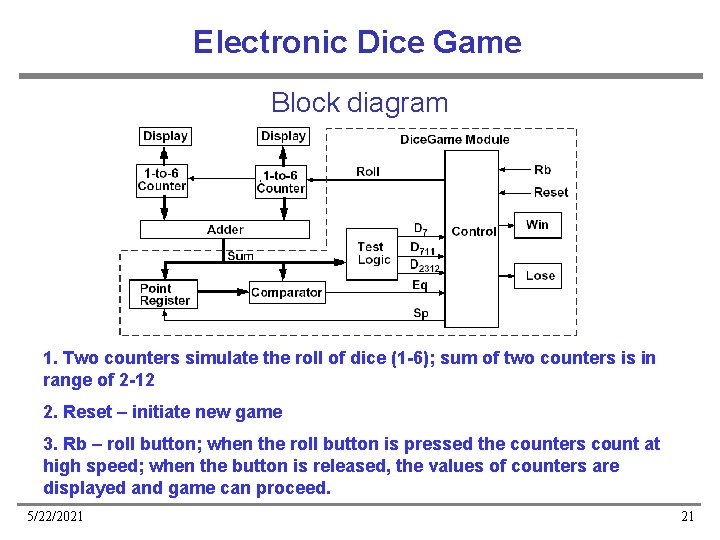

Electronic Dice Game Block diagram 1. Two counters simulate the roll of dice (1 -6); sum of two counters is in range of 2 -12 2. Reset – initiate new game 3. Rb – roll button; when the roll button is pressed the counters count at high speed; when the button is released, the values of counters are displayed and game can proceed. 5/22/2021 21

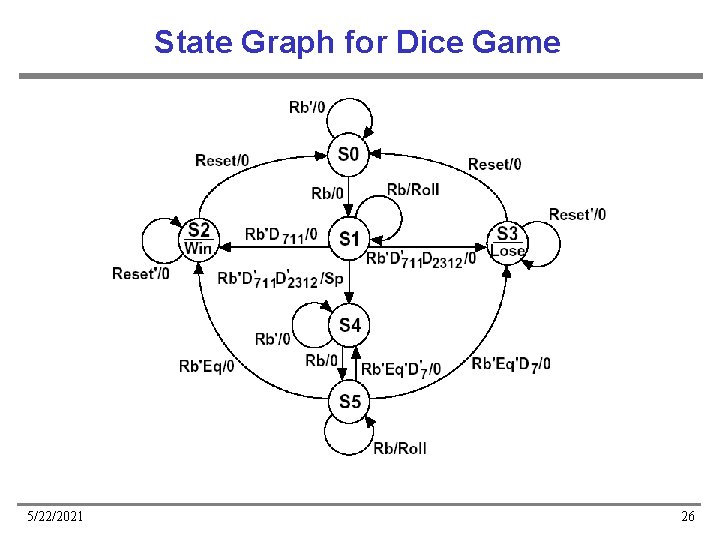

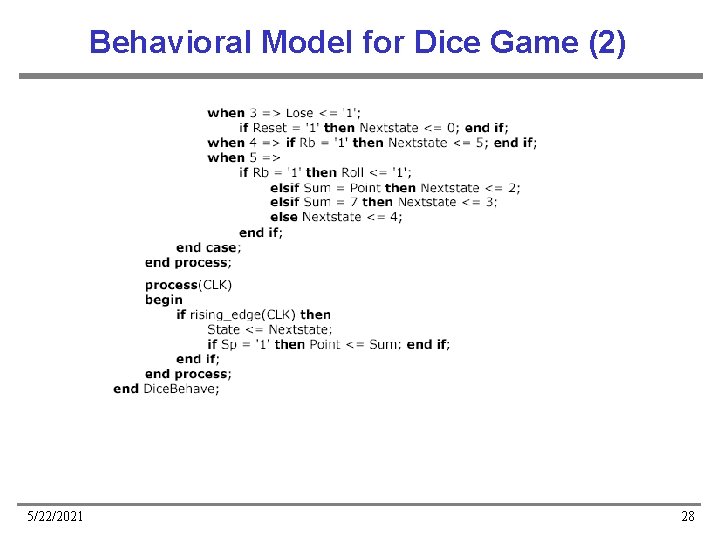

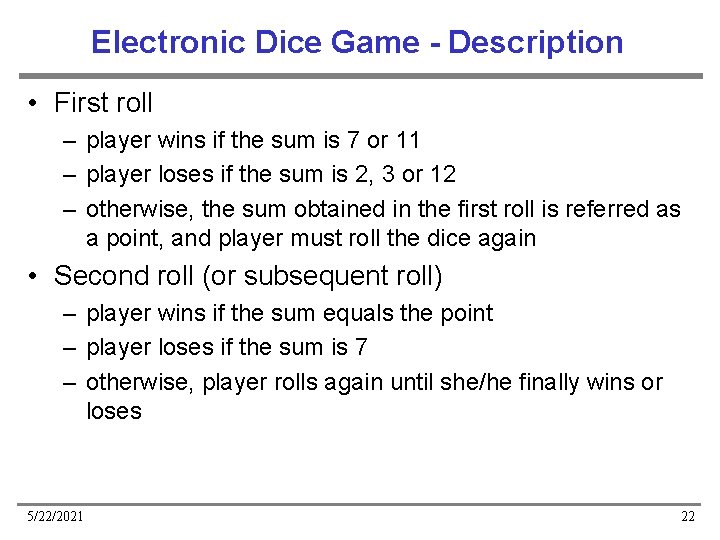

Electronic Dice Game - Description • First roll – player wins if the sum is 7 or 11 – player loses if the sum is 2, 3 or 12 – otherwise, the sum obtained in the first roll is referred as a point, and player must roll the dice again • Second roll (or subsequent roll) – player wins if the sum equals the point – player loses if the sum is 7 – otherwise, player rolls again until she/he finally wins or loses 5/22/2021 22

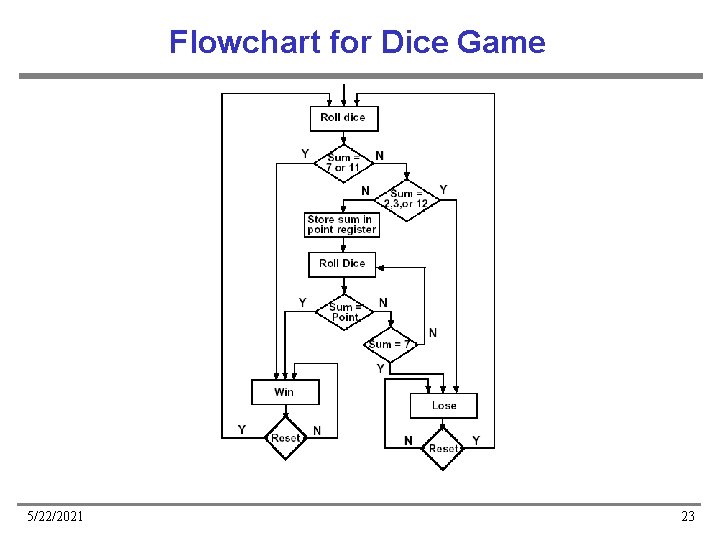

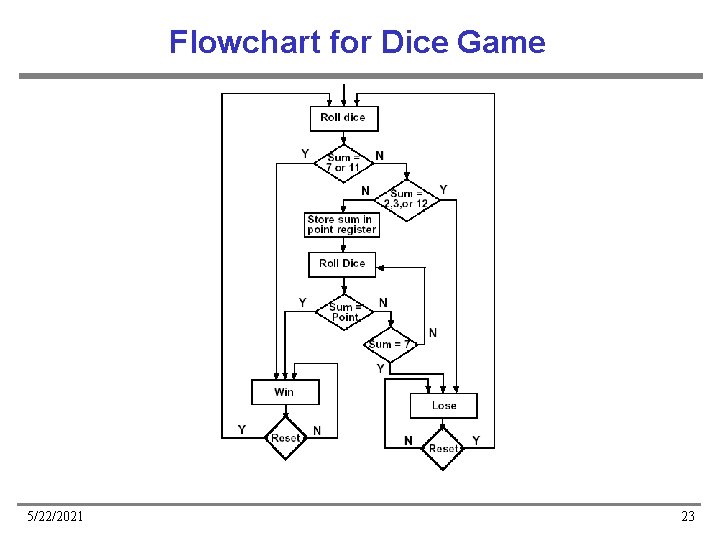

Flowchart for Dice Game 5/22/2021 23

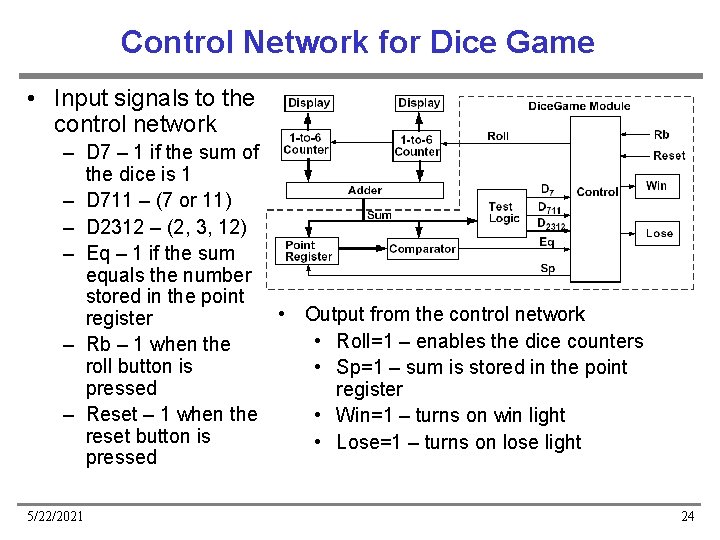

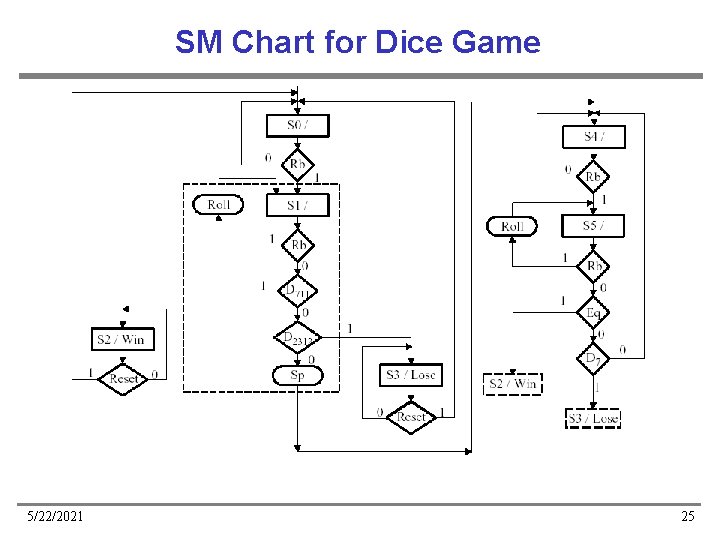

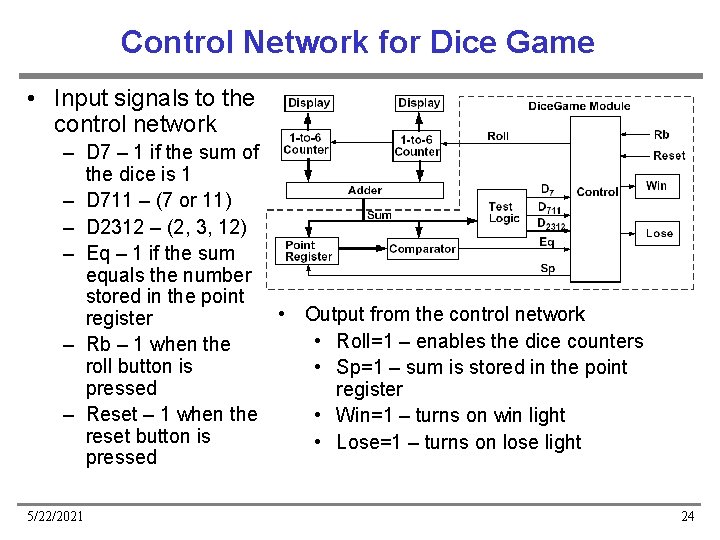

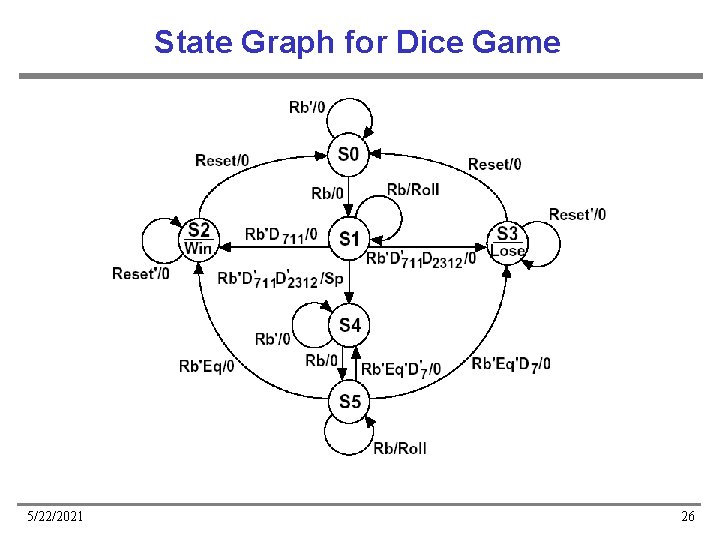

Control Network for Dice Game • Input signals to the control network – D 7 – 1 if the sum of the dice is 1 – D 711 – (7 or 11) – D 2312 – (2, 3, 12) – Eq – 1 if the sum equals the number stored in the point • Output from the control network register • Roll=1 – enables the dice counters – Rb – 1 when the roll button is • Sp=1 – sum is stored in the point pressed register – Reset – 1 when the • Win=1 – turns on win light reset button is • Lose=1 – turns on lose light pressed 5/22/2021 24

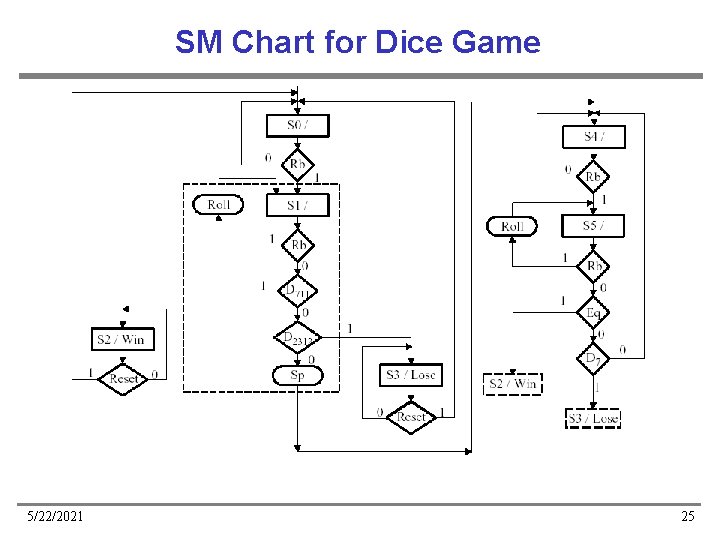

SM Chart for Dice Game 5/22/2021 25

State Graph for Dice Game 5/22/2021 26

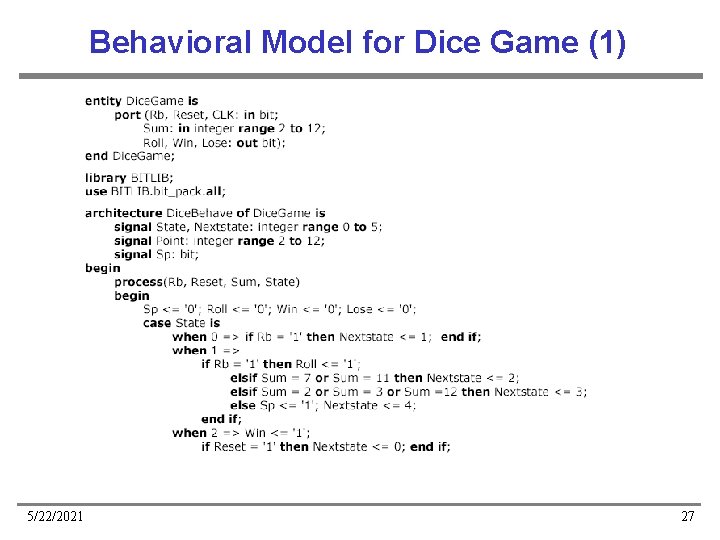

Behavioral Model for Dice Game (1) 5/22/2021 27

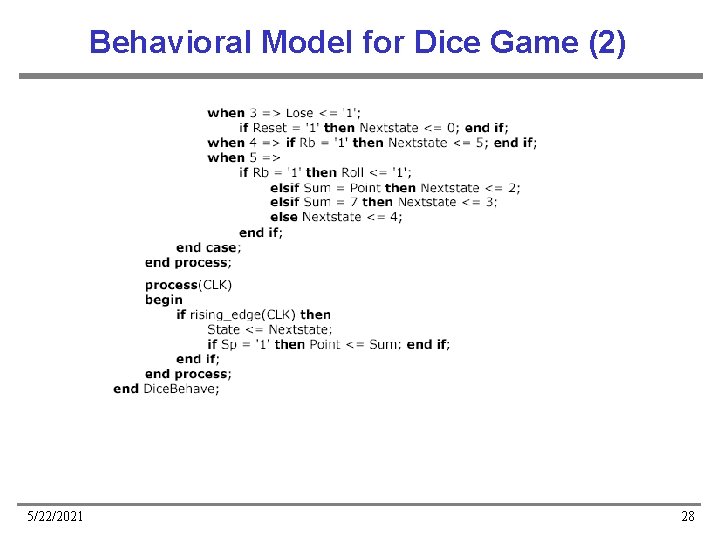

Behavioral Model for Dice Game (2) 5/22/2021 28

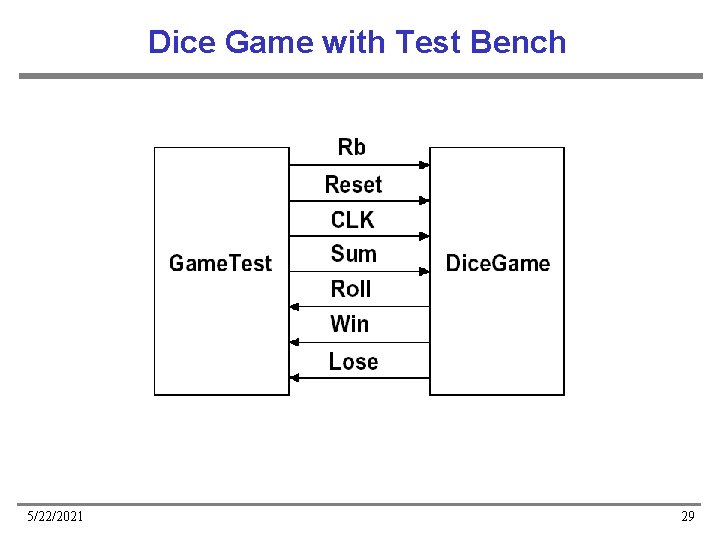

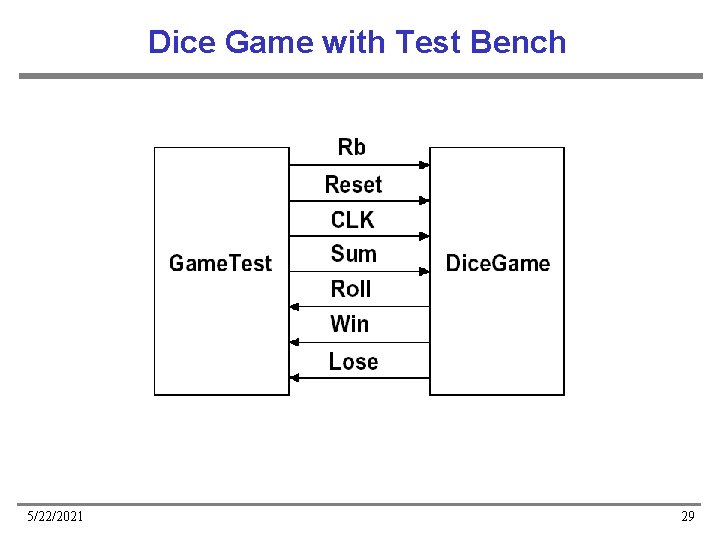

Dice Game with Test Bench 5/22/2021 29

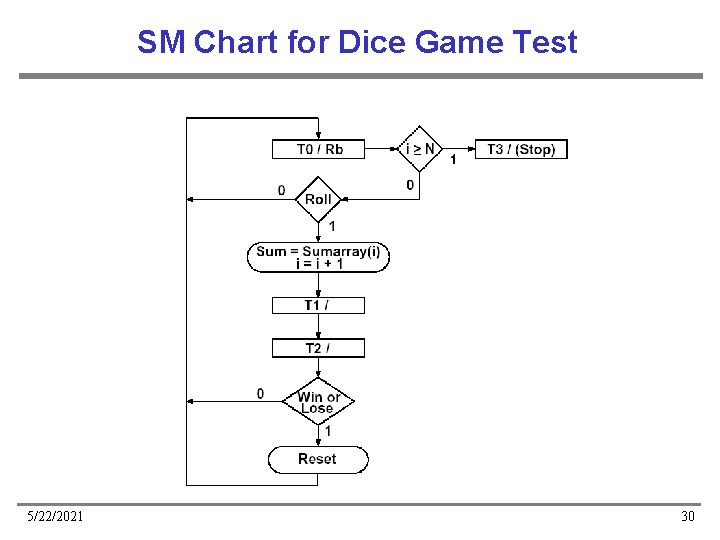

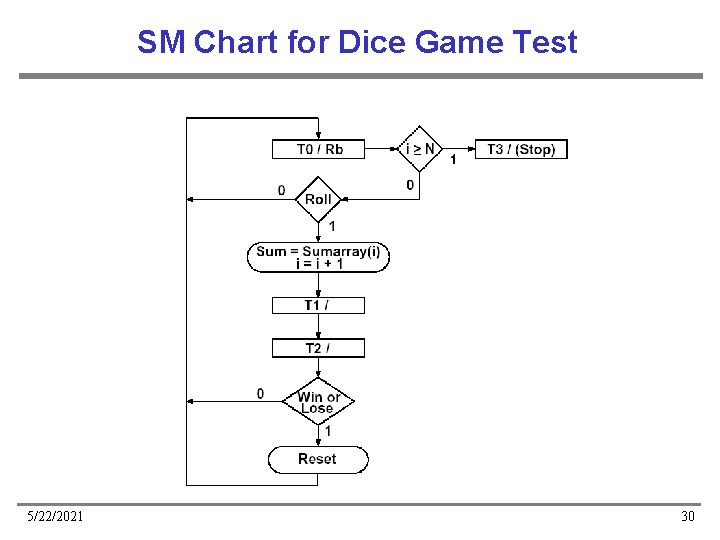

SM Chart for Dice Game Test 5/22/2021 30

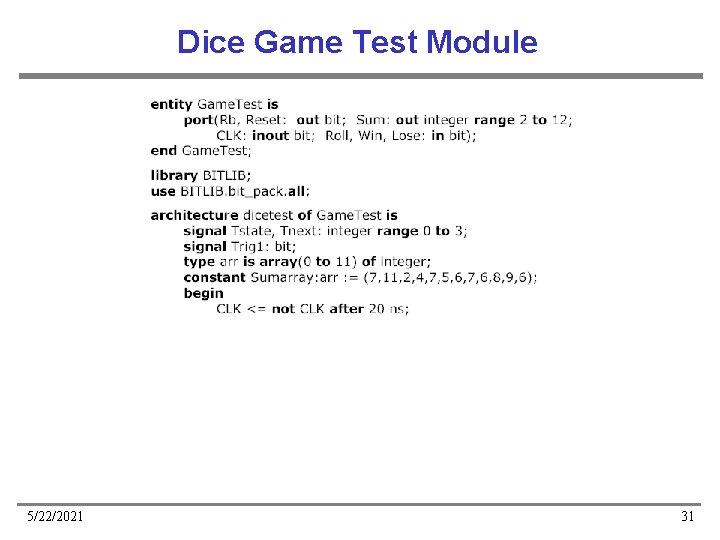

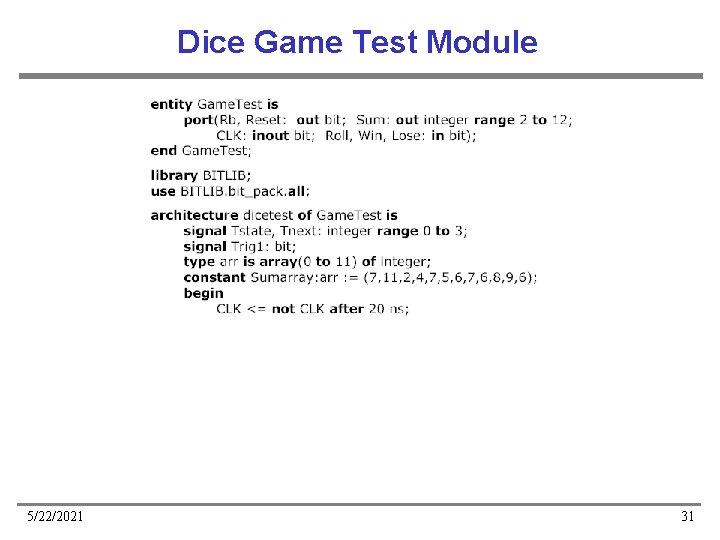

Dice Game Test Module 5/22/2021 31

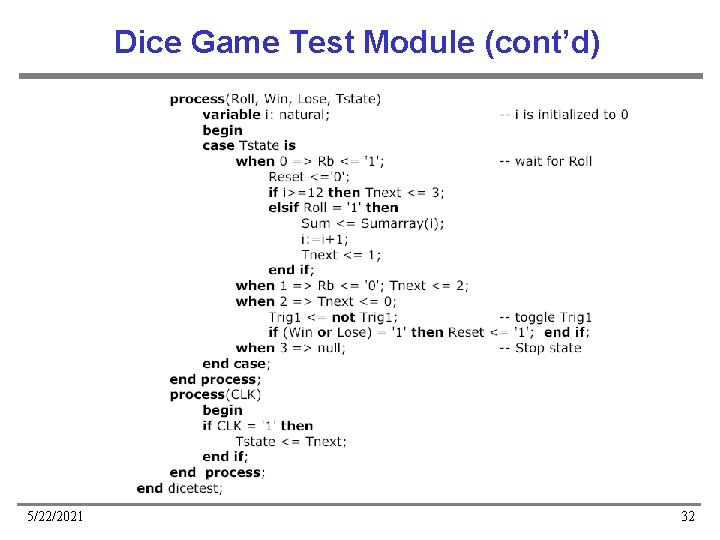

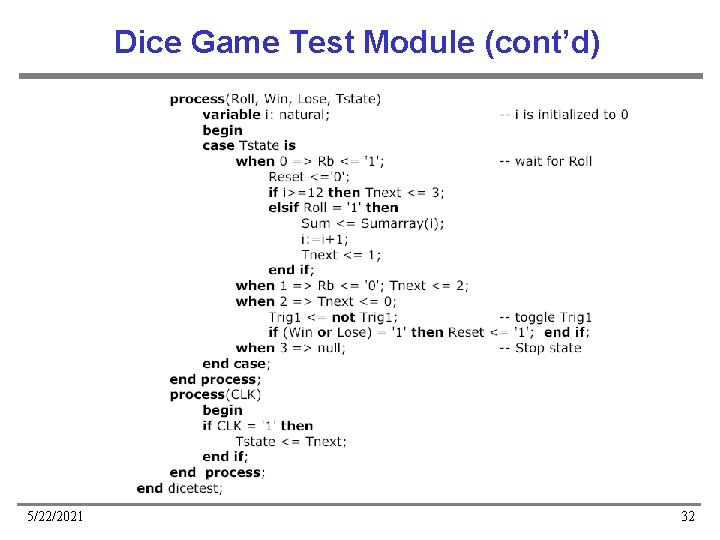

Dice Game Test Module (cont’d) 5/22/2021 32

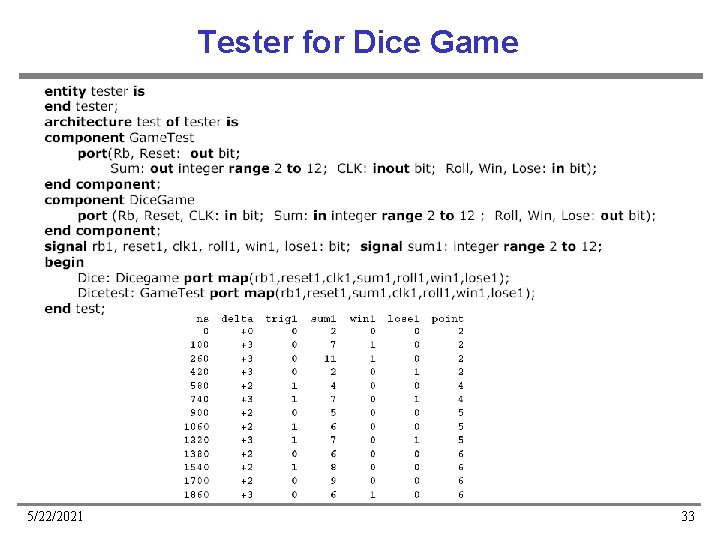

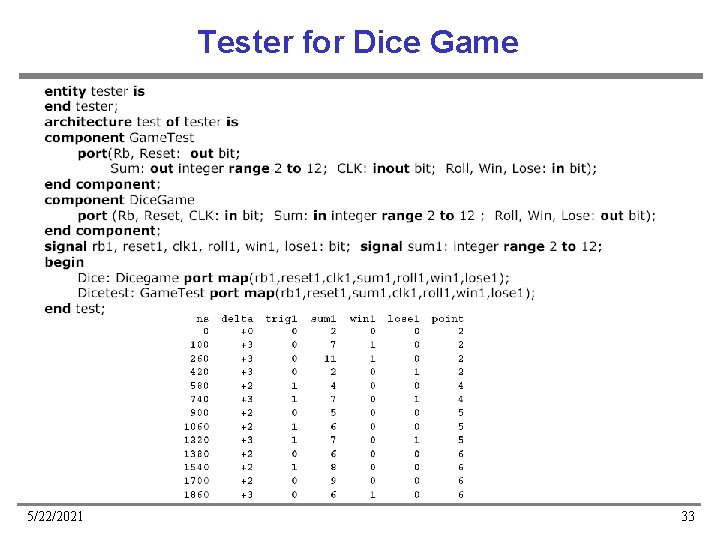

Tester for Dice Game 5/22/2021 33

To Do • Read chapters 5. 1, 5. 2 5/22/2021 34

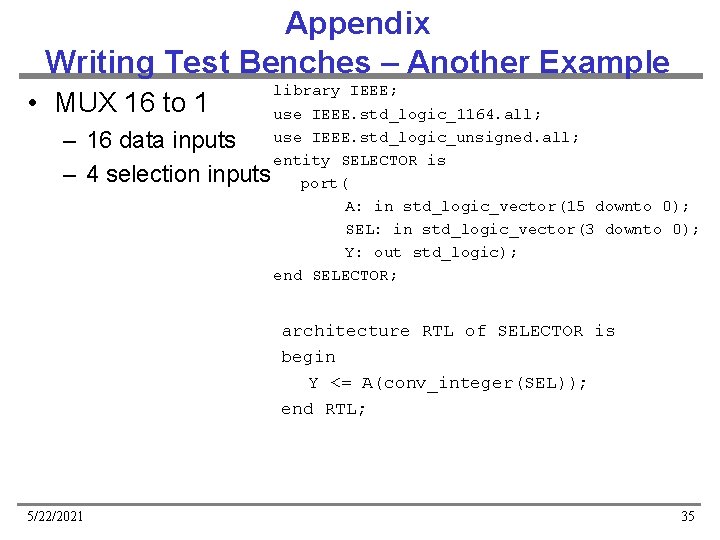

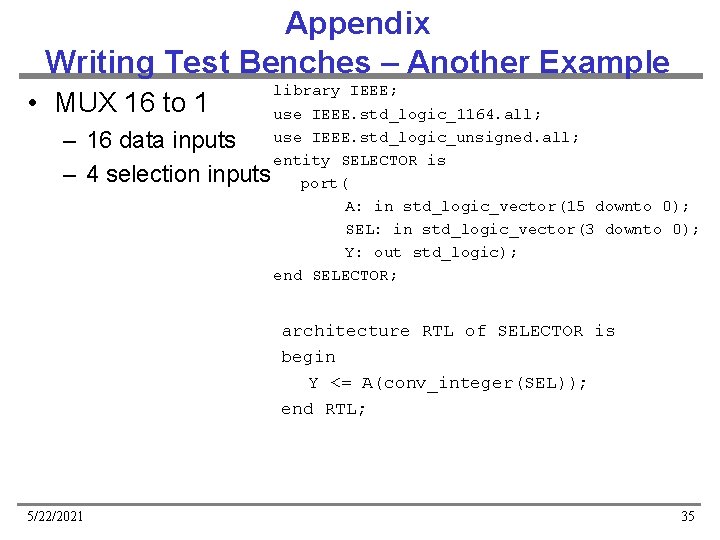

Appendix Writing Test Benches – Another Example library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_unsigned. all; 16 data inputs entity SELECTOR is 4 selection inputs port( A: in std_logic_vector(15 downto 0); SEL: in std_logic_vector(3 downto 0); Y: out std_logic); end SELECTOR; • MUX 16 to 1 – – architecture RTL of SELECTOR is begin Y <= A(conv_integer(SEL)); end RTL; 5/22/2021 35

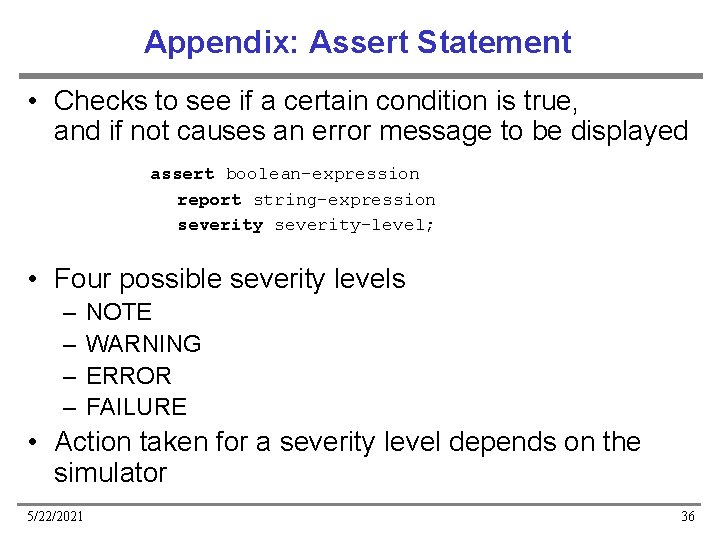

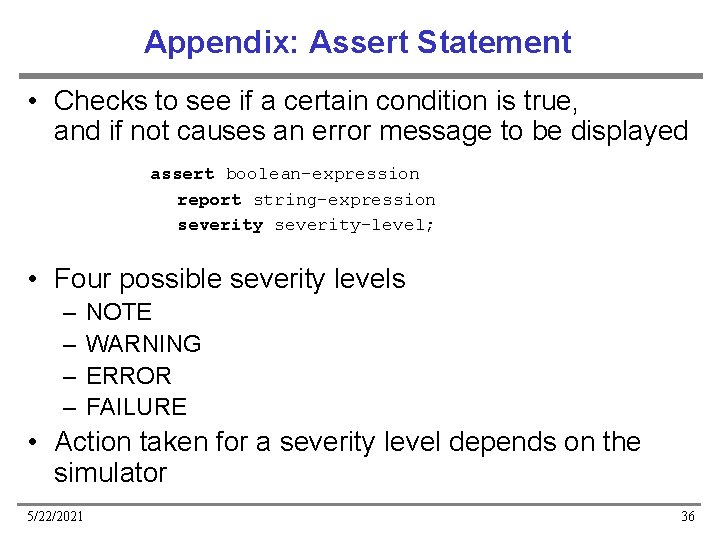

Appendix: Assert Statement • Checks to see if a certain condition is true, and if not causes an error message to be displayed assert boolean-expression report string-expression severity-level; • Four possible severity levels – – NOTE WARNING ERROR FAILURE • Action taken for a severity level depends on the simulator 5/22/2021 36

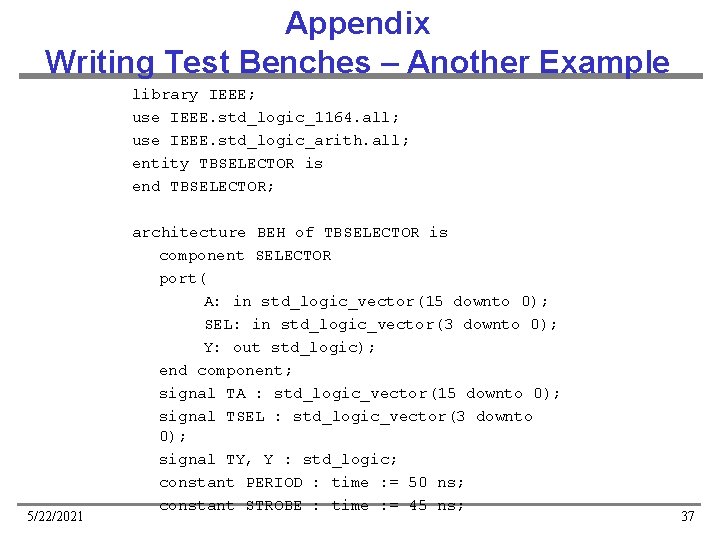

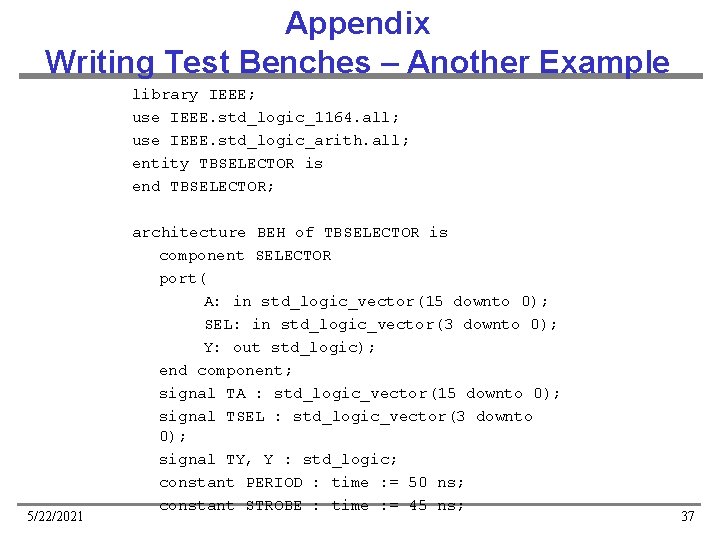

Appendix Writing Test Benches – Another Example library IEEE; use IEEE. std_logic_1164. all; use IEEE. std_logic_arith. all; entity TBSELECTOR is end TBSELECTOR; 5/22/2021 architecture BEH of TBSELECTOR is component SELECTOR port( A: in std_logic_vector(15 downto 0); SEL: in std_logic_vector(3 downto 0); Y: out std_logic); end component; signal TA : std_logic_vector(15 downto 0); signal TSEL : std_logic_vector(3 downto 0); signal TY, Y : std_logic; constant PERIOD : time : = 50 ns; constant STROBE : time : = 45 ns; 37

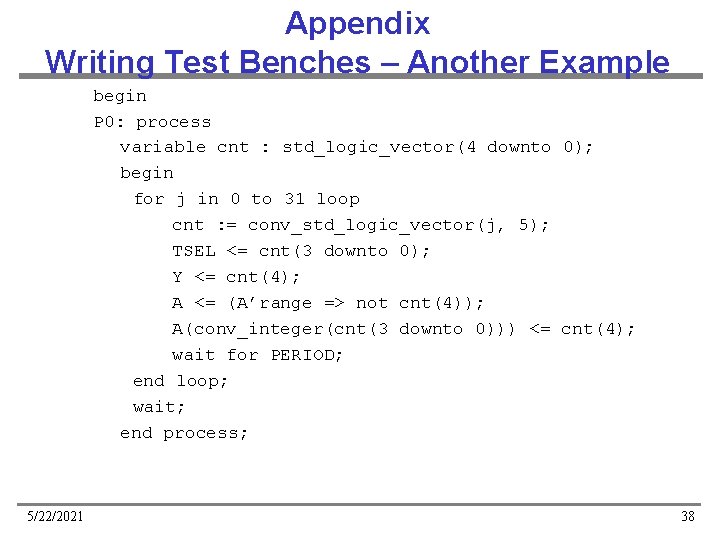

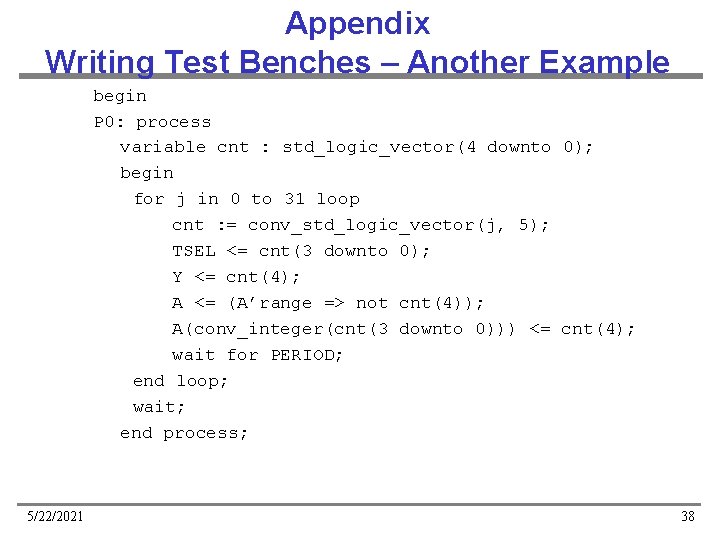

Appendix Writing Test Benches – Another Example begin P 0: process variable cnt : std_logic_vector(4 downto 0); begin for j in 0 to 31 loop cnt : = conv_std_logic_vector(j, 5); TSEL <= cnt(3 downto 0); Y <= cnt(4); A <= (A’range => not cnt(4)); A(conv_integer(cnt(3 downto 0))) <= cnt(4); wait for PERIOD; end loop; wait; end process; 5/22/2021 38

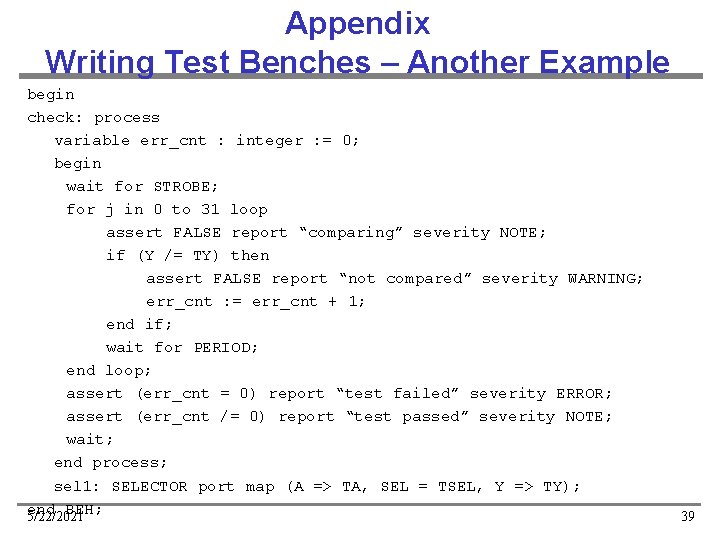

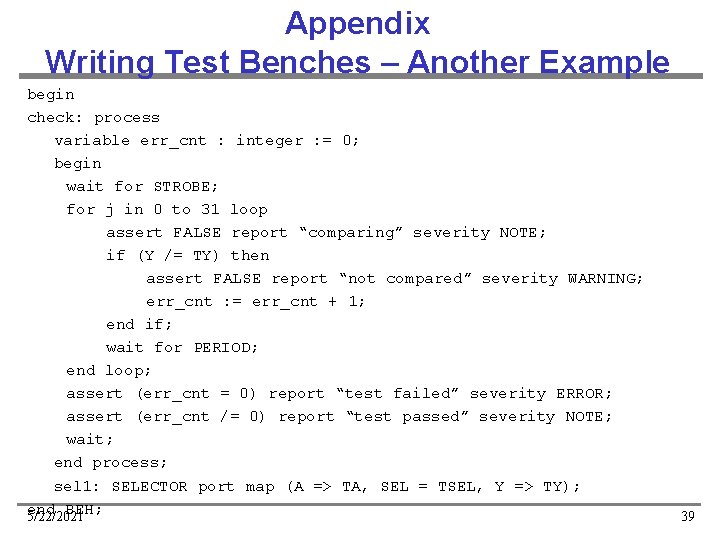

Appendix Writing Test Benches – Another Example begin check: process variable err_cnt : integer : = 0; begin wait for STROBE; for j in 0 to 31 loop assert FALSE report “comparing” severity NOTE; if (Y /= TY) then assert FALSE report “not compared” severity WARNING; err_cnt : = err_cnt + 1; end if; wait for PERIOD; end loop; assert (err_cnt = 0) report “test failed” severity ERROR; assert (err_cnt /= 0) report “test passed” severity NOTE; wait; end process; sel 1: SELECTOR port map (A => TA, SEL = TSEL, Y => TY); end BEH; 5/22/2021 39