Delivering Success Modeling 32 V Asymmetric LDMOS Using

- Slides: 33

Delivering Success. Modeling 32 V Asymmetric LDMOS Using Aurora and Hspice Level 66 By Alhan Farhanah, Mohd Shahrul Amran, Albert Victor Kordesch Device Modeling Department, SILTERRA Malaysia Sdn. Bhd. ESSDERC 2007 MUNICH

Delivering Success. Outline ü ü ü Aurora and HSPICE Level 66 Background 32 V Asymmetric HV MOS Background Modeling Flow for Asymmetric HV MOS Results and Discussion Self Heating Effect in HV MOS Conclusion ESSDERC 2007 MUNICH 2

Aurora and HSPICE Level 66 Background Delivering Success. ü Aurora o product of Synopsys Inc for Modeling. o Beside HSPICE Level 66, Aurora also offers all types of models that normally offered by other products. ü Contends for the modeling and SPICE simulation of digital CMOS, analog and RF circuit that operates up to 100 V. ESSDERC 2007 MUNICH 3

Aurora and HSPICE Level 66 Background (cont’d) Delivering Success. ü HSPICE Level 66 is a proprietary product of Synopsys. ü HSPICE Level 66 model o self heating, forward and reverse mode, asymmetric parasitic, and bias dependent RDS - based on BSIM 4 o primarily targets for LDMOS (Lateral Double Diffused MOSFET) and EDMOS (Extended Drain MOSFET) device technologies. ESSDERC 2007 MUNICH 4

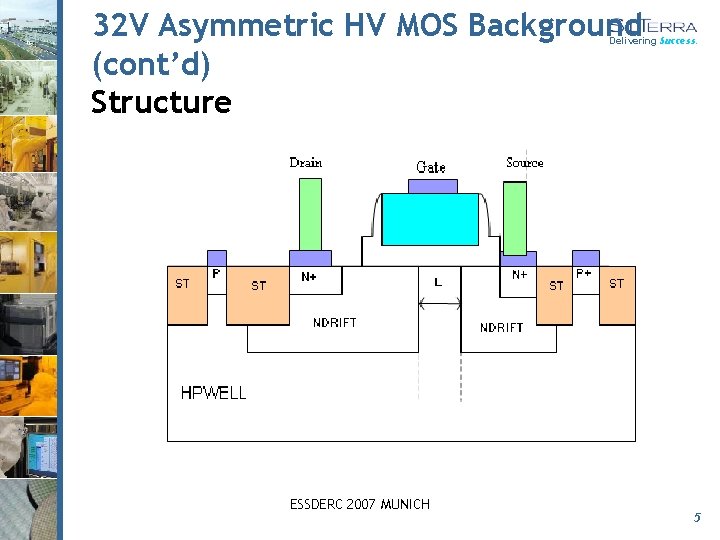

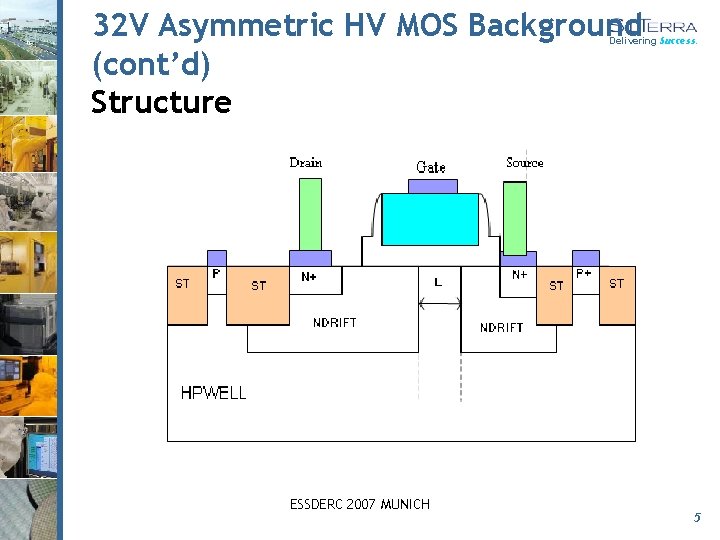

32 V Asymmetric HV MOS Background (cont’d) Structure Delivering Success. ESSDERC 2007 MUNICH 5

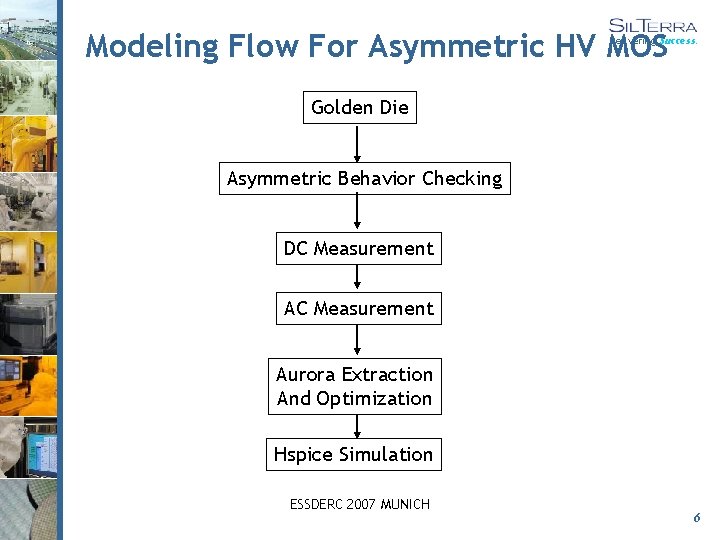

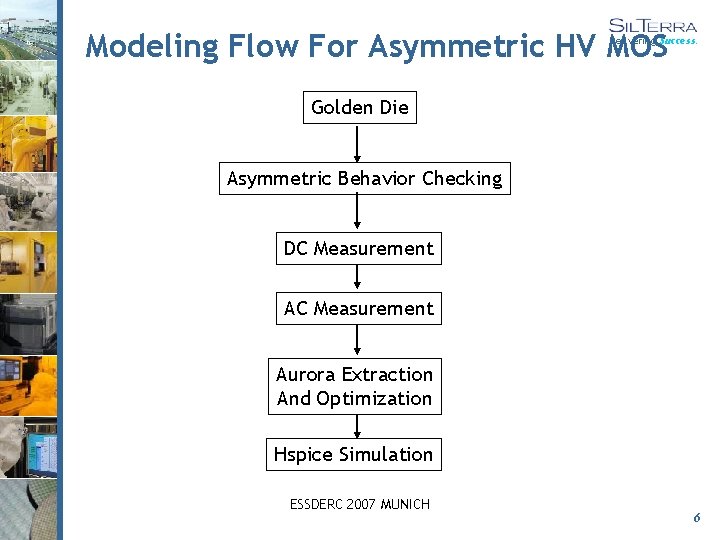

Modeling Flow For Asymmetric HV MOS Delivering Success. Golden Die Asymmetric Behavior Checking DC Measurement Aurora Extraction And Optimization Hspice Simulation ESSDERC 2007 MUNICH 6

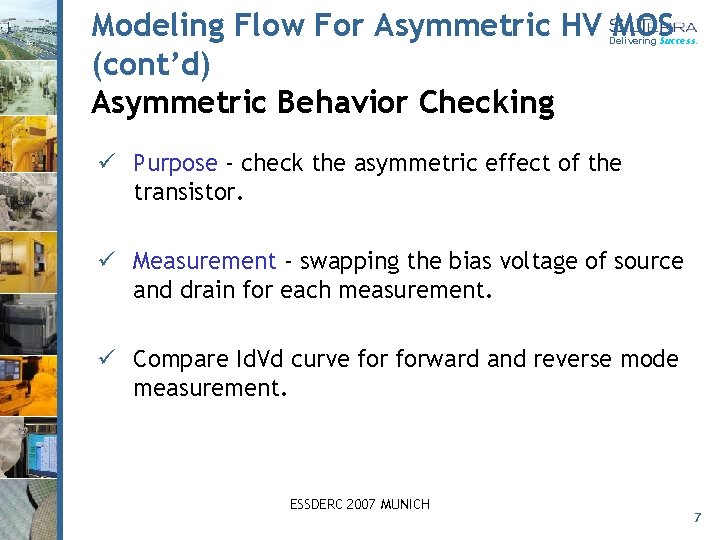

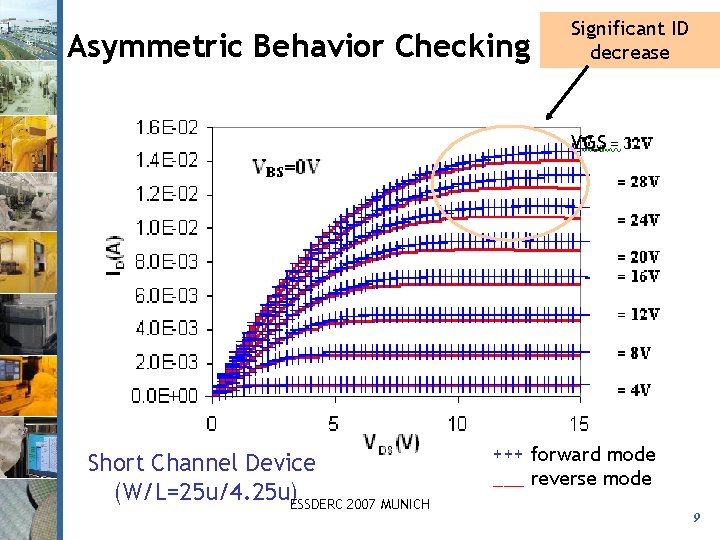

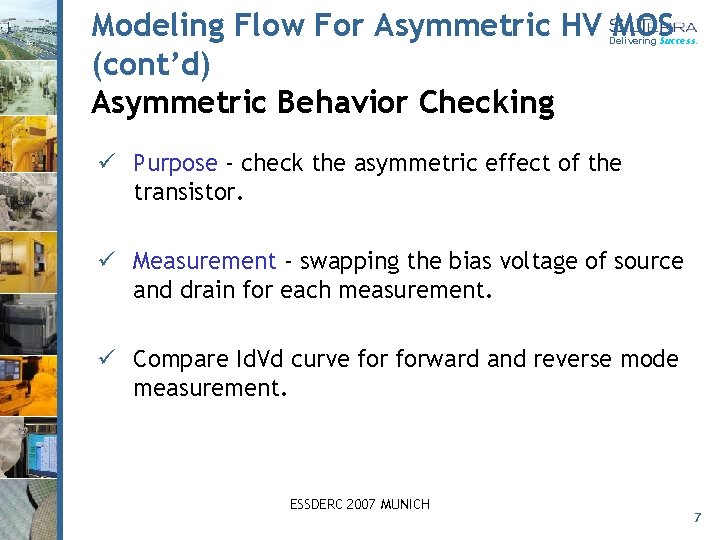

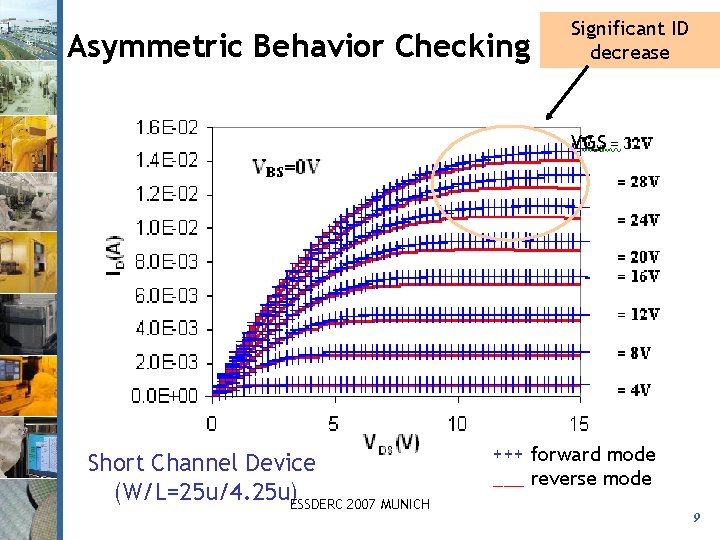

Modeling Flow For Asymmetric HV MOS (cont’d) Asymmetric Behavior Checking Delivering Success. ü Purpose - check the asymmetric effect of the transistor. ü Measurement - swapping the bias voltage of source and drain for each measurement. ü Compare Id. Vd curve forward and reverse mode measurement. ESSDERC 2007 MUNICH 7

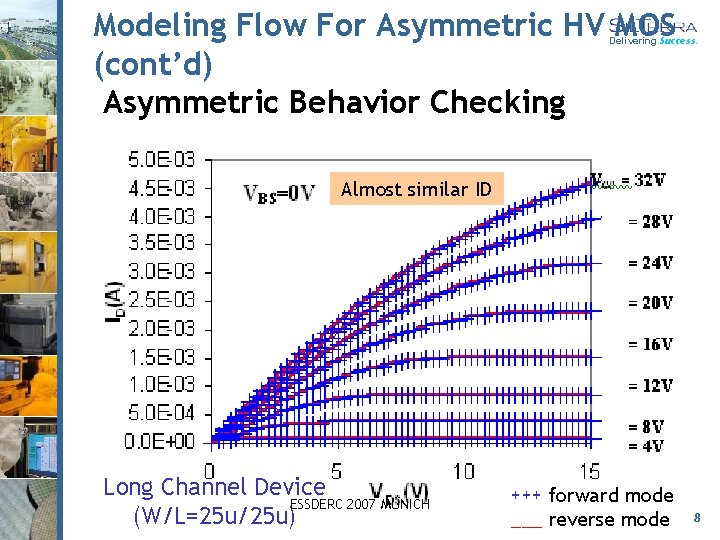

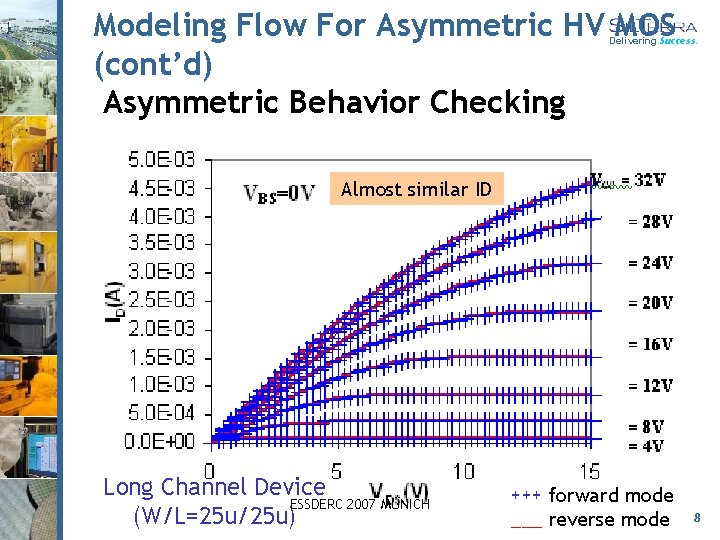

Modeling Flow For Asymmetric HV MOS (cont’d) Asymmetric Behavior Checking Delivering Success. Almost similar ID Long Channel Device ESSDERC 2007 MUNICH (W/L=25 u/25 u) +++ forward mode ___ reverse mode 8

Asymmetric Behavior Checking Significant ID Delivering Success. decrease VGS Short Channel Device (W/L=25 u/4. 25 u)ESSDERC 2007 MUNICH +++ forward mode ___ reverse mode 9

Modeling Flow For Asymmetric HV MOS (cont’d) Delivering Success. ü The results showed that shorter length device exhibits quite significant Id decrease for reverse mode measurement while the long channel device exhibits almost similar Id curve for both modes of measurement ESSDERC 2007 MUNICH 10

Modeling Flow For Asymmetric HV MOS (cont’d) DC Measurement Delivering Success. ü Measurements: o o Id. Vg@low Vdd with different Vb Id. Vg@high Vdd with different Vb Id. Vd @Vb=0 with different Vg Id. Vd @high Vb with different Vg ü Before measuring all the modeling devices, Wide Width and small Length transistor with different back biases and different temperatures must be evaluated first ESSDERC 2007 MUNICH 11

Modeling Flow For Asymmetric HV MOS (cont’d) CV Measurement Delivering Success. ü To properly model the effect of asymmetric, the modeling structure for CV need to be designed with extra structures compare to symmetric structure. ü All the CV modeling structures need to be separated into 2 different structures: o Source design rule o Drain design rule. ü Thus, the CV measurement for asymmetric transistor is almost double compare to symmetric transistor. ESSDERC 2007 MUNICH 12

Modeling Flow For Asymmetric HV MOS (cont’d) Extraction and Optimization Delivering Success. ü Extraction strategy – almost similar to BSIM 4 ü The preferred mobility model in Level 66 o MOBMOD=0 ü Source and Drain parameters are not equal. e. g RSW and RDW, RSWMIN and RDWMIN ü Both drain side and source side bias dependence parameters of LDD resistance can be optimized. ESSDERC 2007 MUNICH 13

Modeling Flow For Asymmetric HV MOS (cont’d) Extraction and Optimization Delivering Success. ü There are reverse mode parameters available for optimization i. e ETA 0 I, ETABI, DSUBI o Too many of these parameters are not encouraged. ü Self heating effect can be turned on by setting SHMOD=1 and RTH 0>0. o Strongly advised to set TSHFLAG=1 during the optimization - internal approximation of self heating effect will be used during the optimization. Hence, the speed of the optimization is significantly improved. In the final step, the optimization can be refined by setting TSHFLAG=0. ü When self heating is turned on, the temperature parameters need to be extracted as much as possible before we do extraction for saturation region ESSDERC 2007 MUNICH 14 parameters.

Modeling Flow For Asymmetric HV MOS (cont’d) Extraction and Optimization Delivering Success. ü Disadvantages of Level 66 model: ü Slower model evaluation -includes internal nodes (solver need to be invoked for every bias point) ü There is no reliable way to extract thermal capacitance. Thus, we need to develop a method to include thermal time constant in our model. ESSDERC 2007 MUNICH 15

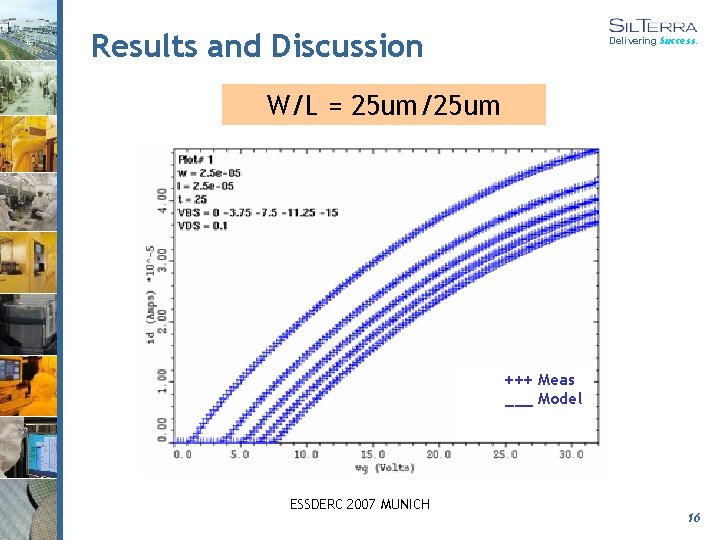

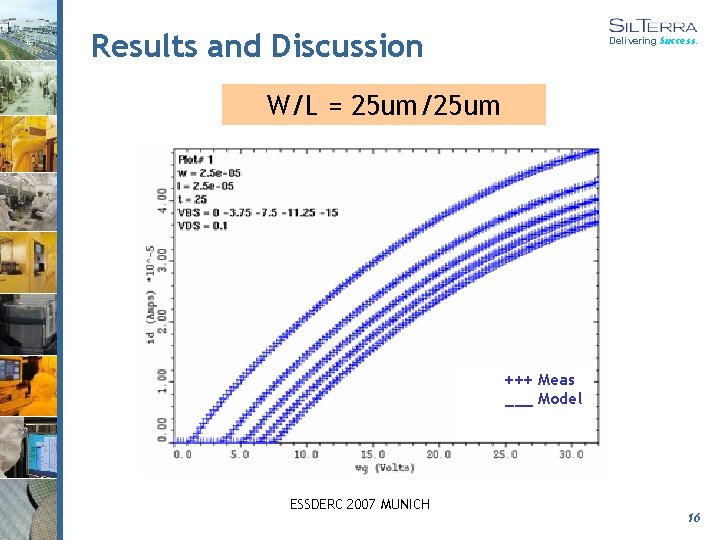

Results and Discussion Delivering Success. W/L = 25 um/25 um +++ Meas ___ Model ESSDERC 2007 MUNICH 16

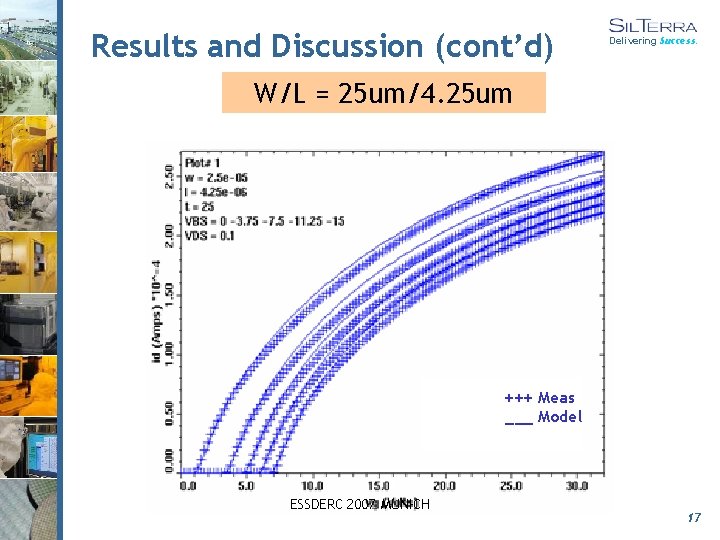

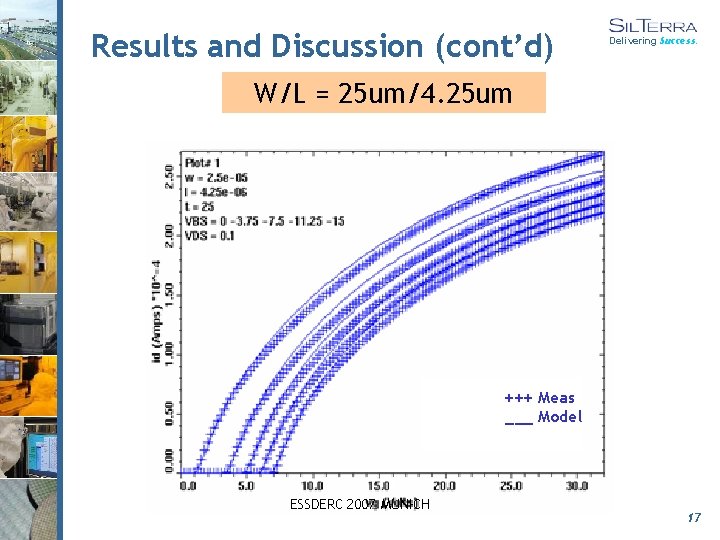

Results and Discussion (cont’d) Delivering Success. W/L = 25 um/4. 25 um +++ Meas ___ Model ESSDERC 2007 MUNICH 17

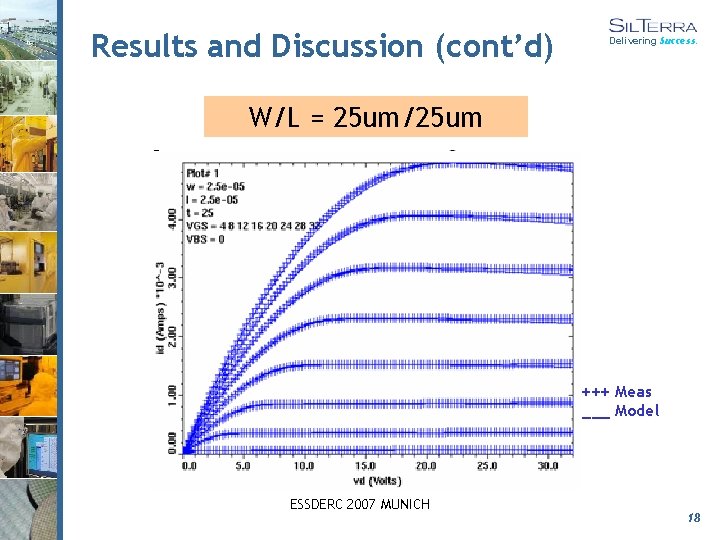

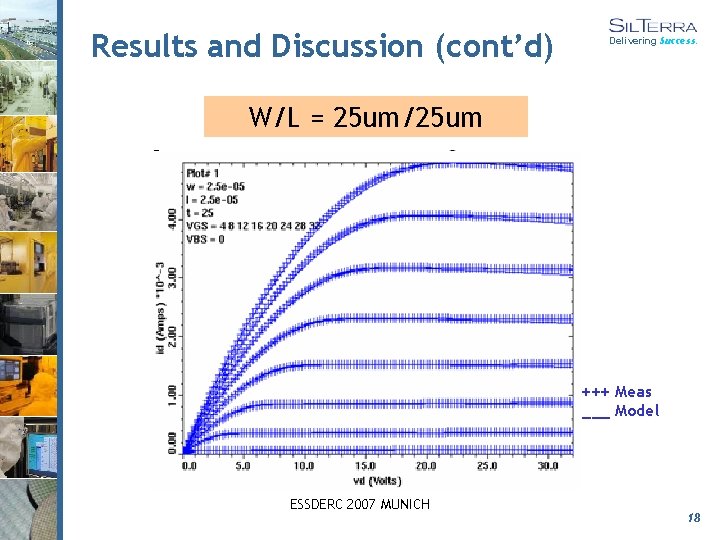

Results and Discussion (cont’d) Delivering Success. W/L = 25 um/25 um +++ Meas ___ Model ESSDERC 2007 MUNICH 18

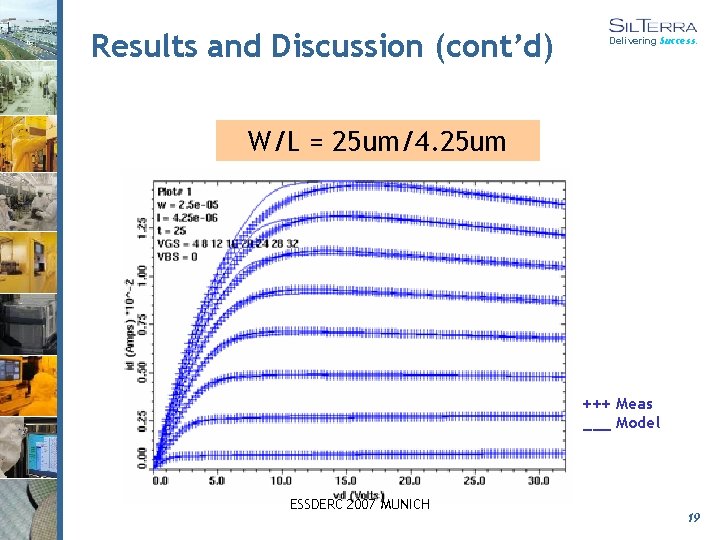

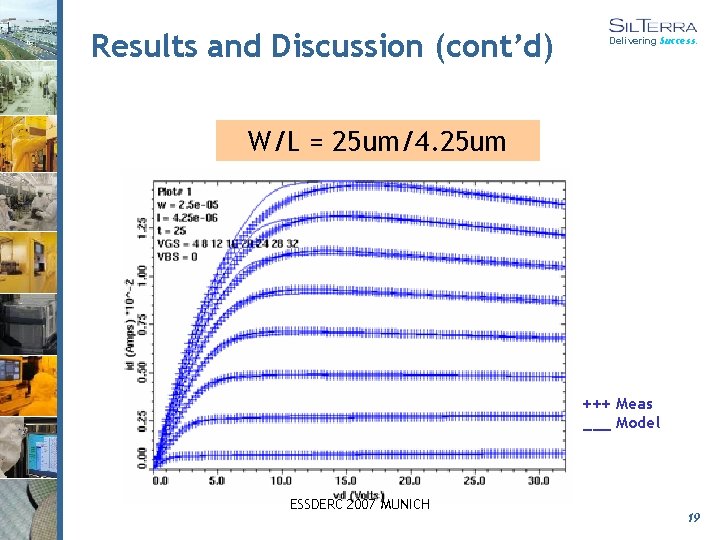

Results and Discussion (cont’d) Delivering Success. W/L = 25 um/4. 25 um +++ Meas ___ Model ESSDERC 2007 MUNICH 19

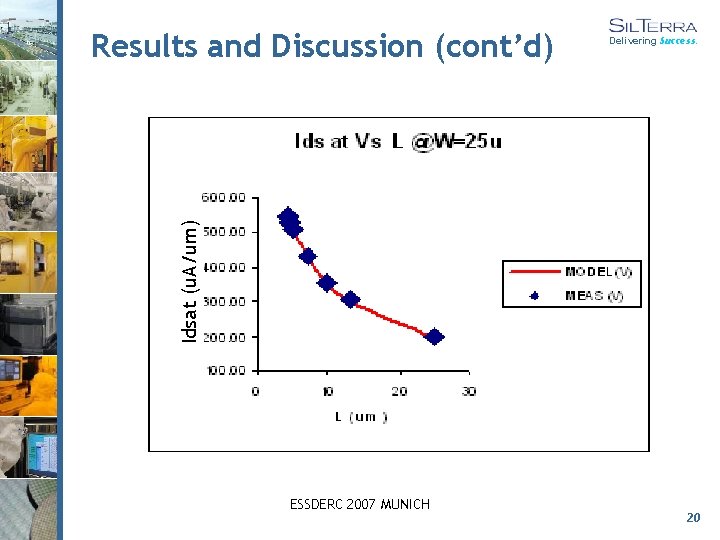

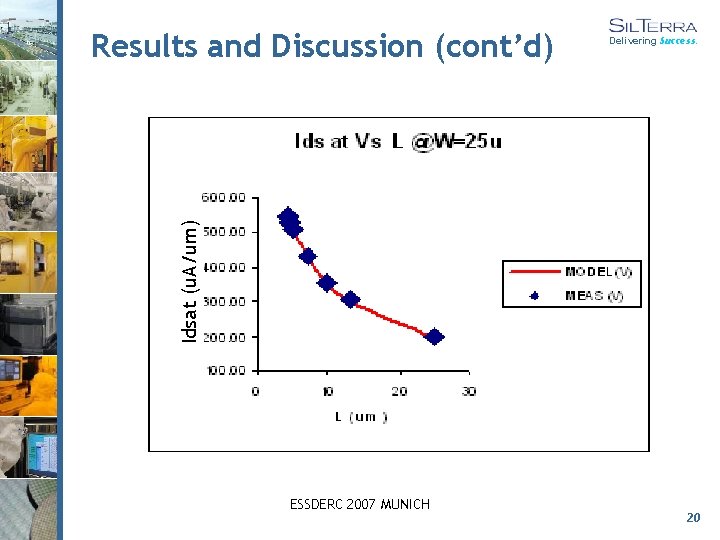

Idsat (u. A/um) Results and Discussion (cont’d) Delivering Success. ESSDERC 2007 MUNICH 20

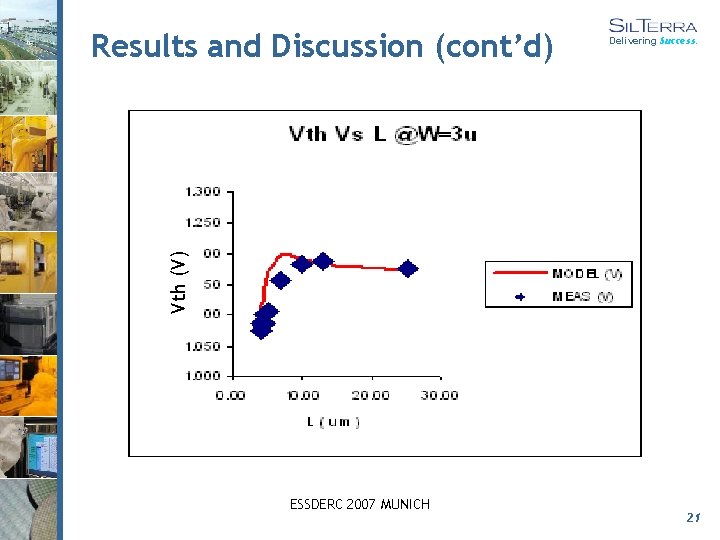

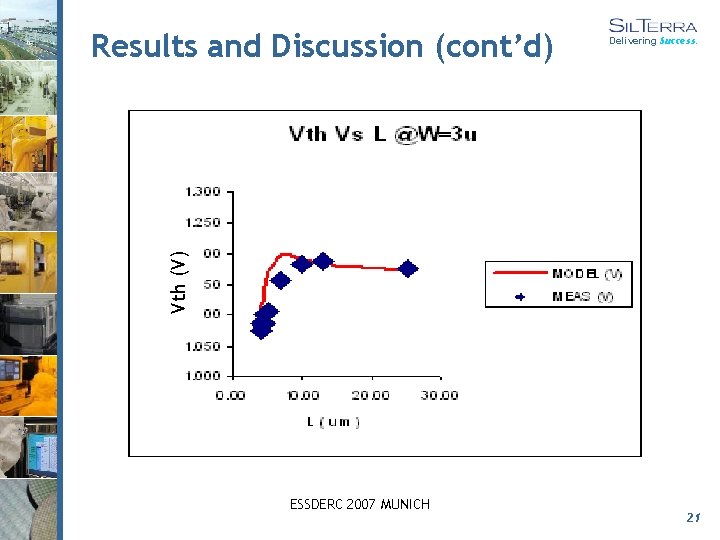

Vth (V) Results and Discussion (cont’d) Delivering Success. ESSDERC 2007 MUNICH 21

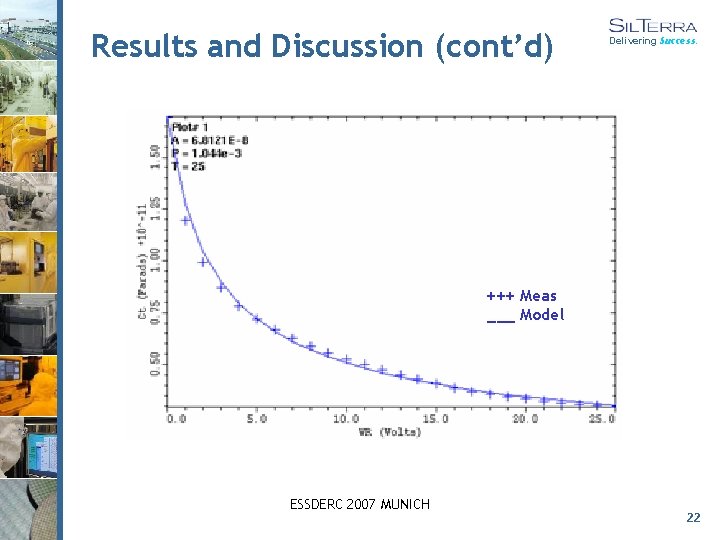

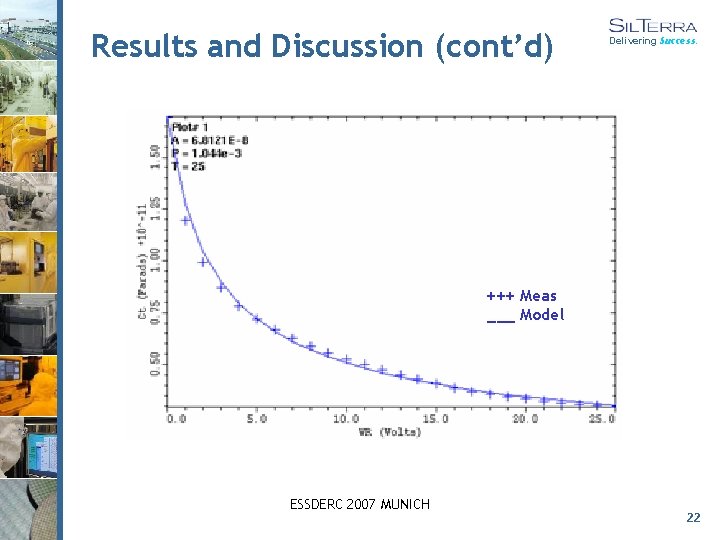

Results and Discussion (cont’d) Delivering Success. +++ Meas ___ Model ESSDERC 2007 MUNICH 22

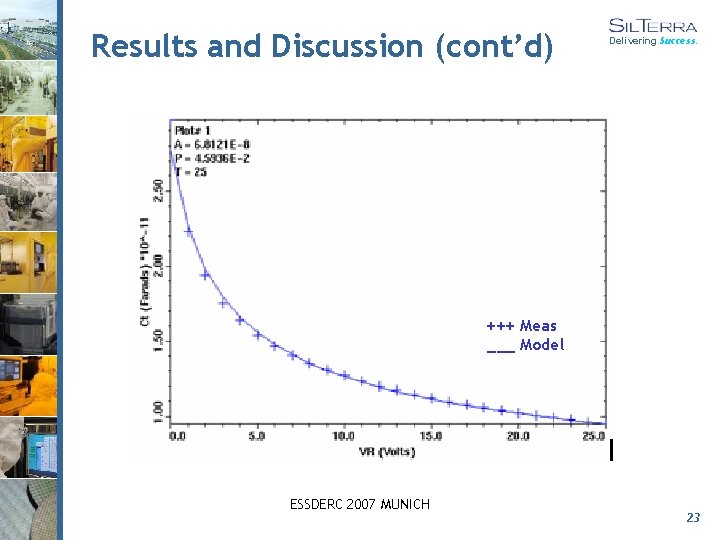

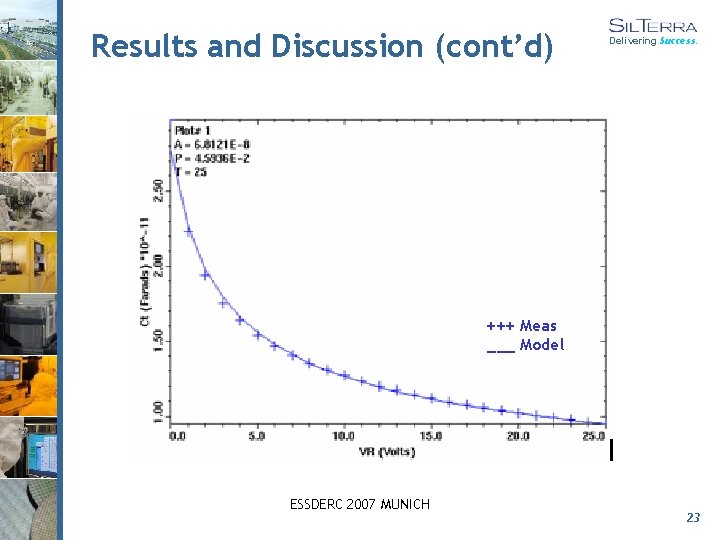

Results and Discussion (cont’d) Delivering Success. +++ Meas ___ Model ESSDERC 2007 MUNICH 23

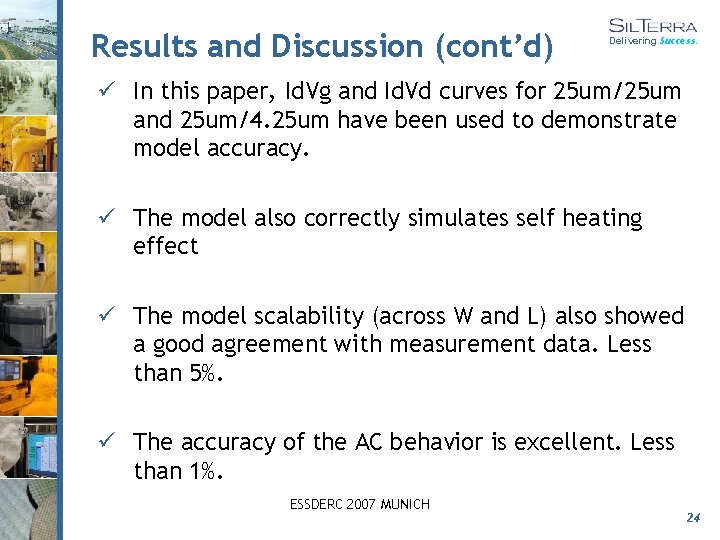

Results and Discussion (cont’d) Delivering Success. ü In this paper, Id. Vg and Id. Vd curves for 25 um/25 um and 25 um/4. 25 um have been used to demonstrate model accuracy. ü The model also correctly simulates self heating effect ü The model scalability (across W and L) also showed a good agreement with measurement data. Less than 5%. ü The accuracy of the AC behavior is excellent. Less than 1%. ESSDERC 2007 MUNICH 24

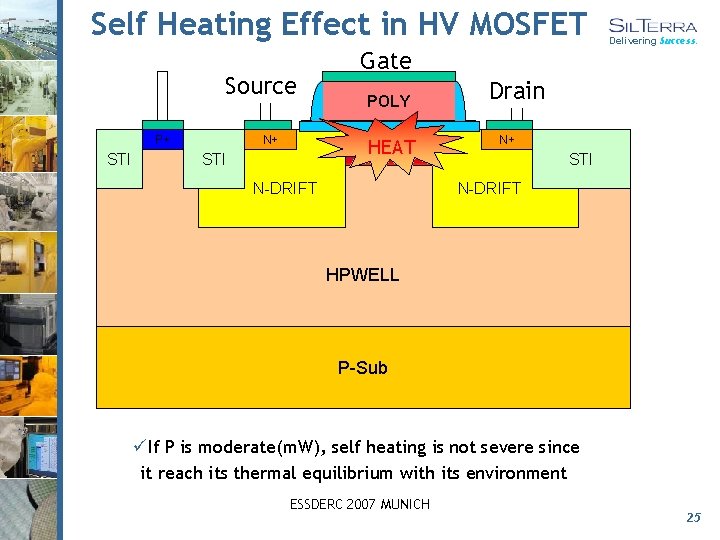

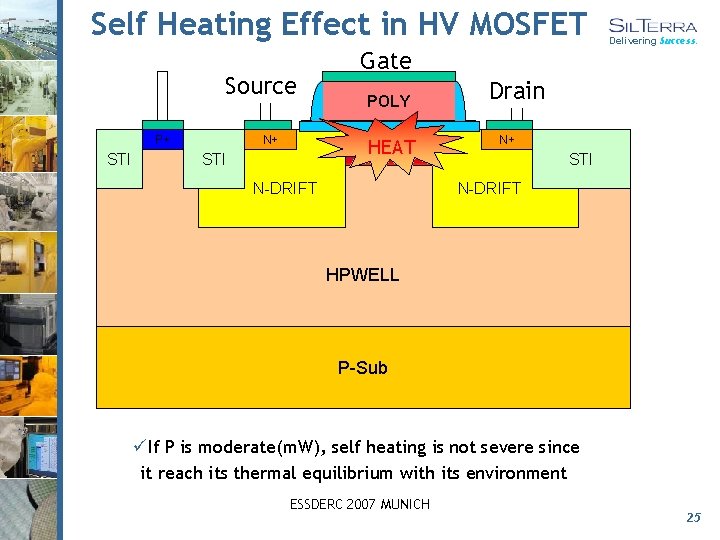

Self Heating Effect in HV MOSFET Source P+ STI N+ Gate POLY HEAT STI Delivering Success. N-DRIFT Drain N+ STI N-DRIFT HPWELL P-Sub üIf P is moderate(m. W), self heating is not severe since it reach its thermal equilibrium with its environment ESSDERC 2007 MUNICH 25

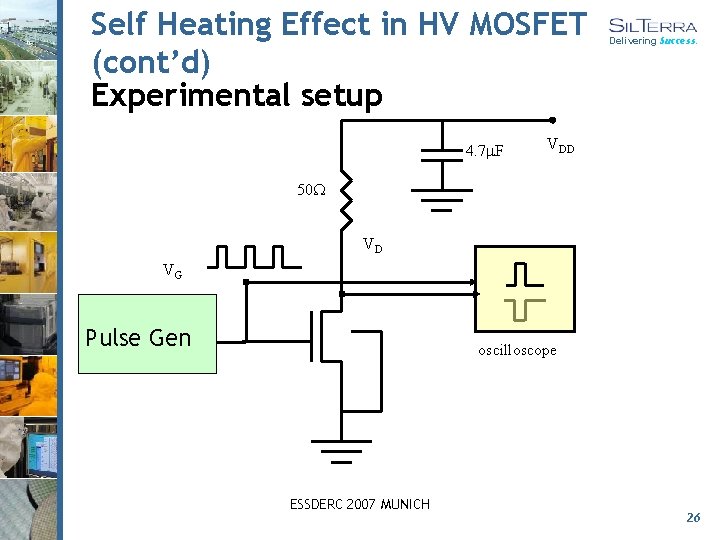

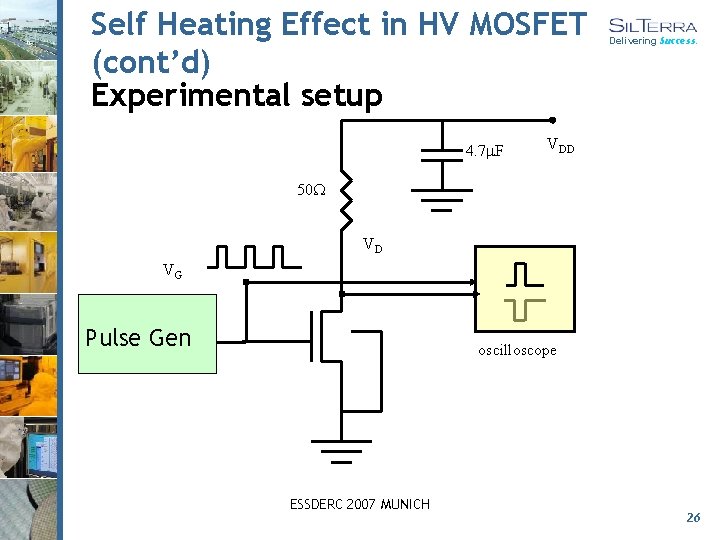

Self Heating Effect in HV MOSFET (cont’d) Experimental setup 4. 7 F Delivering Success. VDD 50 VD VG Pulse Gen oscilloscope ESSDERC 2007 MUNICH 26

Self Heating Effect in HV MOSFET (cont’d) Delivering Success. VG VD Dynamic response of HV NMOS to typical gate pulse ESSDERC 2007 MUNICH 27

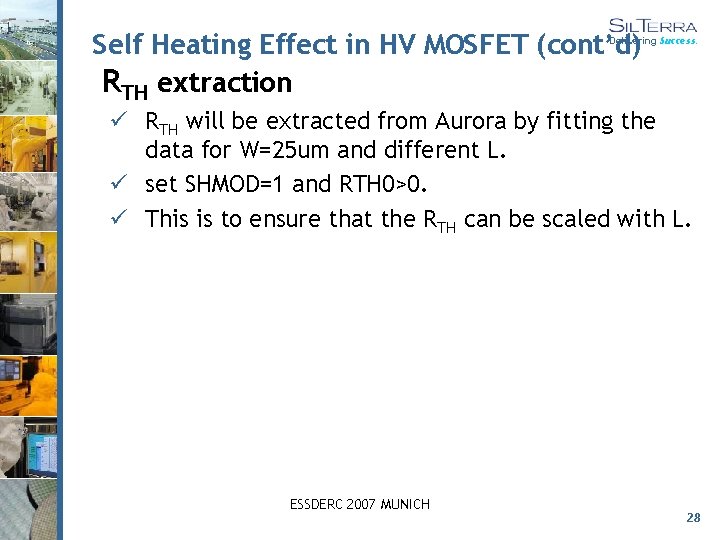

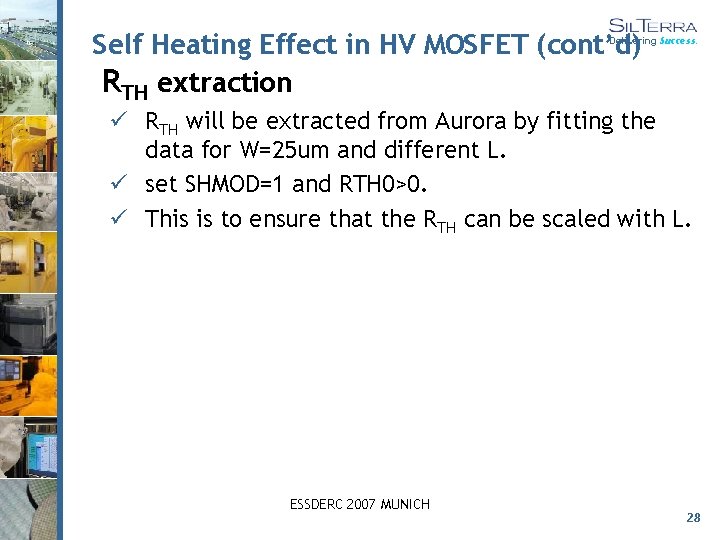

Self Heating Effect in HV MOSFET (cont’d) RTH extraction Delivering Success. ü RTH will be extracted from Aurora by fitting the data for W=25 um and different L. ü set SHMOD=1 and RTH 0>0. ü This is to ensure that the RTH can be scaled with L. ESSDERC 2007 MUNICH 28

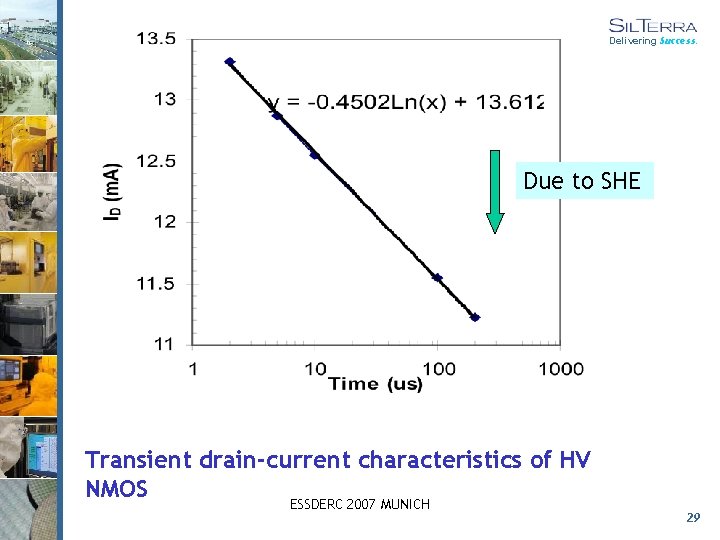

Delivering Success. Due to SHE Transient drain-current characteristics of HV NMOS ESSDERC 2007 MUNICH 29

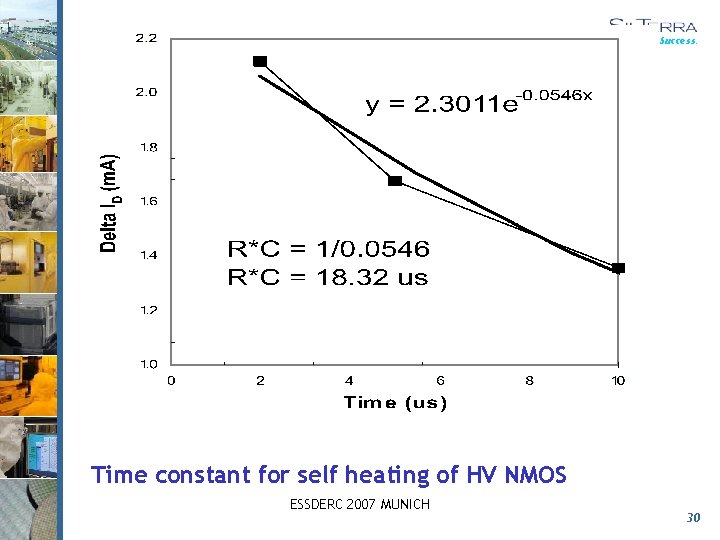

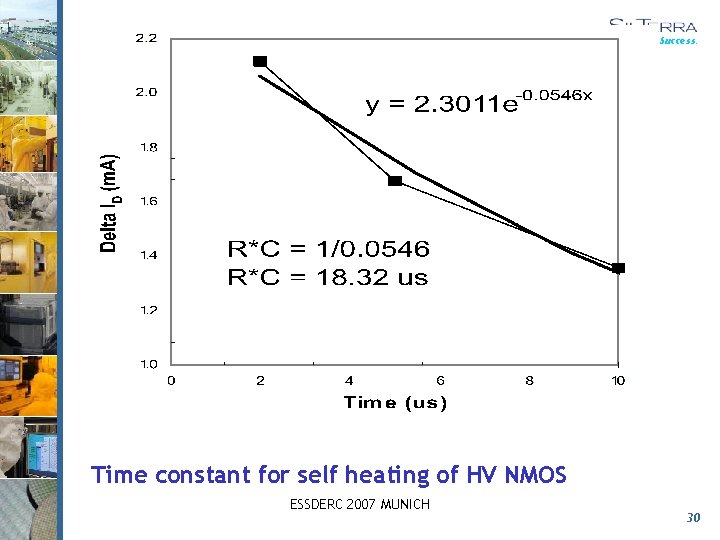

Delivering Success. Time constant for self heating of HV NMOS ESSDERC 2007 MUNICH 30

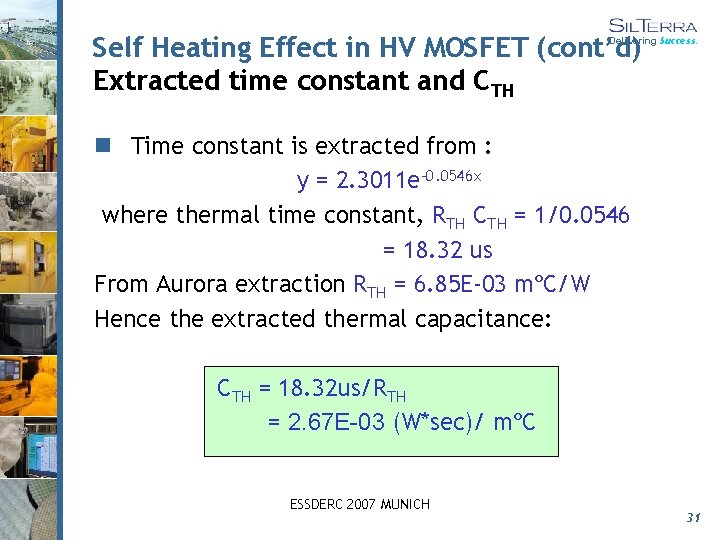

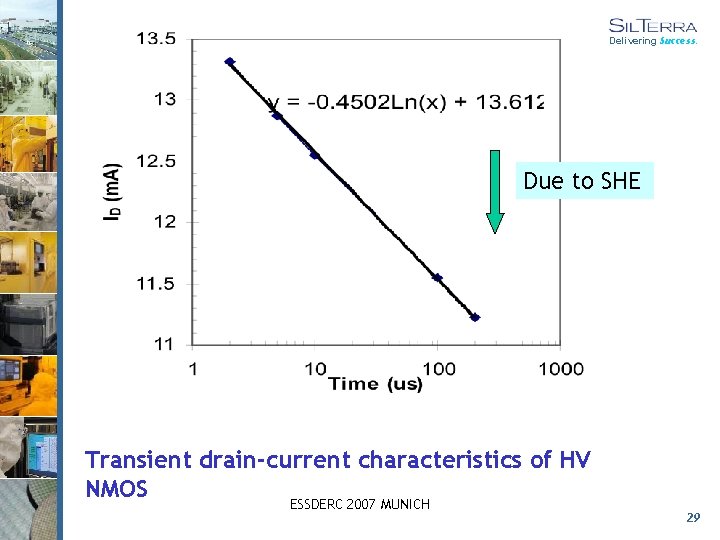

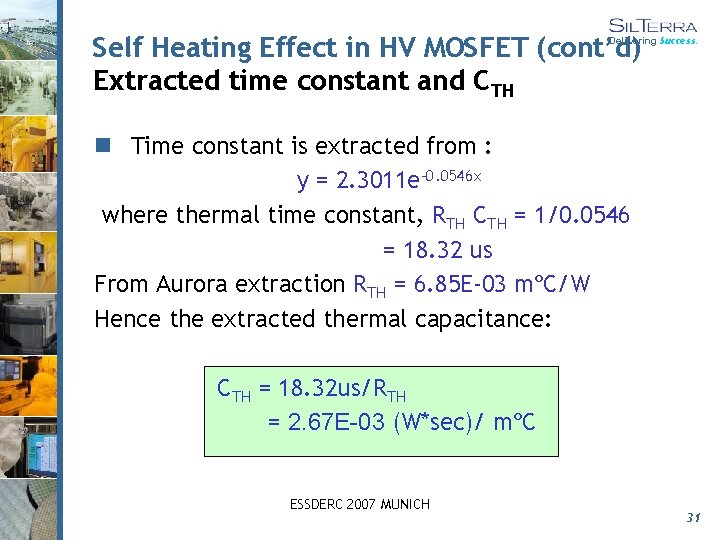

Self Heating Effect in HV MOSFET (cont’d) Extracted time constant and CTH Delivering Success. n Time constant is extracted from : y = 2. 3011 e-0. 0546 x where thermal time constant, RTH CTH = 1/0. 0546 = 18. 32 us From Aurora extraction RTH = 6. 85 E-03 mºC/W Hence the extracted thermal capacitance: CTH = 18. 32 us/RTH = 2. 67 E-03 (W*sec)/ mºC ESSDERC 2007 MUNICH 31

Conclusion Delivering Success. ü Modeling strategies for 32 V asymmetric HV MOSFET using Aurora and HSPICE level 66 has been presented ü Model shows: o Excellent DC IV results for entire DC bias range o Excellent behavior of junction capacitances ü Model scalability (across W and L) also showed good agreement with measurement data. Less than 5% ü Correctly simulate SHE ü Extraction of Thermal resistance and capacitance by Pulsed gate measurement ESSDERC 2007 MUNICH 32

Delivering Success. Thank You ESSDERC 2007 MUNICH 33