CS 35101 Computer Architecture Spring 2006 Week 2

- Slides: 38

CS 35101 Computer Architecture Spring 2006 Week 2

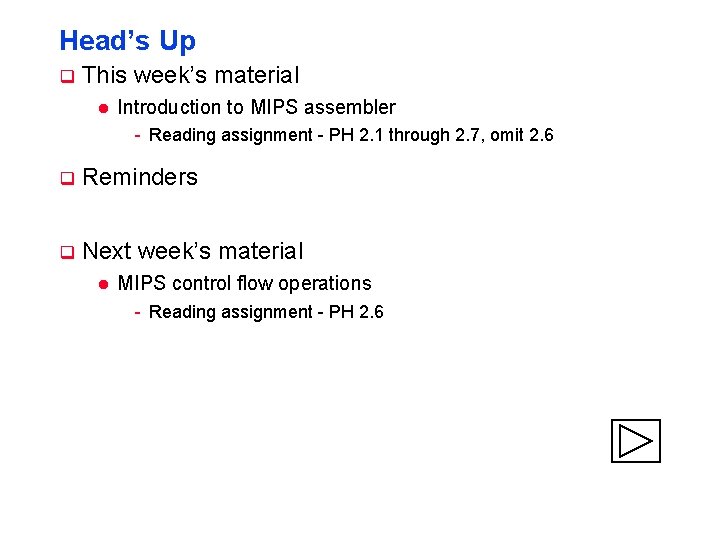

Head’s Up q This week’s material l Introduction to MIPS assembler - Reading assignment - PH 2. 1 through 2. 7, omit 2. 6 q Reminders q Next week’s material l MIPS control flow operations - Reading assignment - PH 2. 6

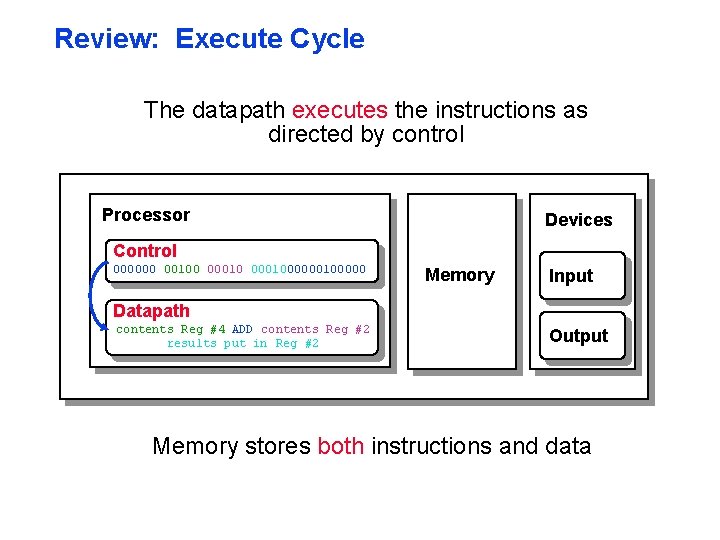

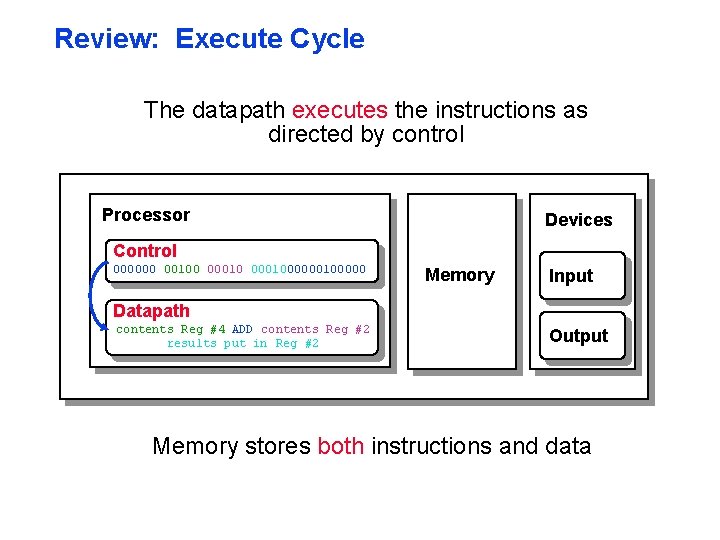

Review: Execute Cycle The datapath executes the instructions as directed by control Processor Devices Control 000000 00100 0001000000100000 Memory Input Datapath contents Reg #4 ADD contents Reg #2 results put in Reg #2 Output Memory stores both instructions and data

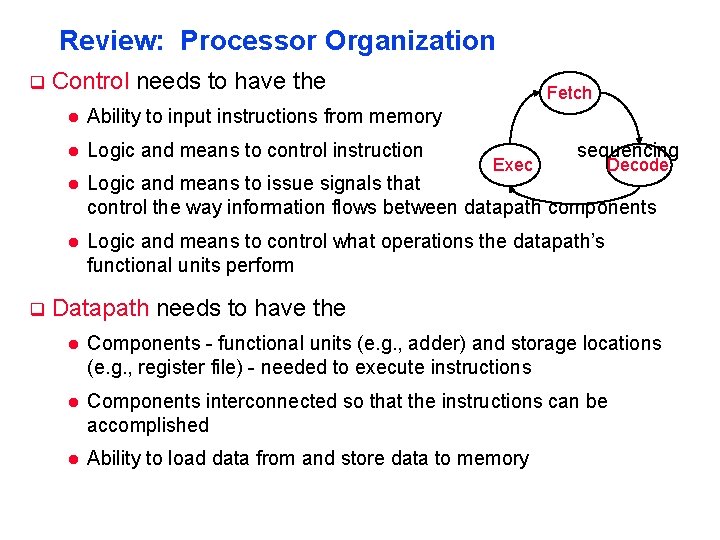

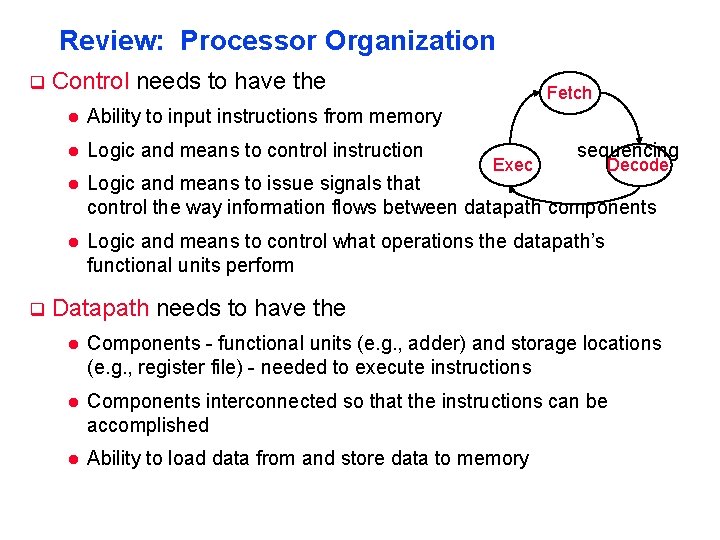

Review: Processor Organization q q Control needs to have the Fetch l Ability to input instructions from memory l Logic and means to control instruction l Logic and means to issue signals that control the way information flows between datapath components l Logic and means to control what operations the datapath’s functional units perform Exec sequencing Decode Datapath needs to have the l Components - functional units (e. g. , adder) and storage locations (e. g. , register file) - needed to execute instructions l Components interconnected so that the instructions can be accomplished l Ability to load data from and store data to memory

For a given level of function, however, that system is best in which one can specify things with the most simplicity and straightforwardness. … Simplicity and straightforwardness proceed from conceptual integrity. … Ease of use, then, dictates unity of design, conceptual integrity. The Mythical Man-Month, Brooks, pg 44

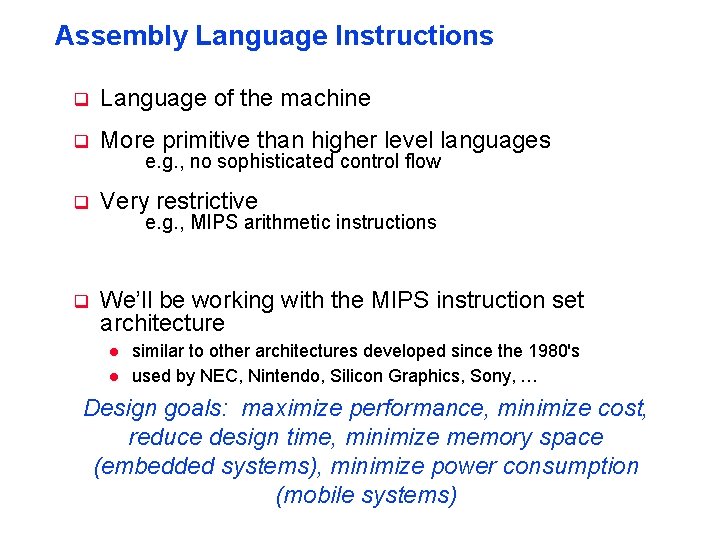

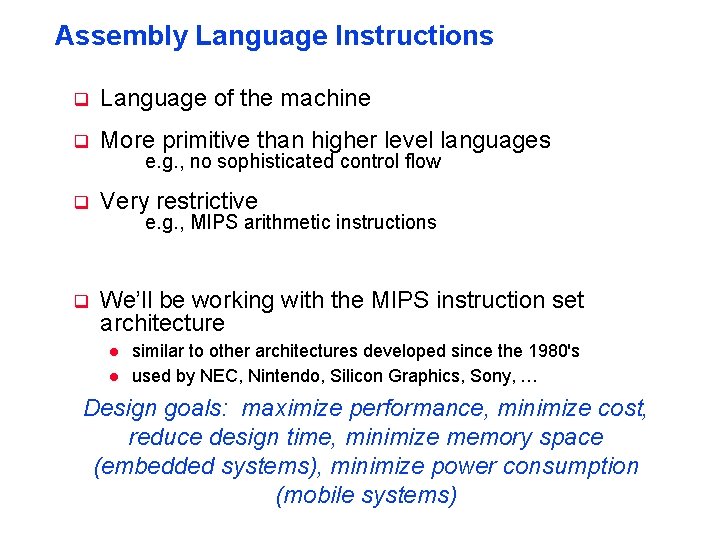

Assembly Language Instructions q Language of the machine q More primitive than higher level languages q Very restrictive q We’ll be working with the MIPS instruction set architecture e. g. , no sophisticated control flow e. g. , MIPS arithmetic instructions l l similar to other architectures developed since the 1980's used by NEC, Nintendo, Silicon Graphics, Sony, … Design goals: maximize performance, minimize cost, reduce design time, minimize memory space (embedded systems), minimize power consumption (mobile systems)

RISC - Reduced Instruction Set Computer q RISC philosophy l fixed instruction lengths load-store instruction sets limited addressing modes l limited operations l l q MIPS, Sun SPARC, HP PA-RISC, IBM Power. PC, Intel (Compaq) Alpha, … q Instruction sets are measured by how well compilers use them as opposed to how well assembly language programmers use them

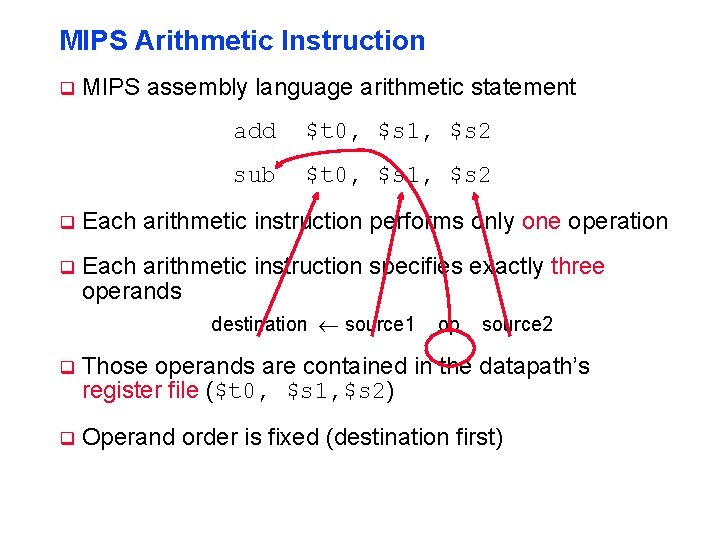

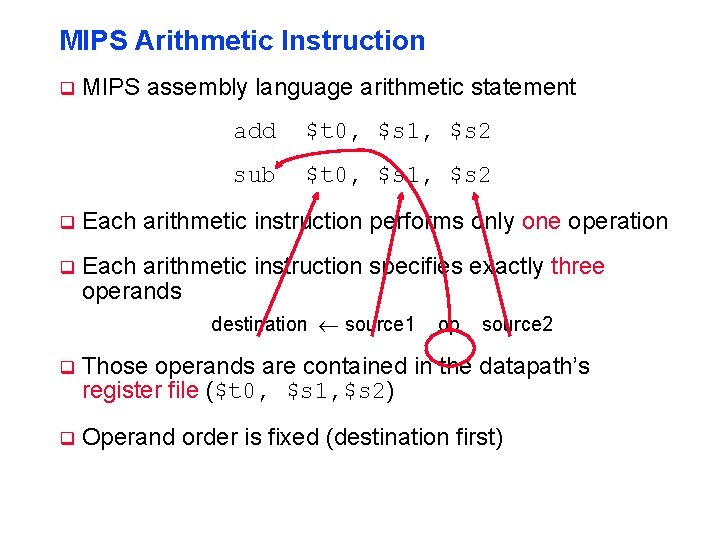

MIPS Arithmetic Instruction q MIPS assembly language arithmetic statement add $t 0, $s 1, $s 2 sub $t 0, $s 1, $s 2 q Each arithmetic instruction performs only one operation q Each arithmetic instruction specifies exactly three operands destination source 1 op source 2 q Those operands are contained in the datapath’s register file ($t 0, $s 1, $s 2) q Operand order is fixed (destination first)

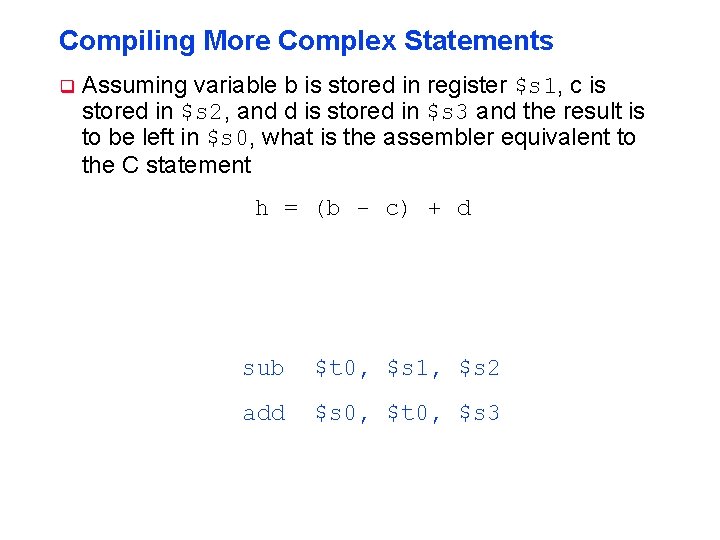

Compiling More Complex Statements q Assuming variable b is stored in register $s 1, c is stored in $s 2, and d is stored in $s 3 and the result is to be left in $s 0, what is the assembler equivalent to the C statement h = (b - c) + d sub $t 0, $s 1, $s 2 add $s 0, $t 0, $s 3

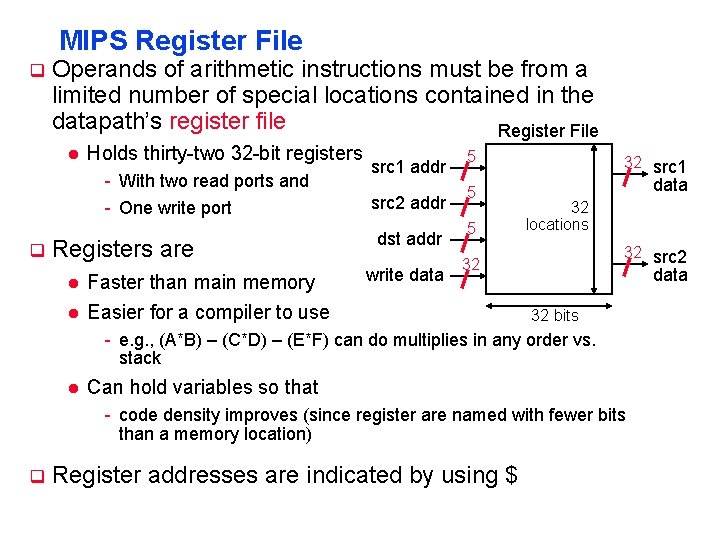

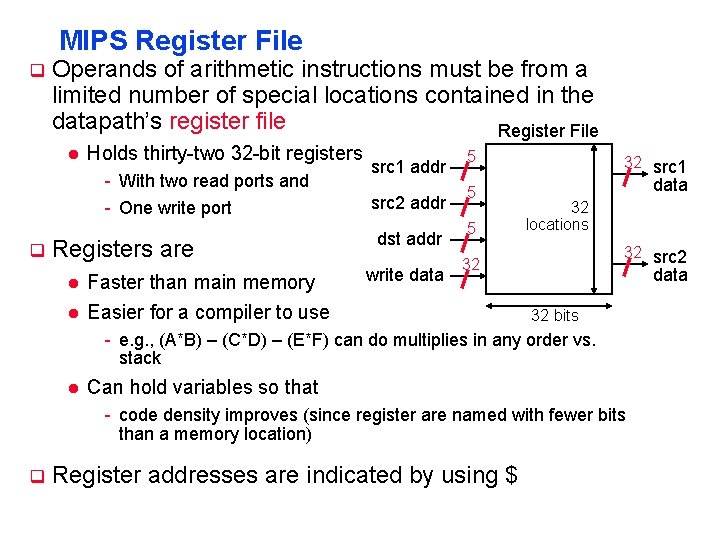

MIPS Register File q Operands of arithmetic instructions must be from a limited number of special locations contained in the datapath’s register file Register File l Holds thirty-two 32 -bit registers - With two read ports and - One write port q Registers are l l Faster than main memory Easier for a compiler to use src 1 addr src 2 addr dst addr write data 5 5 5 32 src 1 data 32 locations 32 src 2 32 data 32 bits - e. g. , (A*B) – (C*D) – (E*F) can do multiplies in any order vs. stack l Can hold variables so that - code density improves (since register are named with fewer bits than a memory location) q Register addresses are indicated by using $

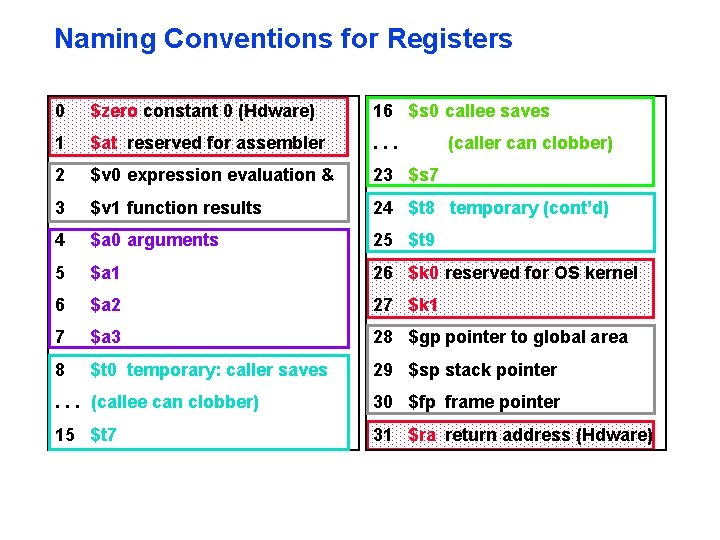

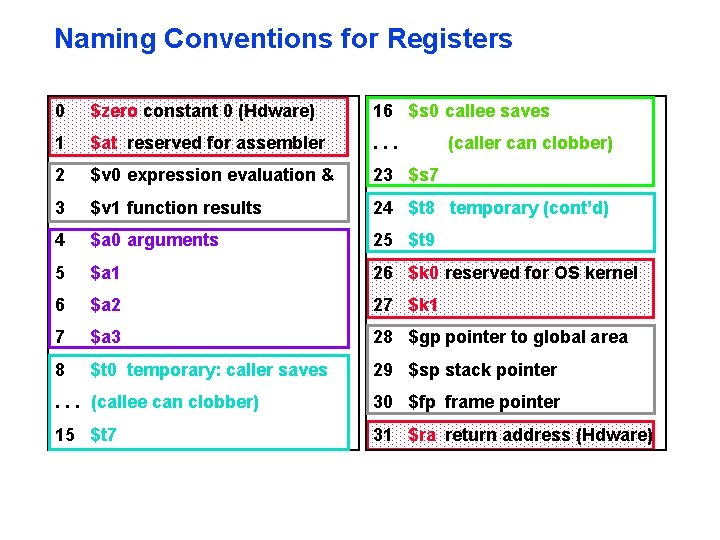

Naming Conventions for Registers 0 $zero constant 0 (Hdware) 16 $s 0 callee saves 1 $at reserved for assembler . . . 2 $v 0 expression evaluation & 23 $s 7 3 $v 1 function results 24 $t 8 temporary (cont’d) 4 $a 0 arguments 25 $t 9 5 $a 1 26 $k 0 reserved for OS kernel 6 $a 2 27 $k 1 7 $a 3 28 $gp pointer to global area 8 $t 0 temporary: caller saves 29 $sp stack pointer (caller can clobber) . . . (callee can clobber) 30 $fp frame pointer 15 $t 7 31 $ra return address (Hdware)

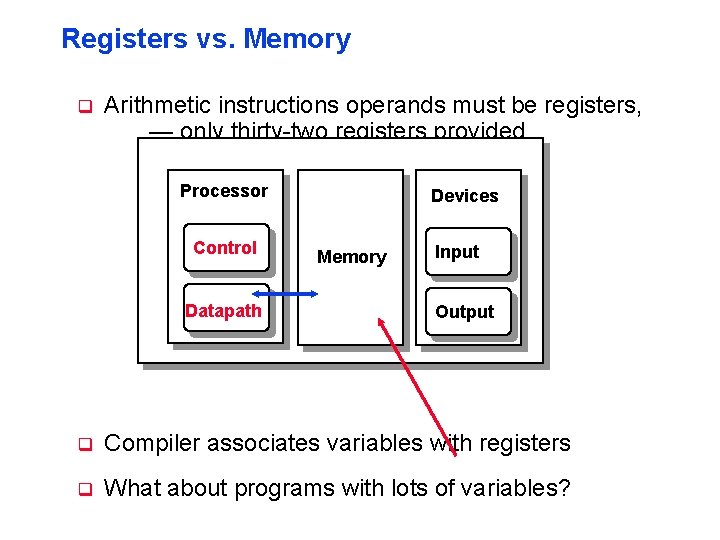

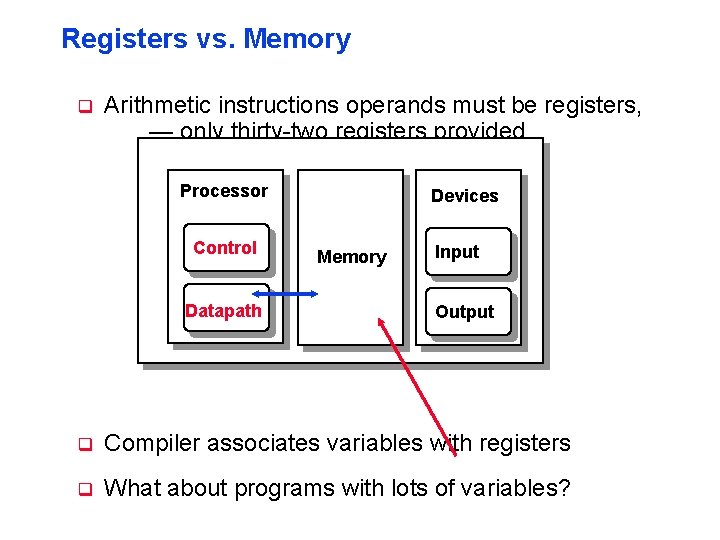

Registers vs. Memory q Arithmetic instructions operands must be registers, — only thirty-two registers provided Processor Control Datapath Devices Memory Input Output q Compiler associates variables with registers q What about programs with lots of variables?

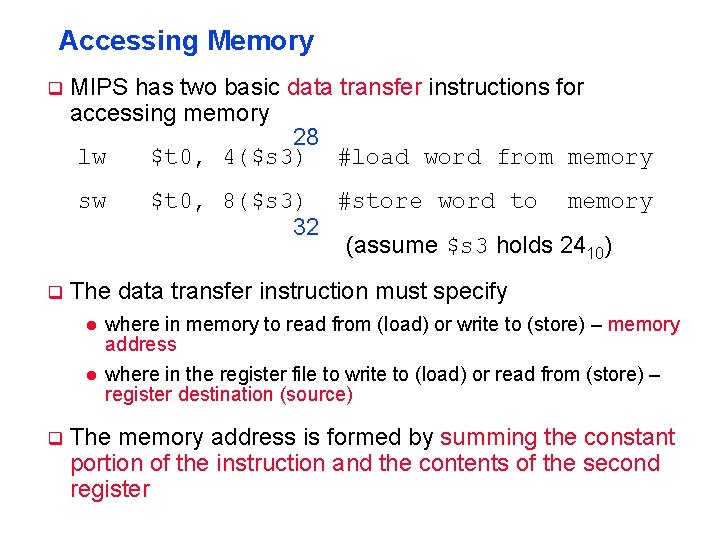

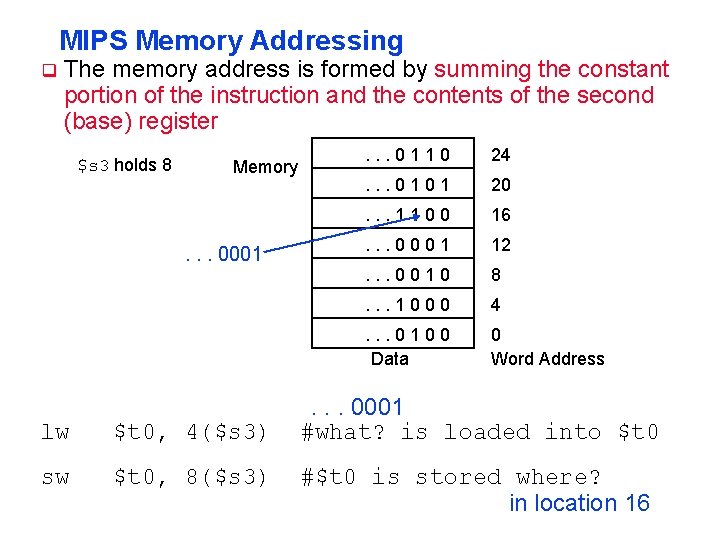

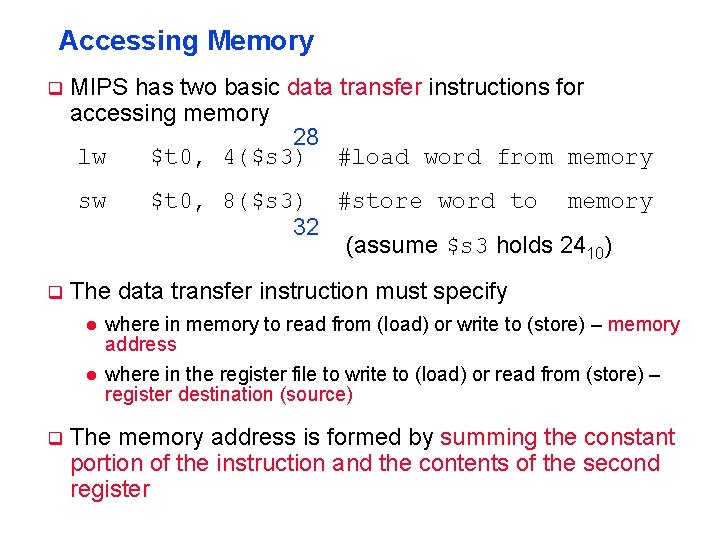

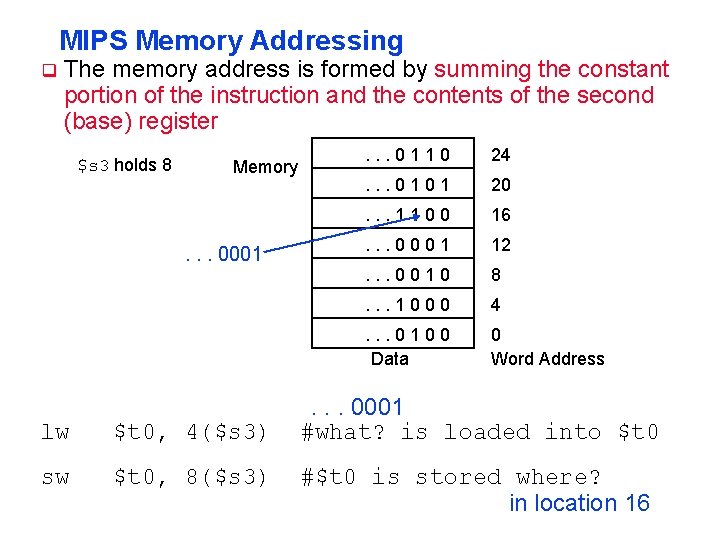

Accessing Memory q MIPS has two basic data transfer instructions for accessing memory 28 lw $t 0, 4($s 3) #load word from memory sw q The data transfer instruction must specify l l q $t 0, 8($s 3) #store word to memory 32 (assume $s 3 holds 2410) where in memory to read from (load) or write to (store) – memory address where in the register file to write to (load) or read from (store) – register destination (source) The memory address is formed by summing the constant portion of the instruction and the contents of the second register

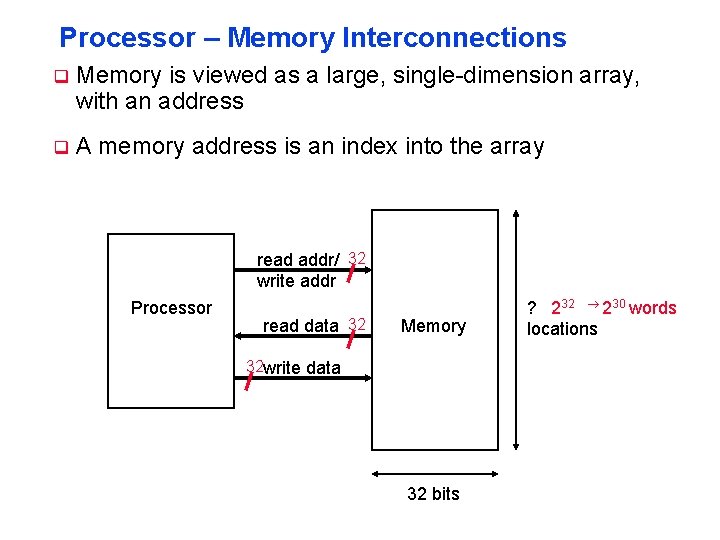

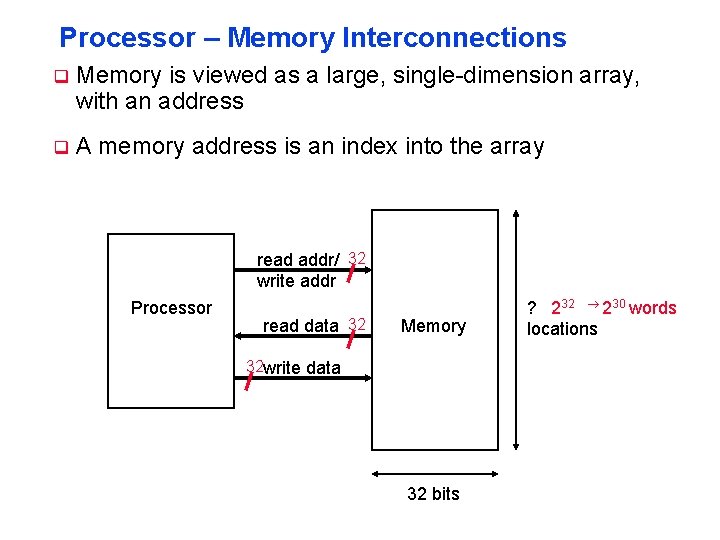

Processor – Memory Interconnections q Memory is viewed as a large, single-dimension array, with an address q A memory address is an index into the array read addr/ 32 write addr Processor read data 32 Memory 32 write data 32 bits ? 232 230 words locations

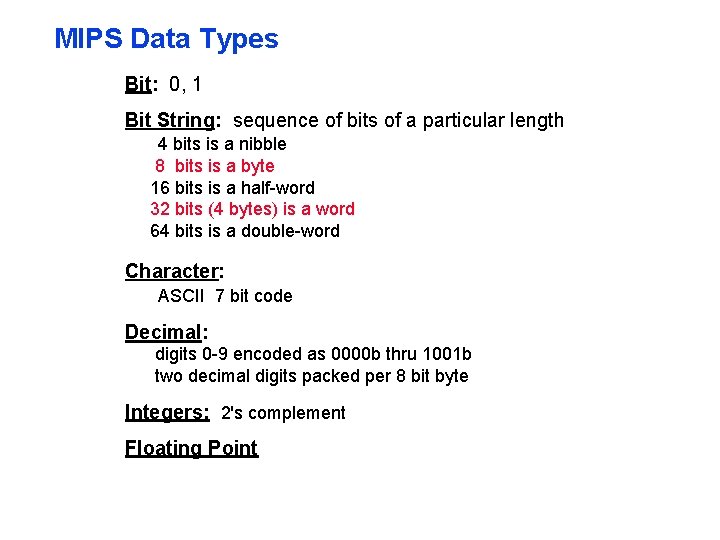

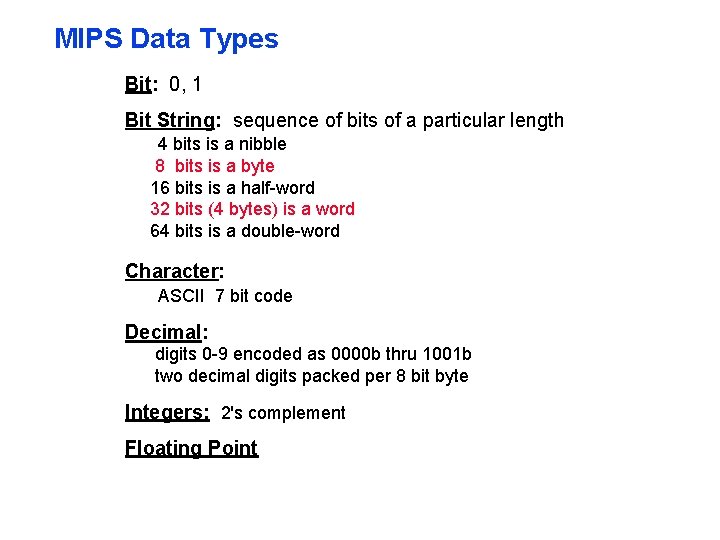

MIPS Data Types Bit: 0, 1 Bit String: sequence of bits of a particular length 4 bits is a nibble 8 bits is a byte 16 bits is a half-word 32 bits (4 bytes) is a word 64 bits is a double-word Character: ASCII 7 bit code Decimal: digits 0 -9 encoded as 0000 b thru 1001 b two decimal digits packed per 8 bit byte Integers: 2's complement Floating Point

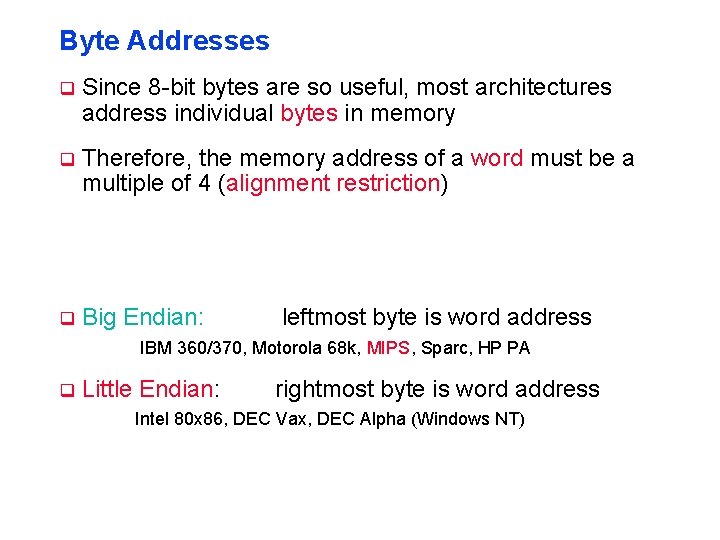

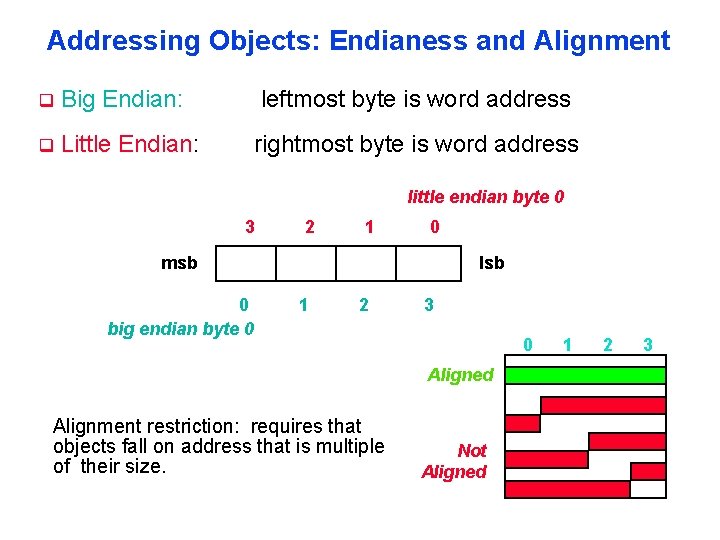

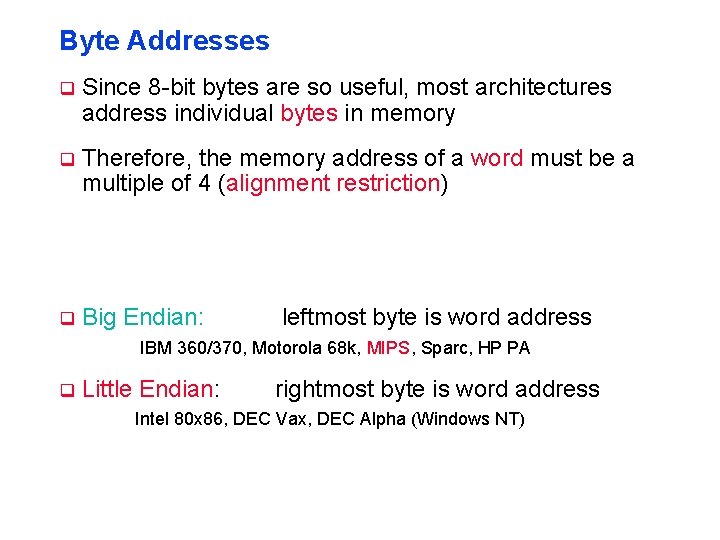

Byte Addresses q Since 8 -bit bytes are so useful, most architectures address individual bytes in memory q Therefore, the memory address of a word must be a multiple of 4 (alignment restriction) q Big Endian: leftmost byte is word address IBM 360/370, Motorola 68 k, MIPS, Sparc, HP PA q Little Endian: rightmost byte is word address Intel 80 x 86, DEC Vax, DEC Alpha (Windows NT)

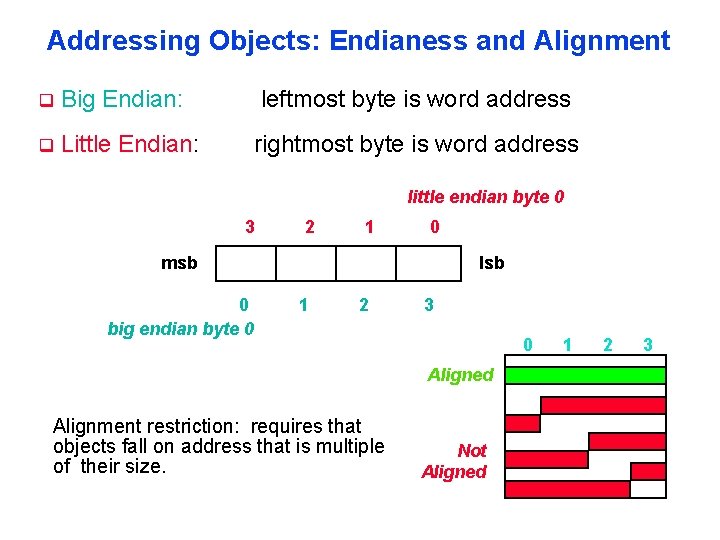

Addressing Objects: Endianess and Alignment q Big Endian: leftmost byte is word address q Little Endian: rightmost byte is word address little endian byte 0 3 2 1 0 msb 0 big endian byte 0 lsb 1 2 3 0 Aligned Alignment restriction: requires that objects fall on address that is multiple of their size. Not Aligned 1 2 3

MIPS Memory Addressing q The memory address is formed by summing the constant portion of the instruction and the contents of the second (base) register $s 3 holds 8 Memory . . . 0001 lw $t 0, 4($s 3) sw $t 0, 8($s 3) . . . 0110 24 . . . 0101 20 . . . 1100 16 . . . 0001 12 . . . 0010 8 . . . 1000 4 . . . 0100 Data 0 Word Address . . . 0001 #what? is loaded into $t 0 #$t 0 is stored where? in location 16

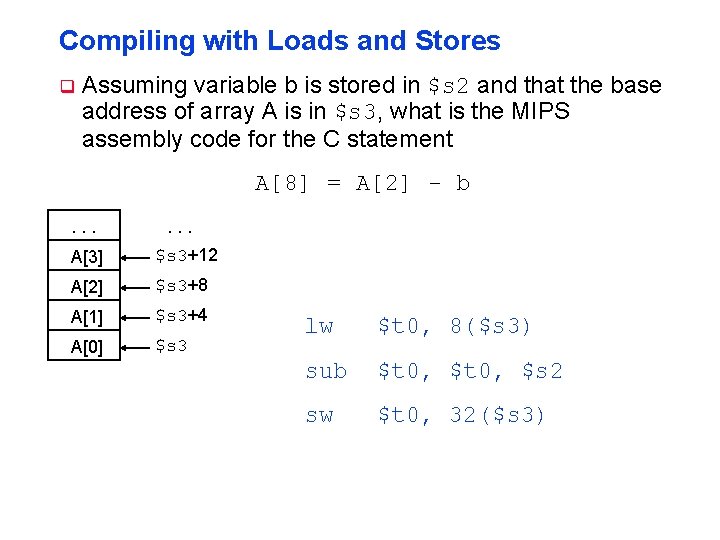

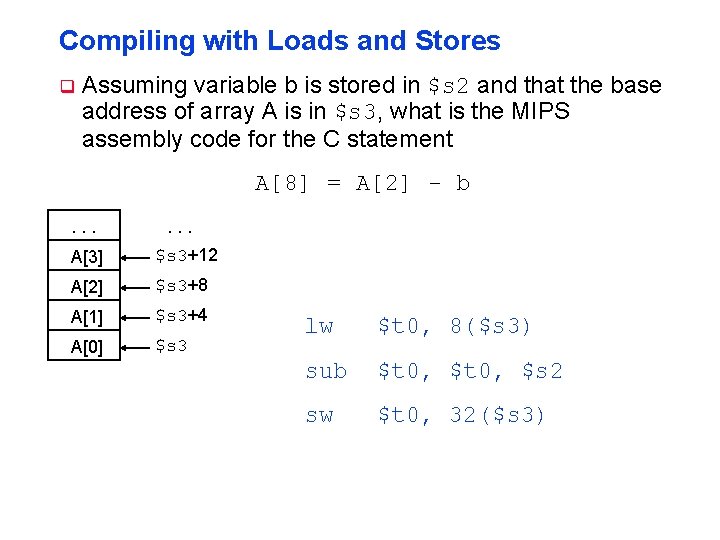

Compiling with Loads and Stores q Assuming variable b is stored in $s 2 and that the base address of array A is in $s 3, what is the MIPS assembly code for the C statement A[8] = A[2] - b . . . A[3] $s 3+12 A[2] $s 3+8 A[1] $s 3+4 A[0] $s 3 lw $t 0, 8($s 3) sub $t 0, $s 2 sw $t 0, 32($s 3)

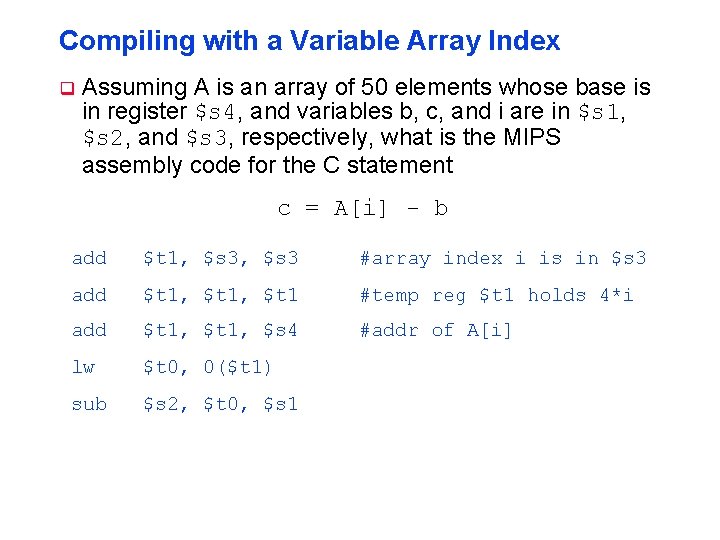

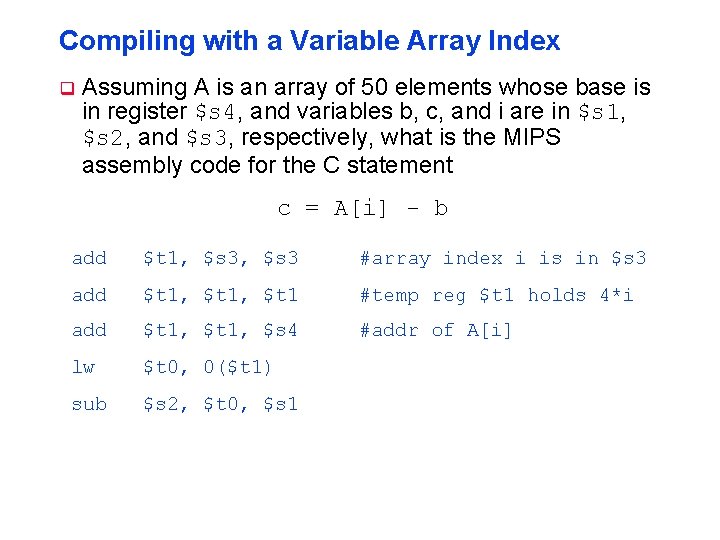

Compiling with a Variable Array Index q Assuming A is an array of 50 elements whose base is in register $s 4, and variables b, c, and i are in $s 1, $s 2, and $s 3, respectively, what is the MIPS assembly code for the C statement c = A[i] - b add $t 1, $s 3 #array index i is in $s 3 add $t 1, $t 1 #temp reg $t 1 holds 4*i add $t 1, $s 4 #addr of A[i] lw $t 0, 0($t 1) sub $s 2, $t 0, $s 1

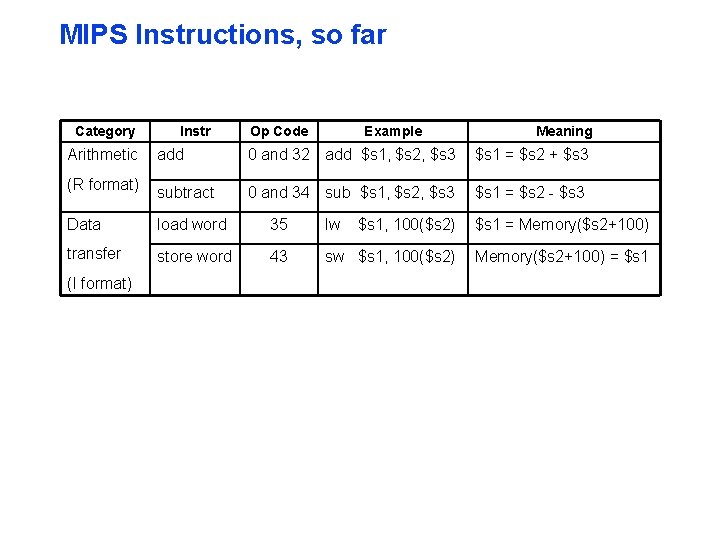

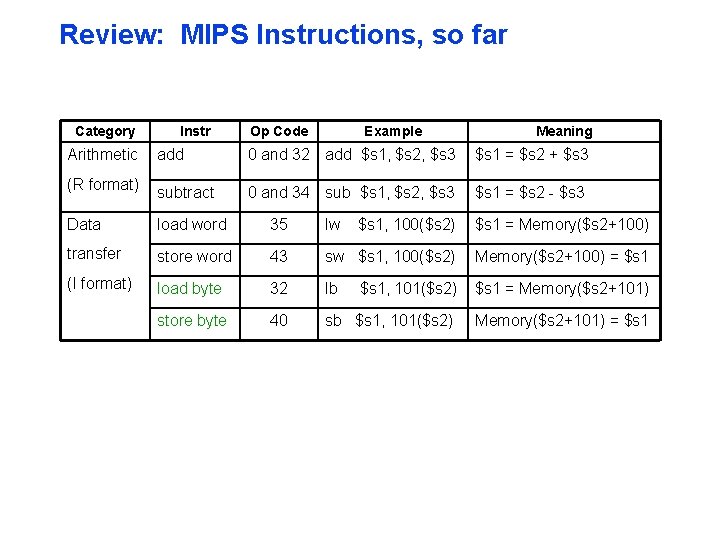

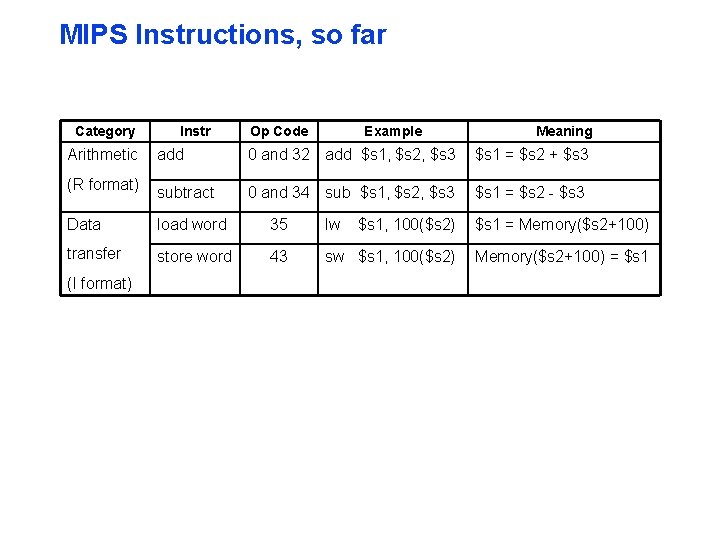

MIPS Instructions, so far Category Instr Op Code Example Meaning Arithmetic add 0 and 32 add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 (R format) subtract 0 and 34 sub $s 1, $s 2, $s 3 $s 1 = $s 2 - $s 3 Data load word 35 lw $s 1, 100($s 2) $s 1 = Memory($s 2+100) transfer store word 43 sw $s 1, 100($s 2) Memory($s 2+100) = $s 1 (I format)

A time was probably coming when components would operate so quickly that the distance that signals had to travel would intimately affect the speed of most commercial computers. Then miniaturization and speed would become more nearly synonymous. The Soul of a New Machine, Kidder, pg. 160

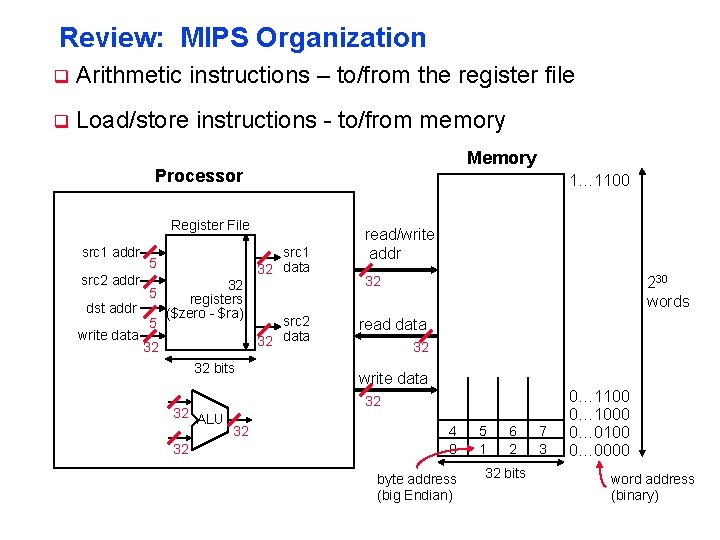

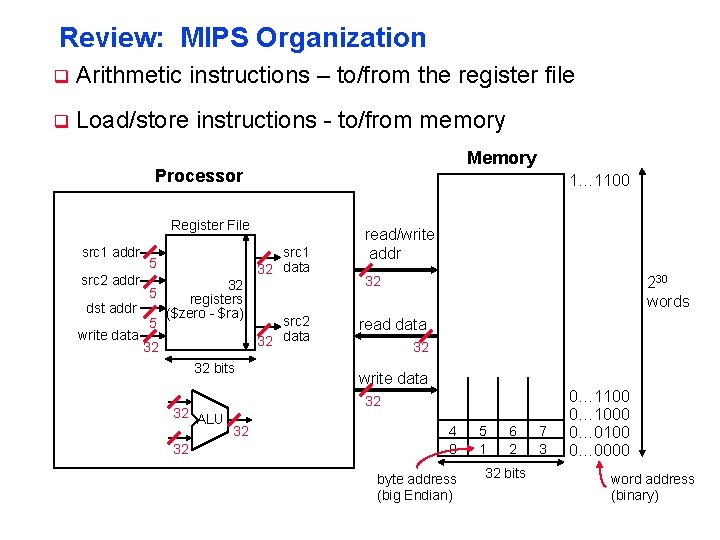

Review: MIPS Organization q Arithmetic instructions – to/from the register file q Load/store instructions - to/from memory Memory Processor 1… 1100 Register File src 1 addr src 1 data 32 5 src 2 addr 32 5 registers dst addr ($zero - $ra) src 2 5 write data 32 32 bits 32 ALU 32 read/write addr 32 230 words read data 32 write data 32 32 4 0 byte address (big Endian) 5 1 6 2 32 bits 7 3 0… 1100 0… 1000 0… 0100 0… 0000 word address (binary)

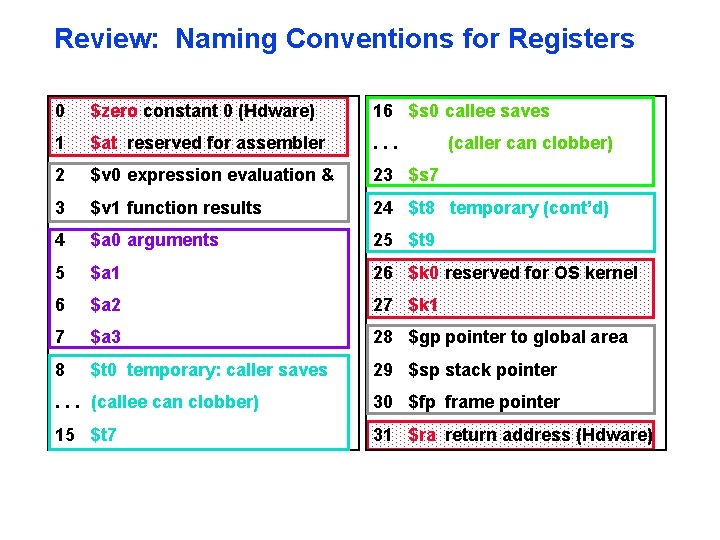

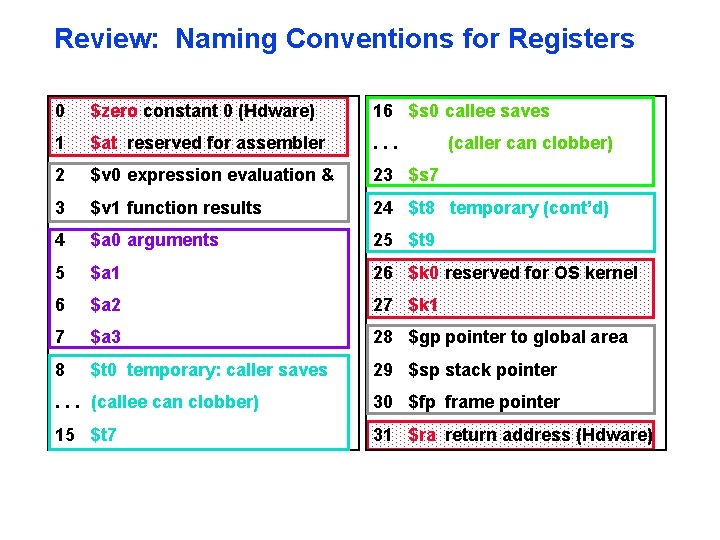

Review: Naming Conventions for Registers 0 $zero constant 0 (Hdware) 16 $s 0 callee saves 1 $at reserved for assembler . . . 2 $v 0 expression evaluation & 23 $s 7 3 $v 1 function results 24 $t 8 temporary (cont’d) 4 $a 0 arguments 25 $t 9 5 $a 1 26 $k 0 reserved for OS kernel 6 $a 2 27 $k 1 7 $a 3 28 $gp pointer to global area 8 $t 0 temporary: caller saves 29 $sp stack pointer (caller can clobber) . . . (callee can clobber) 30 $fp frame pointer 15 $t 7 31 $ra return address (Hdware)

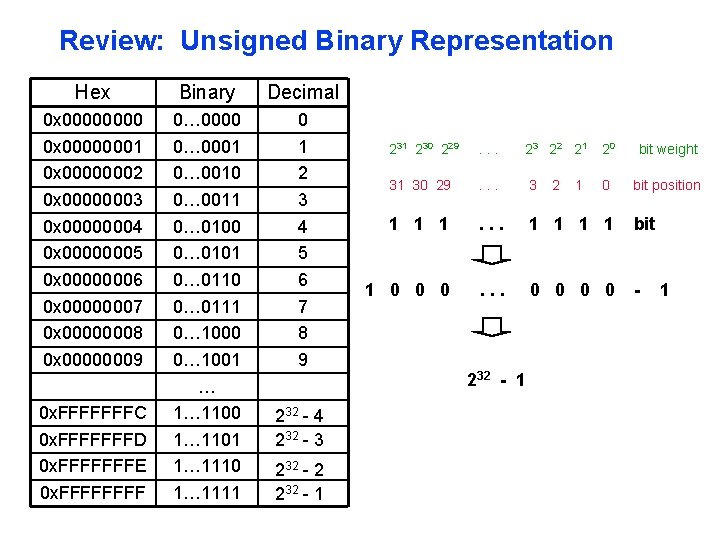

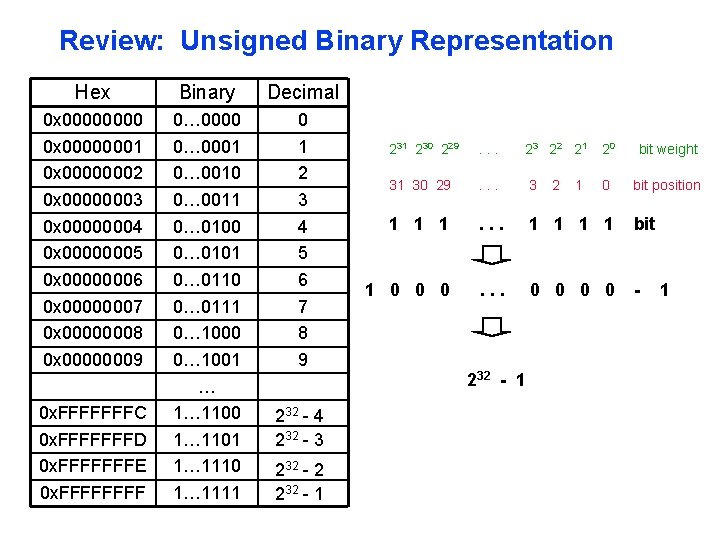

Review: Unsigned Binary Representation Hex Binary Decimal 0 x 00000001 0 x 00000002 0 x 00000003 0 x 00000004 0 x 00000005 0 x 00000006 0 x 00000007 0 x 00000008 0 x 00000009 0… 0000 0… 0001 0… 0010 0… 0011 0… 0100 0… 0101 0… 0110 0… 0111 0… 1000 0… 1001 … 1… 1100 1… 1101 1… 1110 1… 1111 0 1 2 3 4 5 6 7 8 9 0 x. FFFFFFFC 0 x. FFFFFFFD 0 x. FFFFFFFE 0 x. FFFF 232 - 4 232 - 3 232 - 2 232 - 1 230 229 . . . 2 3 22 21 20 bit weight 31 30 29 . . . 3 0 bit position 1 1 1 . . . 1 1 bit 1 0 0 0 . . . 0 0 - 232 - 1 2 1 1

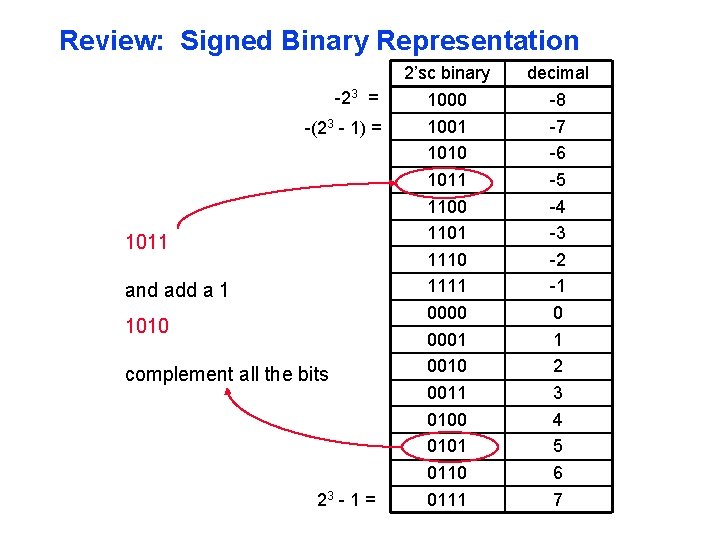

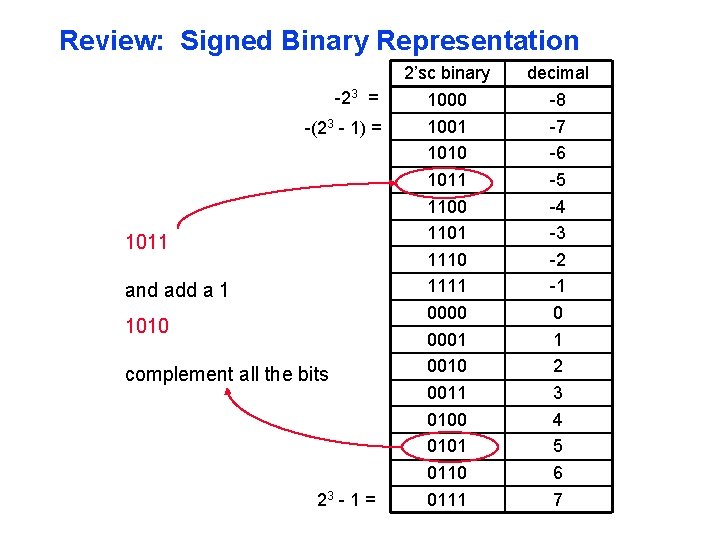

Review: Signed Binary Representation -23 = -(23 - 1) = 1011 and add a 1 1010 complement all the bits 23 - 1 = 2’sc binary 1000 1001 1010 1011 1100 1101 1110 1111 0000 0001 0010 0011 0100 0101 0110 0111 decimal -8 -7 -6 -5 -4 -3 -2 -1 0 1 2 3 4 5 6 7

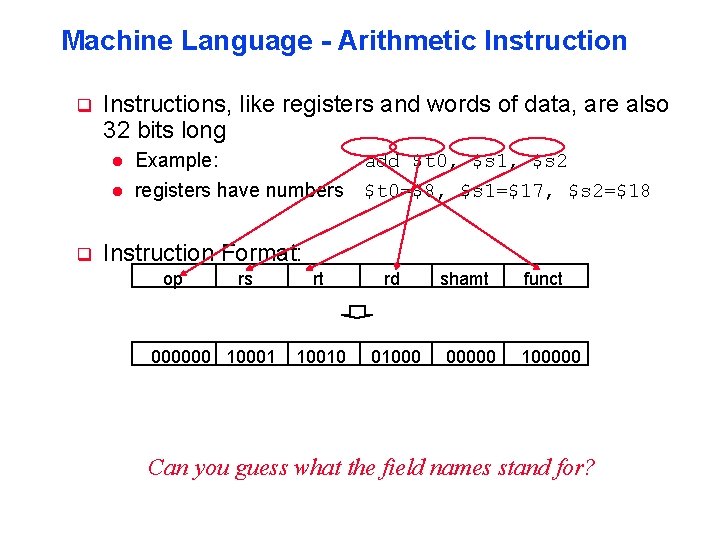

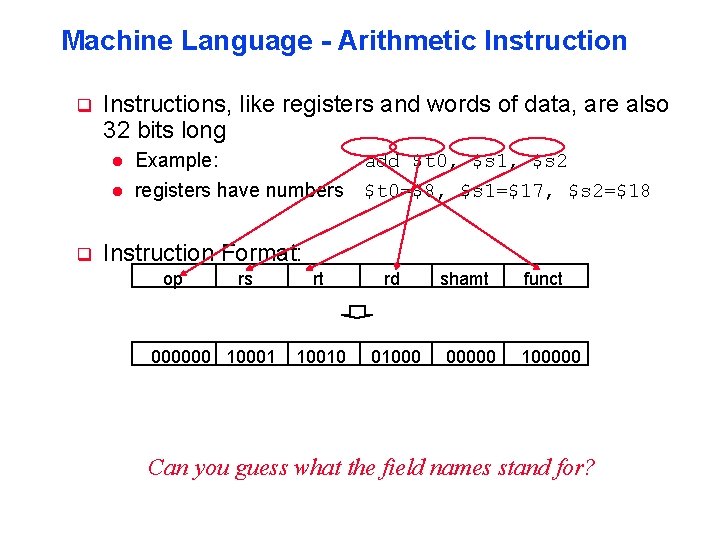

Machine Language - Arithmetic Instruction q Instructions, like registers and words of data, are also 32 bits long l l q Example: registers have numbers add $t 0, $s 1, $s 2 $t 0=$8, $s 1=$17, $s 2=$18 Instruction Format: op rs 000000 10001 rt rd 10010 01000 shamt 00000 funct 100000 Can you guess what the field names stand for?

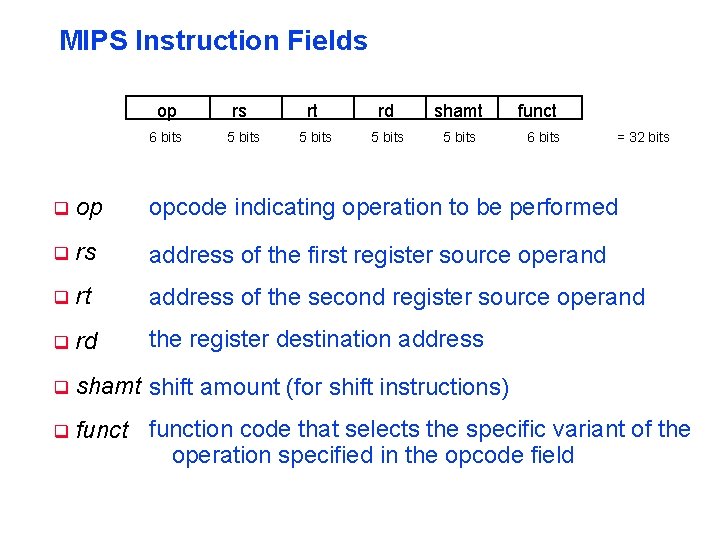

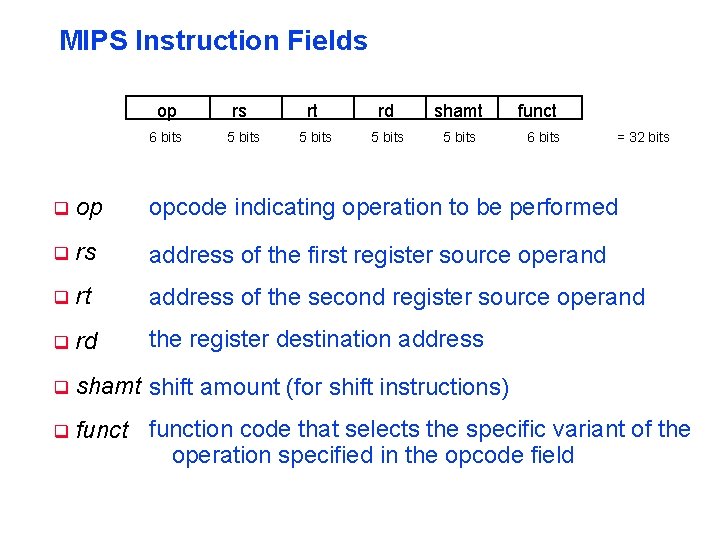

MIPS Instruction Fields op rs rt rd shamt 6 bits 5 bits funct 6 bits = 32 bits q op opcode indicating operation to be performed q rs address of the first register source operand q rt address of the second register source operand q rd the register destination address q shamt shift amount (for shift instructions) q function code that selects the specific variant of the operation specified in the opcode field

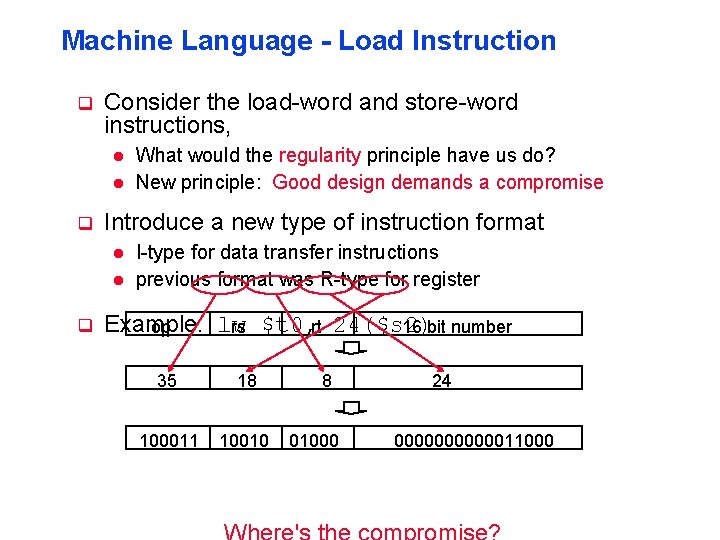

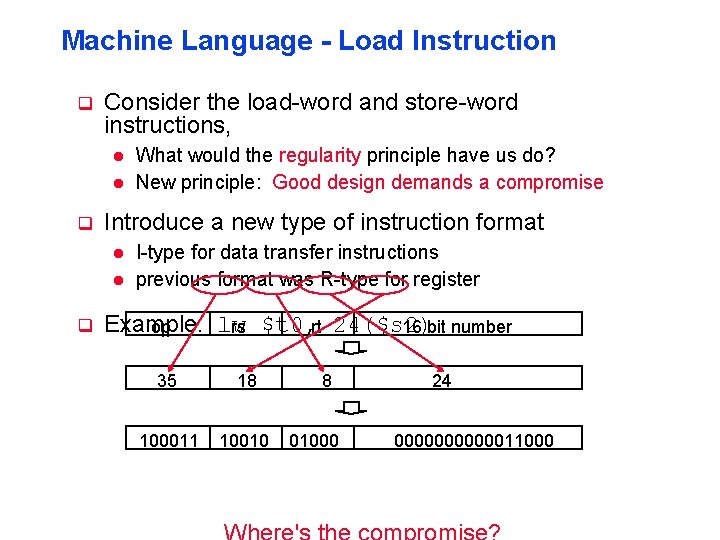

Machine Language - Load Instruction q Consider the load-word and store-word instructions, l l q Introduce a new type of instruction format l l q What would the regularity principle have us do? New principle: Good design demands a compromise I-type for data transfer instructions previous format was R-type for register Example: lw op rs $t 0, rt 24($s 2) 16 bit number 35 18 100011 10010 8 01000 24 00000011000

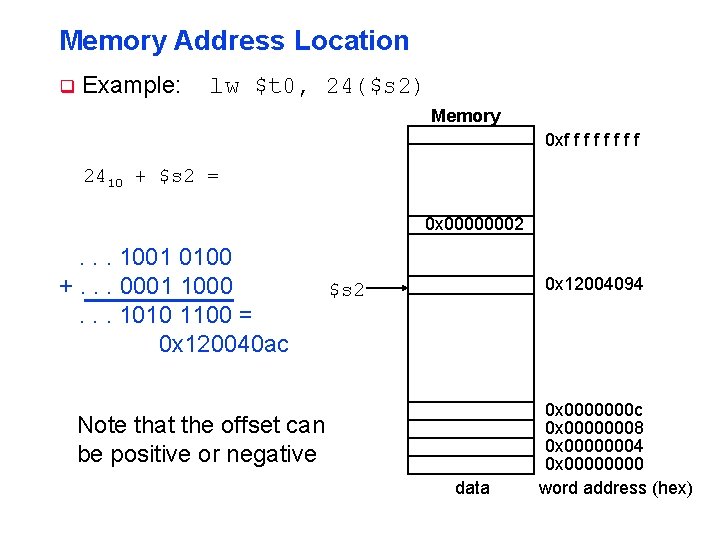

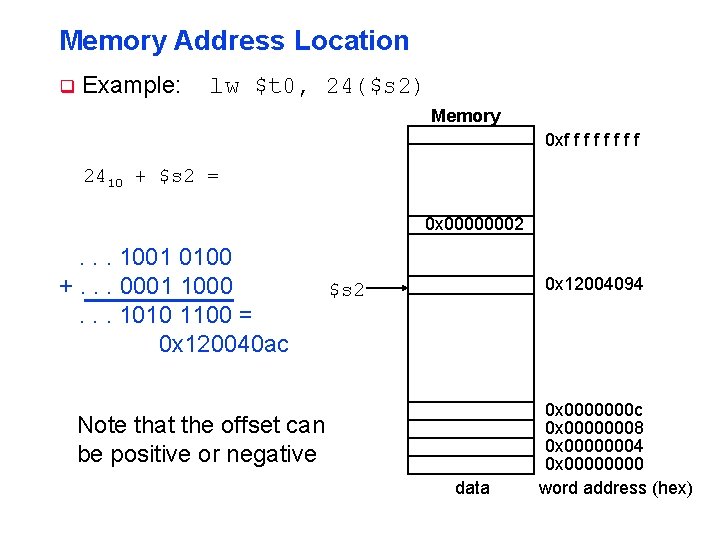

Memory Address Location q Example: lw $t 0, 24($s 2) Memory 0 xf f f f 2410 + $s 2 = 0 x 00000002 . . . 1001 0100 +. . . 0001 1000. . . 1010 1100 = 0 x 120040 ac 0 x 12004094 $s 2 Note that the offset can be positive or negative data 0 x 0000000 c 0 x 00000008 0 x 00000004 0 x 0000 word address (hex)

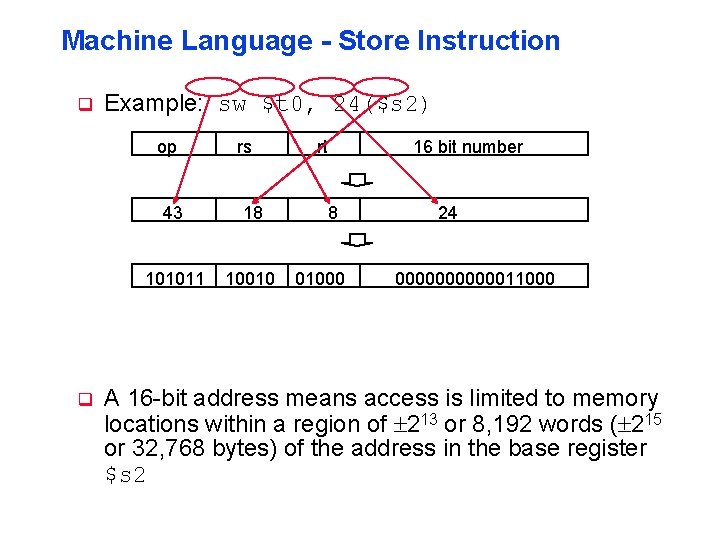

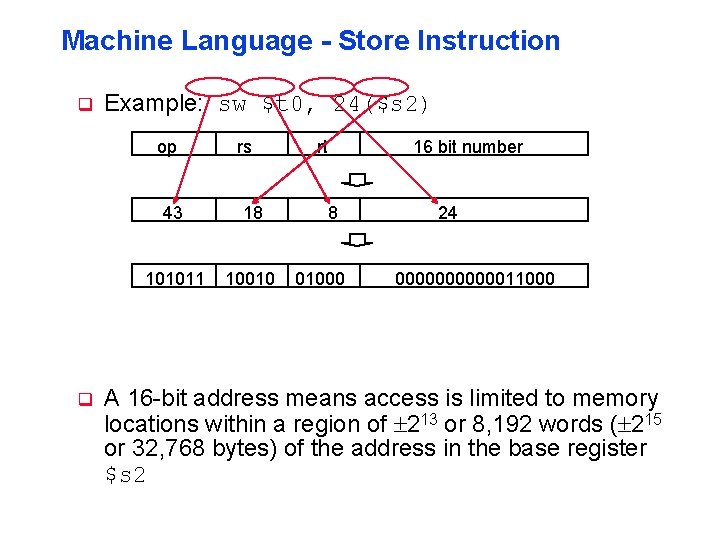

Machine Language - Store Instruction q Example: sw $t 0, 24($s 2) op q rs 43 18 101011 10010 rt 8 01000 16 bit number 24 00000011000 A 16 -bit address means access is limited to memory locations within a region of 213 or 8, 192 words ( 215 or 32, 768 bytes) of the address in the base register $s 2

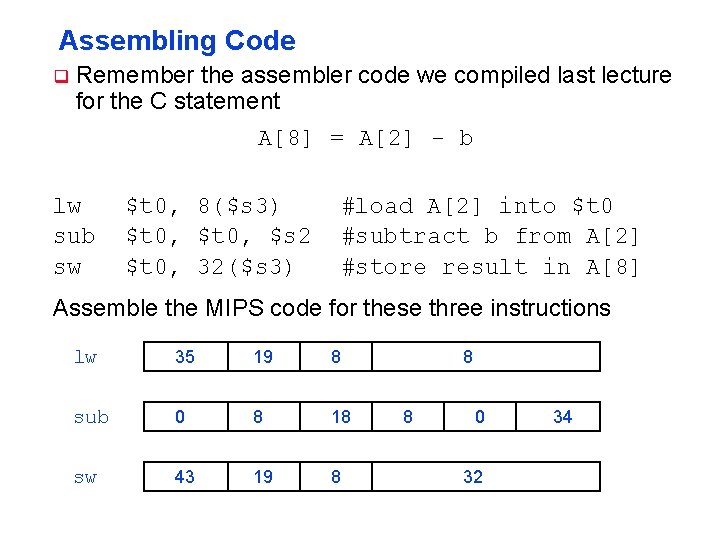

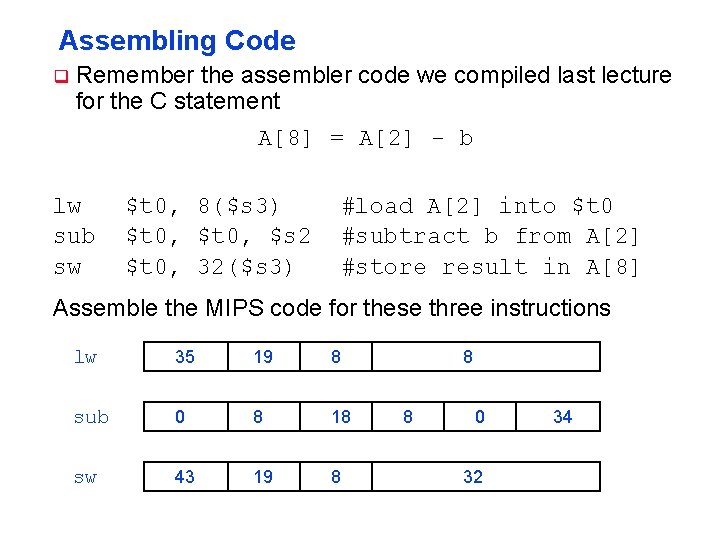

Assembling Code q Remember the assembler code we compiled last lecture for the C statement A[8] = A[2] - b lw sub sw $t 0, 8($s 3) $t 0, $s 2 $t 0, 32($s 3) #load A[2] into $t 0 #subtract b from A[2] #store result in A[8] Assemble the MIPS code for these three instructions lw 35 19 8 sub 0 8 18 sw 43 19 8 8 8 0 32 34

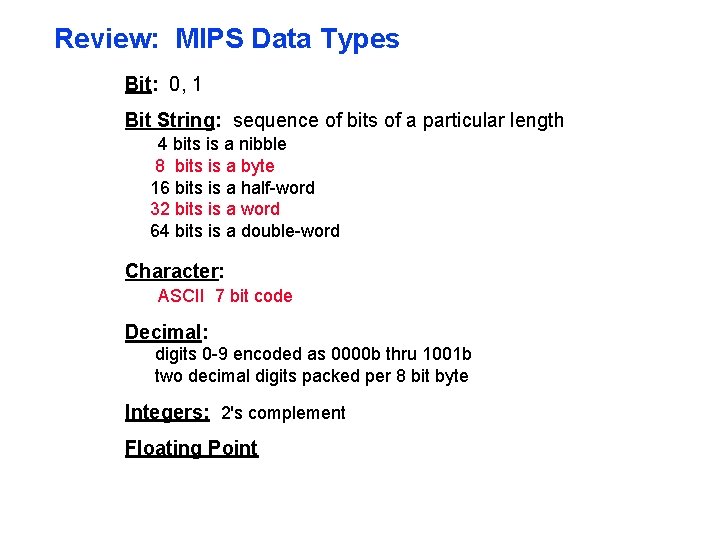

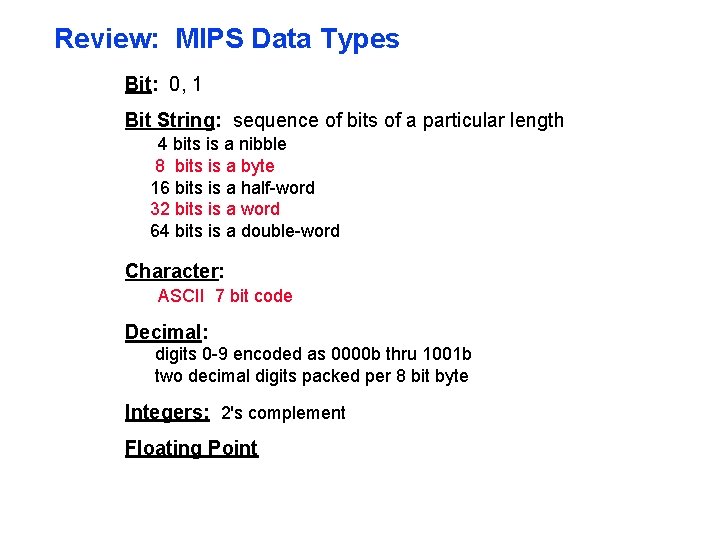

Review: MIPS Data Types Bit: 0, 1 Bit String: sequence of bits of a particular length 4 bits is a nibble 8 bits is a byte 16 bits is a half-word 32 bits is a word 64 bits is a double-word Character: ASCII 7 bit code Decimal: digits 0 -9 encoded as 0000 b thru 1001 b two decimal digits packed per 8 bit byte Integers: 2's complement Floating Point

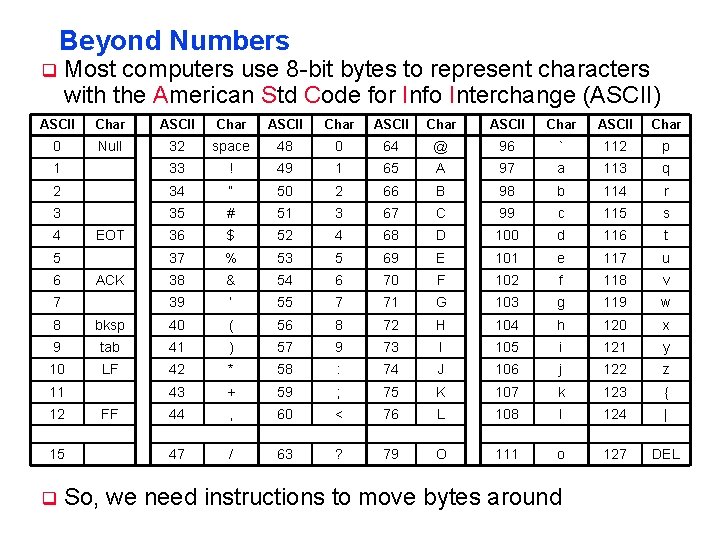

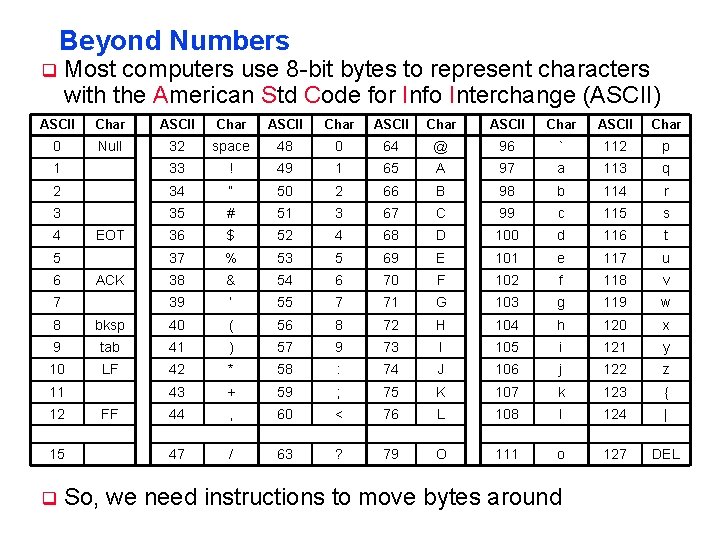

Beyond Numbers q Most computers use 8 -bit bytes to represent characters with the American Std Code for Info Interchange (ASCII) ASCII Char ASCII Char 0 Null 32 space 48 0 64 @ 96 ` 112 p 1 33 ! 49 1 65 A 97 a 113 q 2 34 “ 50 2 66 B 98 b 114 r 3 35 # 51 3 67 C 99 c 115 s 36 $ 52 4 68 D 100 d 116 t 37 % 53 5 69 E 101 e 117 u 38 & 54 6 70 F 102 f 118 v 39 ‘ 55 7 71 G 103 g 119 w 4 EOT 5 6 ACK 7 8 bksp 40 ( 56 8 72 H 104 h 120 x 9 tab 41 ) 57 9 73 I 105 i 121 y 10 LF 42 * 58 : 74 J 106 j 122 z 43 + 59 ; 75 K 107 k 123 { 44 , 60 < 76 L 108 l 124 | 47 / 63 ? 79 O 111 o 127 DEL 11 12 15 q FF So, we need instructions to move bytes around

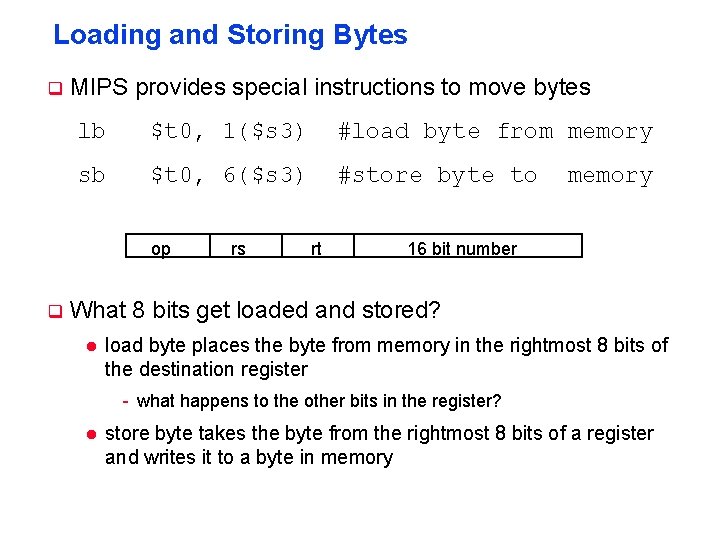

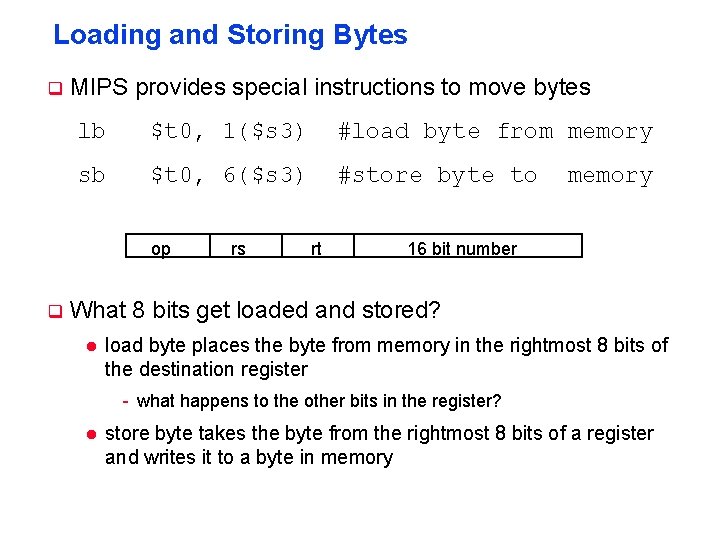

Loading and Storing Bytes q MIPS provides special instructions to move bytes lb $t 0, 1($s 3) #load byte from memory sb $t 0, 6($s 3) #store byte to op q rs rt memory 16 bit number What 8 bits get loaded and stored? l load byte places the byte from memory in the rightmost 8 bits of the destination register - what happens to the other bits in the register? l store byte takes the byte from the rightmost 8 bits of a register and writes it to a byte in memory

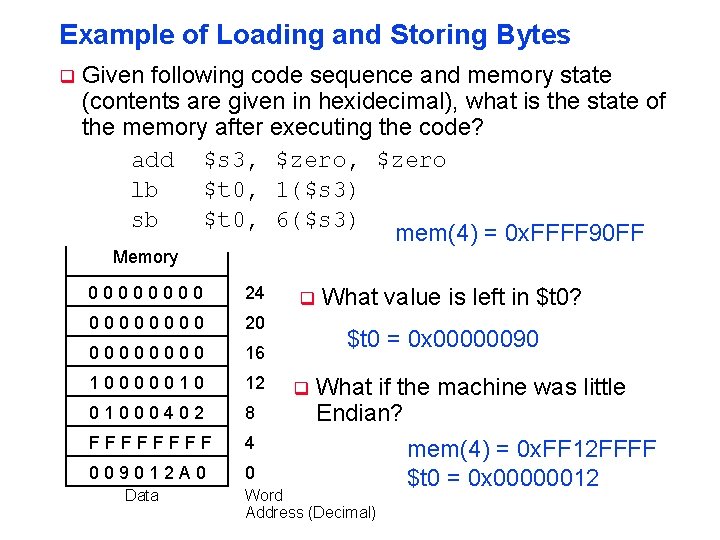

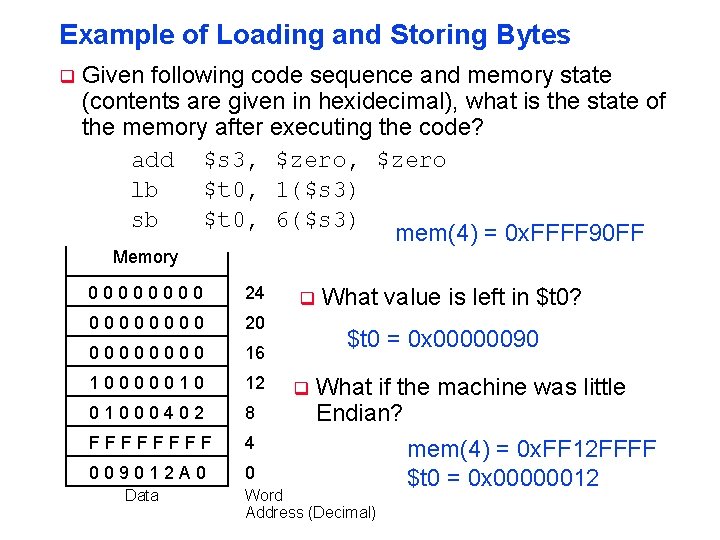

Example of Loading and Storing Bytes q Given following code sequence and memory state (contents are given in hexidecimal), what is the state of the memory after executing the code? add $s 3, $zero lb $t 0, 1($s 3) sb $t 0, 6($s 3) mem(4) = 0 x. FFFF 90 FF Memory 0000 24 0000 20 0000 16 10000010 12 01000402 8 FFFF 4 009012 A 0 0 Data q What value is left in $t 0? $t 0 = 0 x 00000090 q What if the machine was little Endian? Word Address (Decimal) mem(4) = 0 x. FF 12 FFFF $t 0 = 0 x 00000012

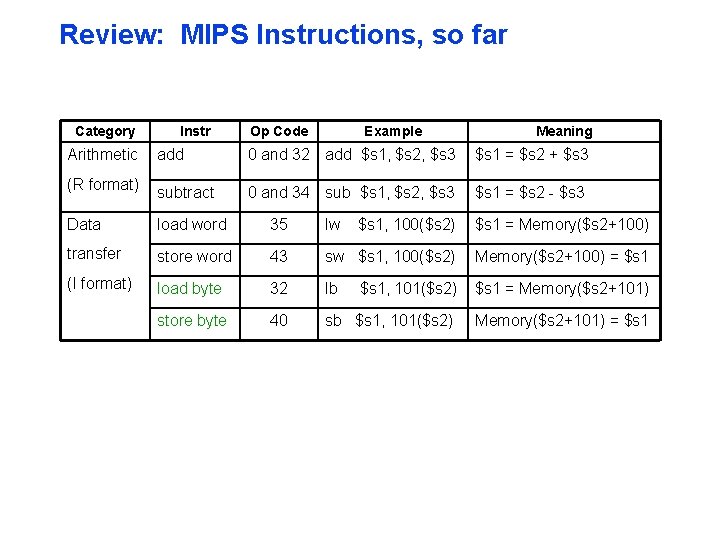

Review: MIPS Instructions, so far Category Instr Op Code Example Meaning Arithmetic add 0 and 32 add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 (R format) subtract 0 and 34 sub $s 1, $s 2, $s 3 $s 1 = $s 2 - $s 3 Data load word 35 lw $s 1, 100($s 2) $s 1 = Memory($s 2+100) transfer store word 43 sw $s 1, 100($s 2) Memory($s 2+100) = $s 1 (I format) load byte 32 lb $s 1, 101($s 2) $s 1 = Memory($s 2+101) store byte 40 sb $s 1, 101($s 2) Memory($s 2+101) = $s 1

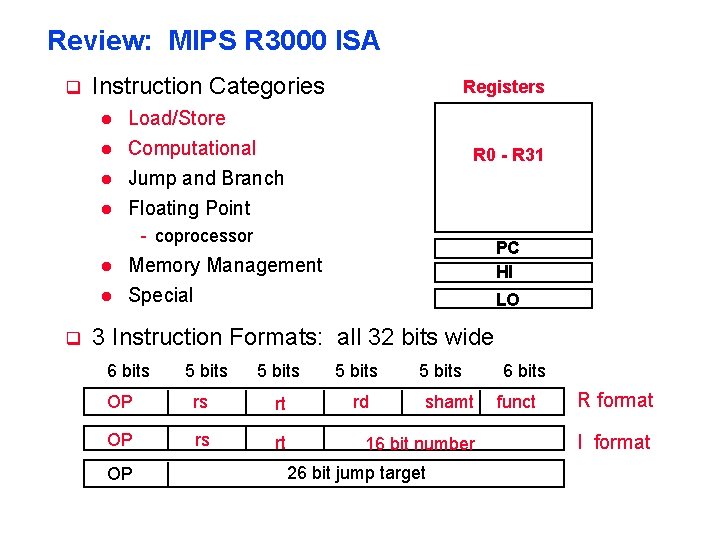

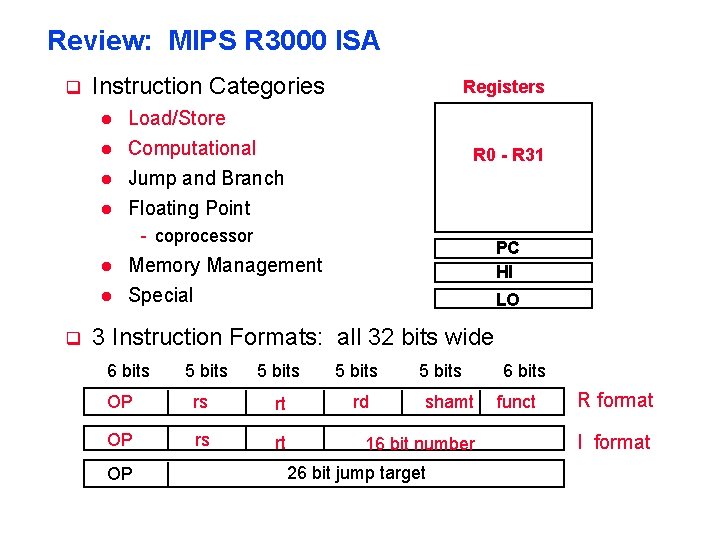

Review: MIPS R 3000 ISA q Instruction Categories Registers R 0 - R 31 l Load/Store Computational Jump and Branch l Floating Point l l - coprocessor q l Memory Management PC HI l Special LO 3 Instruction Formats: all 32 bits wide 6 bits 5 bits rd OP rs rt OP 5 bits shamt 16 bit number 26 bit jump target 6 bits funct R format I format