CS 2204 Laboratory Digital Design Haldun Hadimioglu Computer

CS 2204 Laboratory Digital Design Haldun Hadimioglu Computer and Information Science 3/30/2003 Digital Design

CS 2204 Title : Digital Logic and State Machine Design Credits : 4 Year : Sophomore Format : Lectures and Laboratory 3 -hour lectures 3 -hour laboratory sessions 3/30/2003 Digital Design 2

CS 2204 Content : Digital circuit fundamentals Theory, analysis, design Digital clock Car alarm Traffic light controller Vending machine controller Four function calculator Precursor to courses : Computer Architecture : computer design (junior) Advanced hardware design : chip design (senior) 3/30/2003 Digital Design 3

CS 2204 Laboratory Emphasis on design 20 students per lab 2 -student teams formed first week Teams do lab projects and homework How to approach a large design Problem analysis and solving 3/30/2003 Digital Design 4

CS 2204 Laboratory Introduces current digital design techniques and tools Team-oriented, top-down, corebased design Modern hardware development environment 3/30/2003 Digital Design 5

CS 2204 Laboratory Hardware development environment Computer Aided Design (CAD) Software : Xilinx Foundation (industry software) Simulates hardware Testing hardware : Digilent board FPGA Chip on Digilent board FPGA : Field Programmable Gate Array Emulates hardware 3/30/2003 Digital Design 6

CS 2204 Laboratory Why CAD Design ? Circuit design and test before physical implementation Shorter and cheaper development Design objectives reached faster Speed, cost, power consumption, size, weight, reliability, . . 3/30/2003 Digital Design 7

CS 2204 Laboratory Term Project Spring 2003 : Game playing circuit Human vs machine play against each other Derived from dominoes Chance and thinking determine winner Pieces of circuit completed in 3 to 4 week experiments (deadlines) 3/30/2003 Digital Design 8

Historical Trend Mechanical components replaced by Analog components and Digital components Analog components replaced by Digital components 3/30/2003 Digital Design 9

Digital Revolution Computers (laptops to supercomputers) Microprocessors (Sun Sparc to Intel Pentium 4) Car engine controllers Calculators Video games CD Players Digital cameras 3/30/2003 Digital Design 10

Benefits of Digital Circuits Moore’s Law holds since the 1960 s Every two years, number of transistors on chips doubles Every two years memory size doubles Smaller size devices 3/30/2003 Digital Design 11

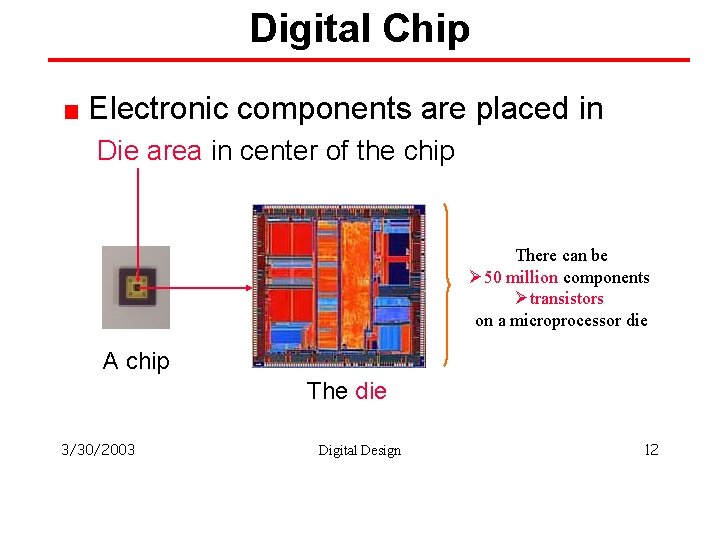

Digital Chip Electronic components are placed in Die area in center of the chip There can be Ø 50 million components Øtransistors on a microprocessor die A chip The die 3/30/2003 Digital Design 12

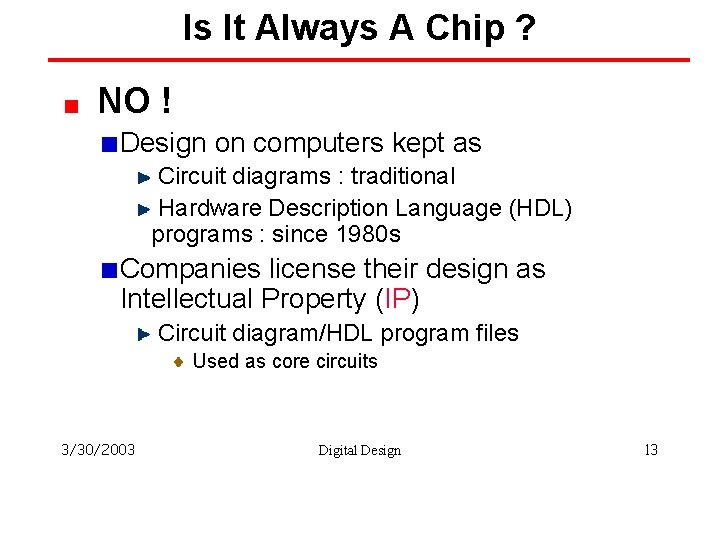

Is It Always A Chip ? NO ! Design on computers kept as Circuit diagrams : traditional Hardware Description Language (HDL) programs : since 1980 s Companies license their design as Intellectual Property (IP) Circuit diagram/HDL program files Used as core circuits 3/30/2003 Digital Design 13

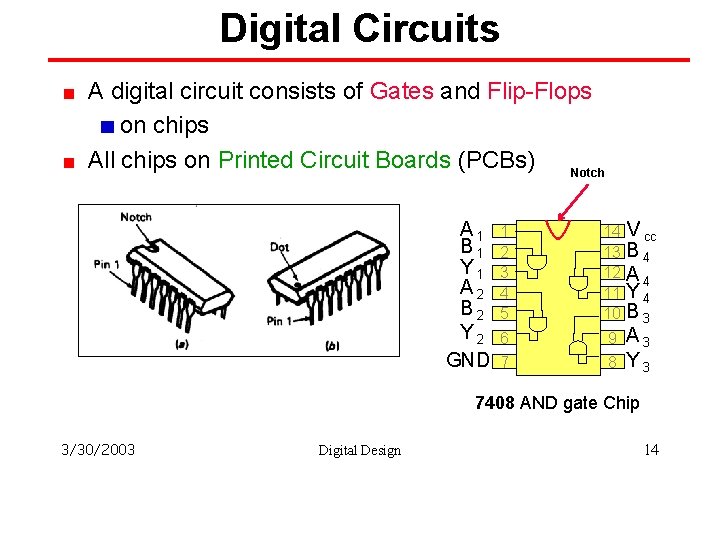

Digital Circuits A digital circuit consists of Gates and Flip-Flops on chips All chips on Printed Circuit Boards (PCBs) Notch A 1 B 1 Y 1 A 2 B 2 Y 2 GND 1 2 3 4 5 14 13 12 11 10 6 9 7 8 V cc B 4 A 4 Y 4 B 3 A 3 Y 3 7408 AND gate Chip 3/30/2003 Digital Design 14

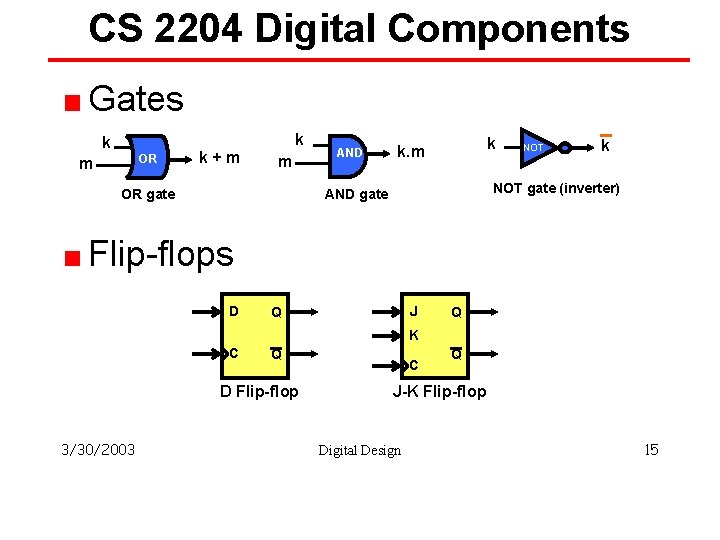

CS 2204 Digital Components Gates k k OR m k+m m OR gate AND k k. m NOT k NOT gate (inverter) AND gate Flip-flops D J Q Q K C Q D Flip-flop 3/30/2003 C Q J-K Flip-flop Digital Design 15

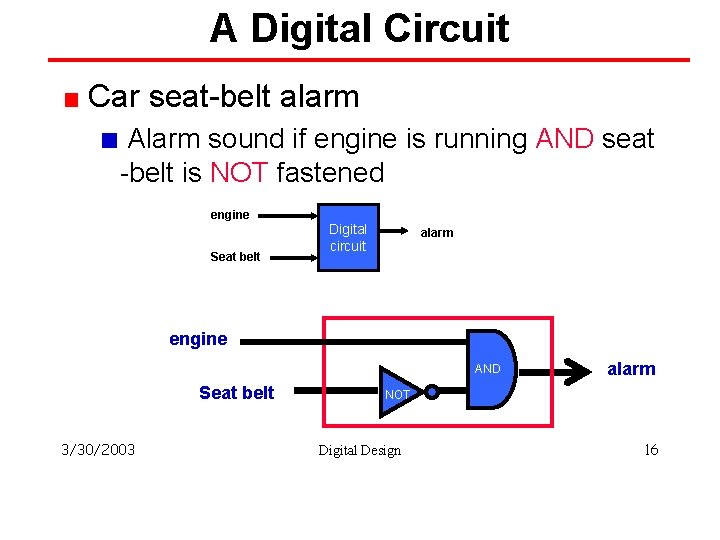

A Digital Circuit Car seat-belt alarm Alarm sound if engine is running AND seat -belt is NOT fastened engine Seat belt Digital circuit alarm engine alarm AND Seat belt 3/30/2003 NOT OR Digital Design AND 16

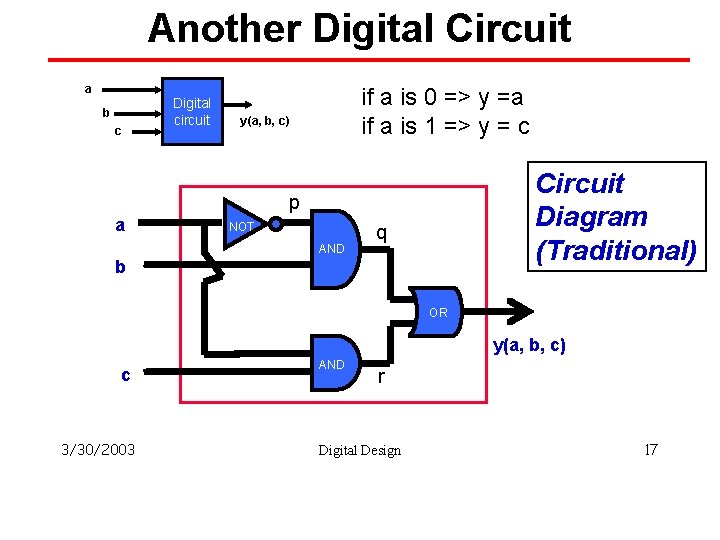

Another Digital Circuit a b c Digital circuit if a is 0 => y =a if a is 1 => y = c y(a, b, c) Circuit Diagram (Traditional) p a NOT AND q b OR y(a, b, c) c 3/30/2003 AND r Digital Design 17

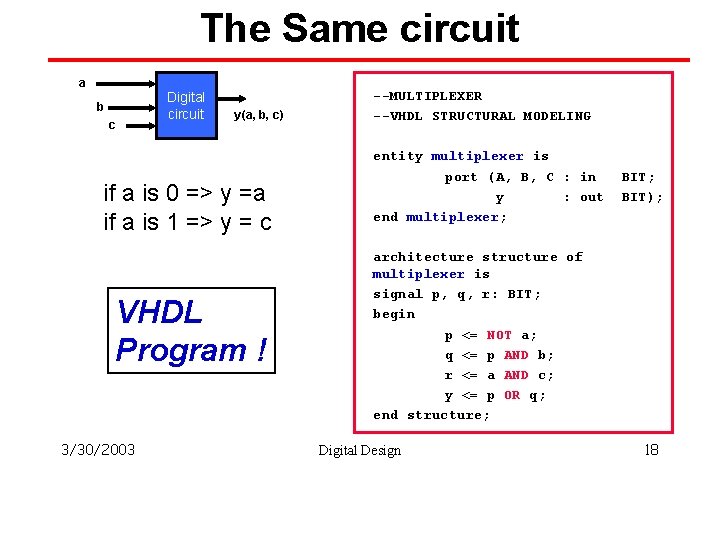

The Same circuit a b c Digital circuit y(a, b, c) if a is 0 => y =a if a is 1 => y = c VHDL Program ! 3/30/2003 --MULTIPLEXER --VHDL STRUCTURAL MODELING entity multiplexer is port (A, B, C : in y : out end multiplexer; BIT; BIT); architecture structure of multiplexer is signal p, q, r: BIT; begin p <= NOT a; q <= p AND b; r <= a AND c; y <= p OR q; end structure; Digital Design 18

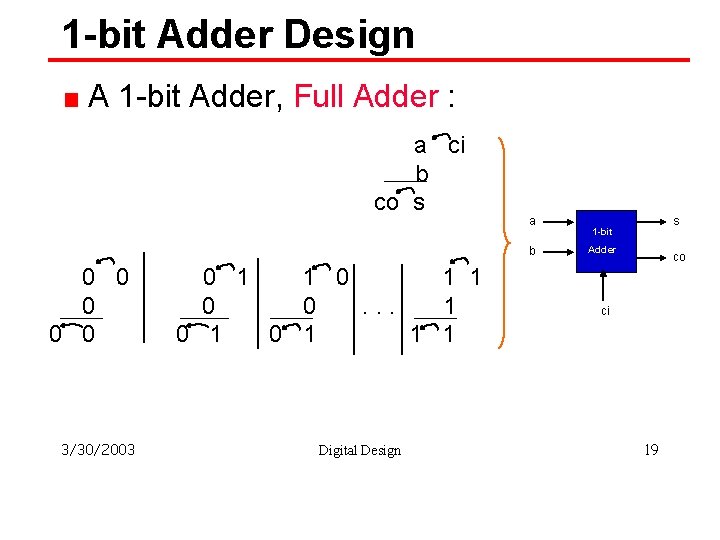

1 -bit Adder Design A 1 -bit Adder, Full Adder : a ci b co s a b 0 0 0 3/30/2003 0 1 1 0 0. . . 1 0 1 1 1 Digital Design s 1 -bit Adder co ci 19

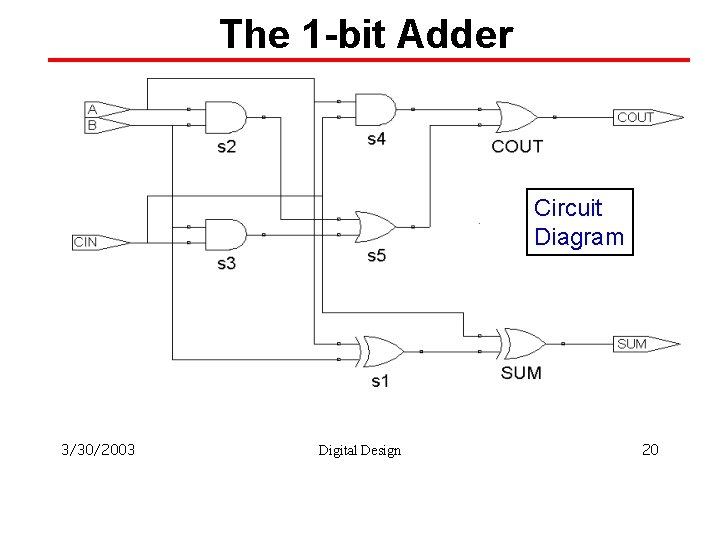

The 1 -bit Adder Circuit Diagram 3/30/2003 Digital Design 20

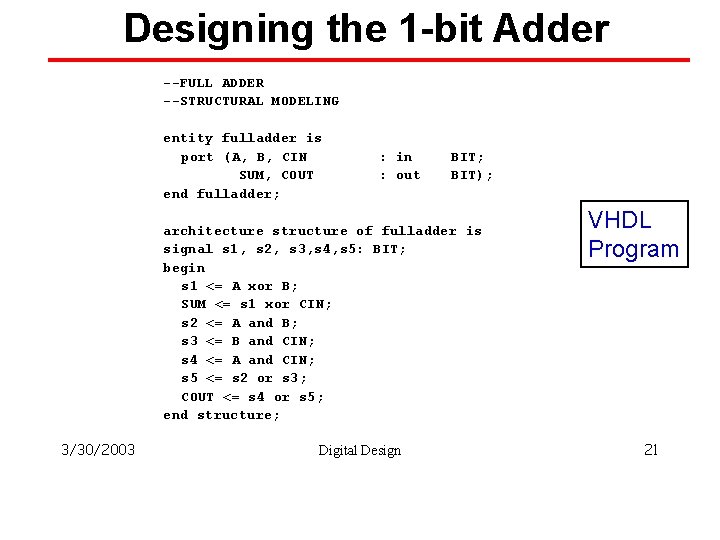

Designing the 1 -bit Adder --FULL ADDER --STRUCTURAL MODELING entity fulladder is port (A, B, CIN SUM, COUT end fulladder; : in : out BIT; BIT); architecture structure of fulladder is signal s 1, s 2, s 3, s 4, s 5: BIT; begin s 1 <= A xor B; SUM <= s 1 xor CIN; s 2 <= A and B; s 3 <= B and CIN; s 4 <= A and CIN; s 5 <= s 2 or s 3; COUT <= s 4 or s 5; end structure; 3/30/2003 Digital Design VHDL Program 21

- Slides: 21