COMP 1321 Digital Infrastructure Richard Henson University of

![Moving data into Memory For example … mov [3] , ax mov [0] , Moving data into Memory For example … mov [3] , ax mov [0] ,](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-7.jpg)

![Fetch-Exec : State 1 Instruction Fetch mov ax , [1] mov ax 1 0 Fetch-Exec : State 1 Instruction Fetch mov ax , [1] mov ax 1 0](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-20.jpg)

![Fetch-Exec : State 2 Decode, Register Operations mov ax , [1] mov ax 1 Fetch-Exec : State 2 Decode, Register Operations mov ax , [1] mov ax 1](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-21.jpg)

![Fetch-Exec : State 3 ALU Operation mov ax , [1] mov ax 1 1 Fetch-Exec : State 3 ALU Operation mov ax , [1] mov ax 1 1](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-22.jpg)

![Fetch-Exec : State 4 Memory Access mov ax , [1] mov ax 1 8 Fetch-Exec : State 4 Memory Access mov ax , [1] mov ax 1 8](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-23.jpg)

![Fetch-Exec : State 5 Register Write mov ax , [1] mov ax 1 8 Fetch-Exec : State 5 Register Write mov ax , [1] mov ax 1 8](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-24.jpg)

- Slides: 31

COMP 1321 Digital Infrastructure Richard Henson University of Worcester October 2018

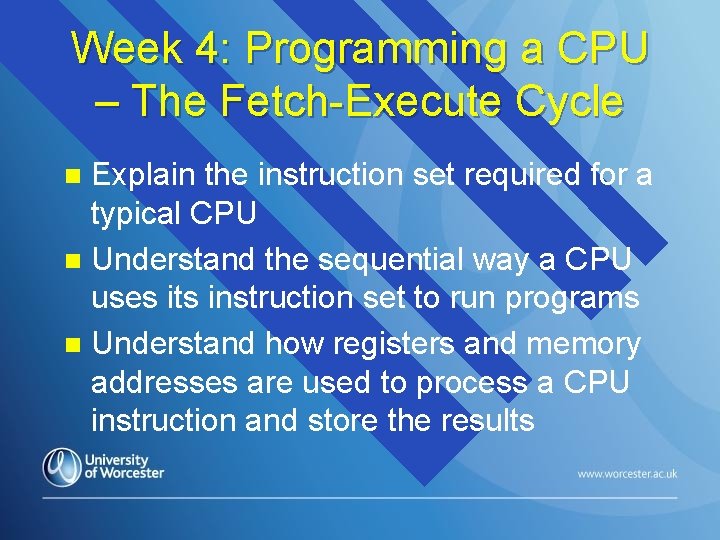

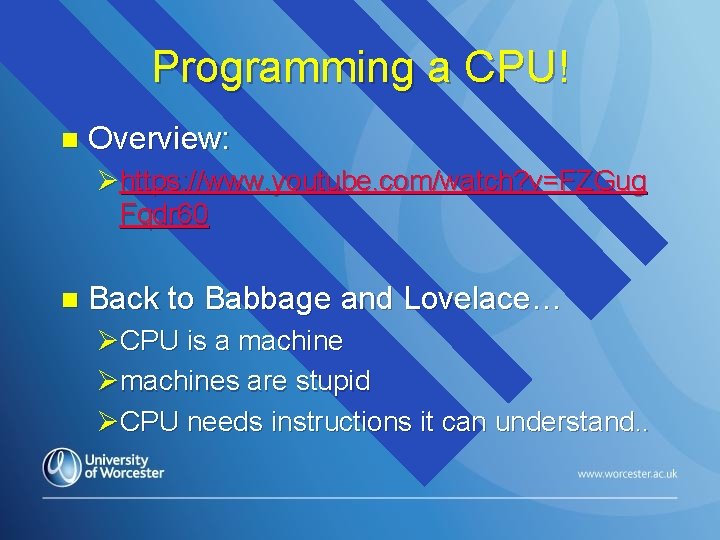

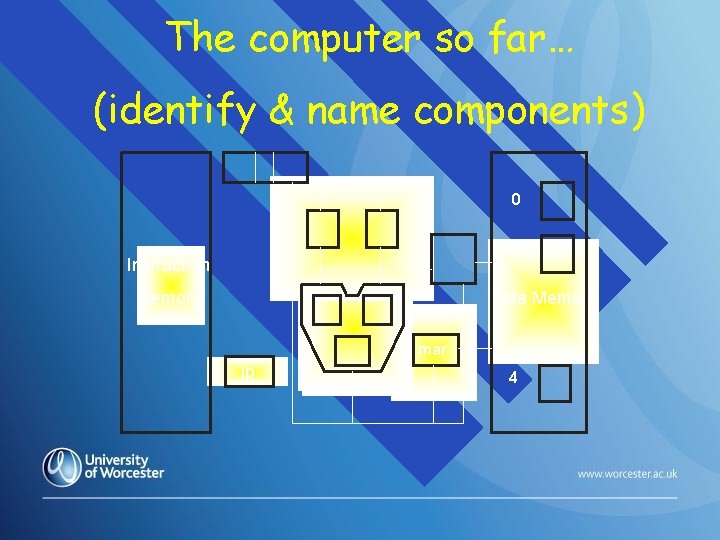

Week 4: Programming a CPU – The Fetch-Execute Cycle Explain the instruction set required for a typical CPU n Understand the sequential way a CPU uses its instruction set to run programs n Understand how registers and memory addresses are used to process a CPU instruction and store the results n

Programming a CPU! n Overview: Øhttps: //www. youtube. com/watch? v=FZGug Fqdr 60 n Back to Babbage and Lovelace… ØCPU is a machine Ømachines are stupid ØCPU needs instructions it can understand. .

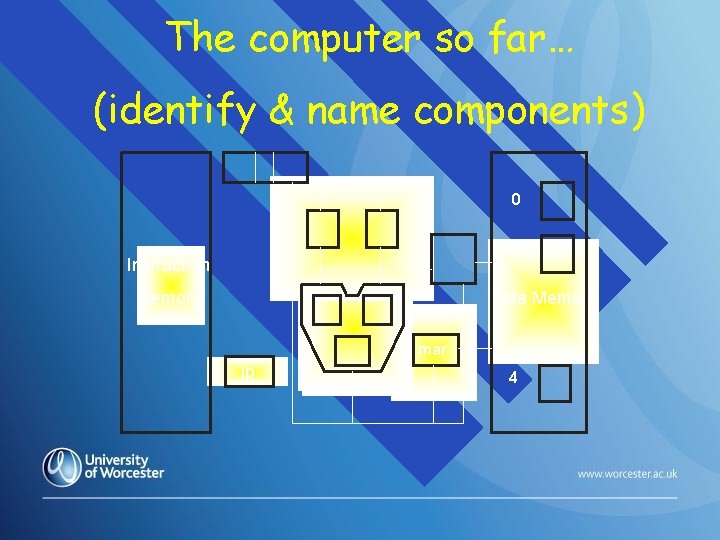

The computer so far… (identify & name components) 0 1 Instruction Memory Data Memory mar ip 4

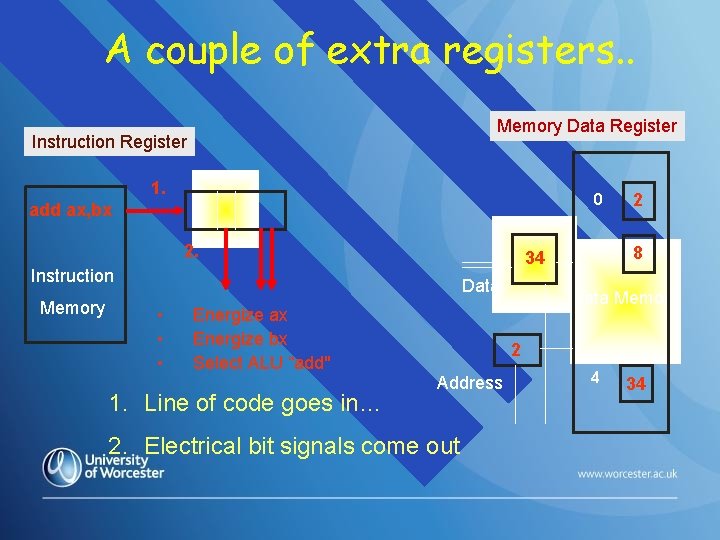

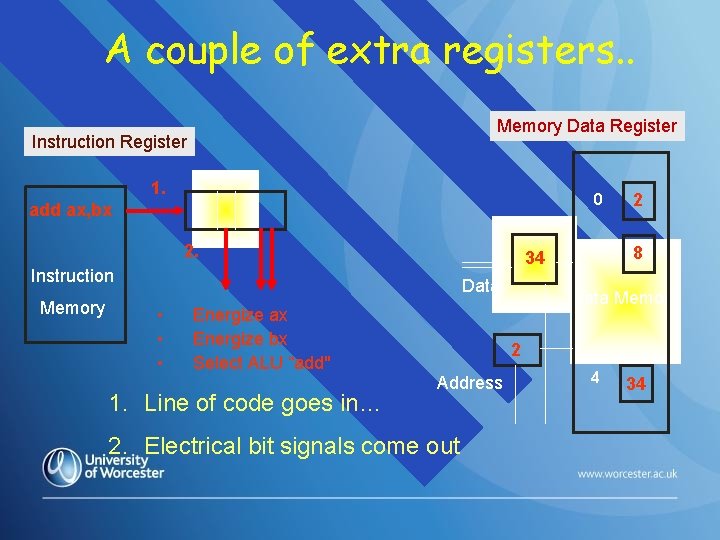

A couple of extra registers. . Memory Data Register Instruction Register 1. add ax, bx 2. 34 Instruction Memory Data • • • Energize ax Energize bx Select ALU “add" 1. Line of code goes in… 0 2 1 8 Data Memory 2 Address 2. Electrical bit signals come out 4 34

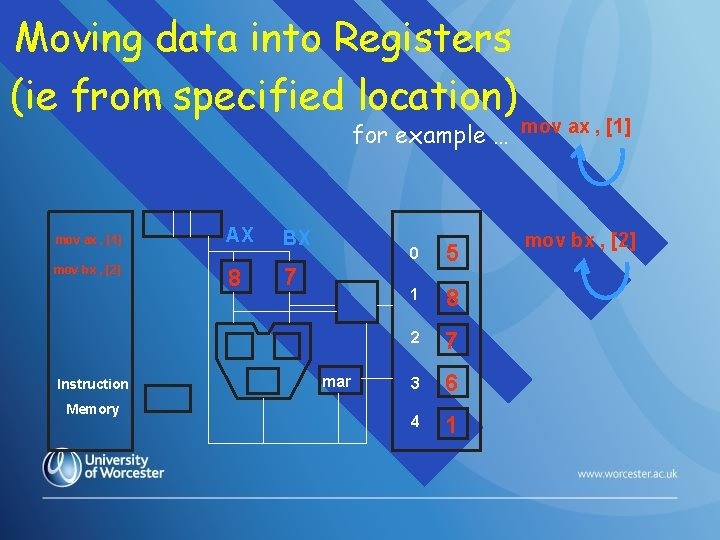

Moving data into Registers (ie from specified location) for example … mov ax , [1] mov bx , [2] Instruction Memory AX BX 8 7 mar 0 5 1 8 2 7 3 6 4 1 mov bx , [2]

![Moving data into Memory For example mov 3 ax mov 0 Moving data into Memory For example … mov [3] , ax mov [0] ,](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-7.jpg)

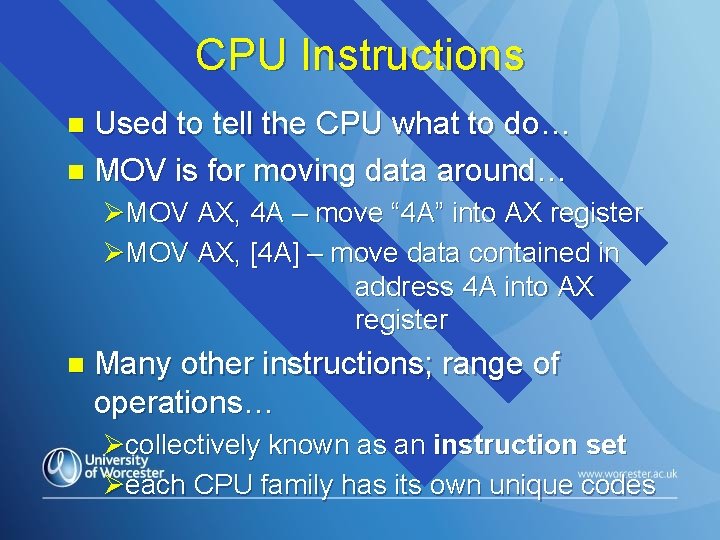

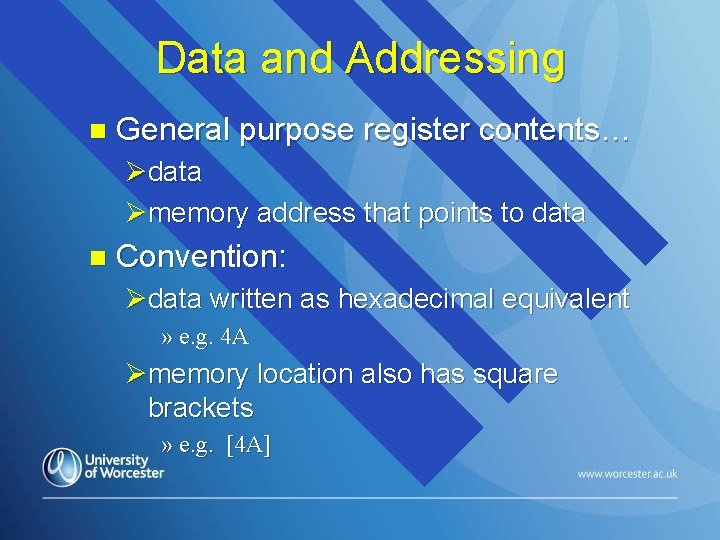

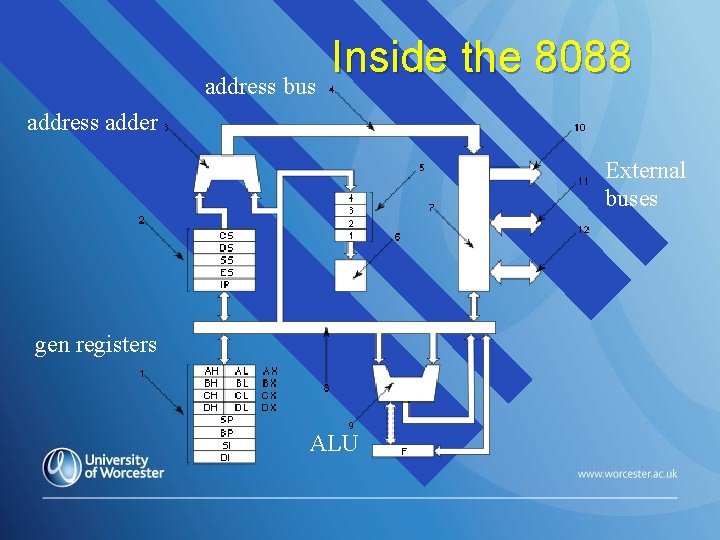

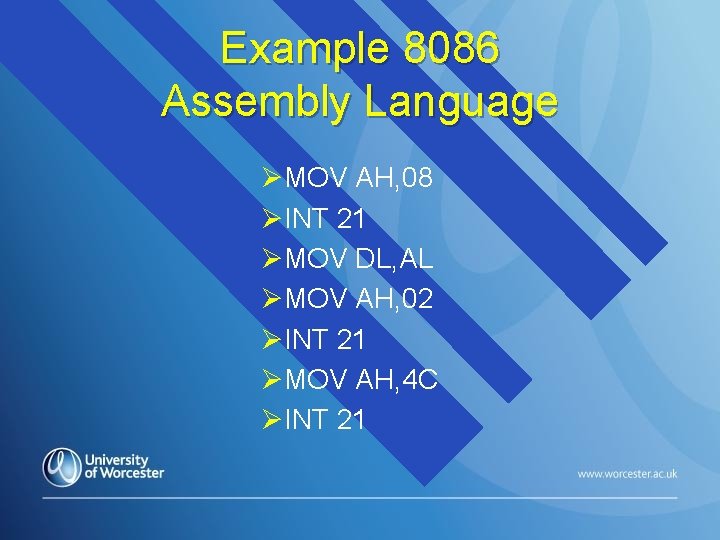

Moving data into Memory For example … mov [3] , ax mov [0] , bx Instruction Memory AX BX 8 7 mov [3] , ax mov [0], bx mar 0 7 5 1 8 2 7 3 8 6 4 1

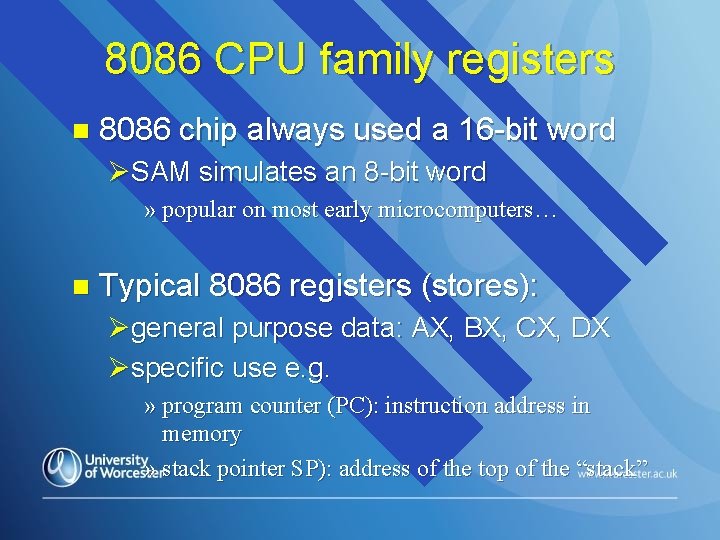

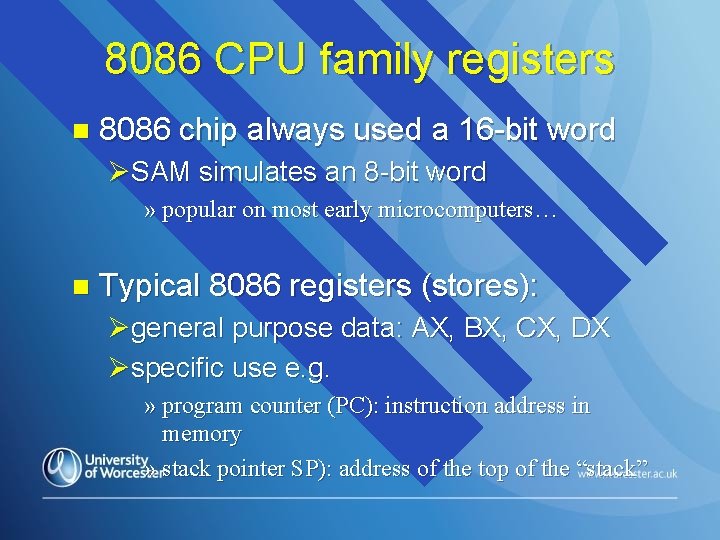

8086 CPU family registers n 8086 chip always used a 16 -bit word ØSAM simulates an 8 -bit word » popular on most early microcomputers… n Typical 8086 registers (stores): Øgeneral purpose data: AX, BX, CX, DX Øspecific use e. g. » program counter (PC): instruction address in memory » stack pointer SP): address of the top of the “stack”

Data and Addressing n General purpose register contents… Ødata Ømemory address that points to data n Convention: Ødata written as hexadecimal equivalent » e. g. 4 A Ømemory location also has square brackets » e. g. [4 A]

CPU Instructions Used to tell the CPU what to do… n MOV is for moving data around… n ØMOV AX, 4 A – move “ 4 A” into AX register ØMOV AX, [4 A] – move data contained in address 4 A into AX register n Many other instructions; range of operations… Øcollectively known as an instruction set Øeach CPU family has its own unique codes

8086 in practice n Four 16 -bit General Purpose registers Øeach gen register (e. g. AX) can be read/written to upper (AH) & lower (AL) byte upper byte lower byte AX AH AL BX BH BL CX CH CL DX DH DL

Another 8086 Instruction: ADD Takes values from two registers n Adds them together n Deposits results back in one of the registers n Which one? n Øthe register that appeared first Øe. g. “MOV, AX, BX” puts result in AX

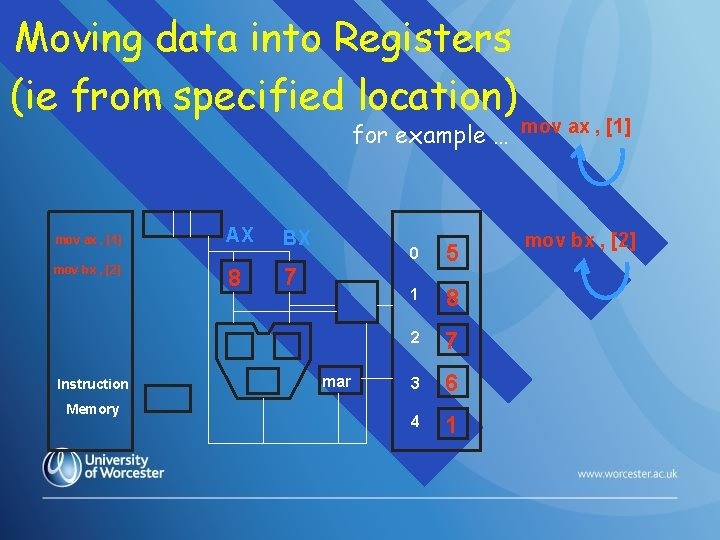

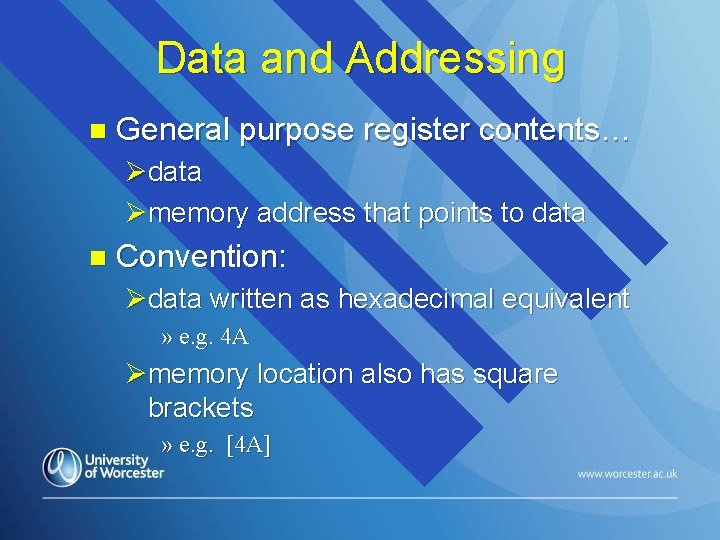

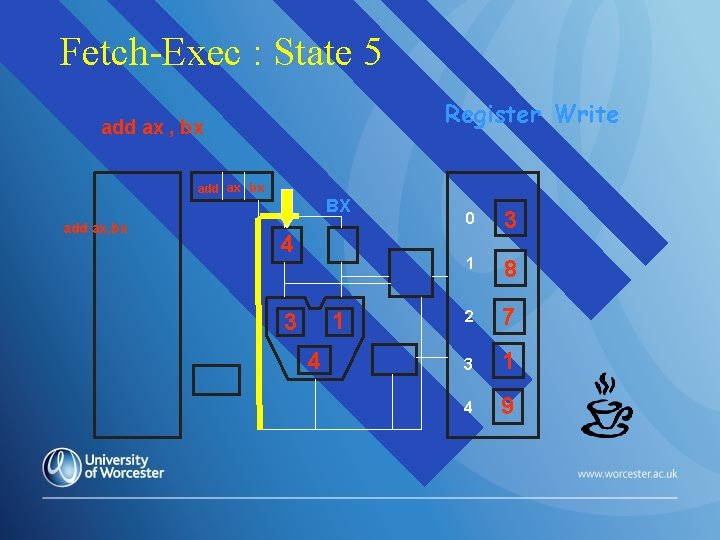

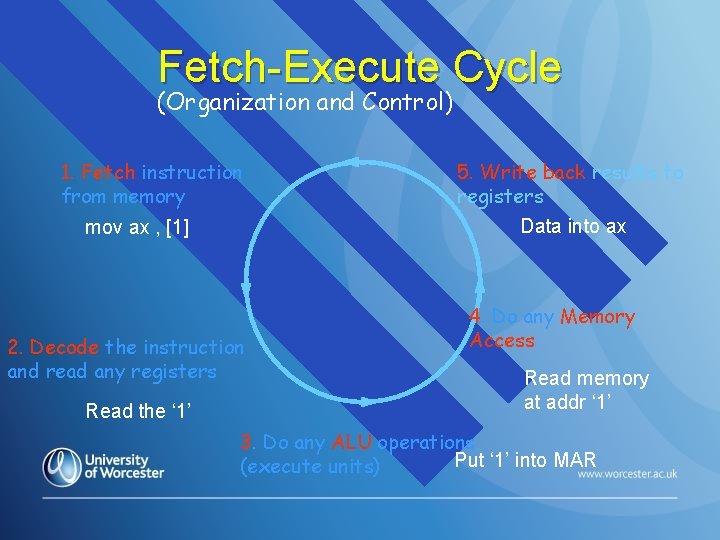

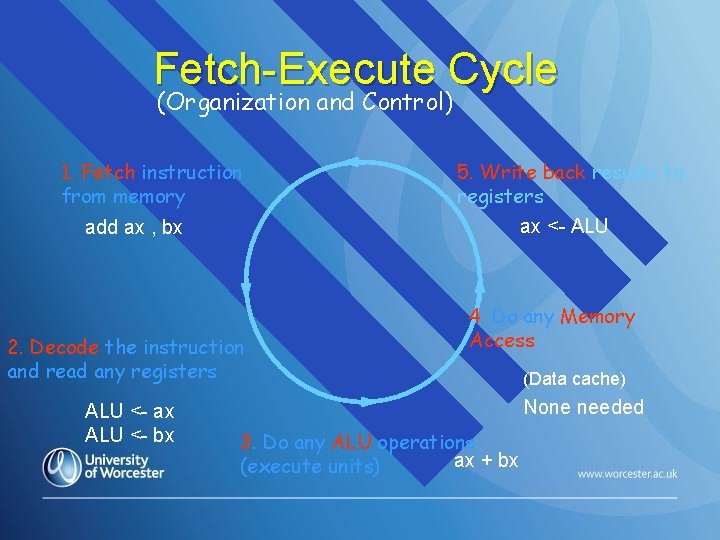

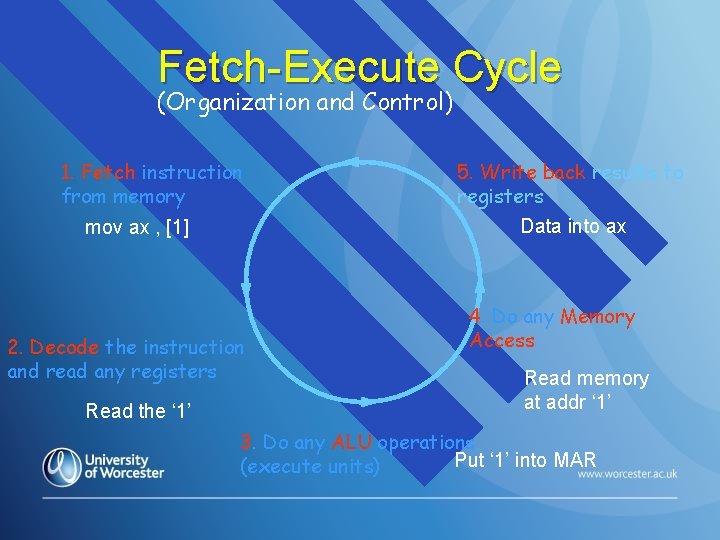

Fetch-Execute Cycle (Organization and Control) 1. Fetch instruction from memory 5. Write back results to registers ax <- ALU add ax , bx 2. Decode the instruction and read any registers ALU <- ax ALU <- bx 4. Do any Memory Access (Data cache) None needed 3. Do any ALU operations ax + bx (execute units)

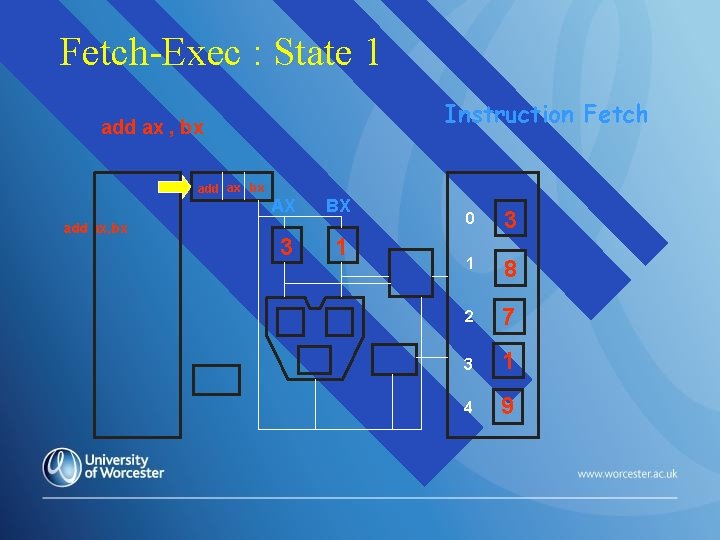

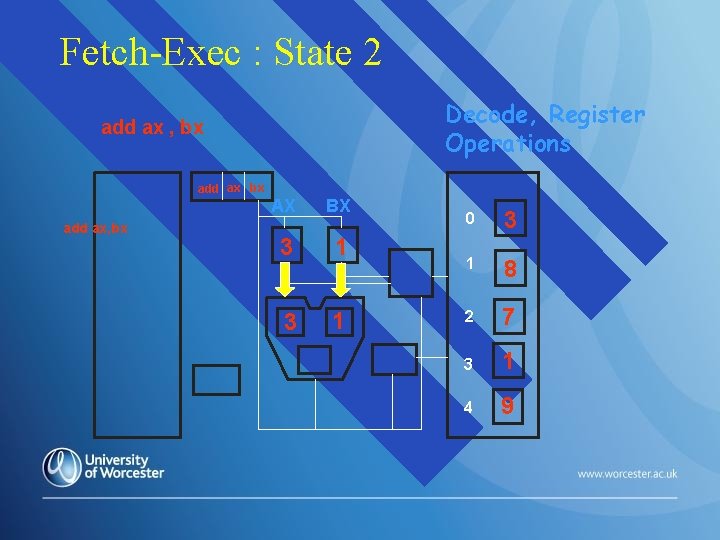

Fetch-Exec : State 1 Instruction Fetch add ax , bx add ax, bx AX BX 3 1 0 3 1 8 2 7 3 1 4 9

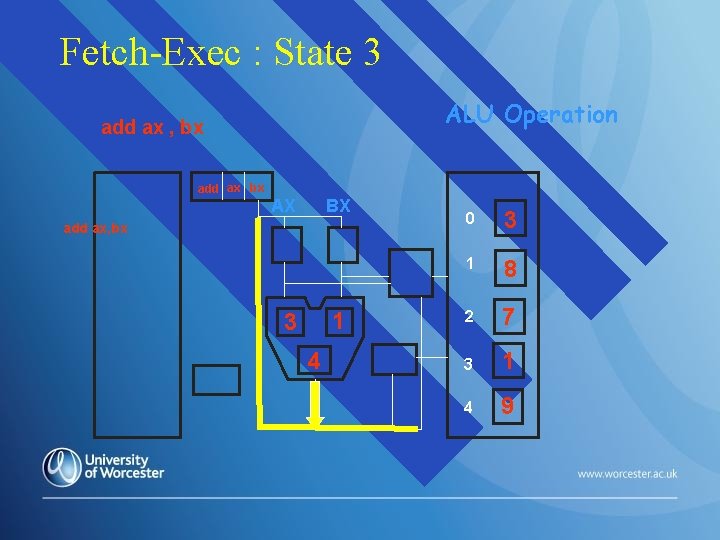

Fetch-Exec : State 2 Decode, Register Operations add ax , bx add ax, bx AX BX 3 1 0 3 1 8 2 7 3 1 4 9

Fetch-Exec : State 3 ALU Operation add ax , bx add ax bx AX BX add ax, bx 1 3 4 0 3 1 8 2 7 3 1 4 9

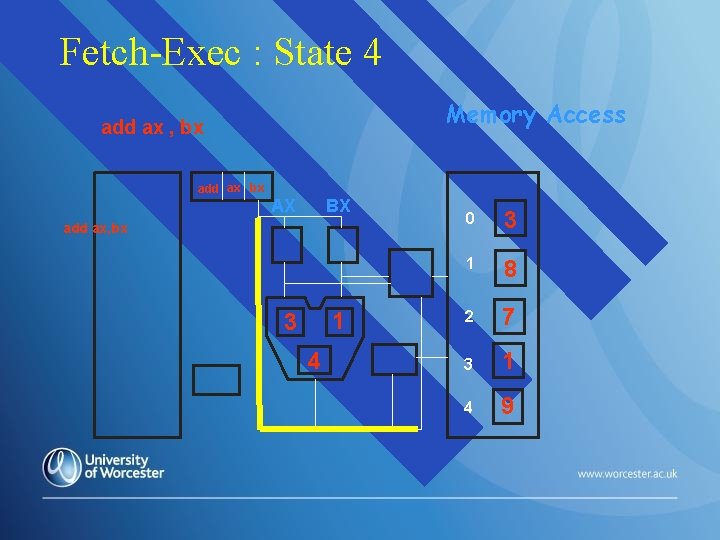

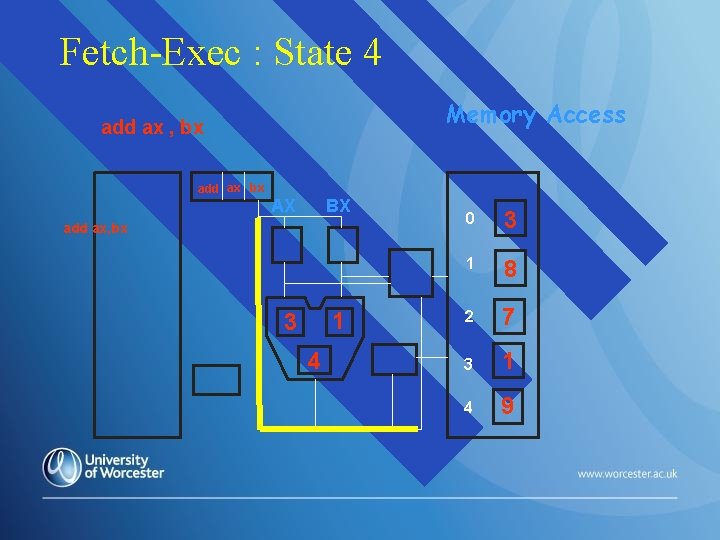

Fetch-Exec : State 4 Memory Access add ax , bx add ax bx AX BX add ax, bx 1 3 4 0 3 1 8 2 7 3 1 4 9

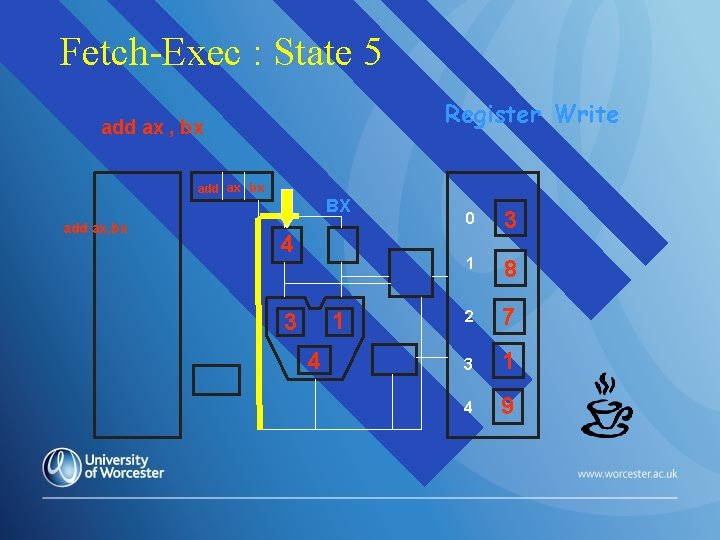

Fetch-Exec : State 5 Register Write add ax , bx add ax bx BX add ax, bx 4 1 3 4 0 3 1 8 2 7 3 1 4 9

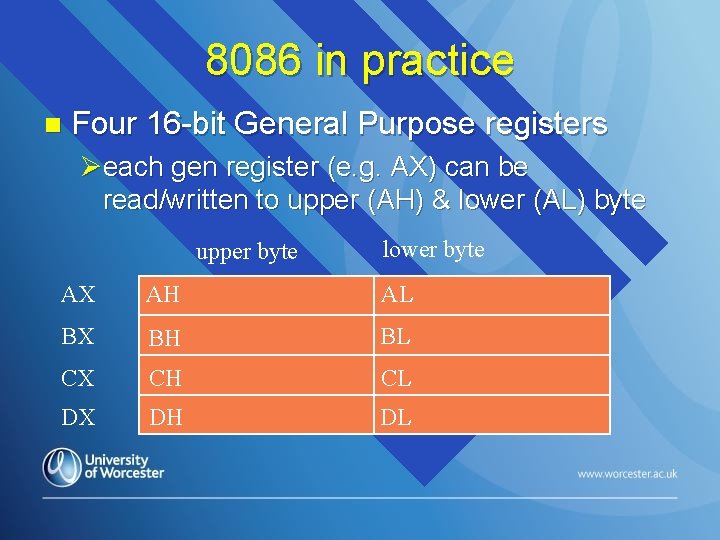

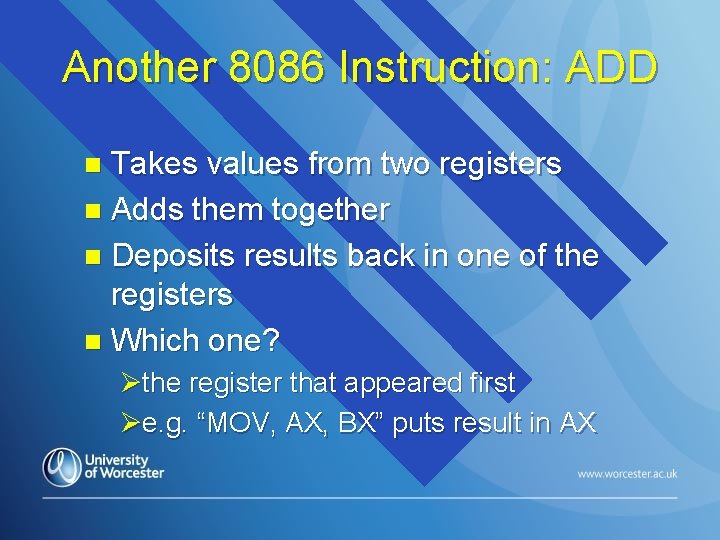

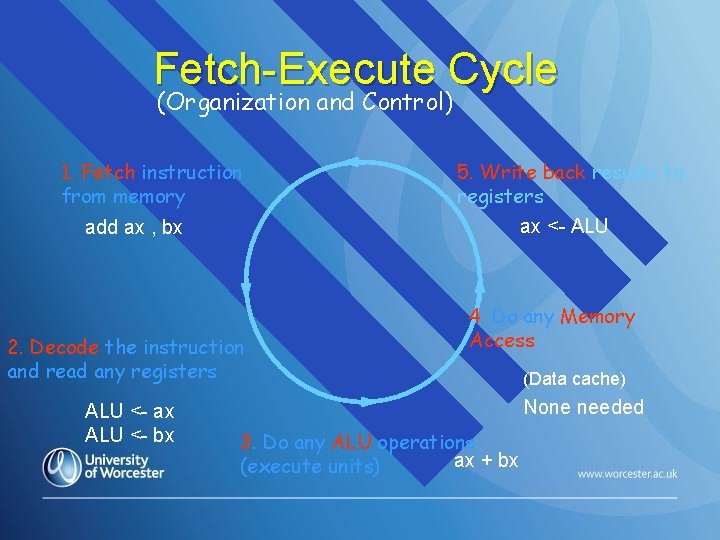

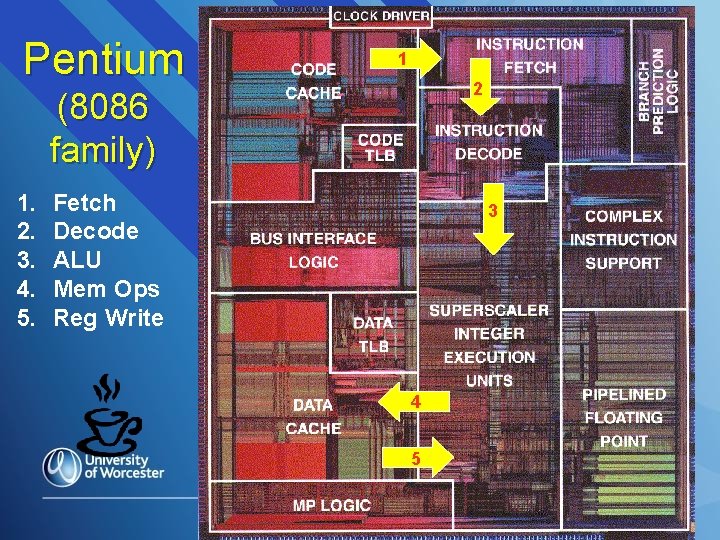

Fetch-Execute Cycle (Organization and Control) 1. Fetch instruction from memory Data into ax mov ax , [1] 2. Decode the instruction and read any registers Read the ‘ 1’ 5. Write back results to registers 4. Do any Memory Access Read memory at addr ‘ 1’ 3. Do any ALU operations Put ‘ 1’ into MAR (execute units)

![FetchExec State 1 Instruction Fetch mov ax 1 mov ax 1 0 Fetch-Exec : State 1 Instruction Fetch mov ax , [1] mov ax 1 0](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-20.jpg)

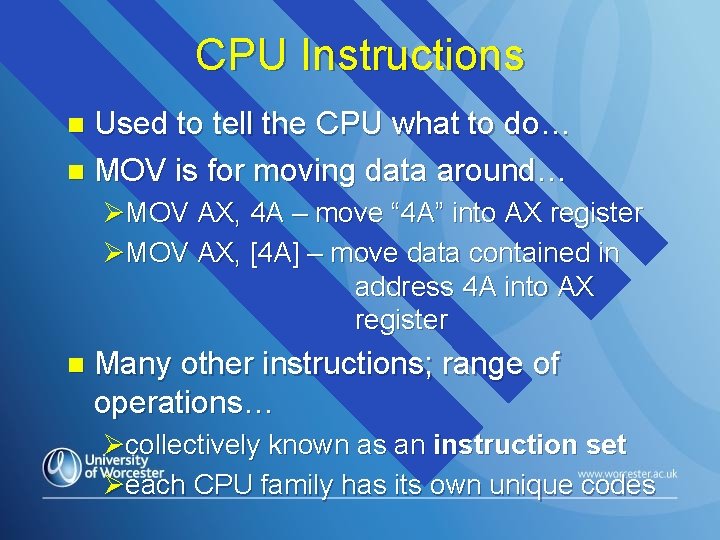

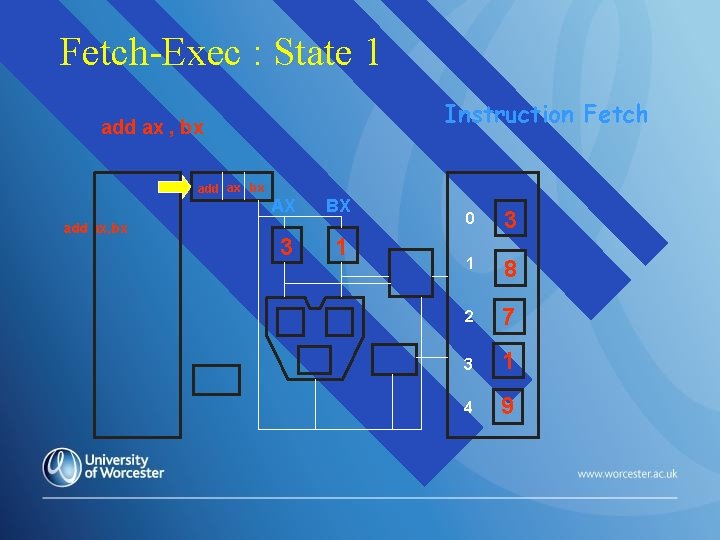

Fetch-Exec : State 1 Instruction Fetch mov ax , [1] mov ax 1 0 3 1 8 2 7 3 1 4 9

![FetchExec State 2 Decode Register Operations mov ax 1 mov ax 1 Fetch-Exec : State 2 Decode, Register Operations mov ax , [1] mov ax 1](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-21.jpg)

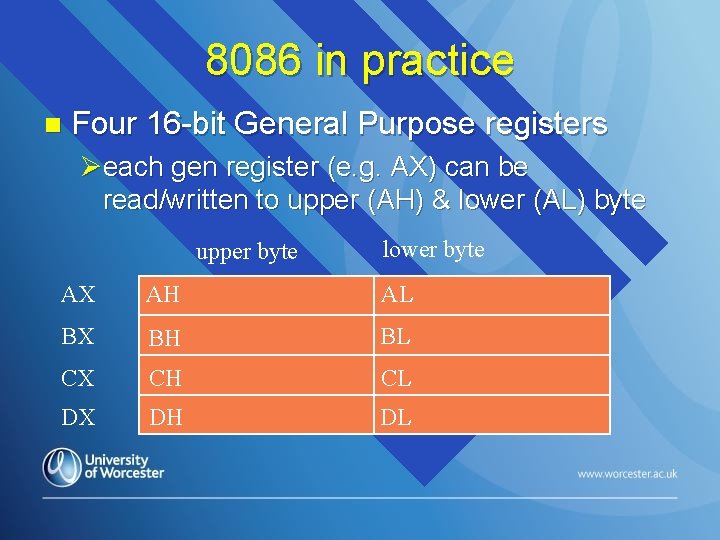

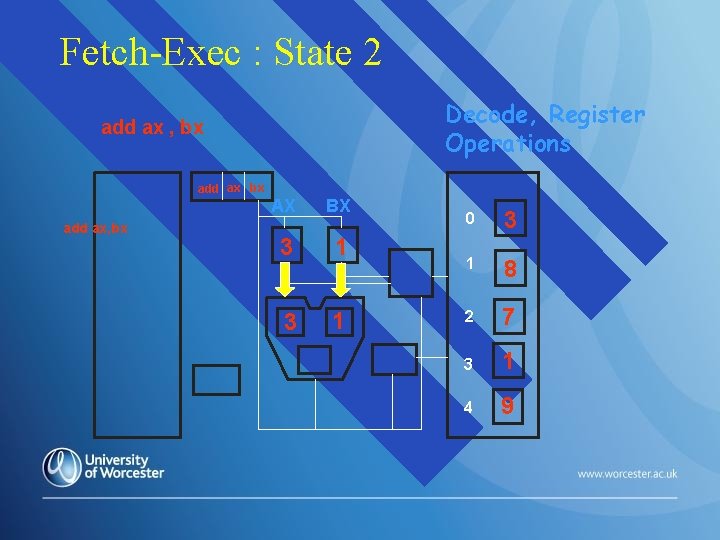

Fetch-Exec : State 2 Decode, Register Operations mov ax , [1] mov ax 1 0 3 1 8 2 7 3 1 4 9

![FetchExec State 3 ALU Operation mov ax 1 mov ax 1 1 Fetch-Exec : State 3 ALU Operation mov ax , [1] mov ax 1 1](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-22.jpg)

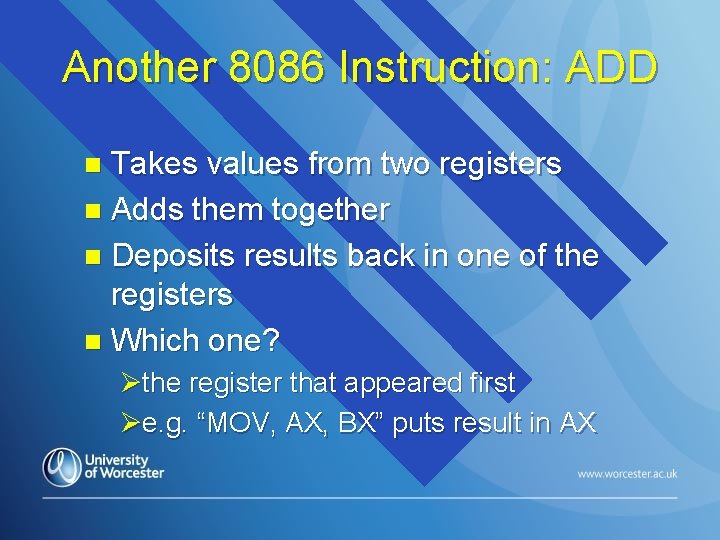

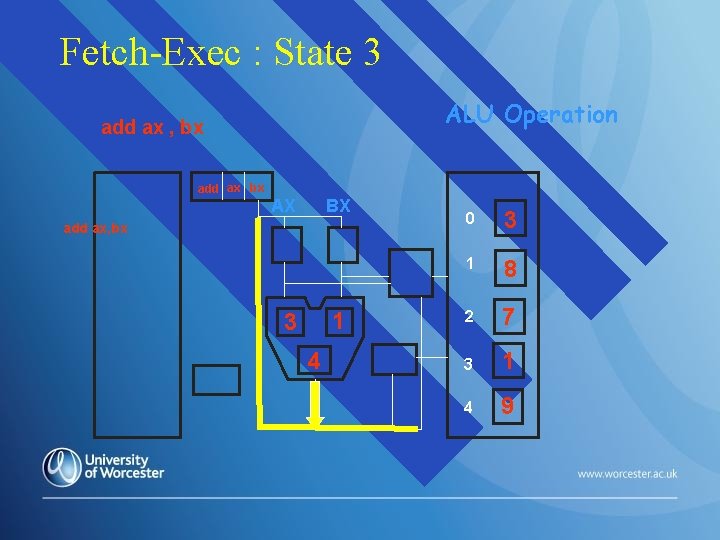

Fetch-Exec : State 3 ALU Operation mov ax , [1] mov ax 1 1 0 3 1 8 2 7 3 1 4 9

![FetchExec State 4 Memory Access mov ax 1 mov ax 1 8 Fetch-Exec : State 4 Memory Access mov ax , [1] mov ax 1 8](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-23.jpg)

Fetch-Exec : State 4 Memory Access mov ax , [1] mov ax 1 8 1 0 3 1 8 2 7 3 1 4 9

![FetchExec State 5 Register Write mov ax 1 mov ax 1 8 Fetch-Exec : State 5 Register Write mov ax , [1] mov ax 1 8](https://slidetodoc.com/presentation_image_h2/75a5bb7e8783514fc4d14420586ecfef/image-24.jpg)

Fetch-Exec : State 5 Register Write mov ax , [1] mov ax 1 8 8 1 0 3 1 8 2 7 3 1 4 9

8088: Brains of the IBM PC

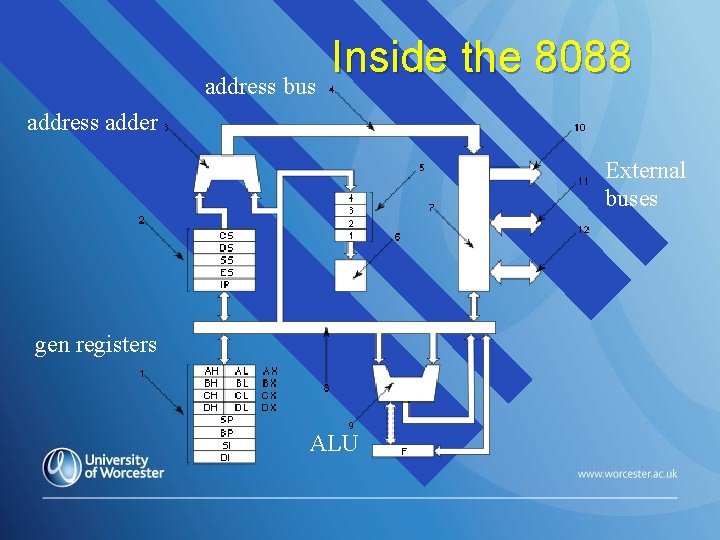

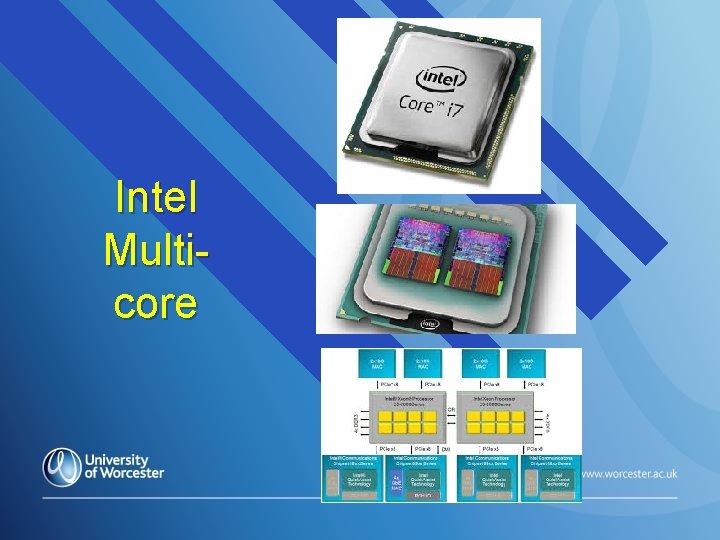

address bus Inside the 8088 address adder External buses gen registers ALU

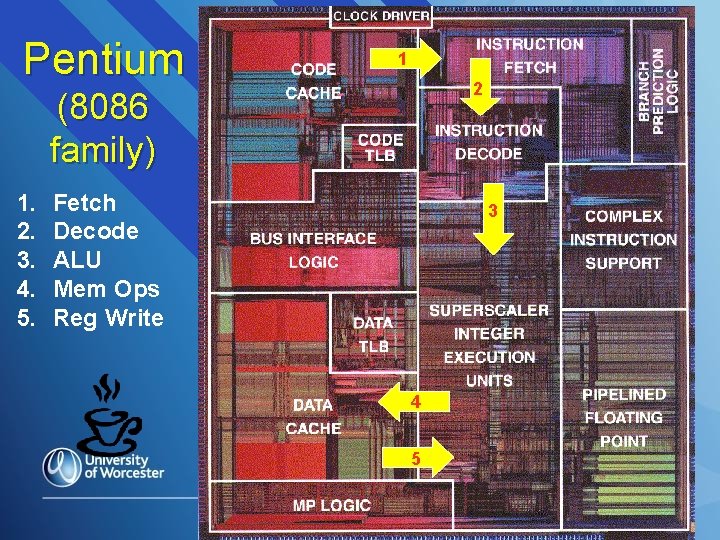

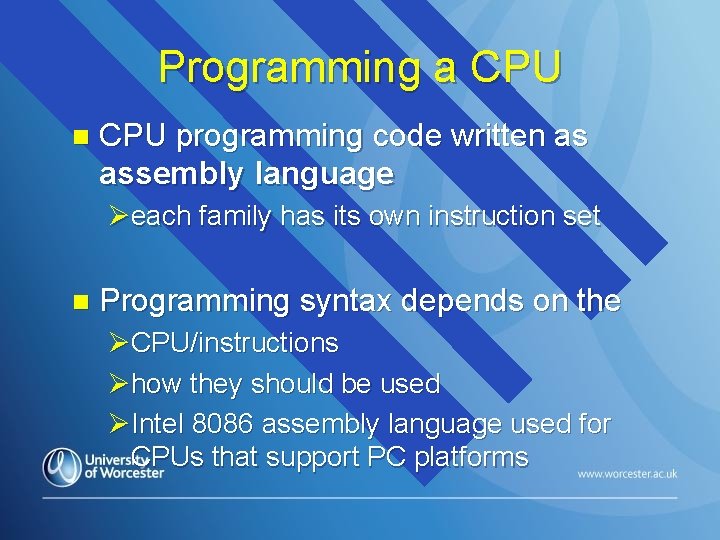

Pentium 1 2 (8086 family) 1. 2. 3. 4. 5. Fetch Decode ALU Mem Ops Reg Write 3 4 5

Intel Multicore

Programming a CPU n CPU programming code written as assembly language Øeach family has its own instruction set n Programming syntax depends on the ØCPU/instructions Øhow they should be used ØIntel 8086 assembly language used for CPUs that support PC platforms

Example 8086 Assembly Language ØMOV AH, 08 ØINT 21 ØMOV DL, AL ØMOV AH, 02 ØINT 21 ØMOV AH, 4 C ØINT 21

So THAT’S how it all works! now you try it on SAM… Next week: a focus on writing programs and i/o