Chapter 4 Pipelined Datapath and Control MIPS Pipeline

- Slides: 35

Chapter 4 Pipelined Datapath and Control

MIPS Pipeline n Five stages, one step per stage 1. IF (Fetch): Instruction fetch from memory 2. ID (Decode): Instruction decode & register read 3. EX (Execute): Execute operation or calculate address 4. MEM (Memory): Access data memory 5. WB (Writeback): Write result back to register Chapter 4 — The Processor — 2

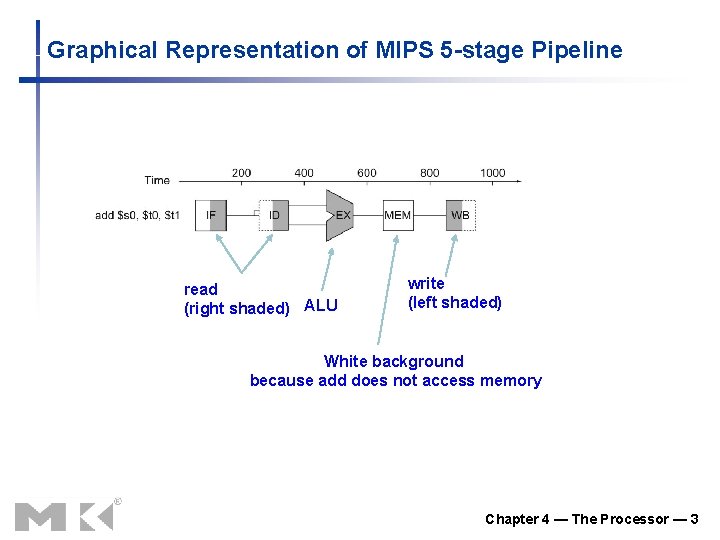

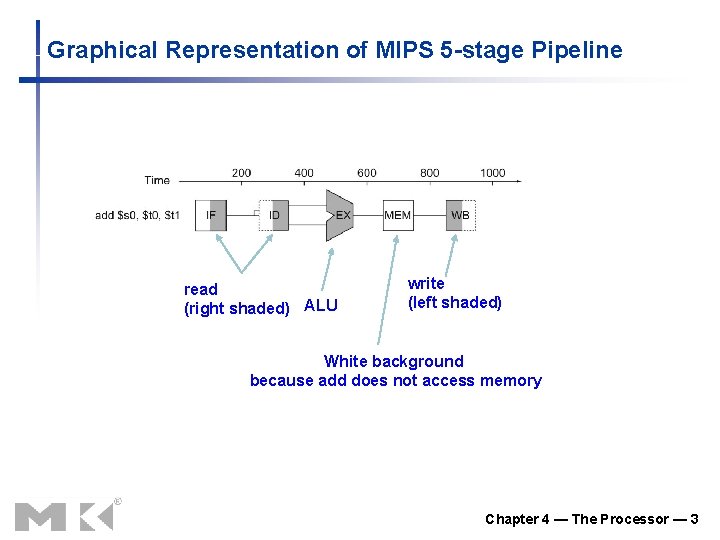

Graphical Representation of MIPS 5 -stage Pipeline read (right shaded) ALU write (left shaded) White background because add does not access memory Chapter 4 — The Processor — 3

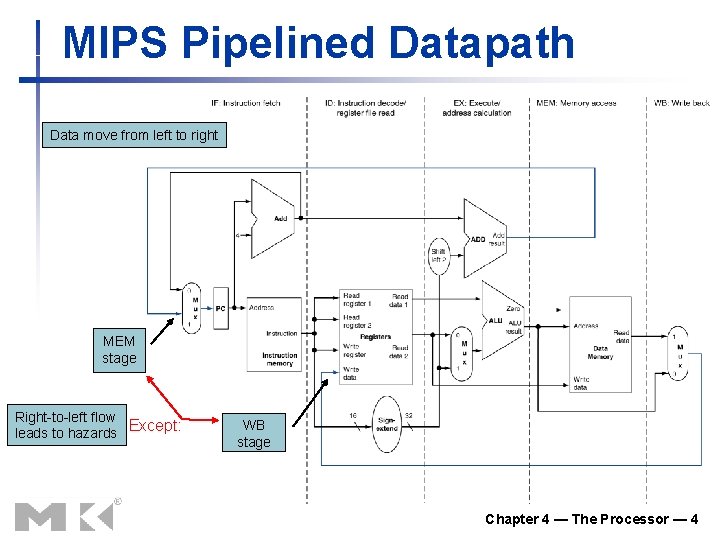

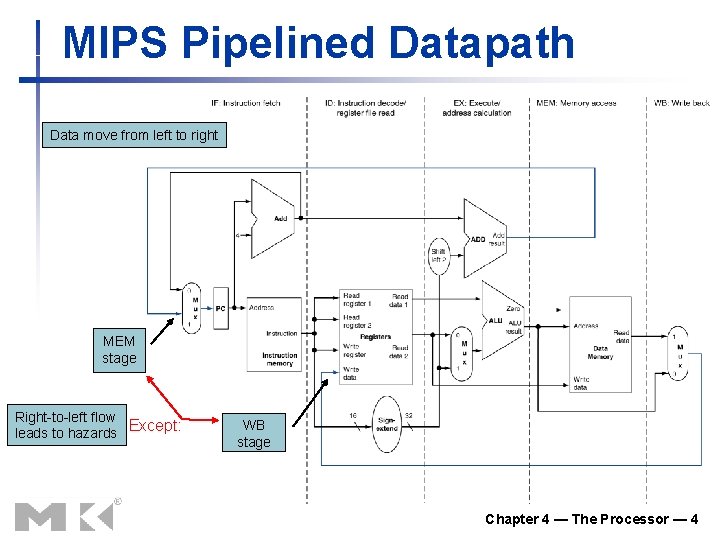

MIPS Pipelined Datapath Data move from left to right MEM stage Right-to-left flow Except: leads to hazards WB stage Chapter 4 — The Processor — 4

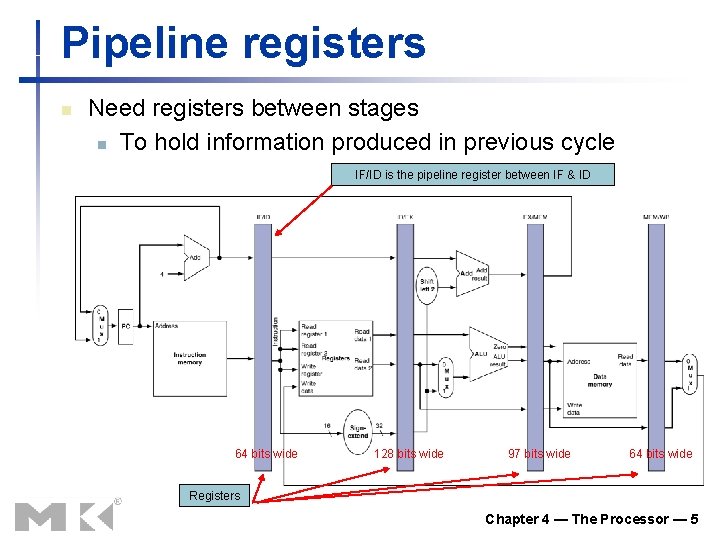

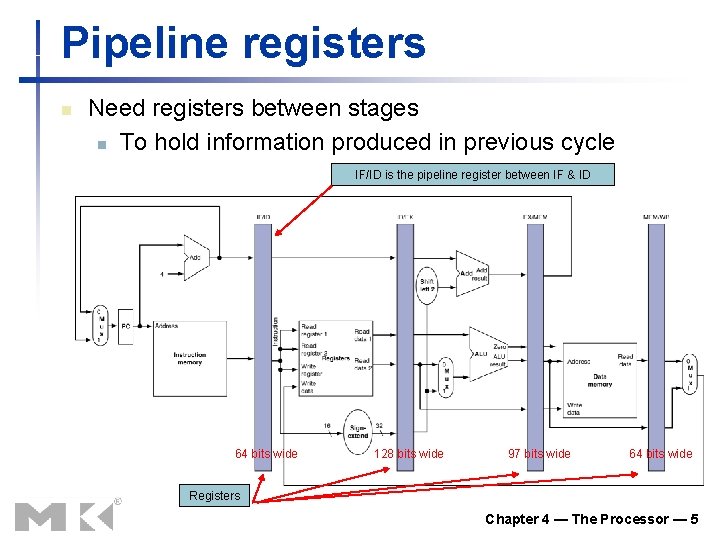

Pipeline registers n Need registers between stages n To hold information produced in previous cycle IF/ID is the pipeline register between IF & ID 64 bits wide 128 bits wide 97 bits wide 64 bits wide Registers Chapter 4 — The Processor — 5

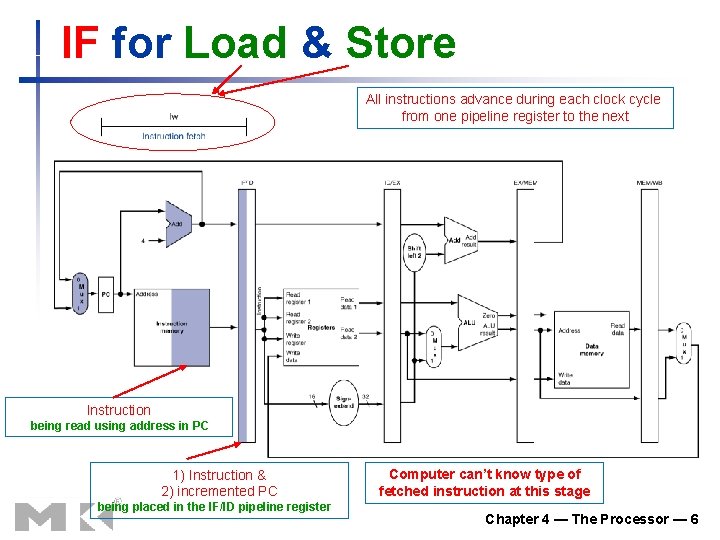

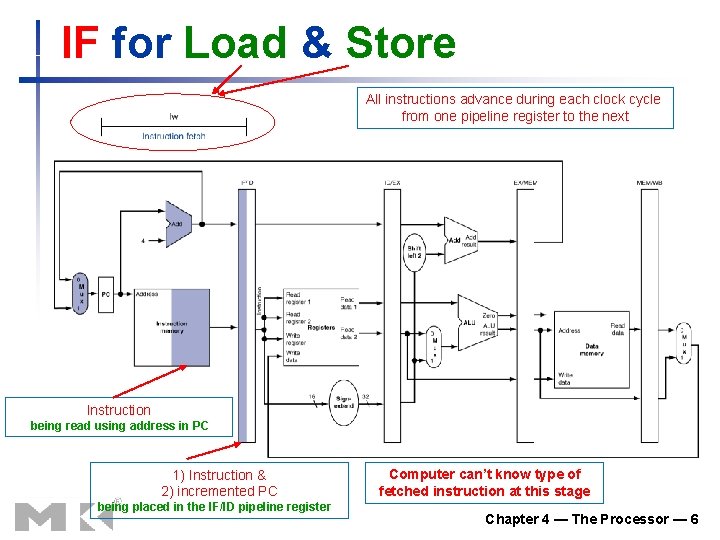

IF for Load & Store All instructions advance during each clock cycle from one pipeline register to the next Instruction being read using address in PC 1) Instruction & 2) incremented PC being placed in the IF/ID pipeline register Computer can’t know type of fetched instruction at this stage Chapter 4 — The Processor — 6

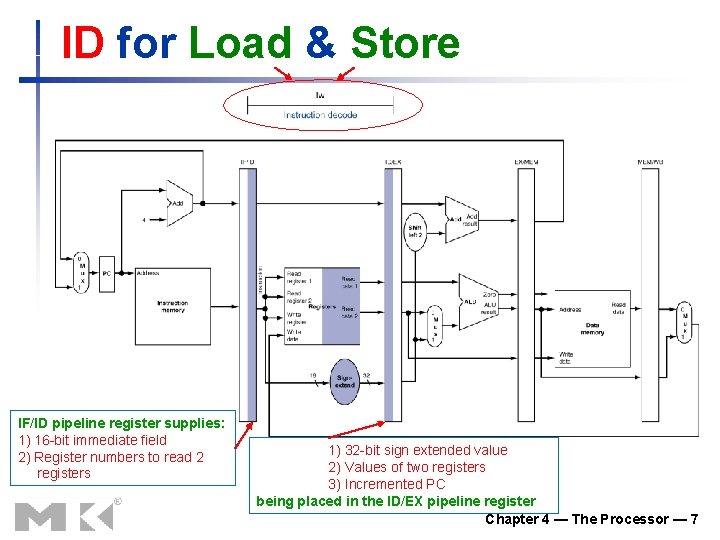

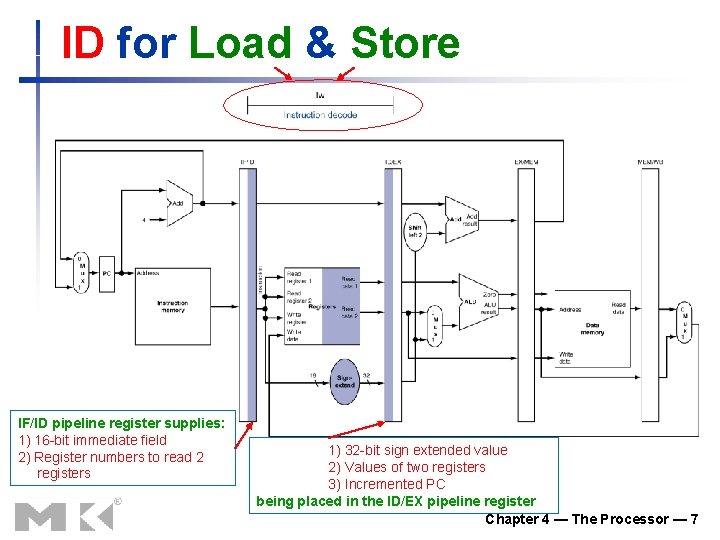

ID for Load & Store IF/ID pipeline register supplies: 1) 16 -bit immediate field 2) Register numbers to read 2 registers 1) 32 -bit sign extended value 2) Values of two registers 3) Incremented PC being placed in the ID/EX pipeline register Chapter 4 — The Processor — 7

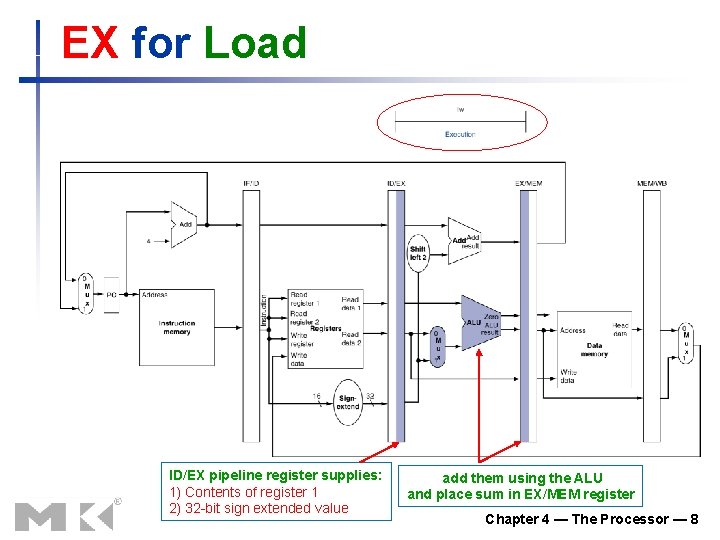

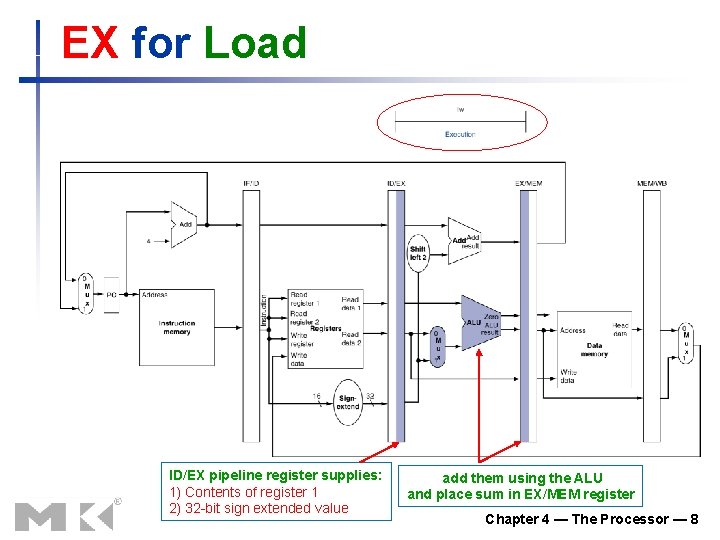

EX for Load ID/EX pipeline register supplies: 1) Contents of register 1 2) 32 -bit sign extended value add them using the ALU and place sum in EX/MEM register Chapter 4 — The Processor — 8

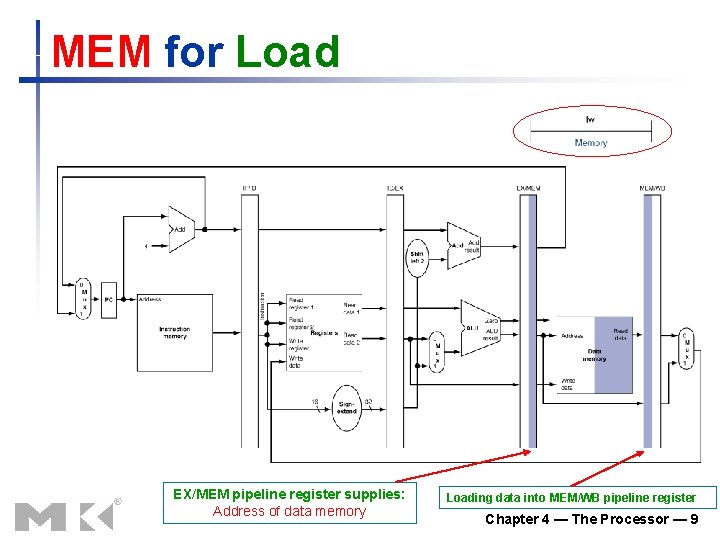

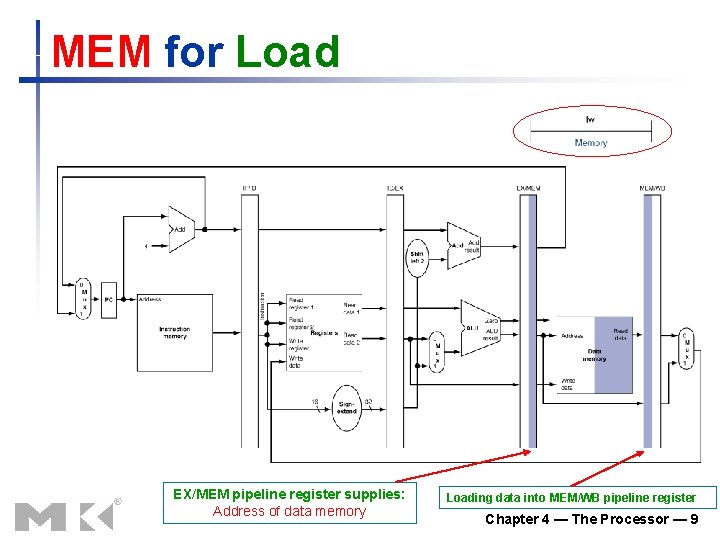

MEM for Load EX/MEM pipeline register supplies: Address of data memory Loading data into MEM/WB pipeline register Chapter 4 — The Processor — 9

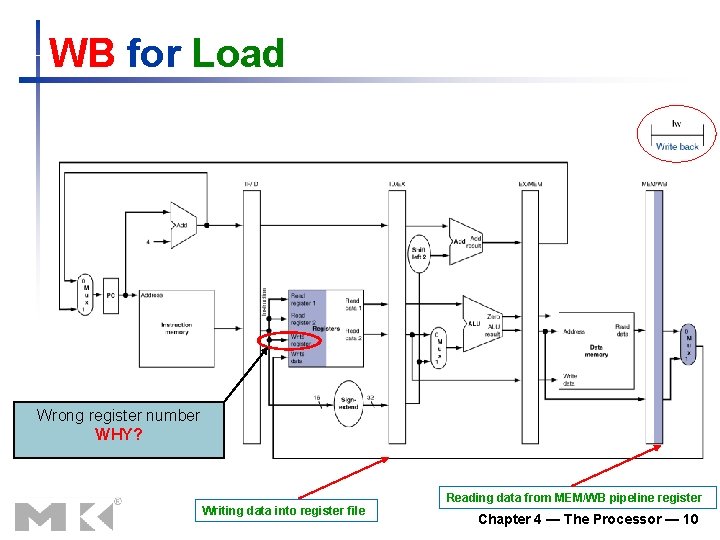

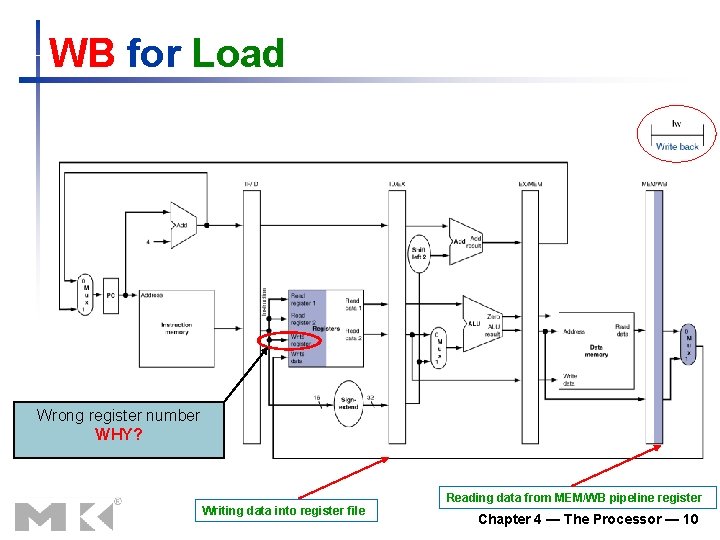

WB for Load Wrong register number WHY? Reading data from MEM/WB pipeline register Writing data into register file Chapter 4 — The Processor — 10

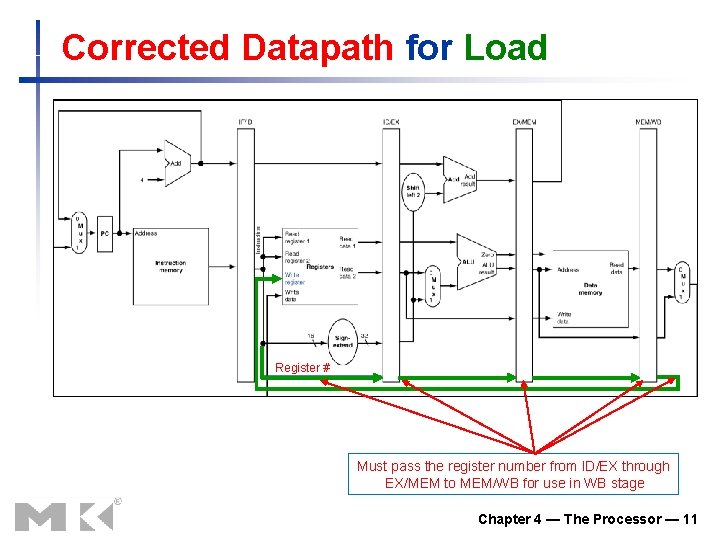

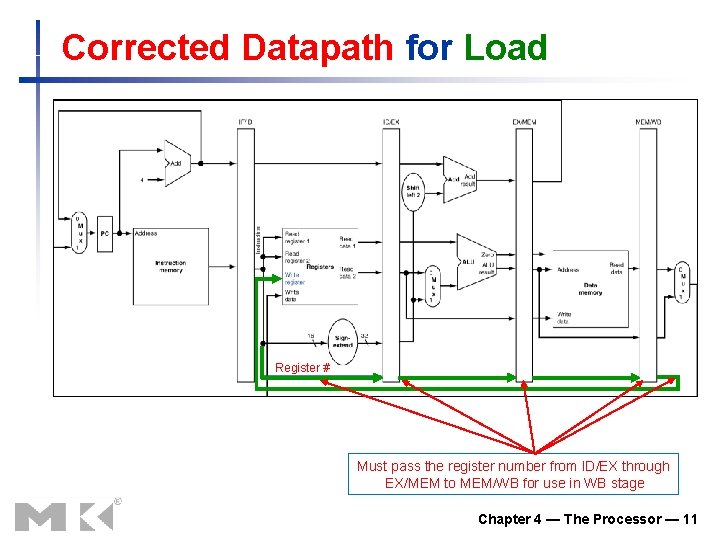

Corrected Datapath for Load Register # Must pass the register number from ID/EX through EX/MEM to MEM/WB for use in WB stage Chapter 4 — The Processor — 11

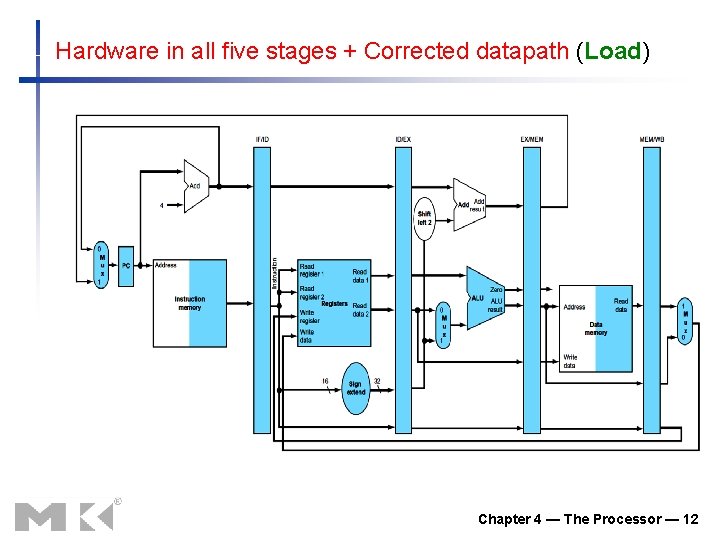

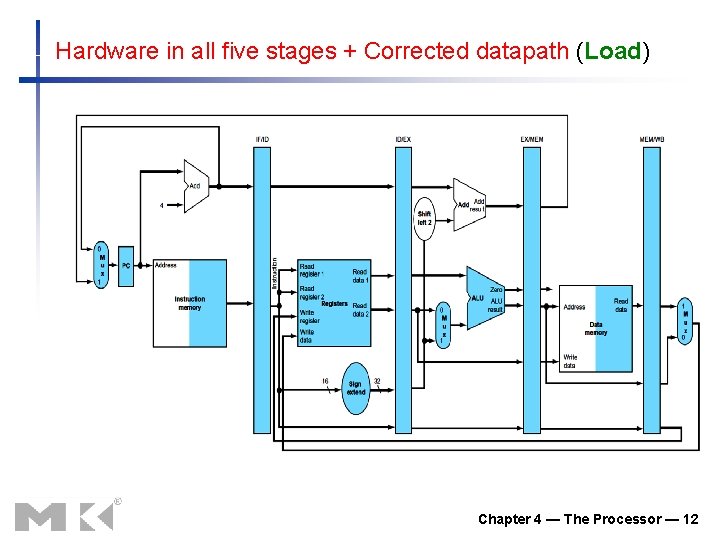

Hardware in all five stages + Corrected datapath (Load) Chapter 4 — The Processor — 12

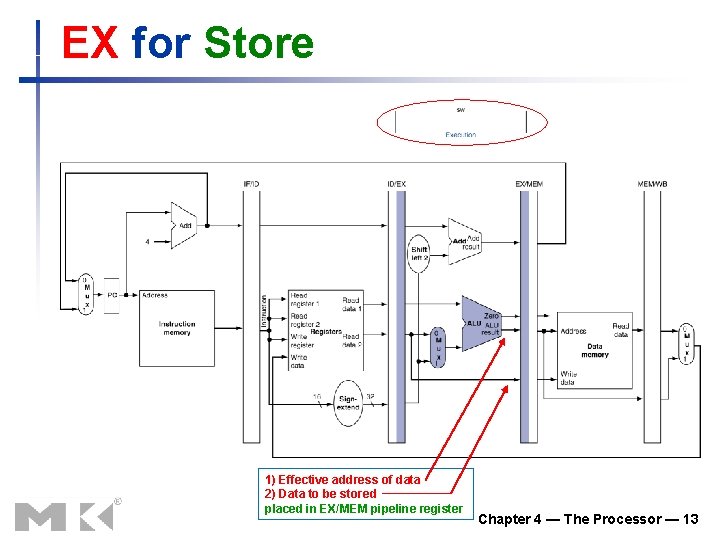

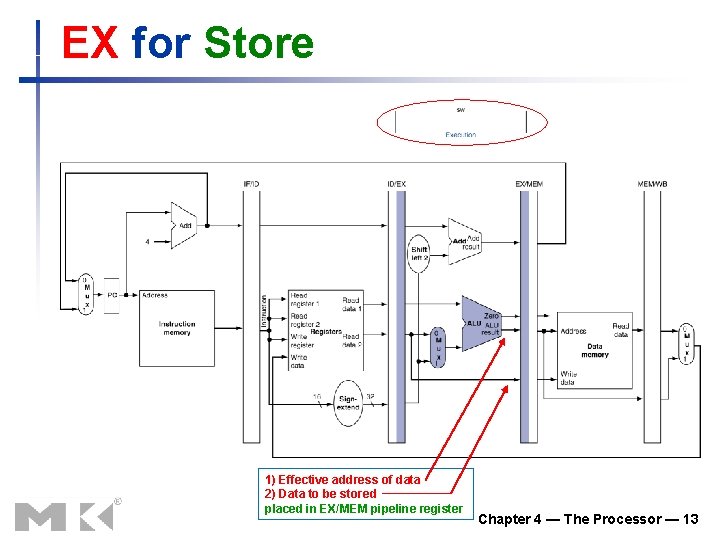

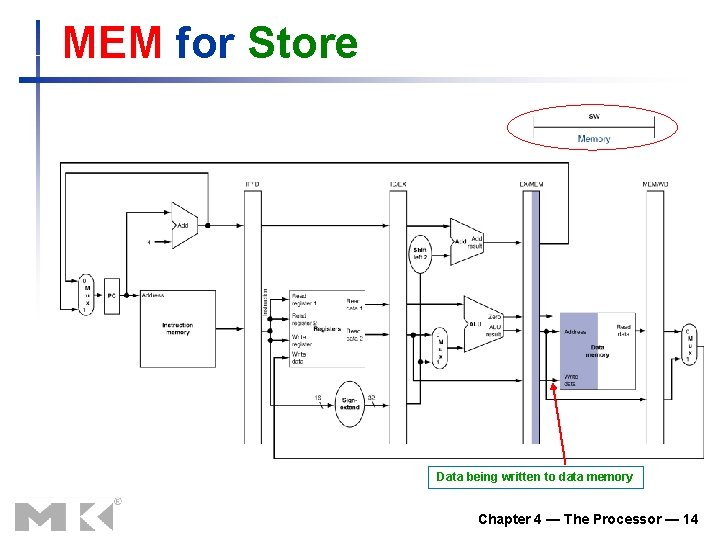

EX for Store 1) Effective address of data 2) Data to be stored placed in EX/MEM pipeline register Chapter 4 — The Processor — 13

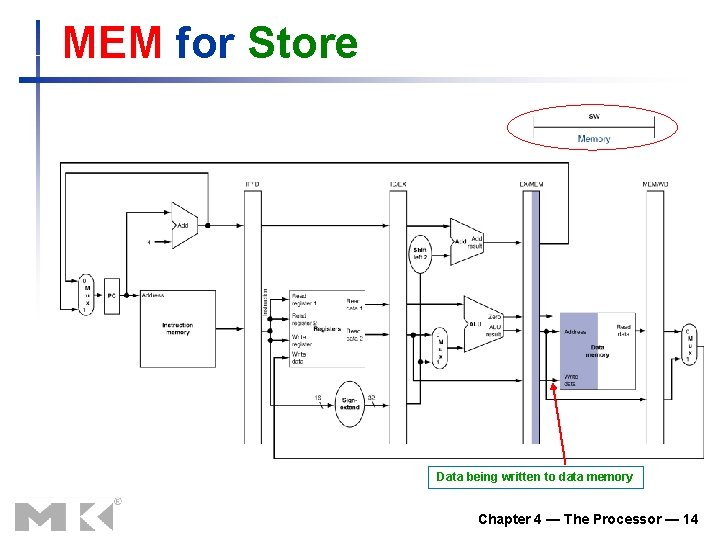

MEM for Store Data being written to data memory Chapter 4 — The Processor — 14

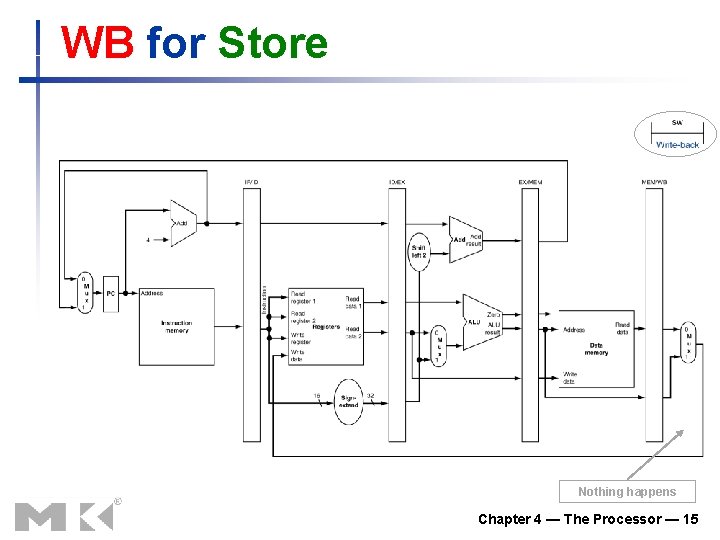

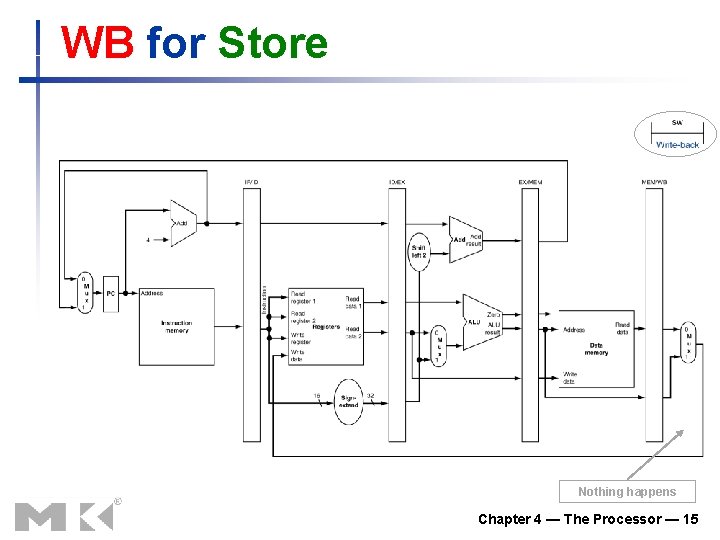

WB for Store Nothing happens Chapter 4 — The Processor — 15

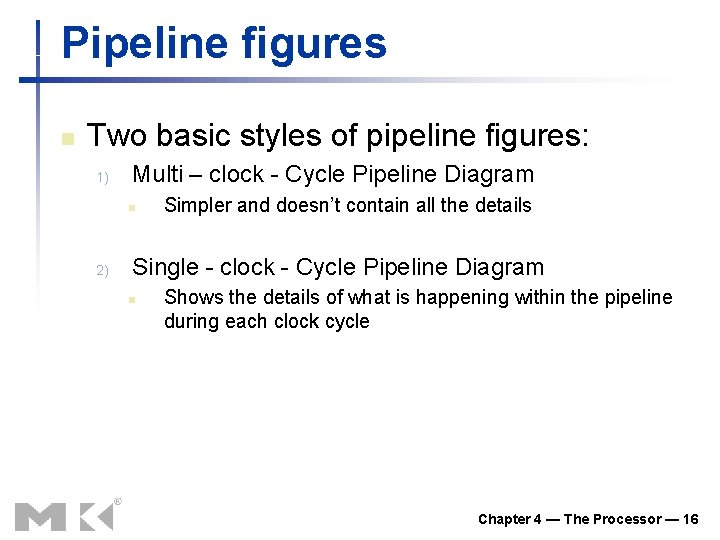

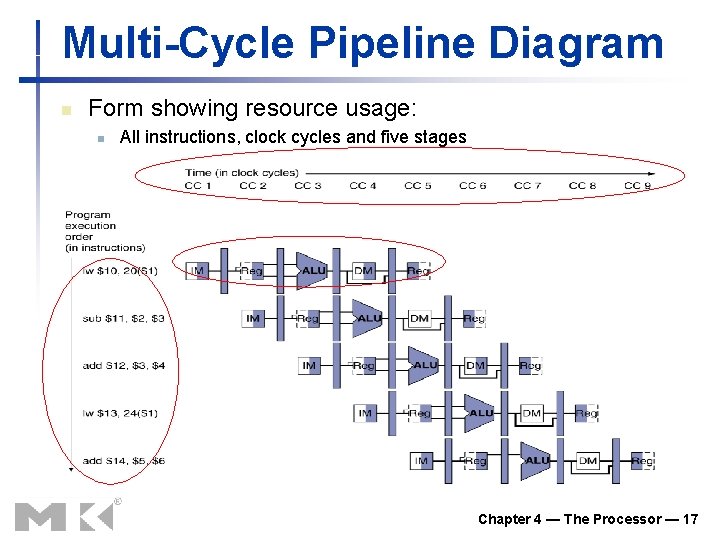

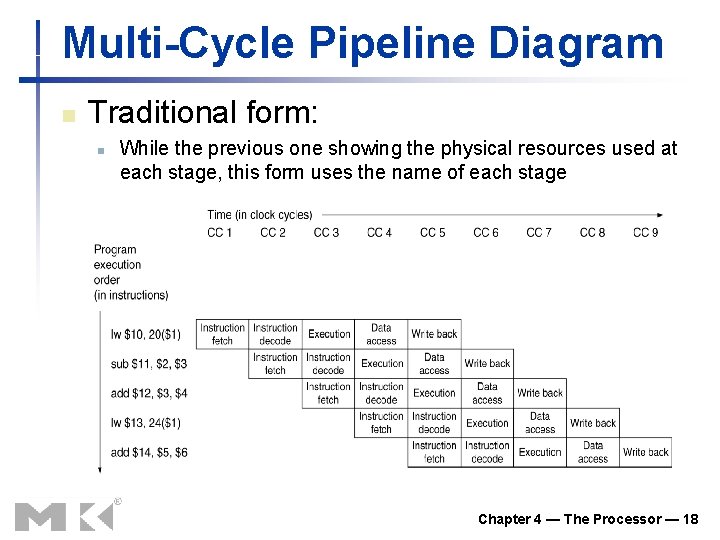

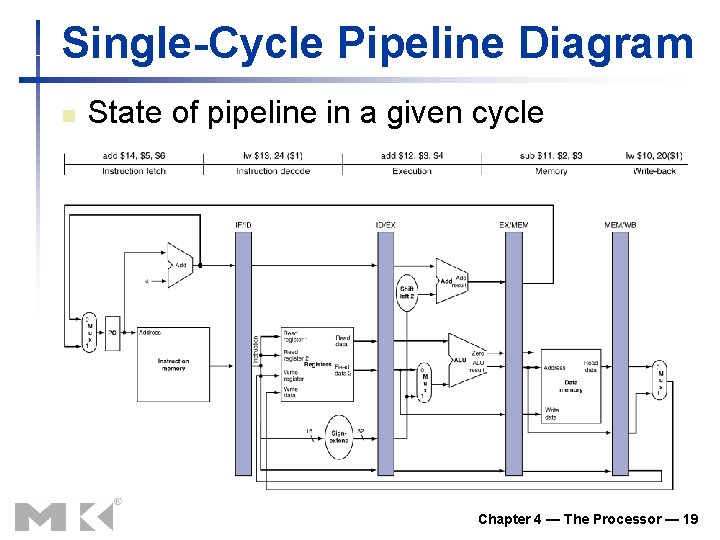

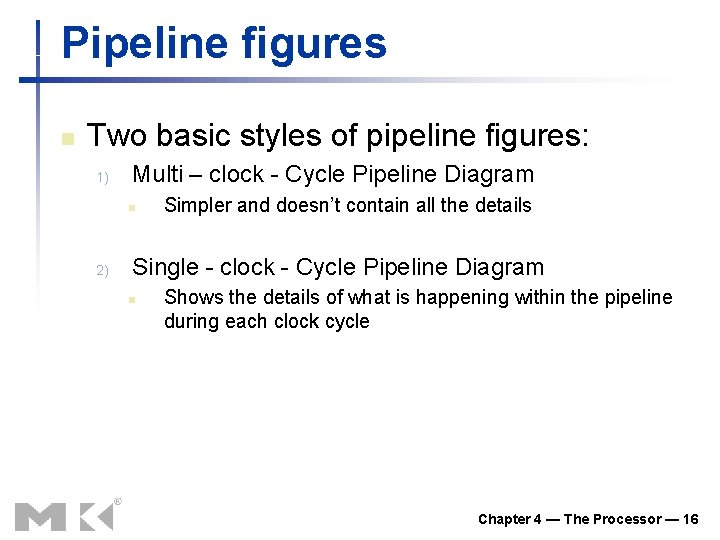

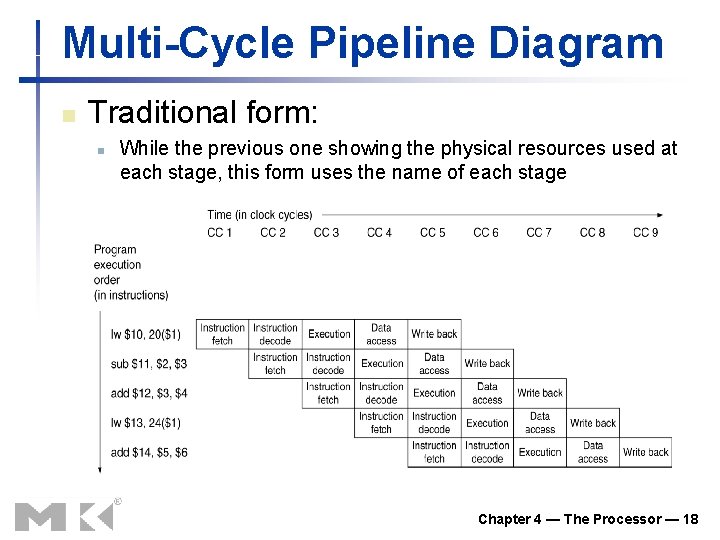

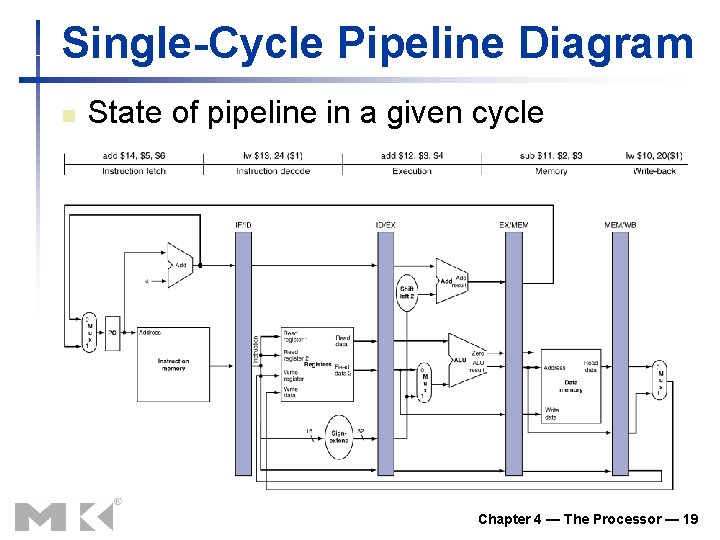

Pipeline figures n Two basic styles of pipeline figures: 1) Multi – clock - Cycle Pipeline Diagram n 2) Simpler and doesn’t contain all the details Single - clock - Cycle Pipeline Diagram n Shows the details of what is happening within the pipeline during each clock cycle Chapter 4 — The Processor — 16

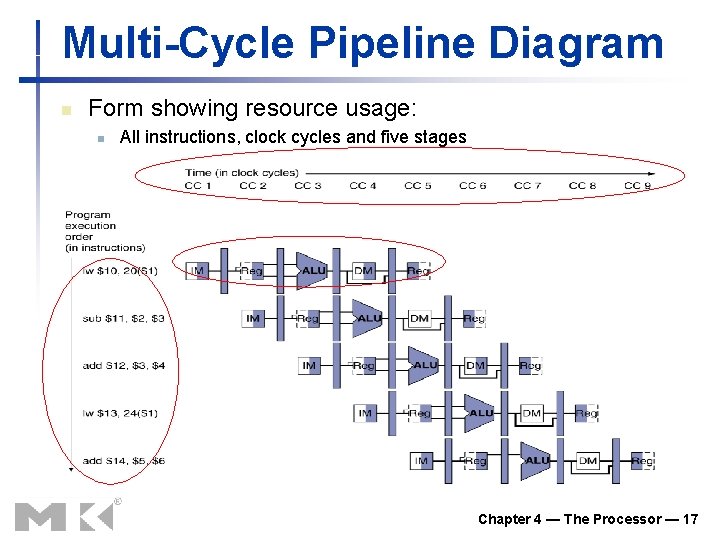

Multi-Cycle Pipeline Diagram n Form showing resource usage: n All instructions, clock cycles and five stages Chapter 4 — The Processor — 17

Multi-Cycle Pipeline Diagram n Traditional form: n While the previous one showing the physical resources used at each stage, this form uses the name of each stage Chapter 4 — The Processor — 18

Single-Cycle Pipeline Diagram n State of pipeline in a given cycle Chapter 4 — The Processor — 19

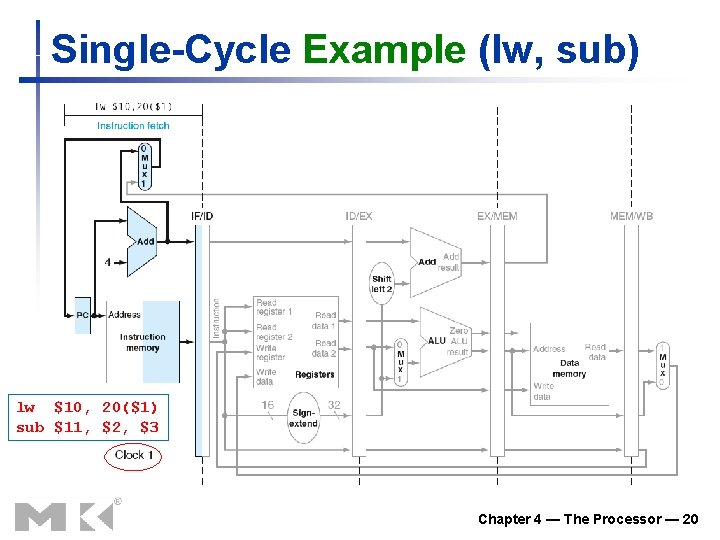

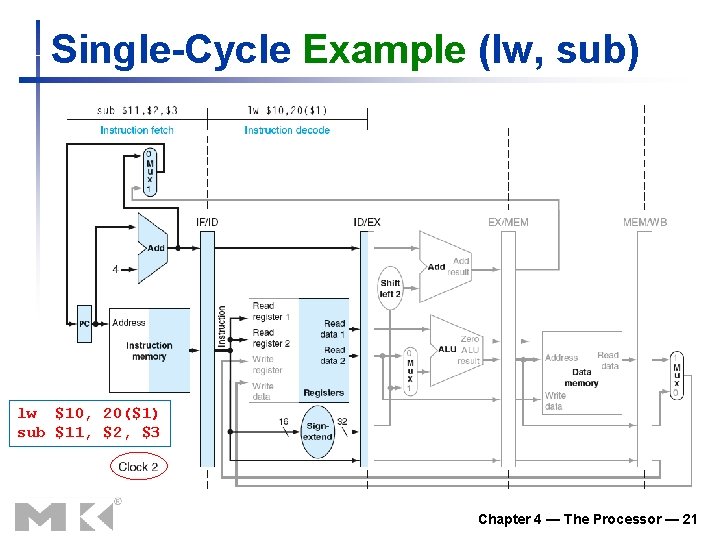

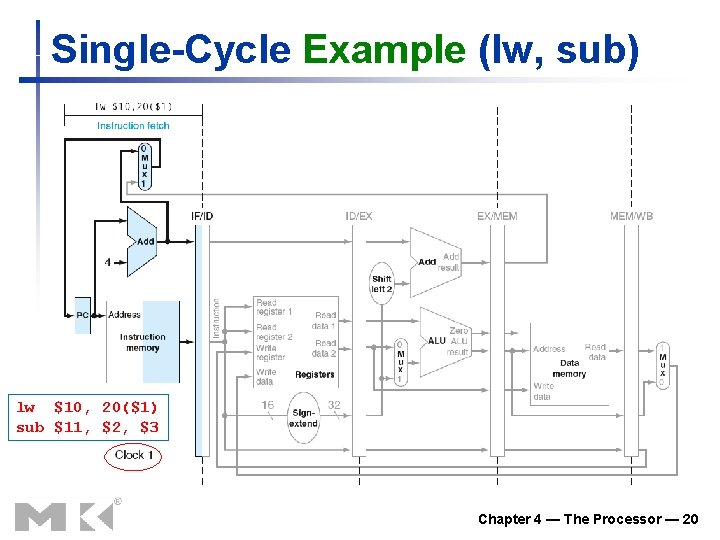

Single-Cycle Example (lw, sub) lw $10, 20($1) sub $11, $2, $3 Chapter 4 — The Processor — 20

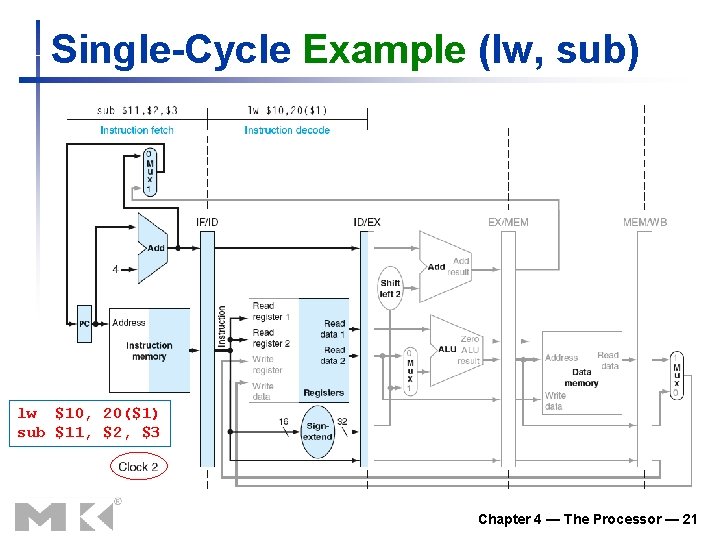

Single-Cycle Example (lw, sub) lw $10, 20($1) sub $11, $2, $3 Chapter 4 — The Processor — 21

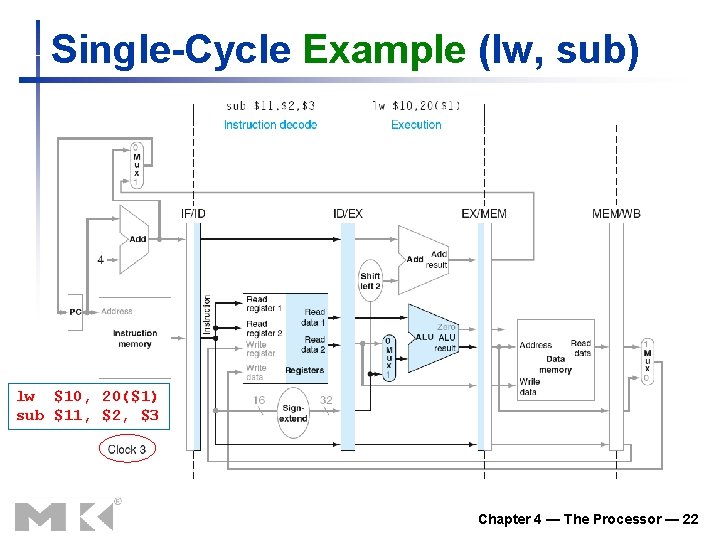

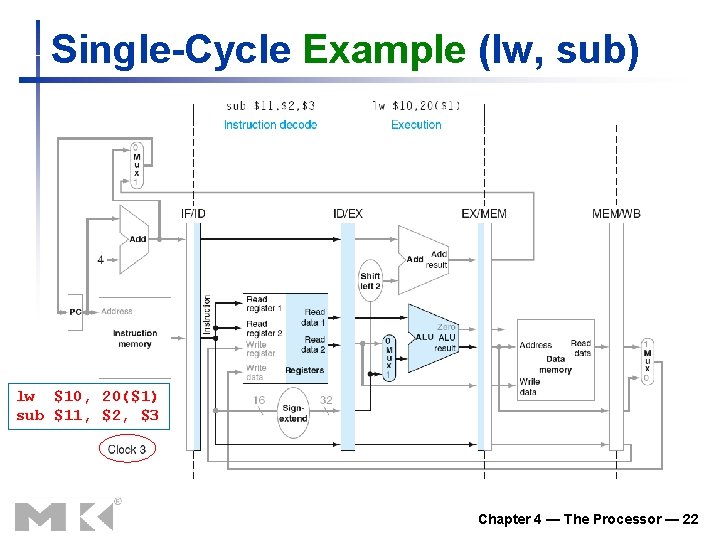

Single-Cycle Example (lw, sub) lw $10, 20($1) sub $11, $2, $3 Chapter 4 — The Processor — 22

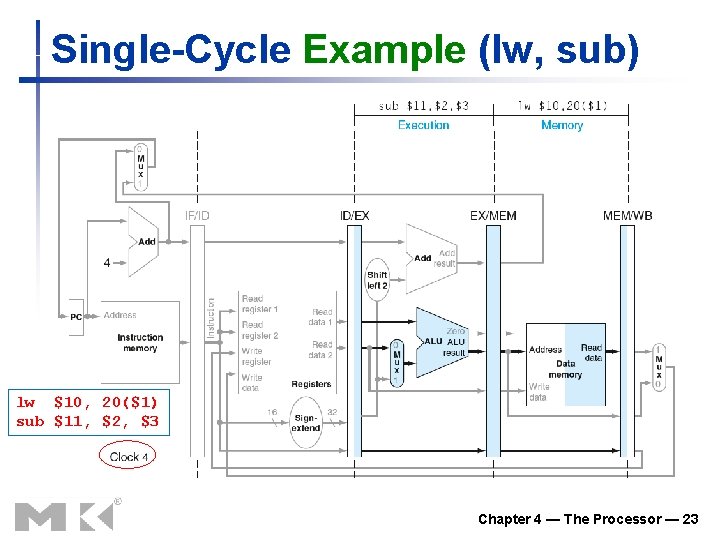

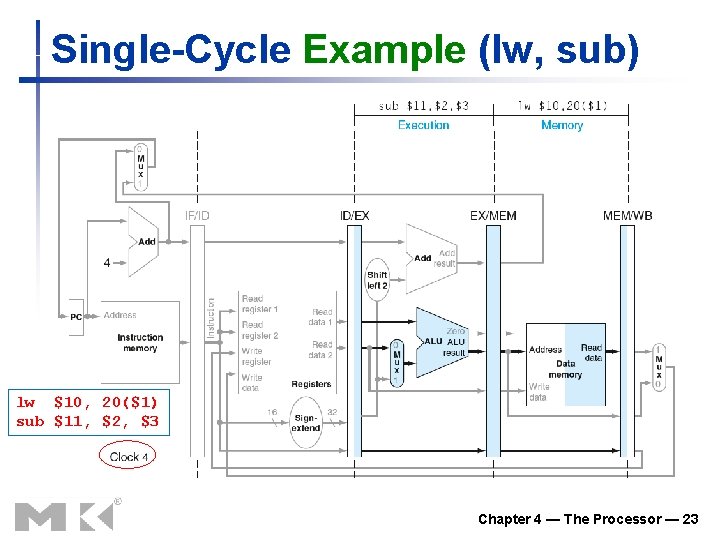

Single-Cycle Example (lw, sub) lw $10, 20($1) sub $11, $2, $3 Chapter 4 — The Processor — 23

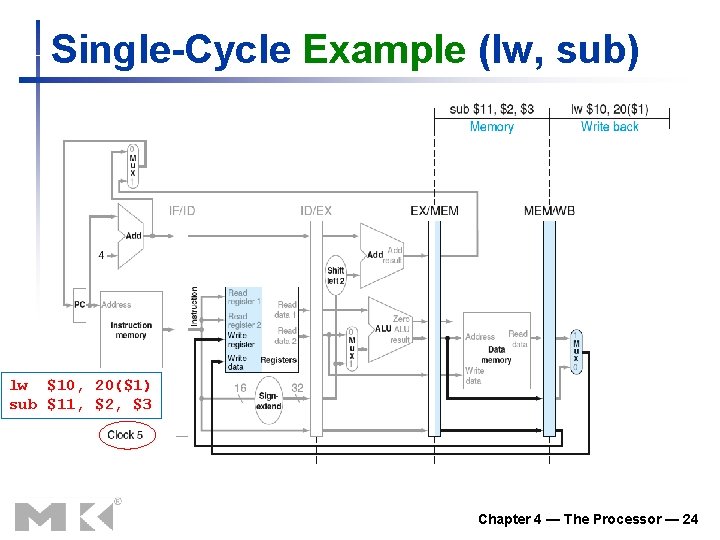

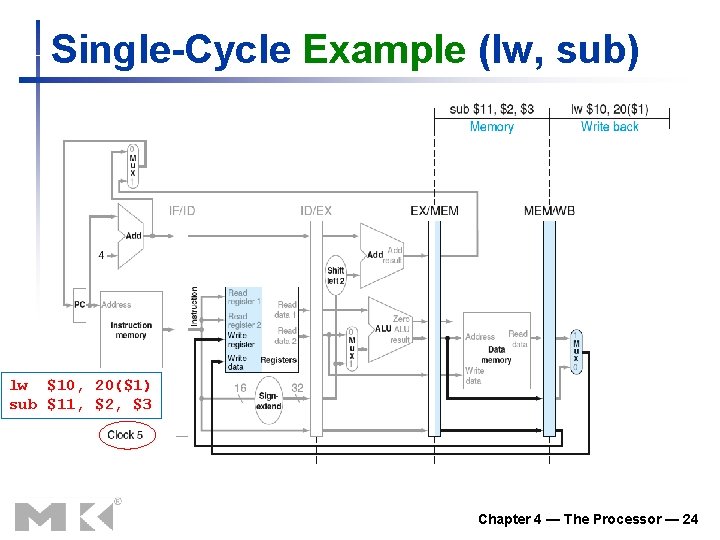

Single-Cycle Example (lw, sub) lw $10, 20($1) sub $11, $2, $3 Chapter 4 — The Processor — 24

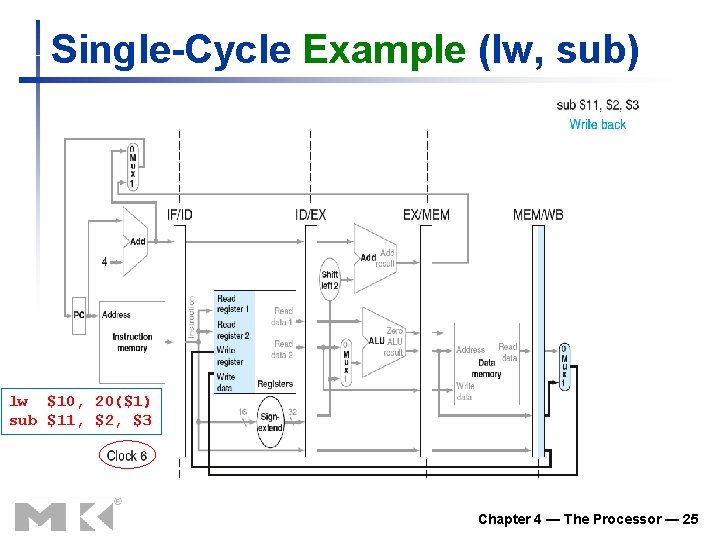

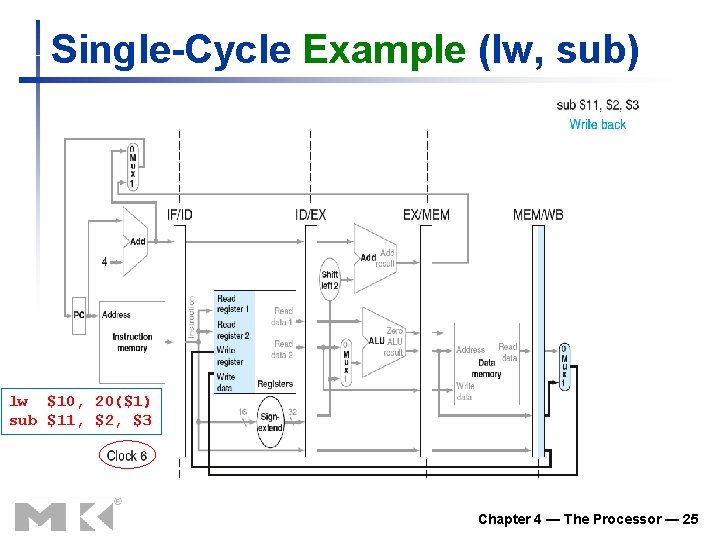

Single-Cycle Example (lw, sub) lw $10, 20($1) sub $11, $2, $3 Chapter 4 — The Processor — 25

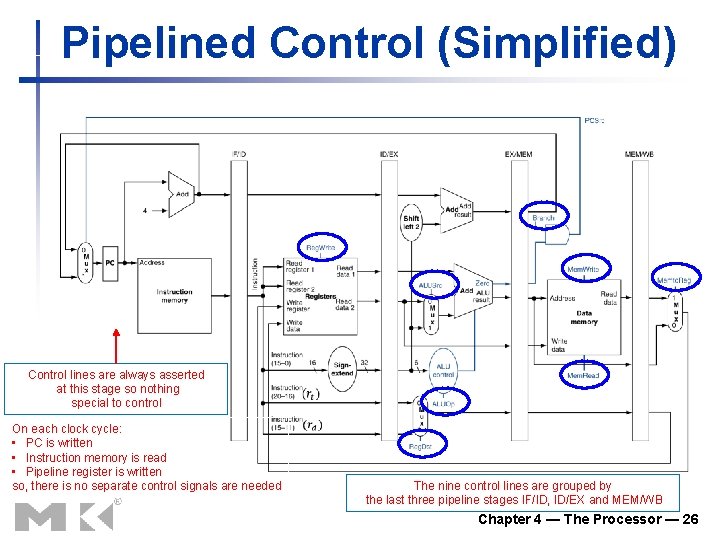

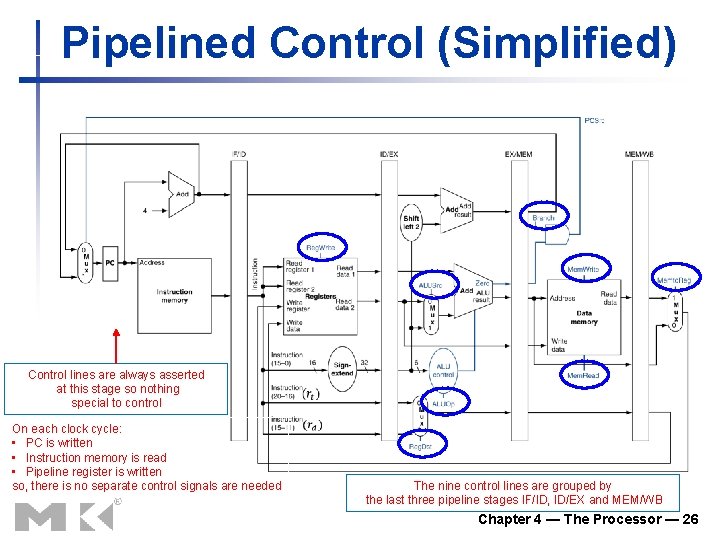

Pipelined Control (Simplified) Control lines are always asserted at this stage so nothing special to control On each clock cycle: • PC is written • Instruction memory is read • Pipeline register is written so, there is no separate control signals are needed The nine control lines are grouped by the last three pipeline stages IF/ID, ID/EX and MEM/WB Chapter 4 — The Processor — 26

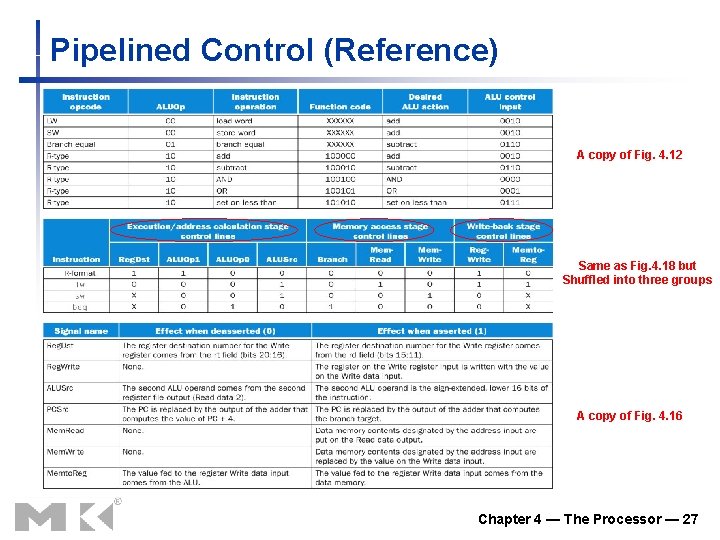

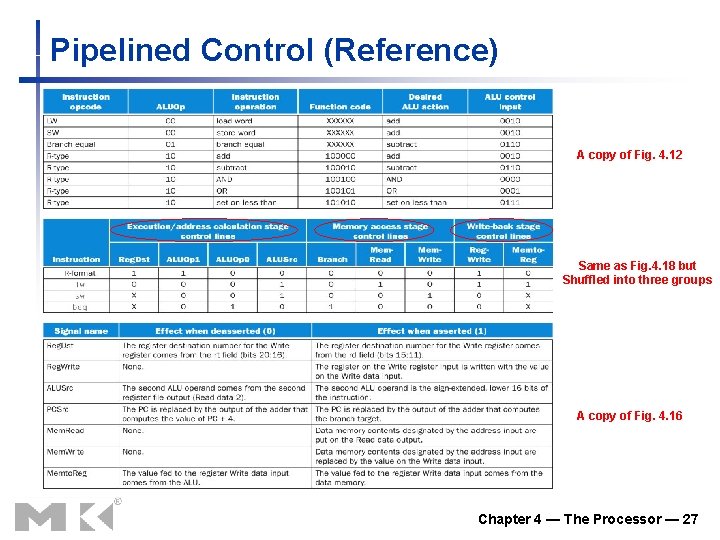

Pipelined Control (Reference) A copy of Fig. 4. 12 Same as Fig. 4. 18 but Shuffled into three groups A copy of Fig. 4. 16 Chapter 4 — The Processor — 27

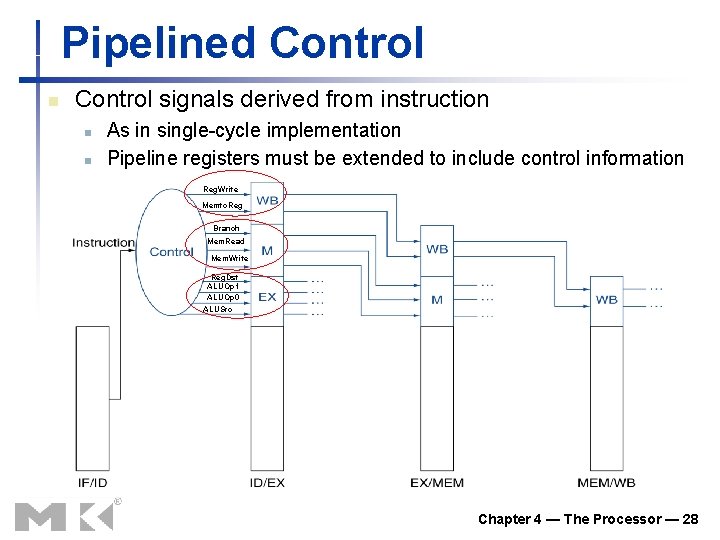

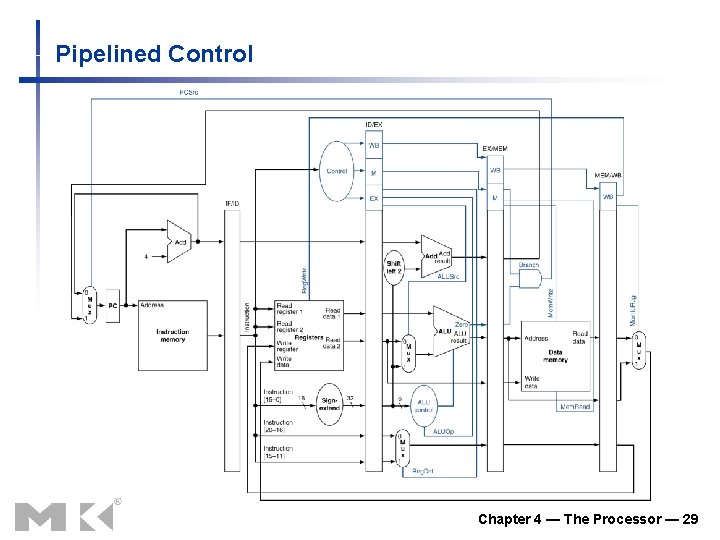

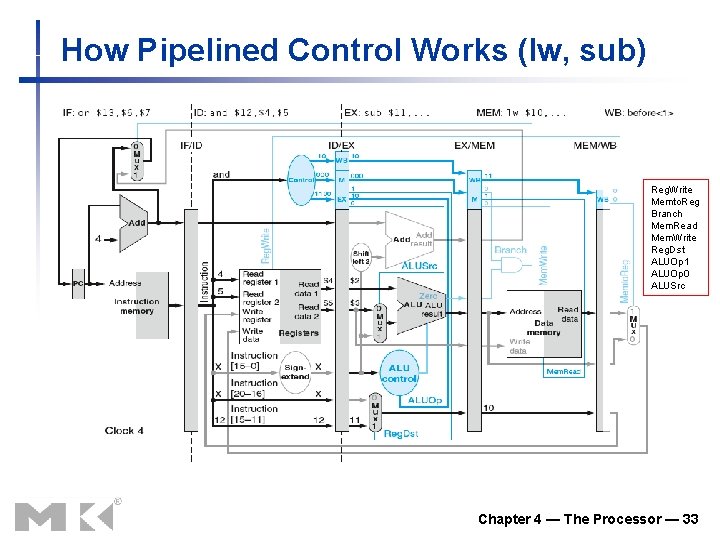

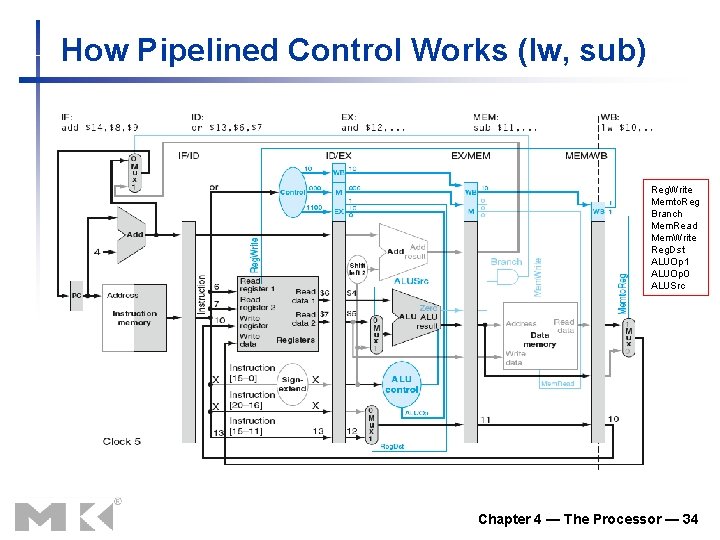

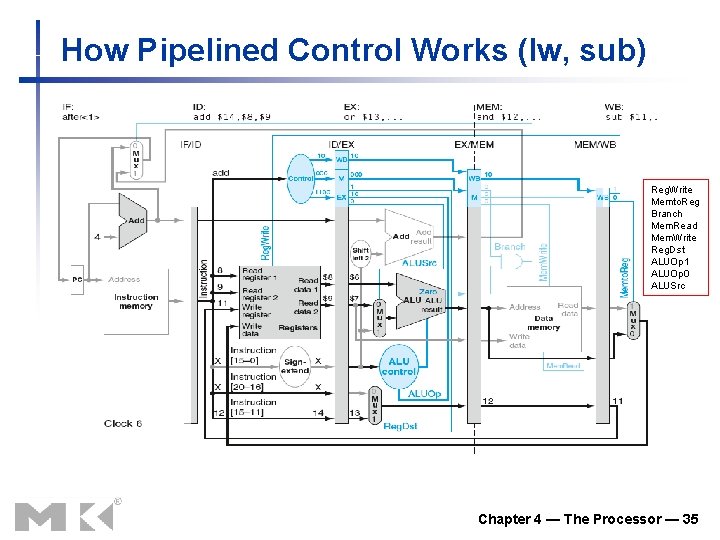

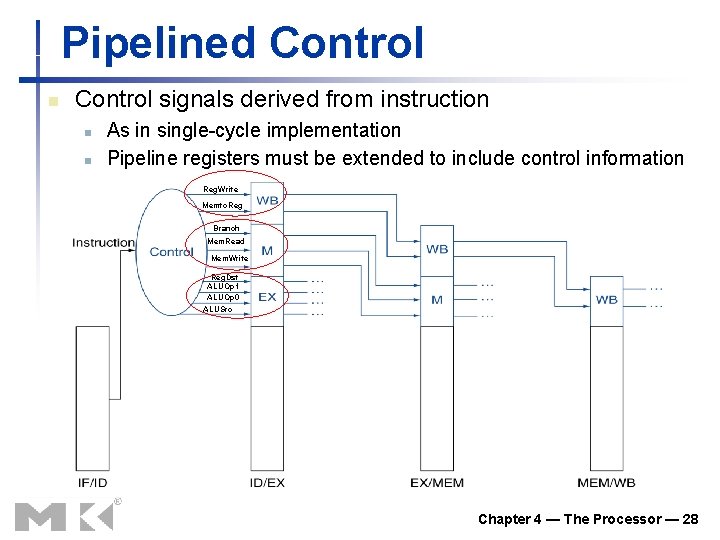

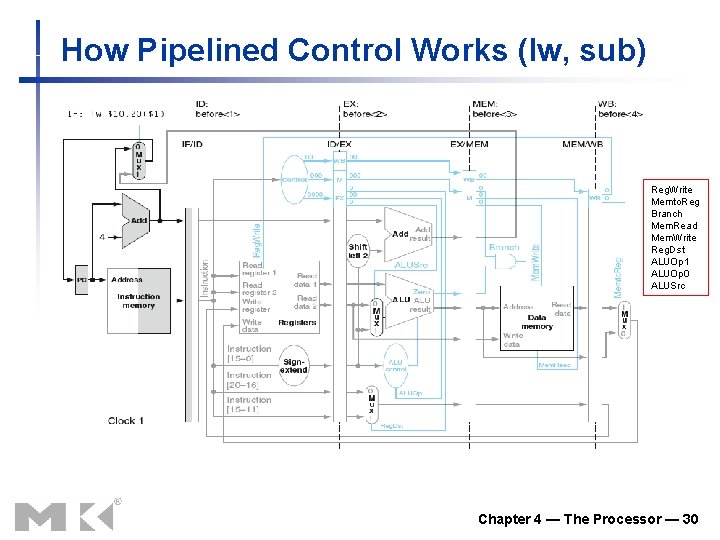

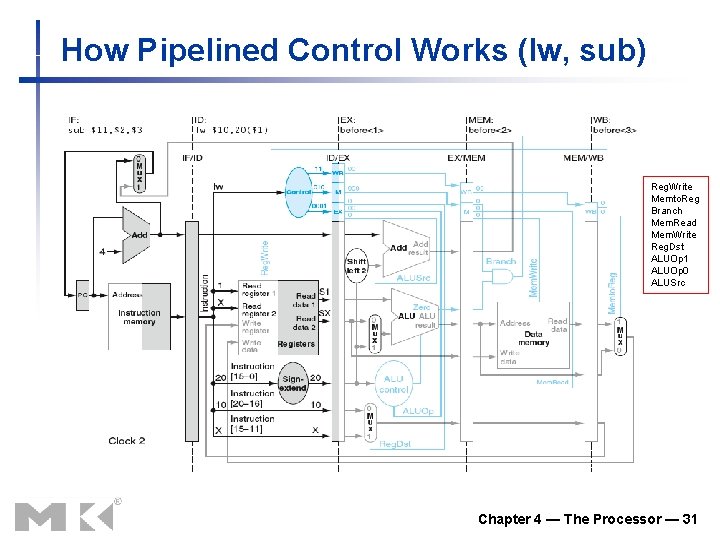

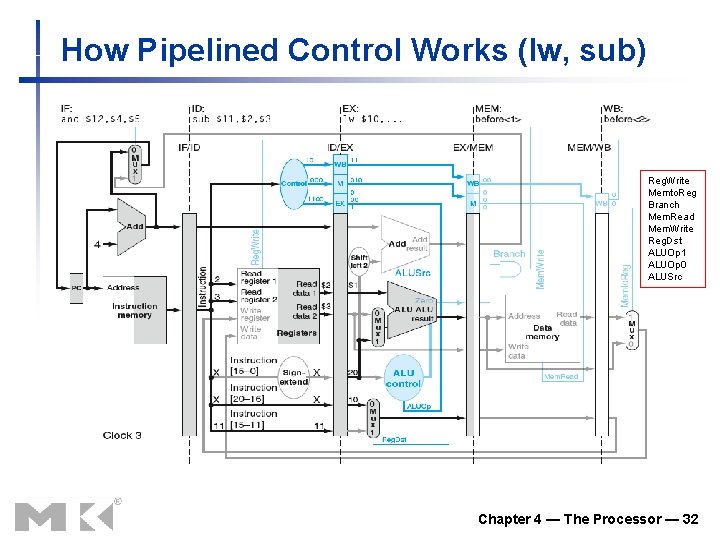

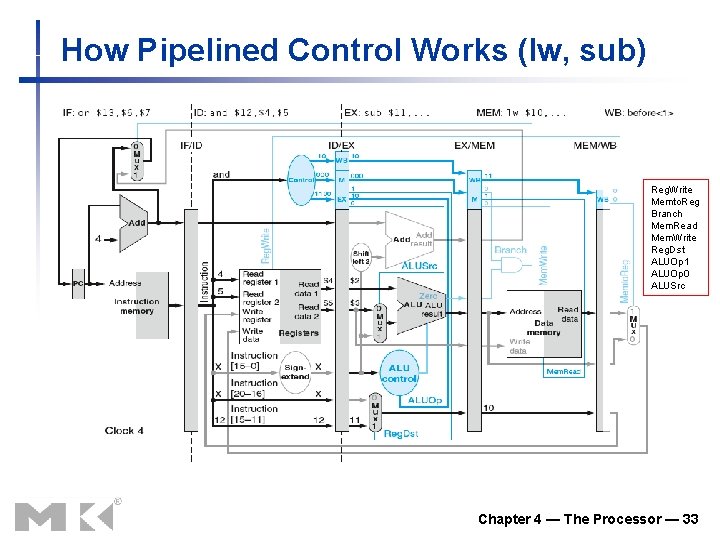

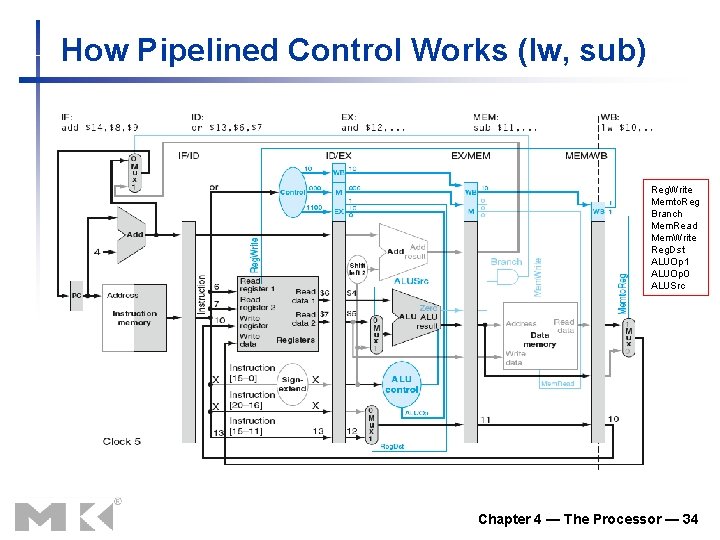

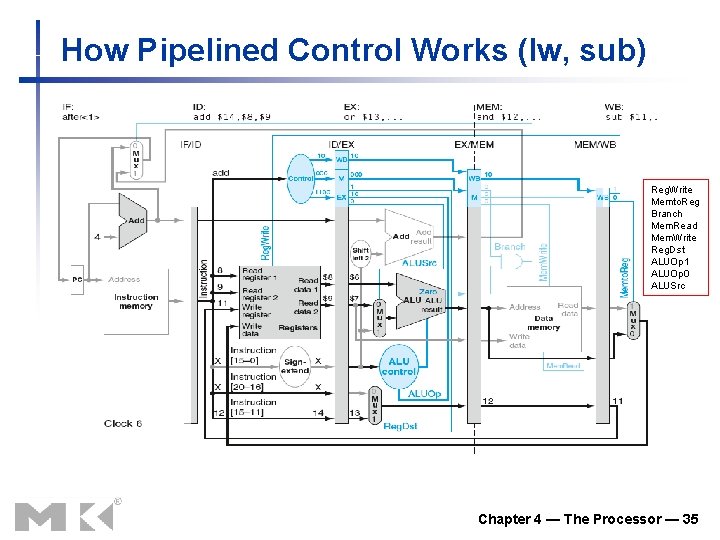

Pipelined Control n Control signals derived from instruction n n As in single-cycle implementation Pipeline registers must be extended to include control information Reg. Write Memto. Reg Branch Mem. Read Mem. Write Reg. Dst ALUOp 1 ALUOp 0 ALUSrc Chapter 4 — The Processor — 28

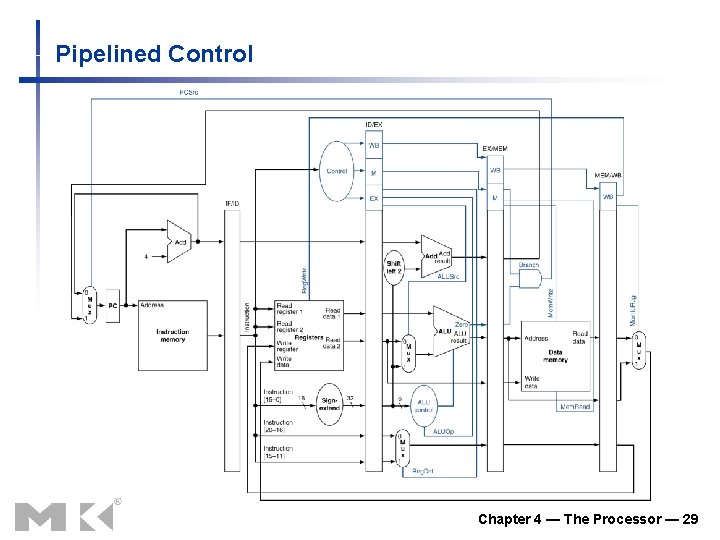

Pipelined Control Chapter 4 — The Processor — 29

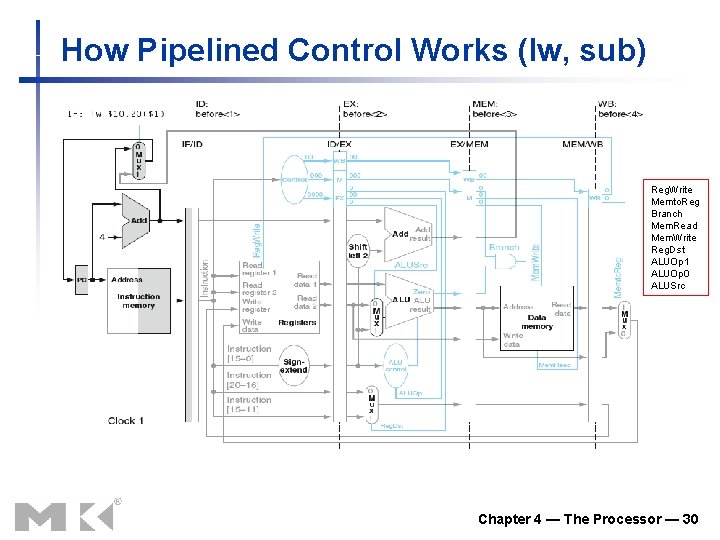

How Pipelined Control Works (lw, sub) Reg. Write Memto. Reg Branch Mem. Read Mem. Write Reg. Dst ALUOp 1 ALUOp 0 ALUSrc Chapter 4 — The Processor — 30

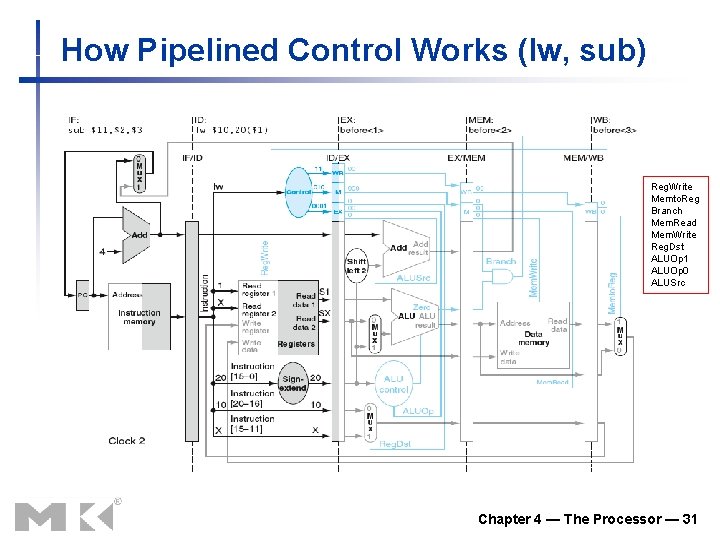

How Pipelined Control Works (lw, sub) Reg. Write Memto. Reg Branch Mem. Read Mem. Write Reg. Dst ALUOp 1 ALUOp 0 ALUSrc Chapter 4 — The Processor — 31

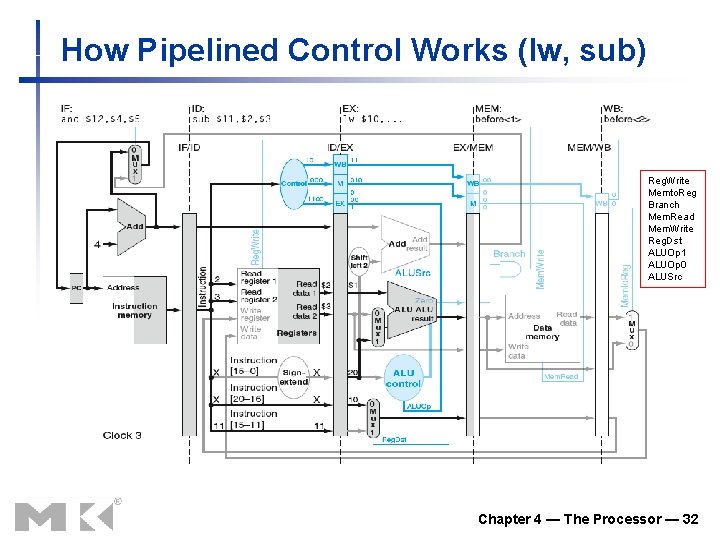

How Pipelined Control Works (lw, sub) Reg. Write Memto. Reg Branch Mem. Read Mem. Write Reg. Dst ALUOp 1 ALUOp 0 ALUSrc Chapter 4 — The Processor — 32

How Pipelined Control Works (lw, sub) Reg. Write Memto. Reg Branch Mem. Read Mem. Write Reg. Dst ALUOp 1 ALUOp 0 ALUSrc Chapter 4 — The Processor — 33

How Pipelined Control Works (lw, sub) Reg. Write Memto. Reg Branch Mem. Read Mem. Write Reg. Dst ALUOp 1 ALUOp 0 ALUSrc Chapter 4 — The Processor — 34

How Pipelined Control Works (lw, sub) Reg. Write Memto. Reg Branch Mem. Read Mem. Write Reg. Dst ALUOp 1 ALUOp 0 ALUSrc Chapter 4 — The Processor — 35