Chapter 4 Instruction Set 1 Instruction Set Overview

- Slides: 31

Chapter 4 Instruction Set 1

Instruction Set Overview Ø PIC 18 F 4520 devices incorporate the standard set of: § 75 PIC 18 core instructions, § 8 extended set of instructions, for the optimization of code 2

Standard Instruction Set Ø The standard PIC 18 instruction set are : § a single program memory word (16 bits), and § four instructions that require two program memory locations. Ø Each single-word instruction is a 16 -bit word divided into: § an opcode, which specifies the instruction type and § one or more operands, which further specify the operation of the instruction. 3

Standard Instruction Set Ø The instruction set is grouped into four basic categories: § Byte-oriented operations § Bit-oriented operations § Literal operations § Control operations 4

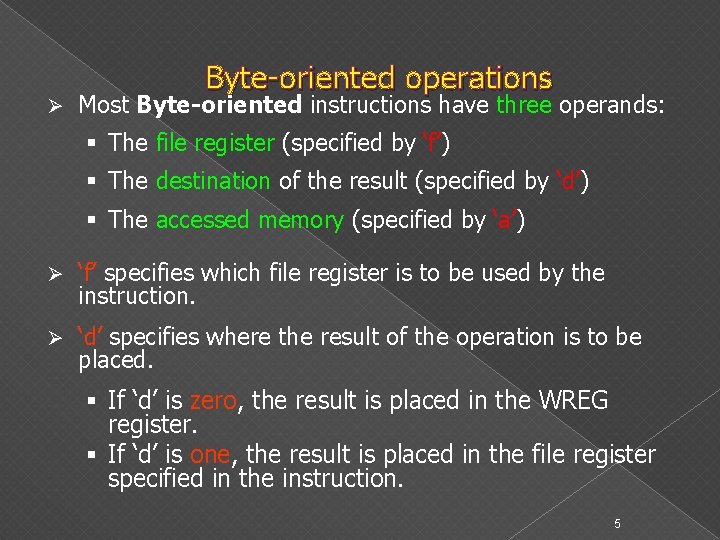

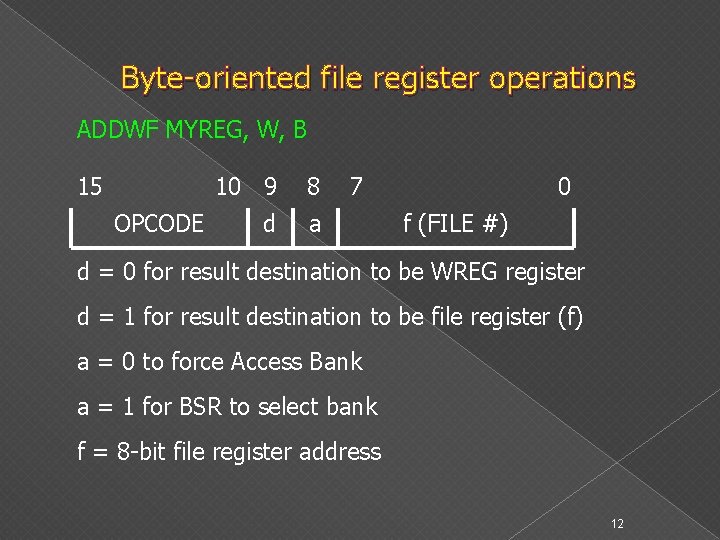

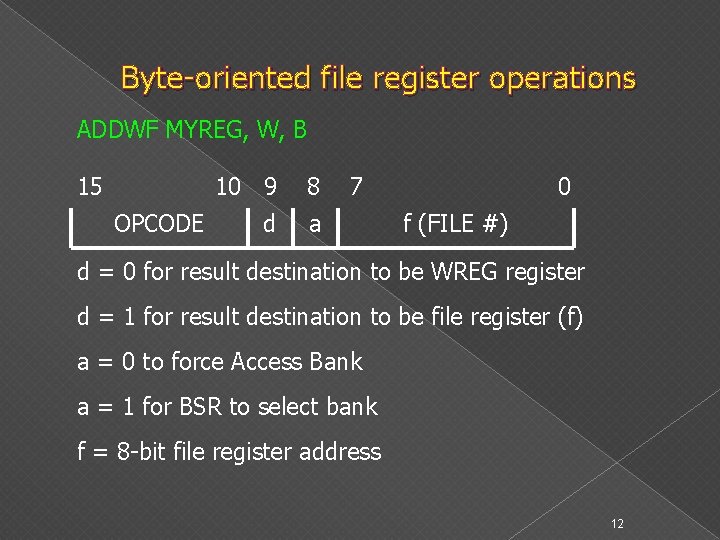

Ø Byte-oriented operations Most Byte-oriented instructions have three operands: § The file register (specified by ‘f’) § The destination of the result (specified by ‘d’) § The accessed memory (specified by ‘a’) Ø ‘f’ specifies which file register is to be used by the instruction. Ø ‘d’ specifies where the result of the operation is to be placed. § If ‘d’ is zero, the result is placed in the WREG register. § If ‘d’ is one, the result is placed in the file register specified in the instruction. 5

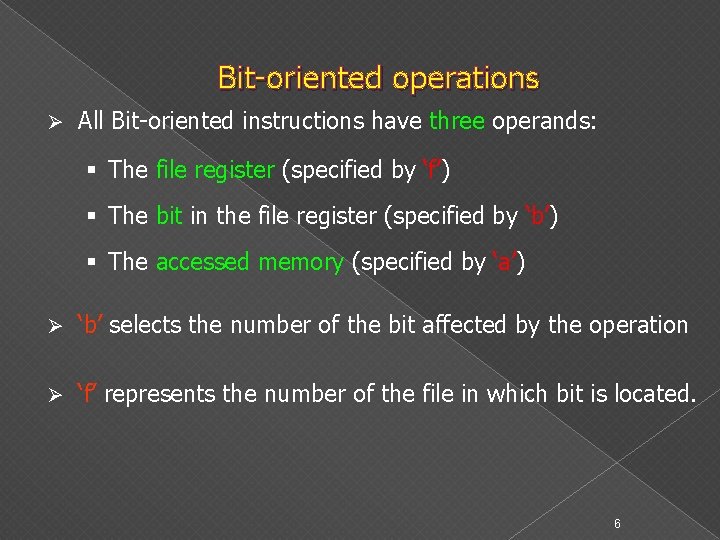

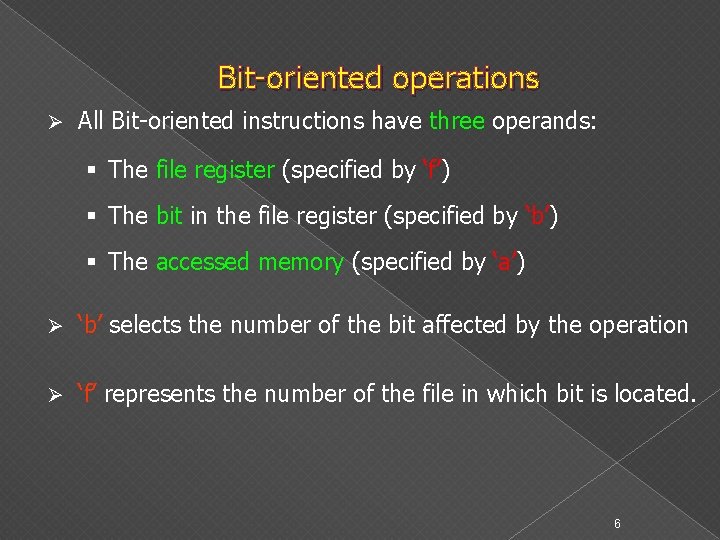

Bit-oriented operations Ø All Bit-oriented instructions have three operands: § The file register (specified by ‘f’) § The bit in the file register (specified by ‘b’) § The accessed memory (specified by ‘a’) Ø ‘b’ selects the number of the bit affected by the operation Ø ‘f’ represents the number of the file in which bit is located. 6

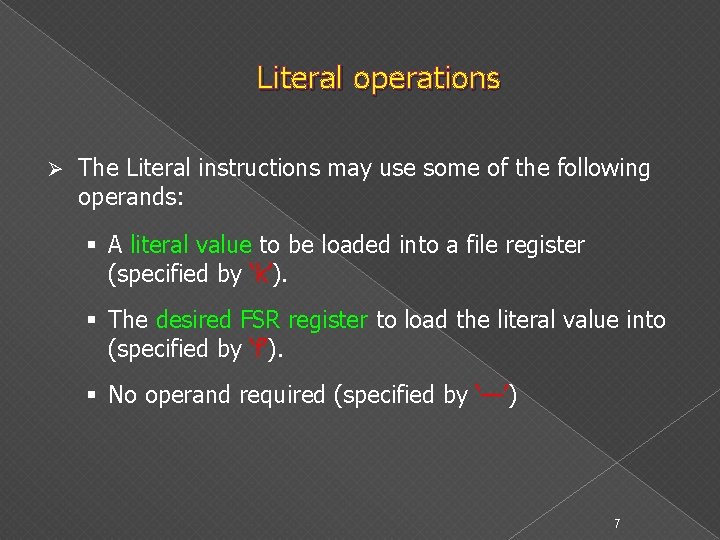

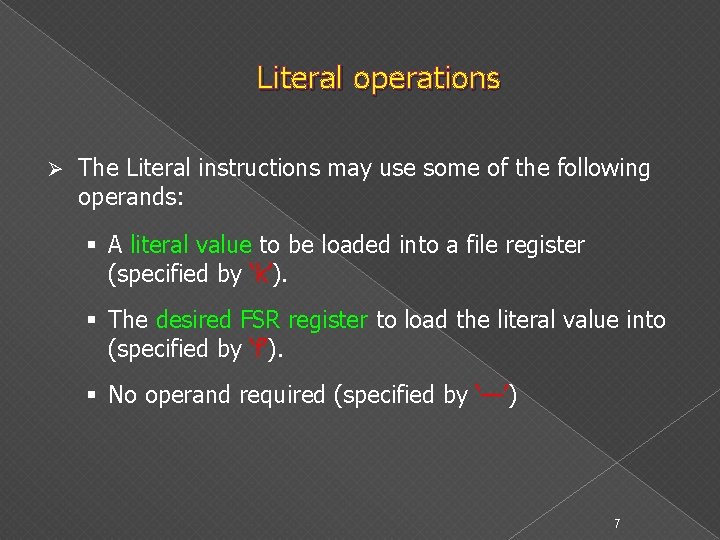

Literal operations Ø The Literal instructions may use some of the following operands: § A literal value to be loaded into a file register (specified by ‘k’). § The desired FSR register to load the literal value into (specified by ‘f’). § No operand required (specified by ‘—’) 7

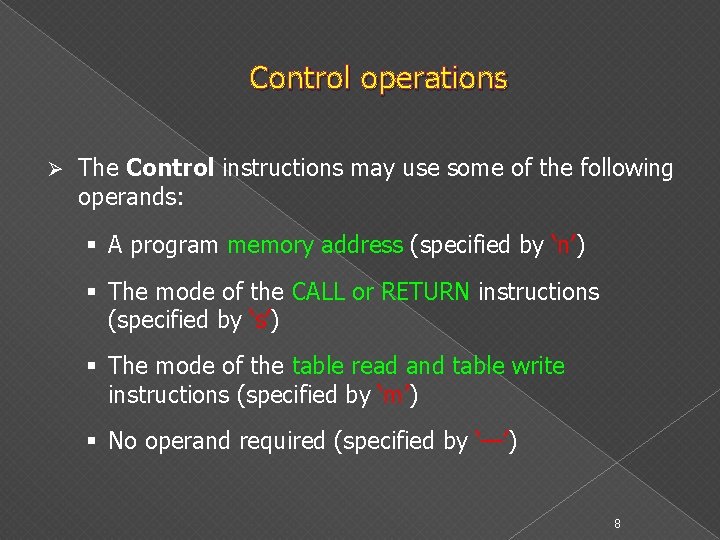

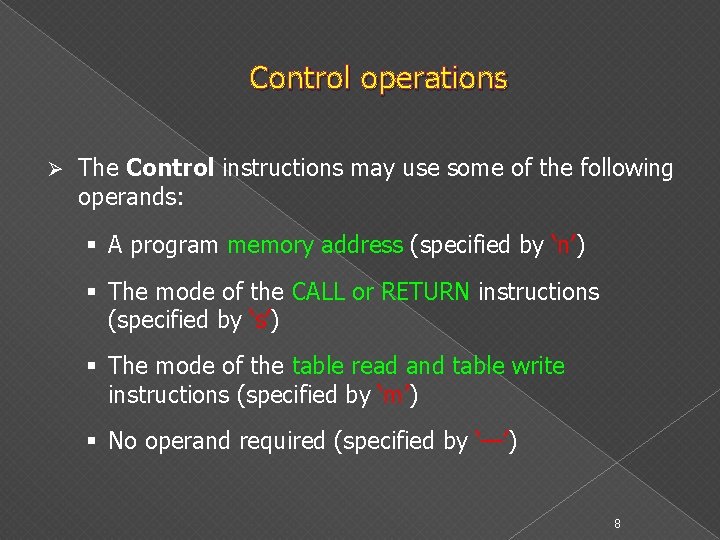

Control operations Ø The Control instructions may use some of the following operands: § A program memory address (specified by ‘n’) § The mode of the CALL or RETURN instructions (specified by ‘s’) § The mode of the table read and table write instructions (specified by ‘m’) § No operand required (specified by ‘—’) 8

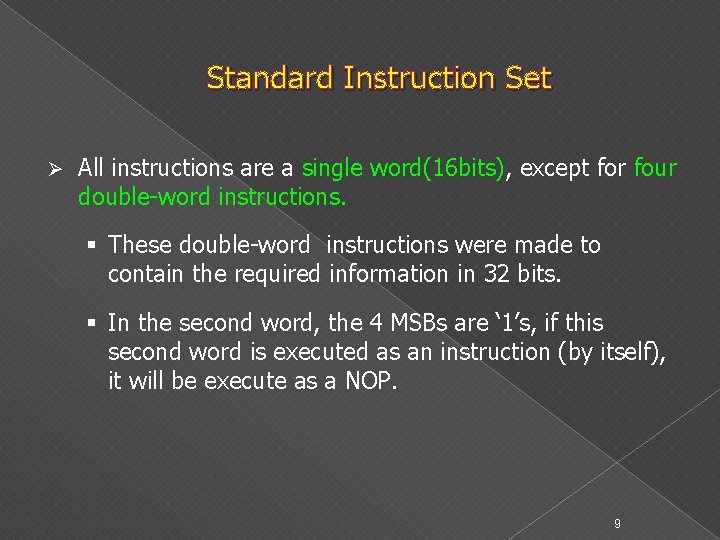

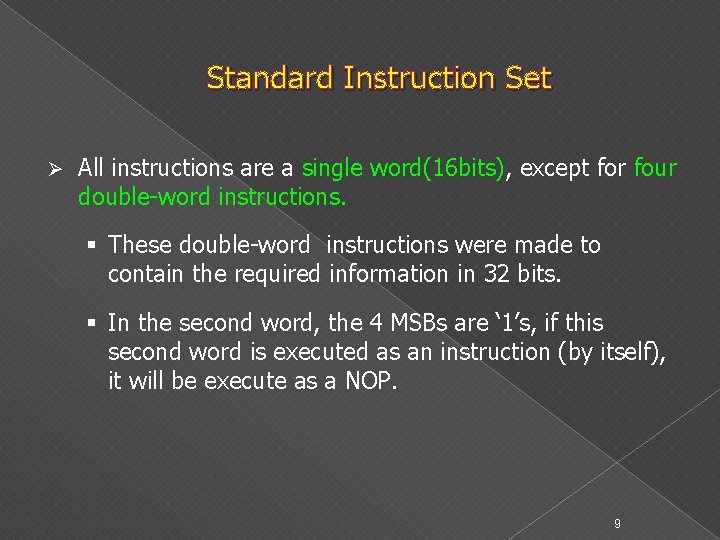

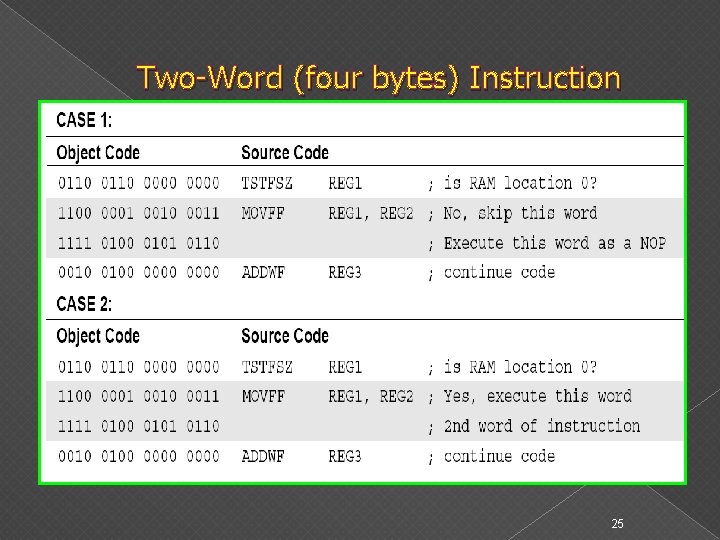

Standard Instruction Set Ø All instructions are a single word(16 bits), except for four double-word instructions. § These double-word instructions were made to contain the required information in 32 bits. § In the second word, the 4 MSBs are ‘ 1’s, if this second word is executed as an instruction (by itself), it will be execute as a NOP. 9

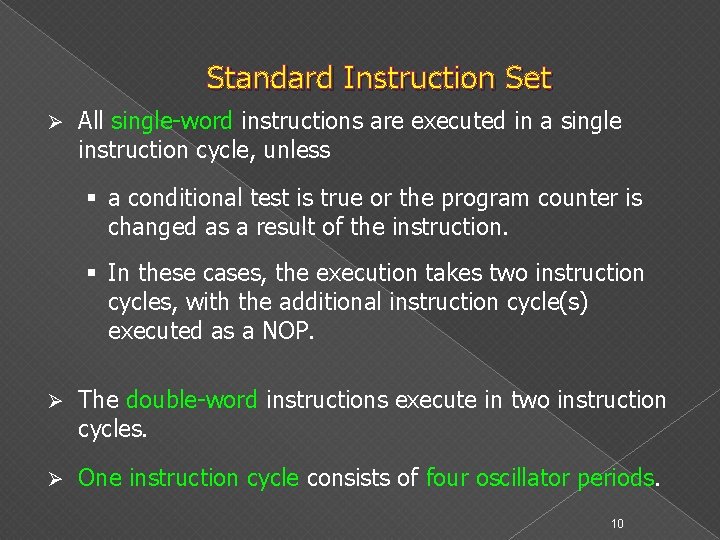

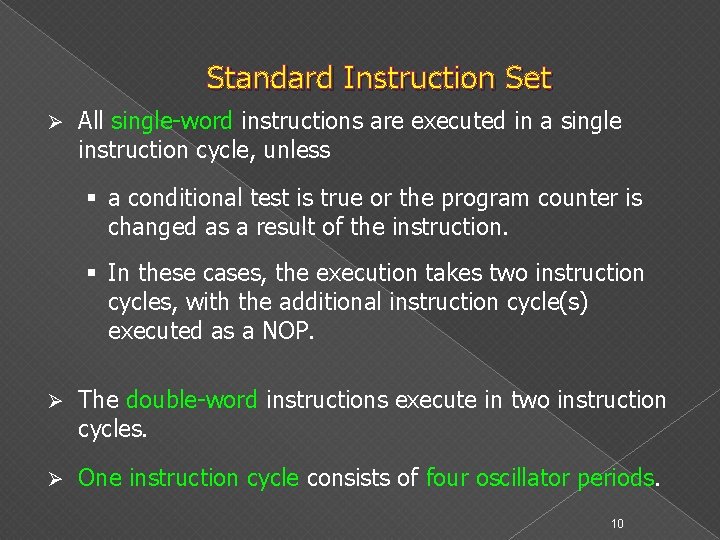

Standard Instruction Set Ø All single-word instructions are executed in a single instruction cycle, unless § a conditional test is true or the program counter is changed as a result of the instruction. § In these cases, the execution takes two instruction cycles, with the additional instruction cycle(s) executed as a NOP. Ø The double-word instructions execute in two instruction cycles. Ø One instruction cycle consists of four oscillator periods. 10

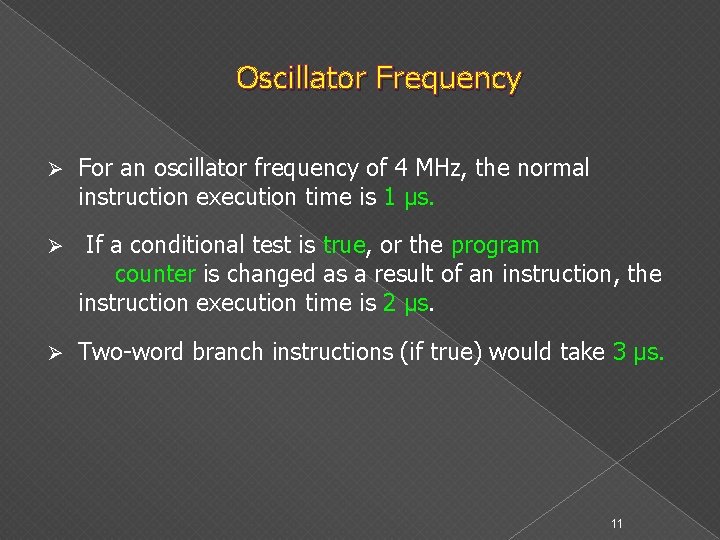

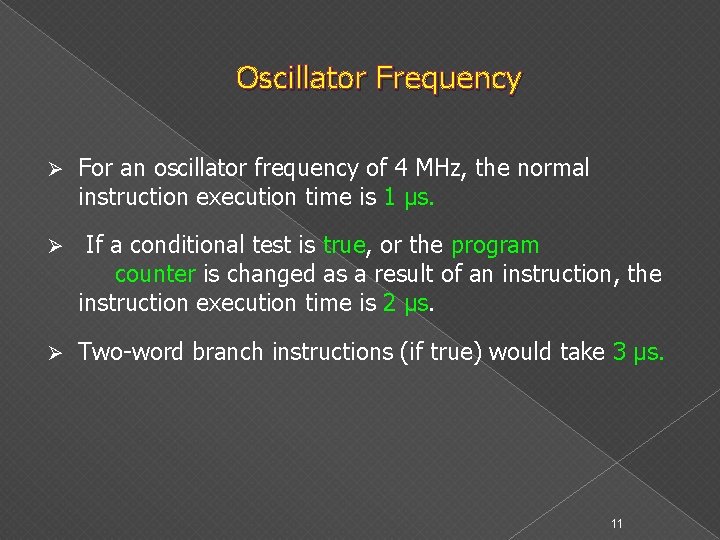

Oscillator Frequency Ø For an oscillator frequency of 4 MHz, the normal instruction execution time is 1 μs. Ø If a conditional test is true, or the program counter is changed as a result of an instruction, the instruction execution time is 2 μs. Ø Two-word branch instructions (if true) would take 3 μs. 11

Byte-oriented file register operations ADDWF MYREG, W, B 15 OPCODE 10 9 8 d a 7 0 f (FILE #) d = 0 for result destination to be WREG register d = 1 for result destination to be file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8 -bit file register address 12

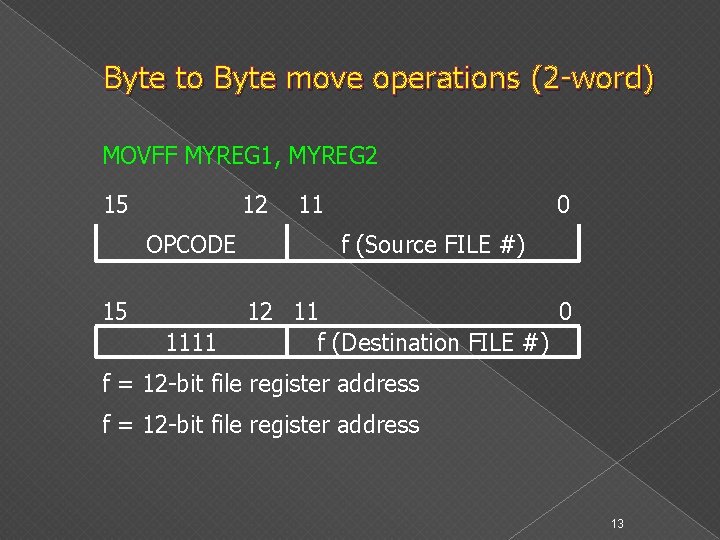

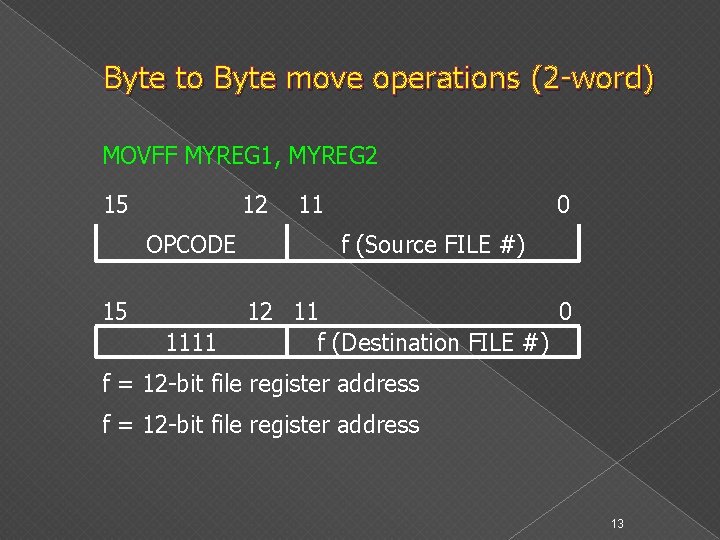

Byte to Byte move operations (2 -word) MOVFF MYREG 1, MYREG 2 15 12 OPCODE 15 1111 11 0 f (Source FILE #) 12 11 0 f (Destination FILE #) f = 12 -bit file register address 13

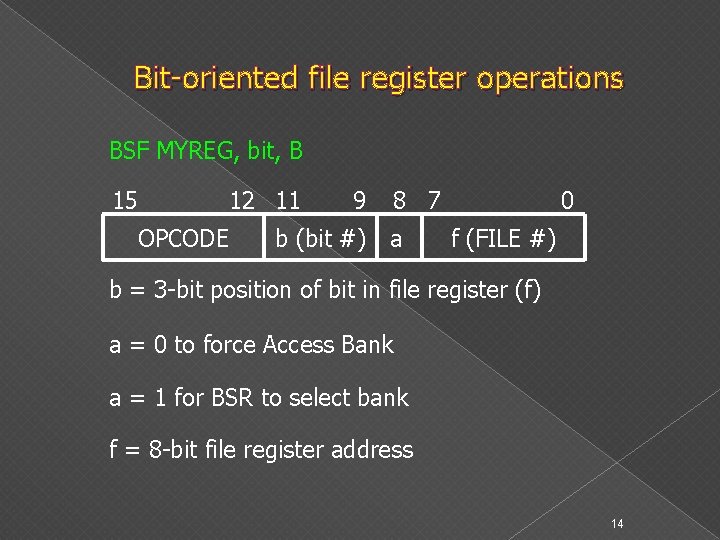

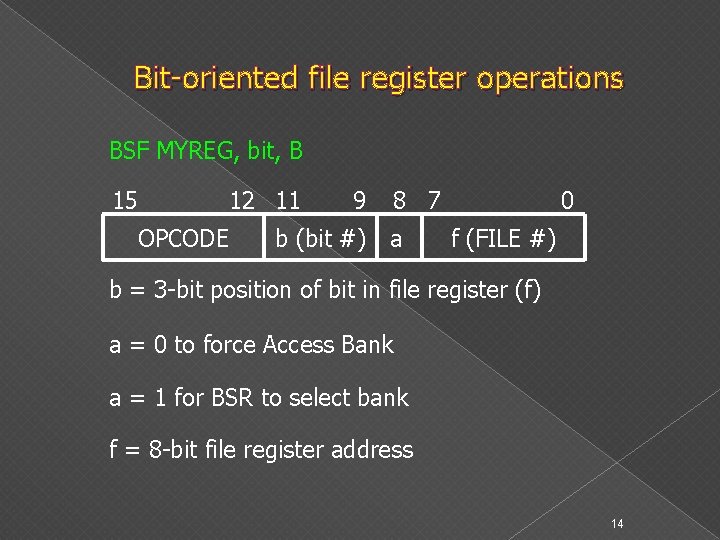

Bit-oriented file register operations BSF MYREG, bit, B 15 12 11 OPCODE 9 b (bit #) 8 7 a 0 f (FILE #) b = 3 -bit position of bit in file register (f) a = 0 to force Access Bank a = 1 for BSR to select bank f = 8 -bit file register address 14

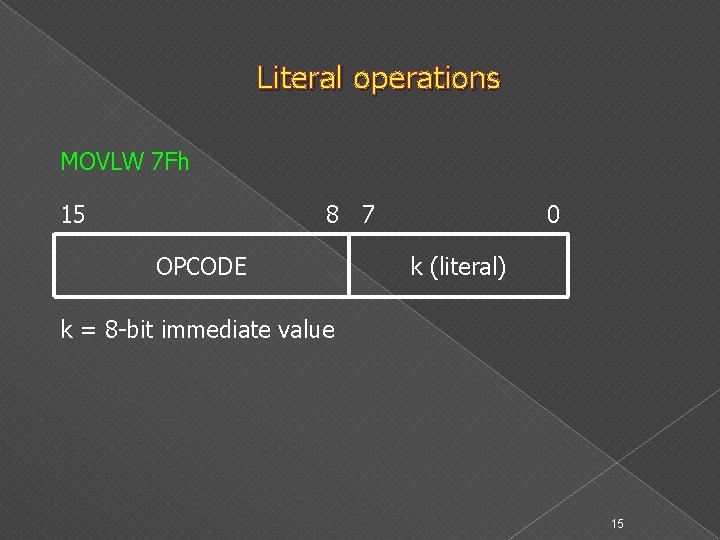

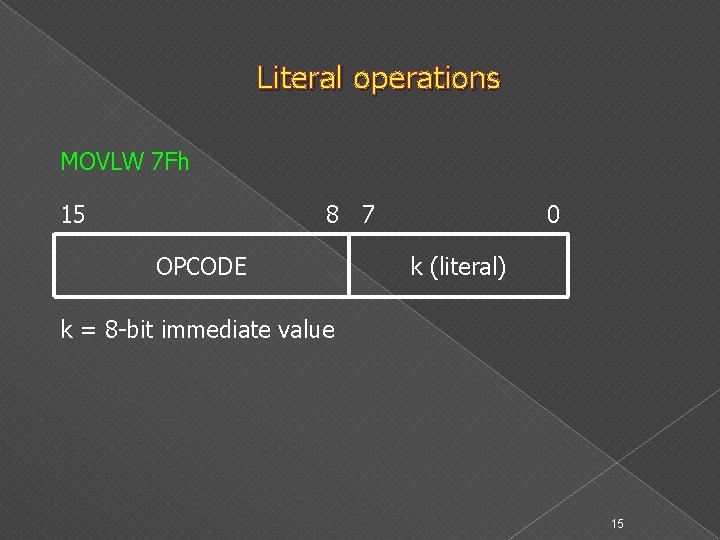

Literal operations MOVLW 7 Fh 15 8 7 OPCODE 0 k (literal) k = 8 -bit immediate value 15

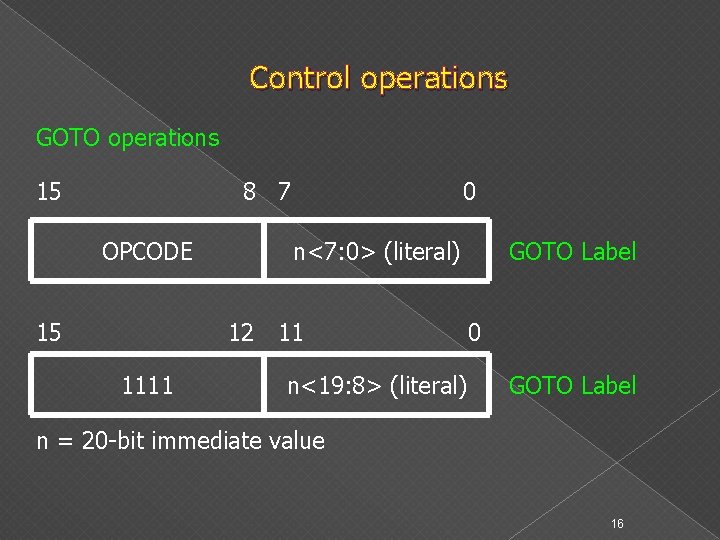

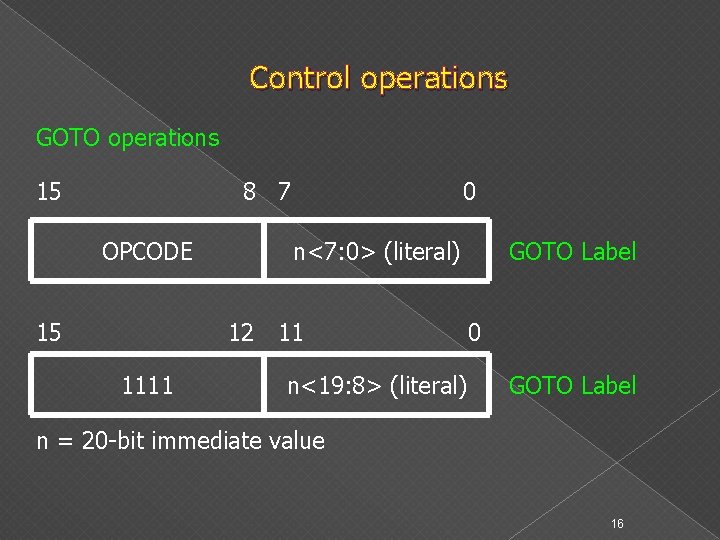

Control operations GOTO operations 15 8 7 OPCODE 15 0 n<7: 0> (literal) 12 11 1111 n<19: 8> (literal) GOTO Label 0 GOTO Label n = 20 -bit immediate value 16

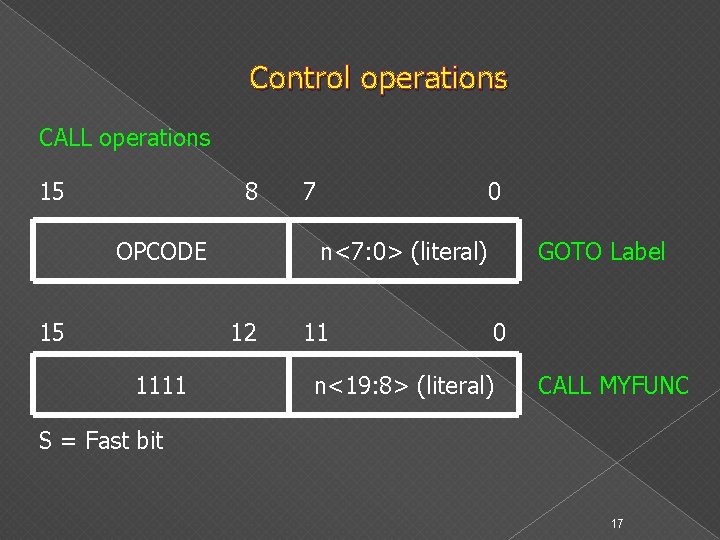

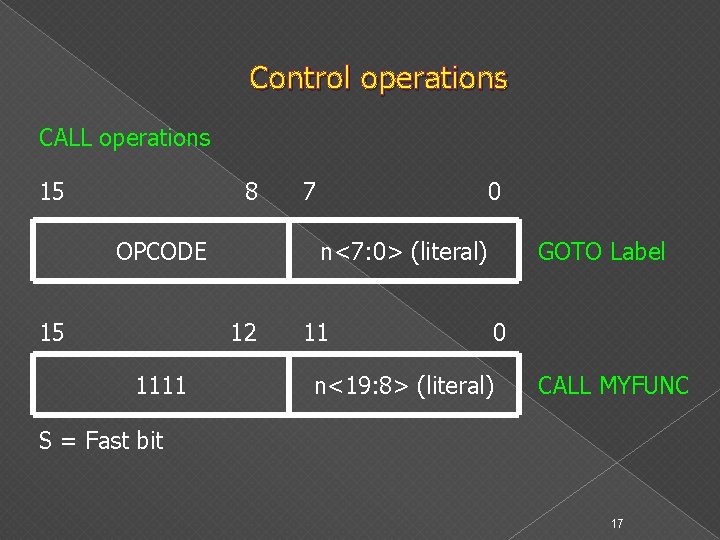

Control operations CALL operations 15 8 OPCODE 15 0 n<7: 0> (literal) 12 1111 7 11 GOTO Label 0 n<19: 8> (literal) CALL MYFUNC S = Fast bit 17

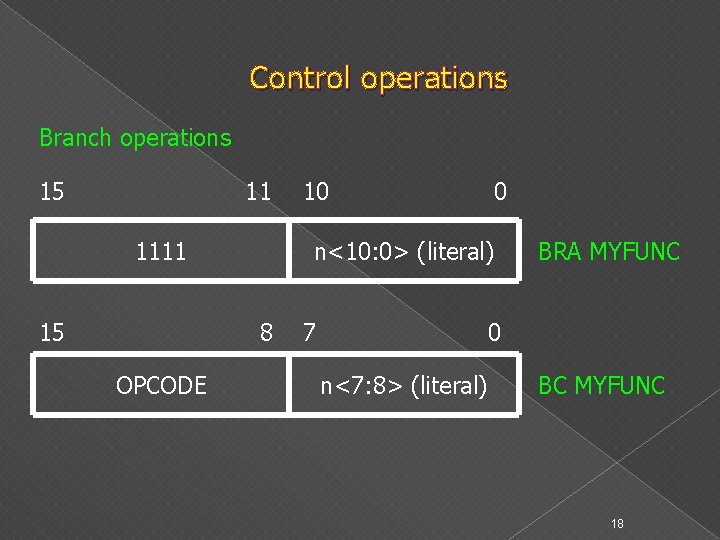

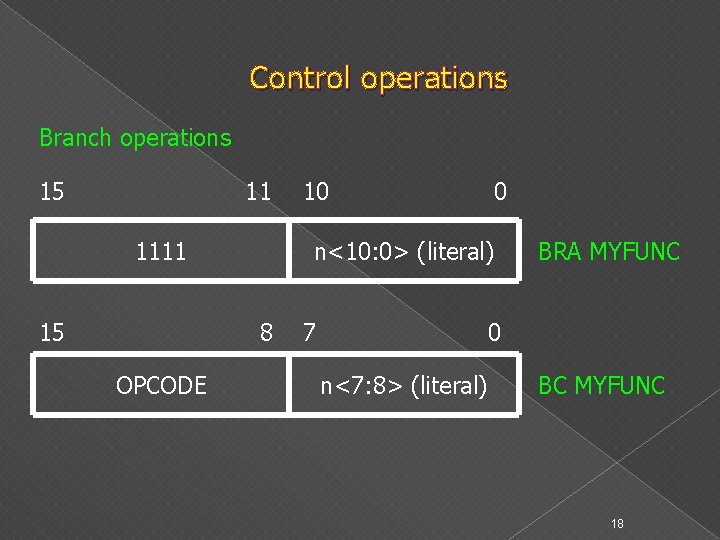

Control operations Branch operations 15 11 1111 15 0 n<10: 0> (literal) 8 OPCODE 10 7 BRA MYFUNC 0 n<7: 8> (literal) BC MYFUNC 18

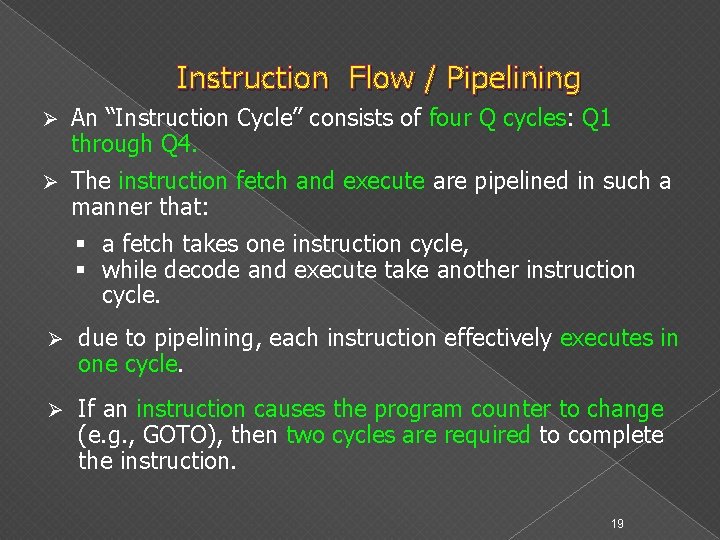

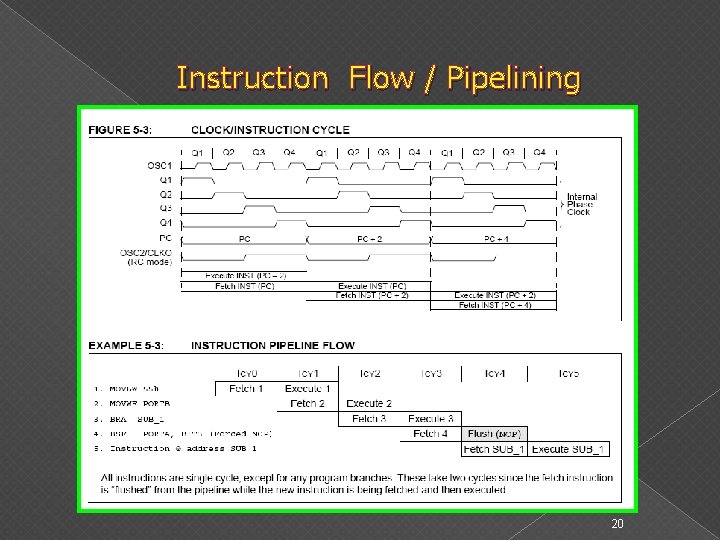

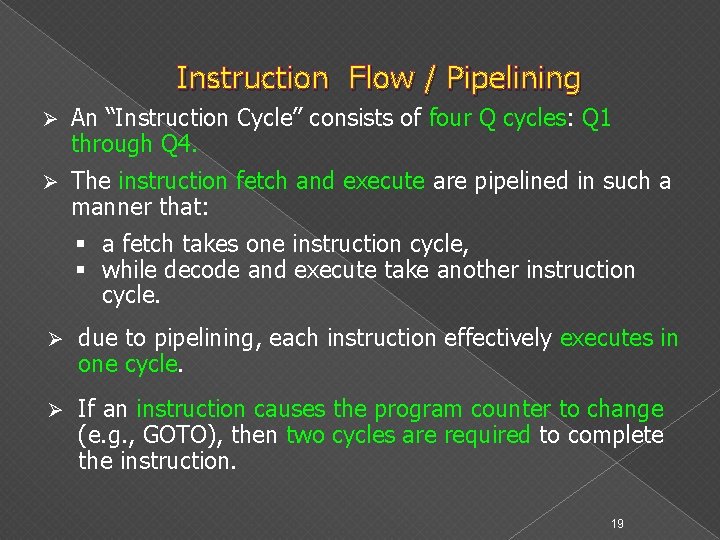

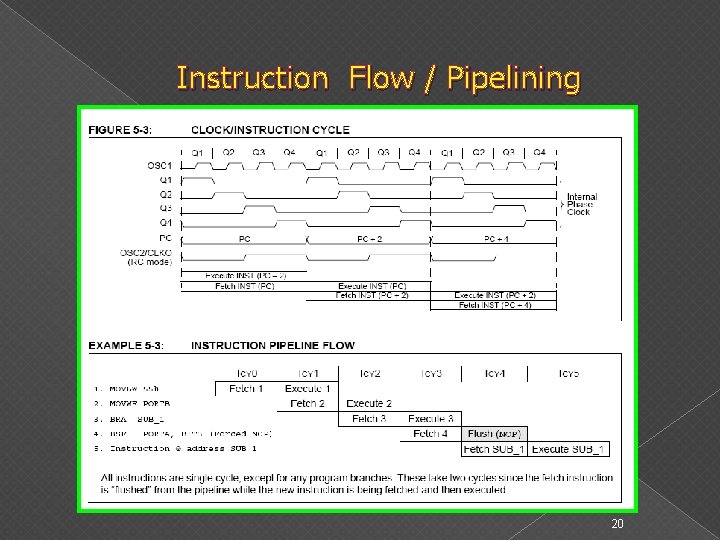

Instruction Flow / Pipelining Ø An “Instruction Cycle” consists of four Q cycles: Q 1 through Q 4. Ø The instruction fetch and execute are pipelined in such a manner that: § a fetch takes one instruction cycle, § while decode and execute take another instruction cycle. Ø due to pipelining, each instruction effectively executes in one cycle. Ø If an instruction causes the program counter to change (e. g. , GOTO), then two cycles are required to complete the instruction. 19

Instruction Flow / Pipelining 20

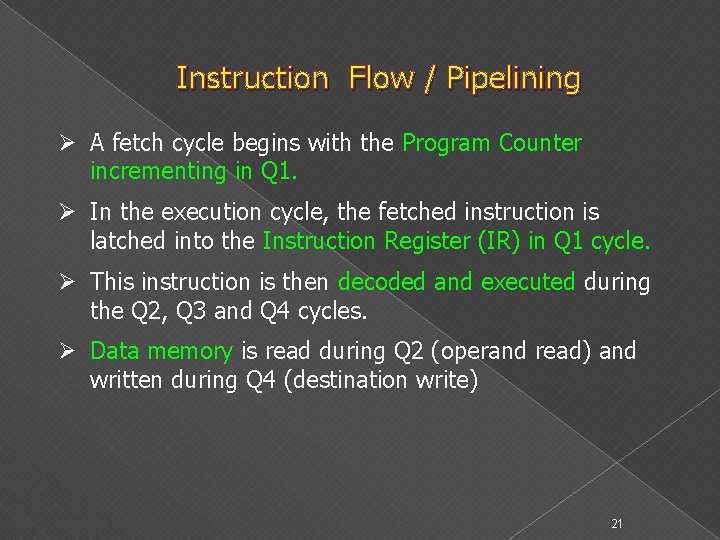

Instruction Flow / Pipelining Ø A fetch cycle begins with the Program Counter incrementing in Q 1. Ø In the execution cycle, the fetched instruction is latched into the Instruction Register (IR) in Q 1 cycle. Ø This instruction is then decoded and executed during the Q 2, Q 3 and Q 4 cycles. Ø Data memory is read during Q 2 (operand read) and written during Q 4 (destination write) 21

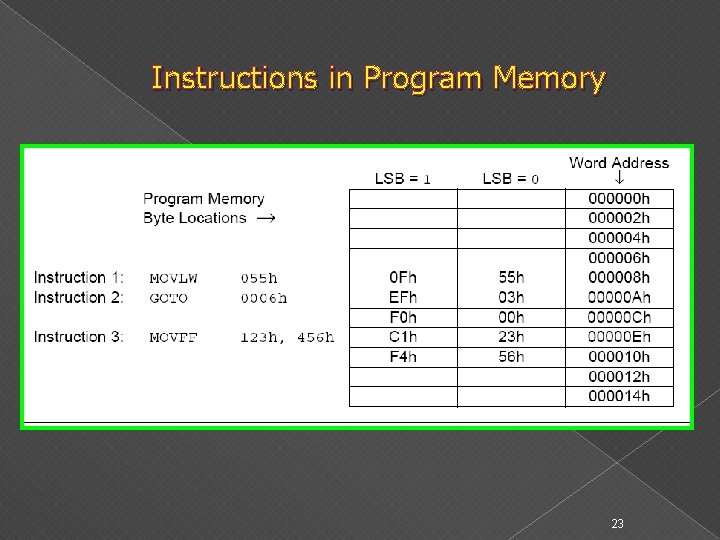

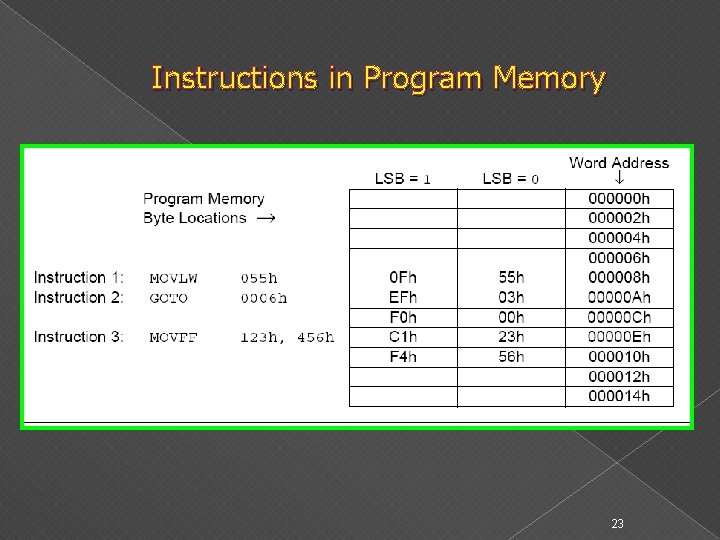

Instructions in Program Memory Ø The program memory is addressed in bytes. Ø Instructions are stored as two bytes or four bytes in program memory. Ø The Least Significant Byte of an instruction word is always stored in a program memory location with an even address (LSB = 0). Ø To maintain alignment with instruction boundaries, the PC increments in steps of 2 and the LSB will always read ‘ 0’. 22

Instructions in Program Memory 23

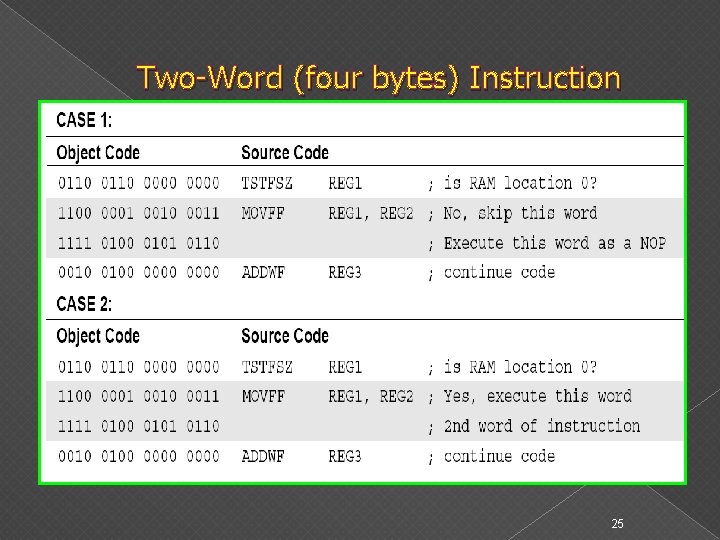

Two-Word (four bytes) Instruction Ø The standard PIC 18 instruction set has 4 two-word instructions: § § Ø CALL MOVFF GOTO LSFR. The entire data memory may be accessed by : § Direct, § Indirect or § Indexed Addressing modes. 24

Two-Word (four bytes) Instruction 25

Data Addressing Modes Ø The addressing modes are: § § Ø Inherent Literal Direct Indirect An additional addressing mode, Indexed Literal Offset, is available when the extended instruction set is enabled (XINST Configuration bit = 1). 26

Inherent Addressing Ø Do not need any argument at all Ø They either perform an operation that globally affects the device or they operate implicitly on one register. Ø Examples include SLEEP, RESET and DAW. 27

Literal Addressing Ø Require an additional explicit argument in the opcode. Ø They require some literal value as an argument. Ø Examples are ADDLW and MOVLW, which, add or move a literal value to the W register. Ø CALL and GOTO, which include a 20 -bit program memory address. 28

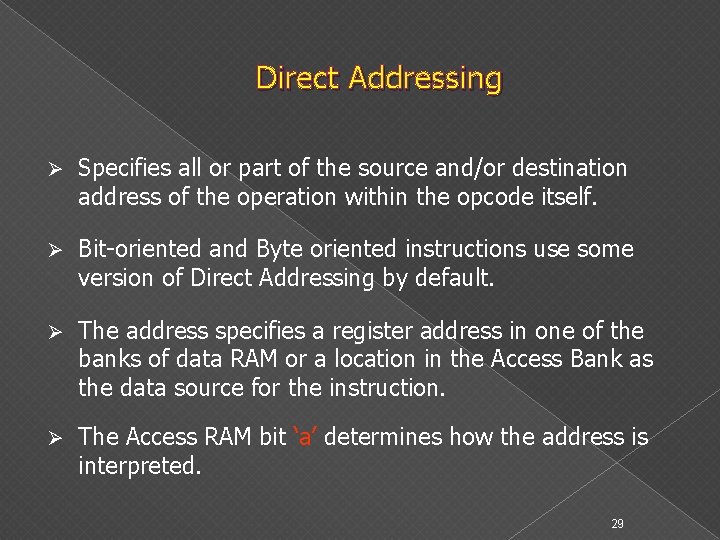

Direct Addressing Ø Specifies all or part of the source and/or destination address of the operation within the opcode itself. Ø Bit-oriented and Byte oriented instructions use some version of Direct Addressing by default. Ø The address specifies a register address in one of the banks of data RAM or a location in the Access Bank as the data source for the instruction. Ø The Access RAM bit ‘a’ determines how the address is interpreted. 29

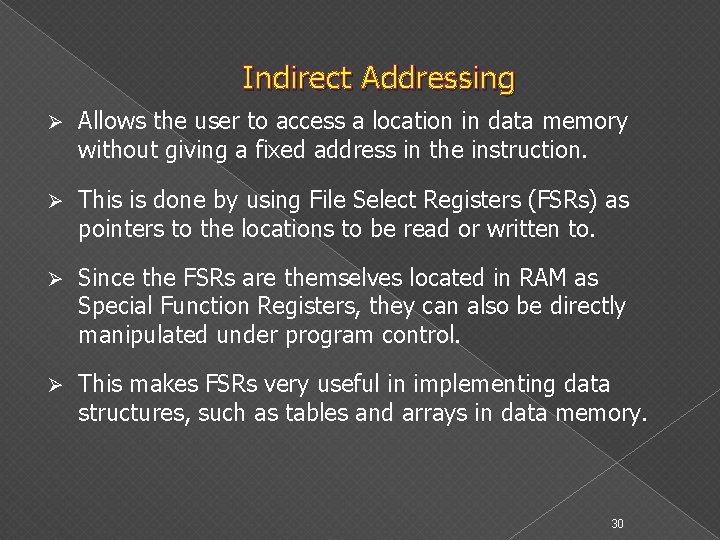

Indirect Addressing Ø Allows the user to access a location in data memory without giving a fixed address in the instruction. Ø This is done by using File Select Registers (FSRs) as pointers to the locations to be read or written to. Ø Since the FSRs are themselves located in RAM as Special Function Registers, they can also be directly manipulated under program control. Ø This makes FSRs very useful in implementing data structures, such as tables and arrays in data memory. 30

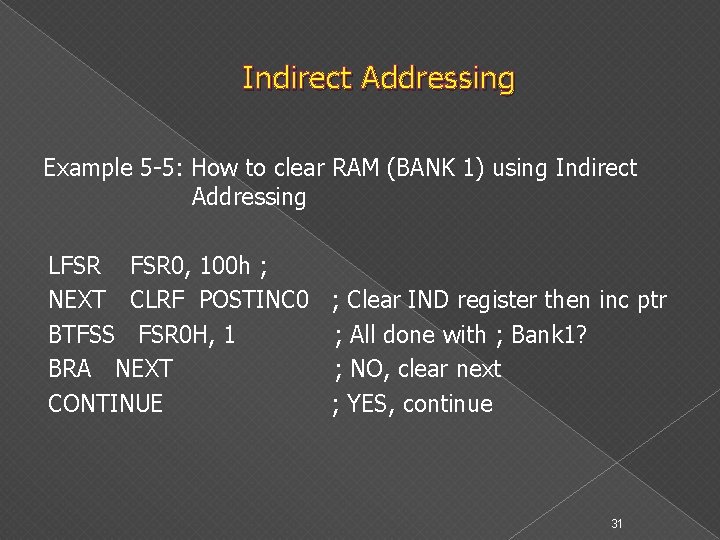

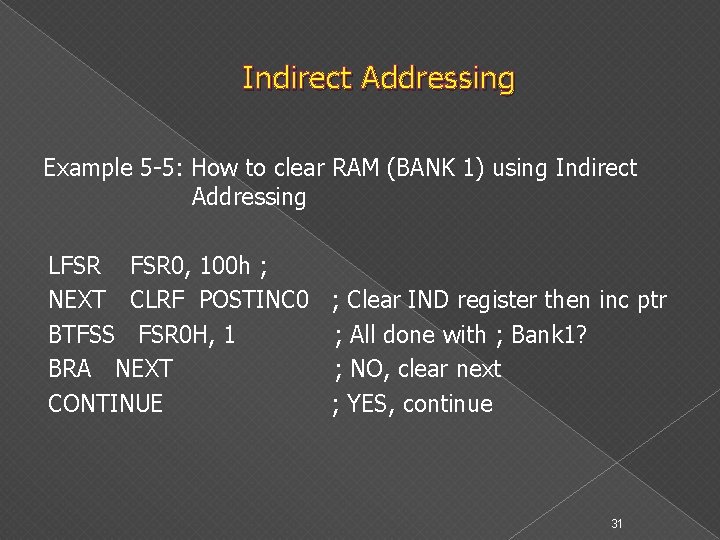

Indirect Addressing Example 5 -5: How to clear RAM (BANK 1) using Indirect Addressing LFSR 0, 100 h ; NEXT CLRF POSTINC 0 ; Clear IND register then inc ptr BTFSS FSR 0 H, 1 ; All done with ; Bank 1? BRA NEXT ; NO, clear next CONTINUE ; YES, continue 31