DSP 56800 E Instruction Set Instruction set can

- Slides: 52

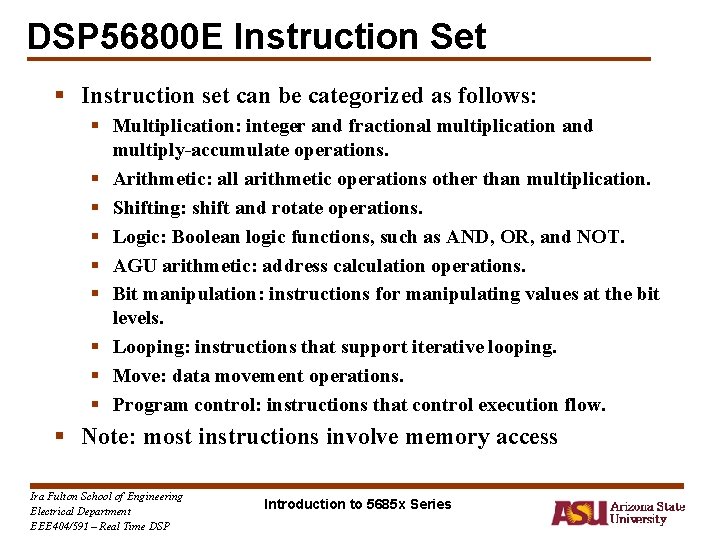

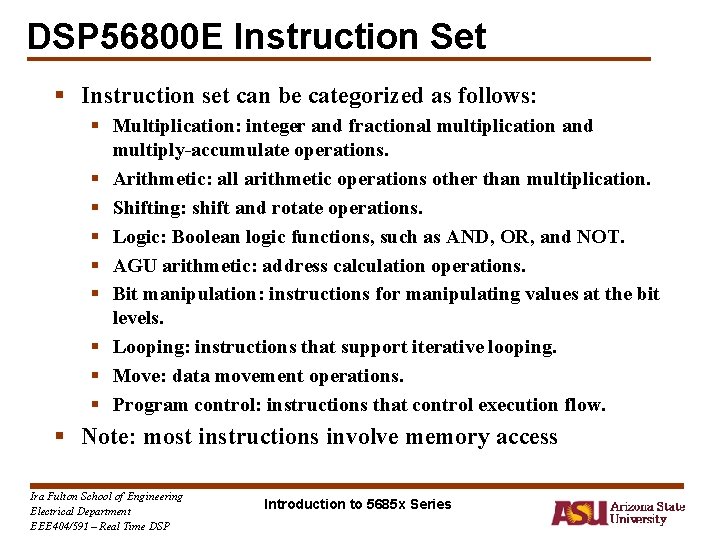

DSP 56800 E Instruction Set § Instruction set can be categorized as follows: § Multiplication: integer and fractional multiplication and multiply-accumulate operations. § Arithmetic: all arithmetic operations other than multiplication. § Shifting: shift and rotate operations. § Logic: Boolean logic functions, such as AND, OR, and NOT. § AGU arithmetic: address calculation operations. § Bit manipulation: instructions for manipulating values at the bit levels. § Looping: instructions that support iterative looping. § Move: data movement operations. § Program control: instructions that control execution flow. § Note: most instructions involve memory access Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series

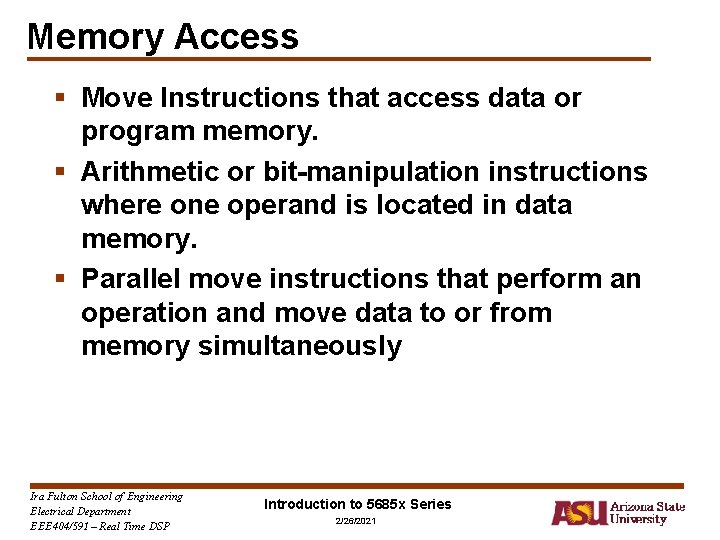

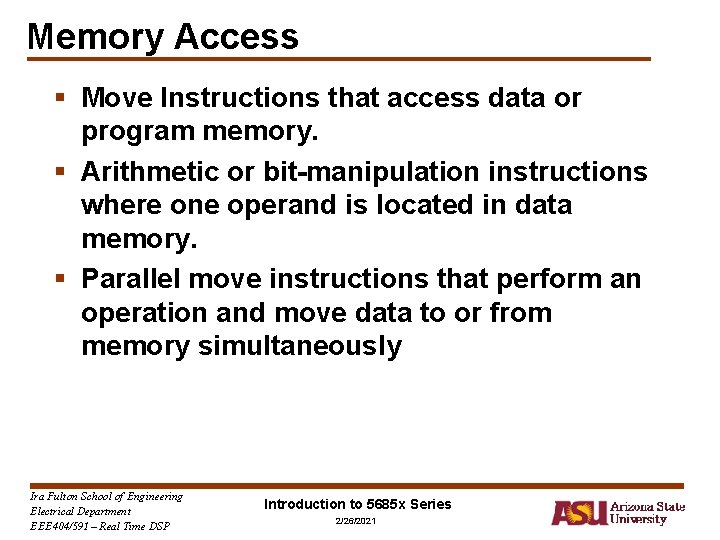

Memory Access § Move Instructions that access data or program memory. § Arithmetic or bit-manipulation instructions where one operand is located in data memory. § Parallel move instructions that perform an operation and move data to or from memory simultaneously Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

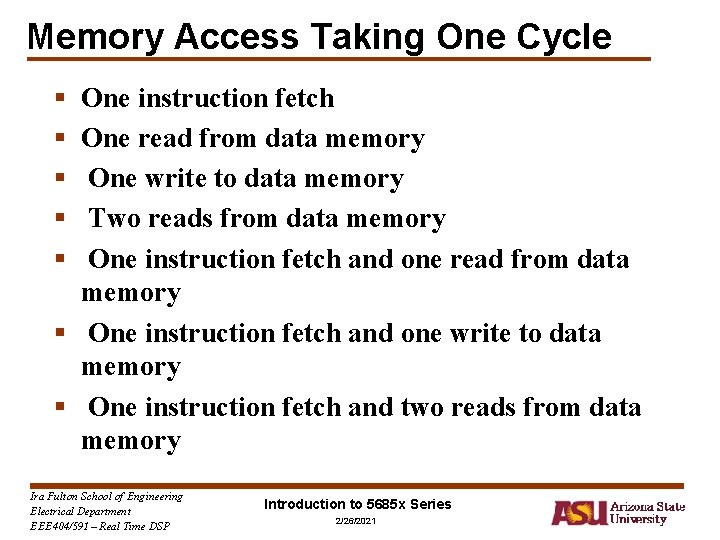

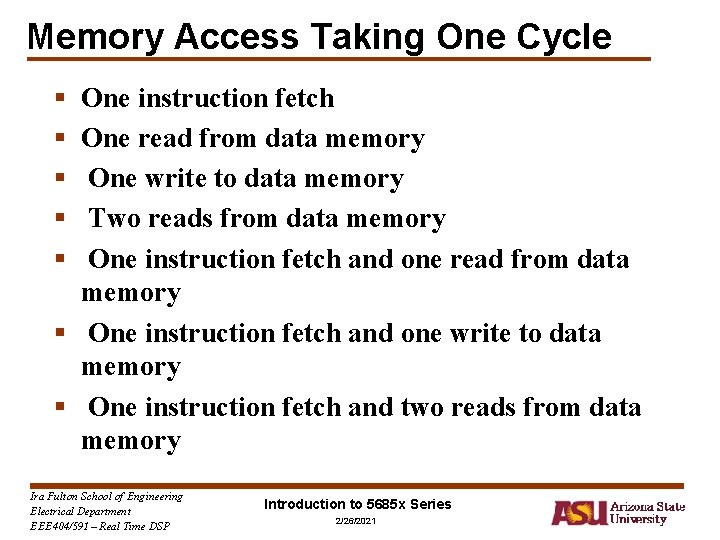

Memory Access Taking One Cycle § § § One instruction fetch One read from data memory One write to data memory Two reads from data memory One instruction fetch and one read from data memory § One instruction fetch and one write to data memory § One instruction fetch and two reads from data memory Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

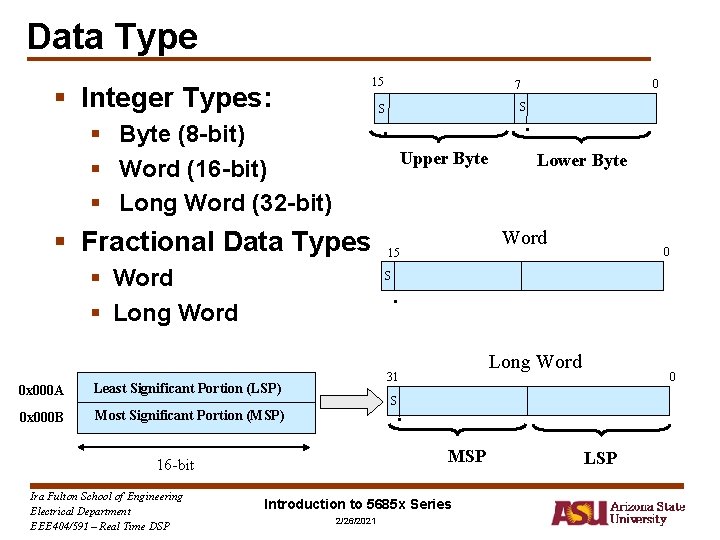

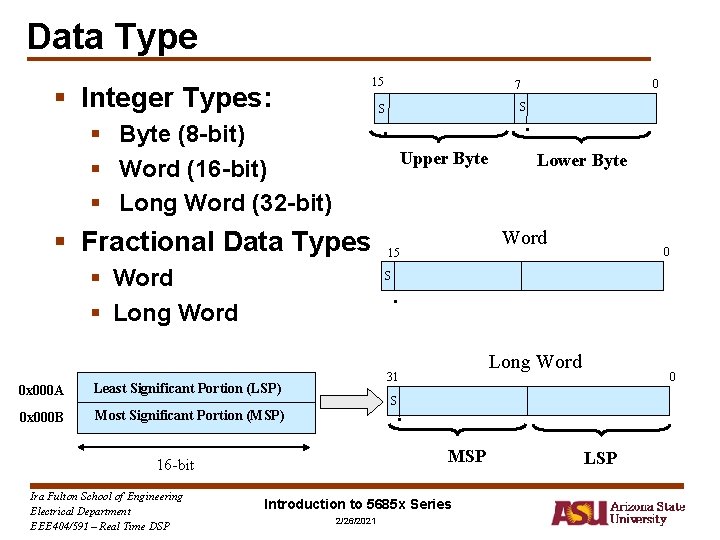

Data Type 15 § Integer Types: . . Upper Byte § Fractional Data Types § Word § Long Word Lower Byte Word 15 0 S . 0 x 000 A Least Significant Portion (LSP) 0 x 000 B Most Significant Portion (MSP) Long Word 31 0 S . MSP 16 -bit Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP S S § Byte (8 -bit) § Word (16 -bit) § Long Word (32 -bit) 0 7 Introduction to 5685 x Series 2/26/2021 LSP

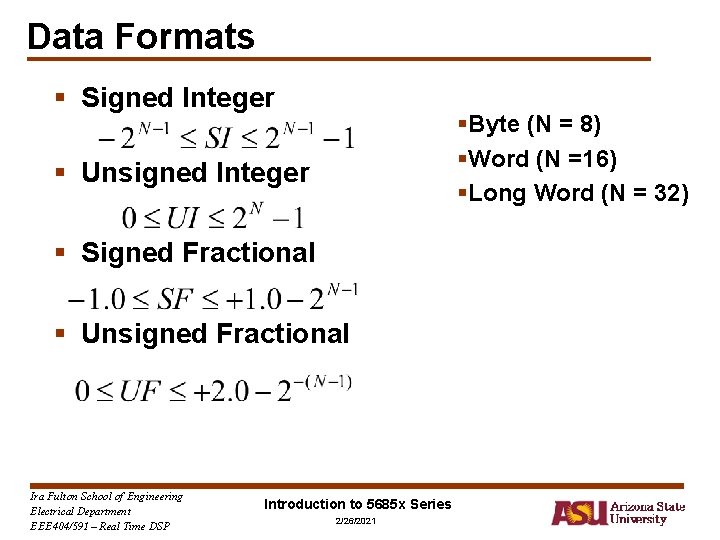

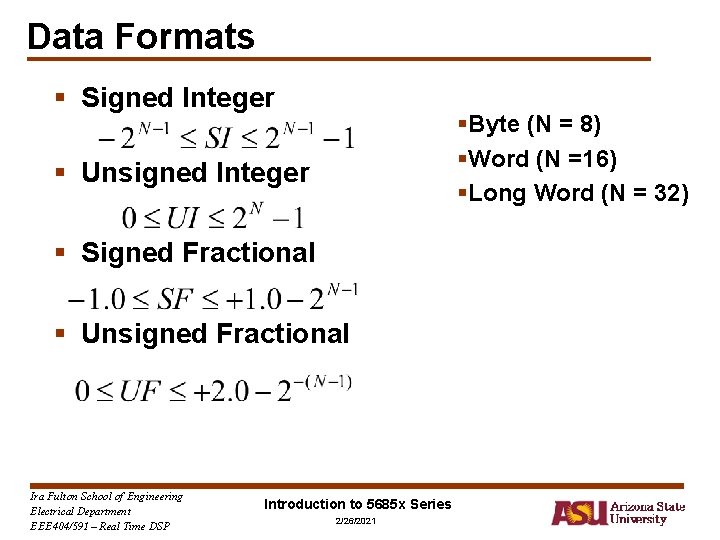

Data Formats § Signed Integer §Byte (N = 8) §Word (N =16) §Long Word (N = 32) § Unsigned Integer § Signed Fractional § Unsigned Fractional Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

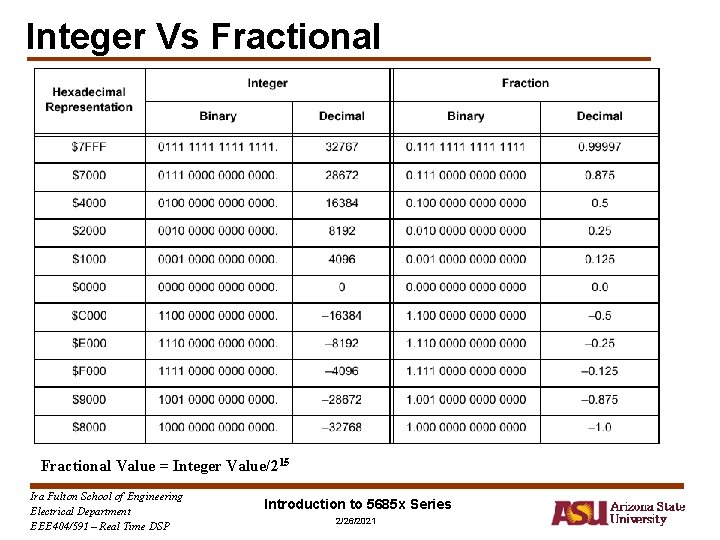

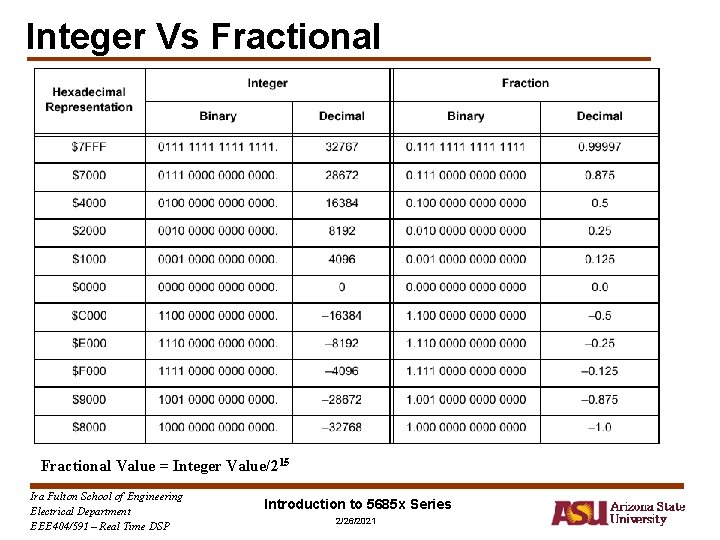

Integer Vs Fractional Value = Integer Value/215 Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

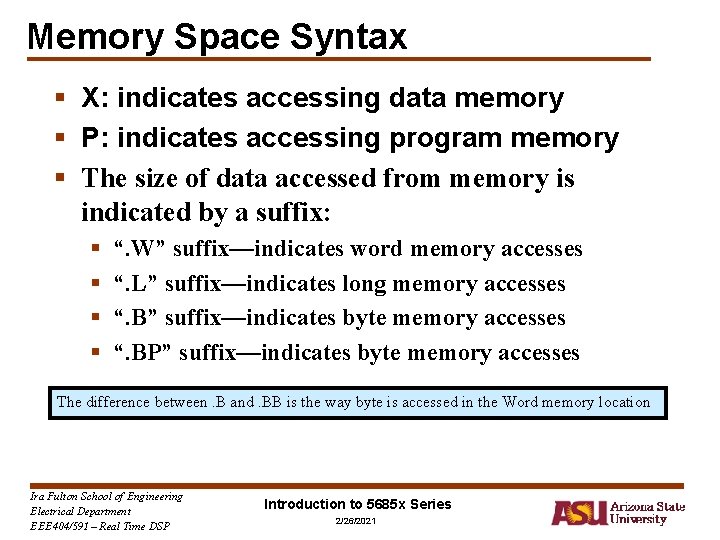

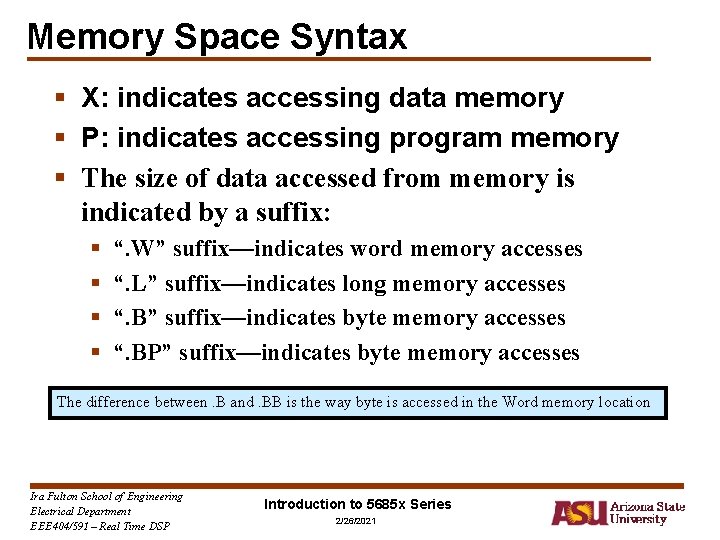

Memory Space Syntax § X: indicates accessing data memory § P: indicates accessing program memory § The size of data accessed from memory is indicated by a suffix: § § “. W” suffix—indicates word memory accesses “. L” suffix—indicates long memory accesses “. B” suffix—indicates byte memory accesses “. BP” suffix—indicates byte memory accesses The difference between. B and. BB is the way byte is accessed in the Word memory location Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

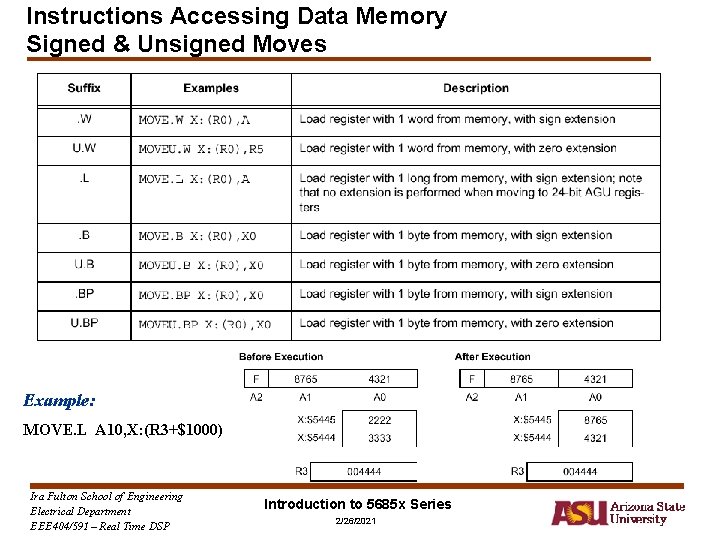

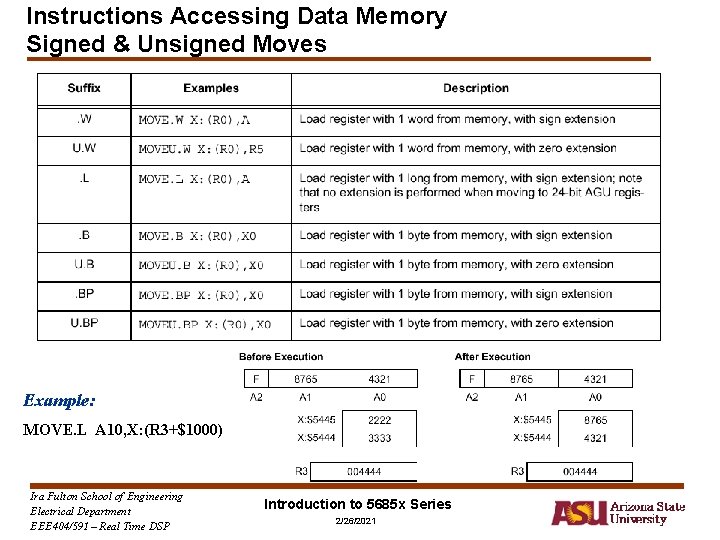

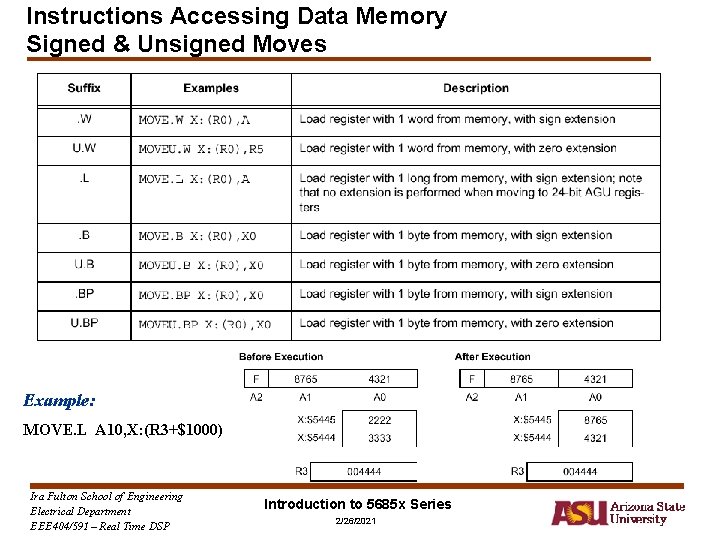

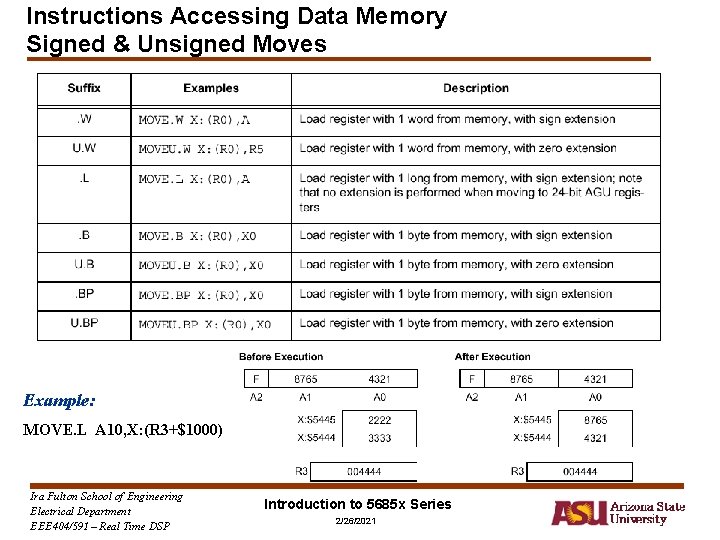

Instructions Accessing Data Memory Signed & Unsigned Moves Example: MOVE. L A 10, X: (R 3+$1000) Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Addressing Modes - Summary § § § Immediate Absolute Direct Indexed Circular Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Addressing Modes § Immediate § Value of operand (data) specified directly in instruction. § Examples: MOVE. W #$4301, A ; Load accumulator A with 31 MOVE. W #4301, A; Load accumulator A with 4301 MOVE. W #%1010, A; Load accumulator A with 16 -bit binary $000 A. § Absolute § Address of operand specified directly in instruction § MOVE. W X: $FF 22, A; Load A with number stored in address $FF 22 of memory “X”. § Register-Direct § Example: MOVE R 1, A; Operands are internal registers (i. e: R 1, A) § Data stored in registers § Register-Indirect Addressing or Indirect Addressing: § Register contains address of (points to) memory location in which data is stored § Example: MOVE. W X: (R 1), A § Indexed Addressing § Similar to indirect addressing but pointer incremented by an offset before accessing memory. Example: MOVE. W X: (R 1 + 5), A Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Circular Address § Normal buffer except when reaching the end, it loops back to the starting point § Define buffer size Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

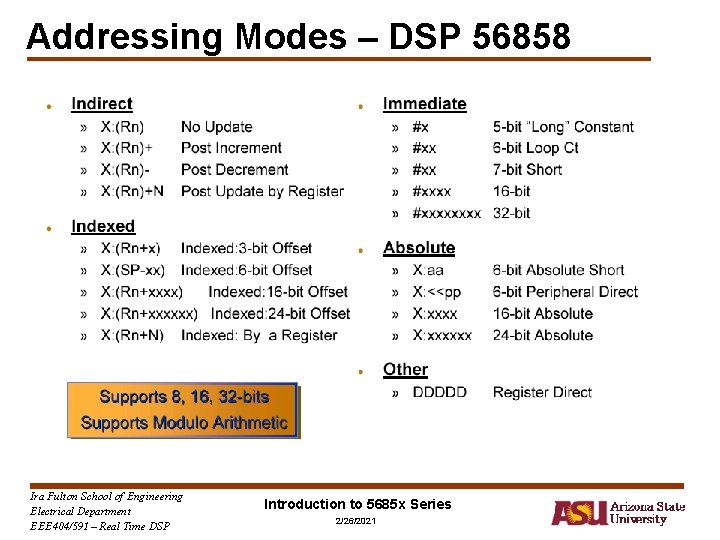

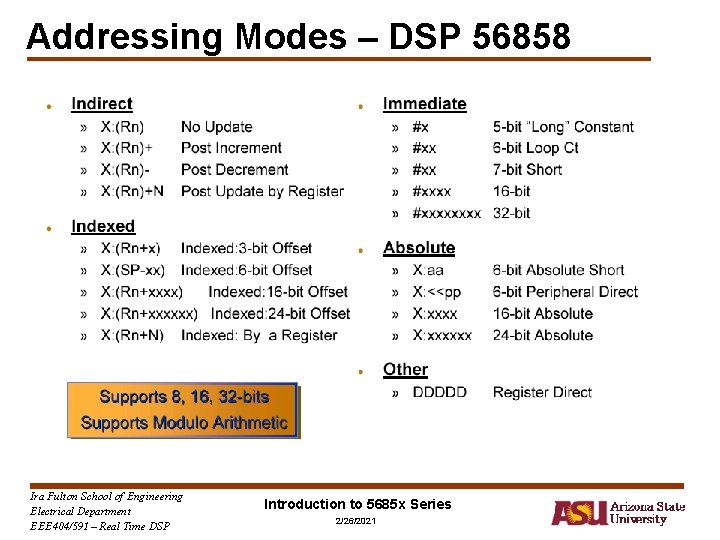

Addressing Modes – DSP 56858 Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

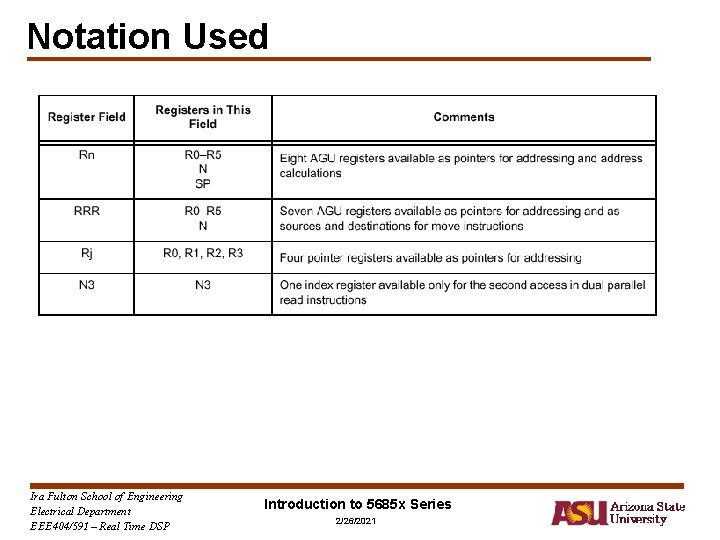

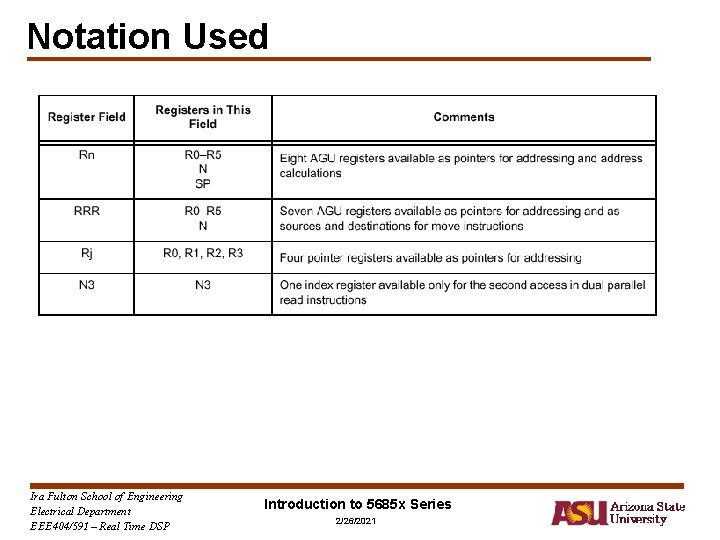

Notation Used Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

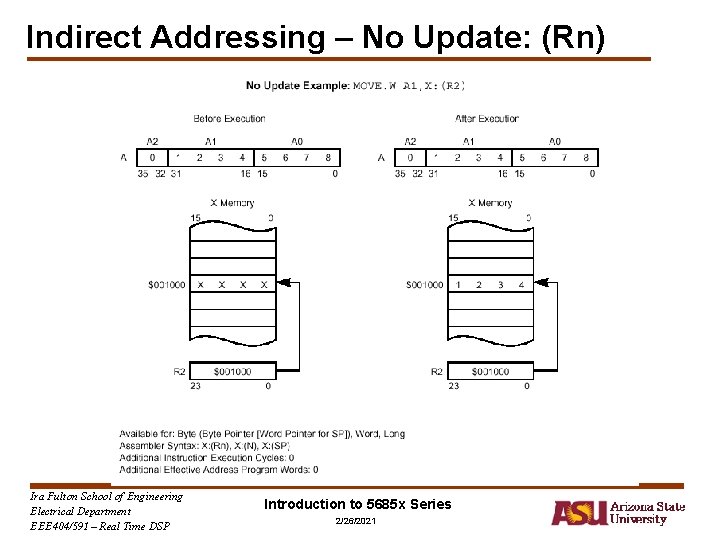

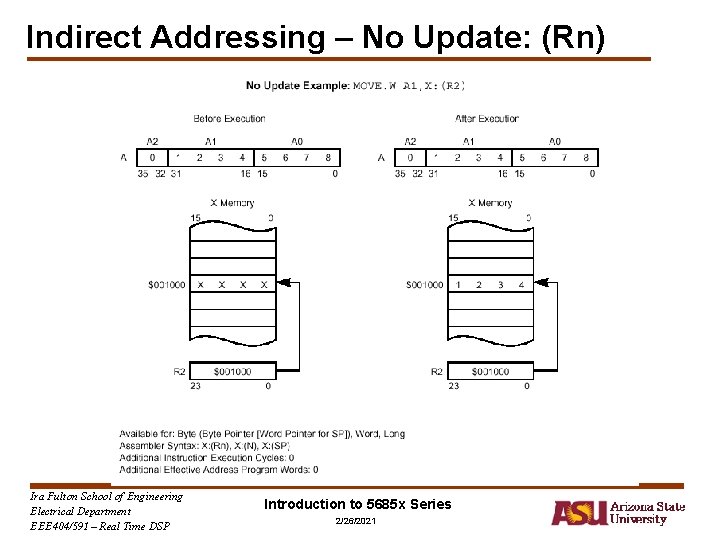

Indirect Addressing – No Update: (Rn) Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

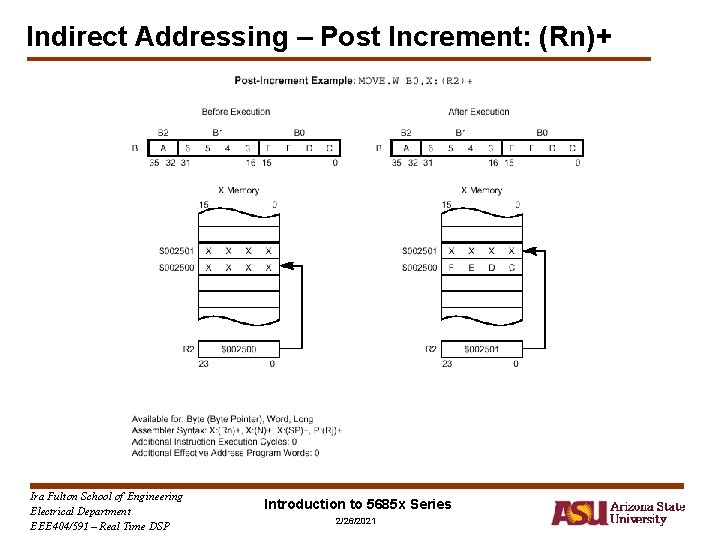

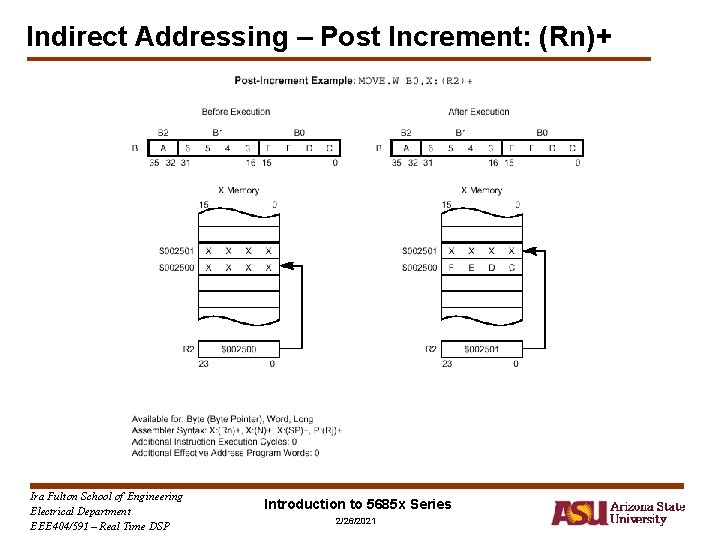

Indirect Addressing – Post Increment: (Rn)+ Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

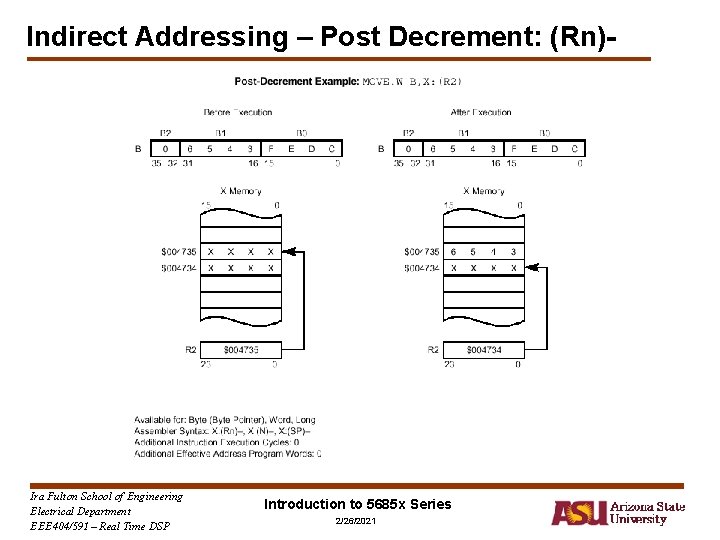

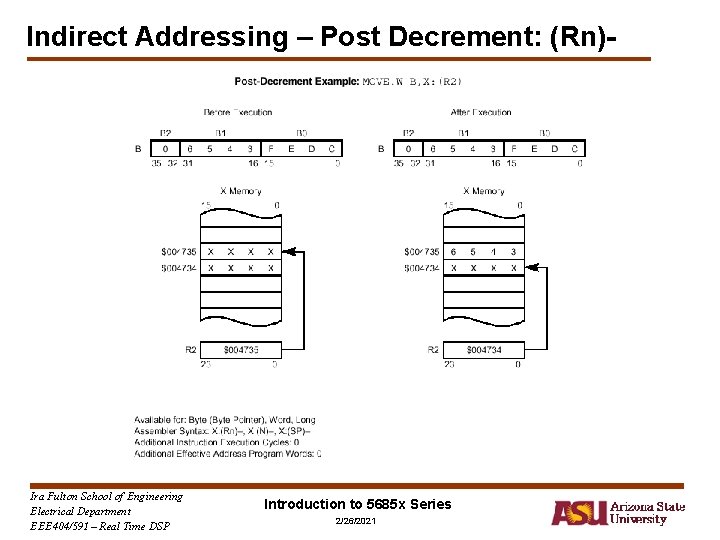

Indirect Addressing – Post Decrement: (Rn)- Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

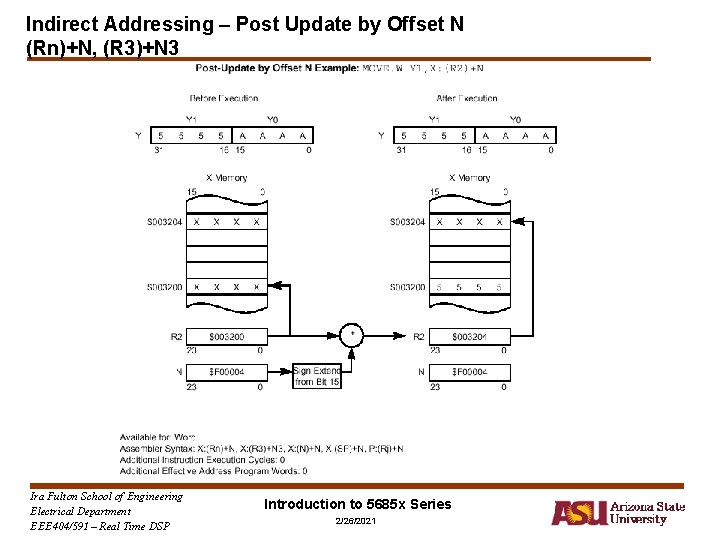

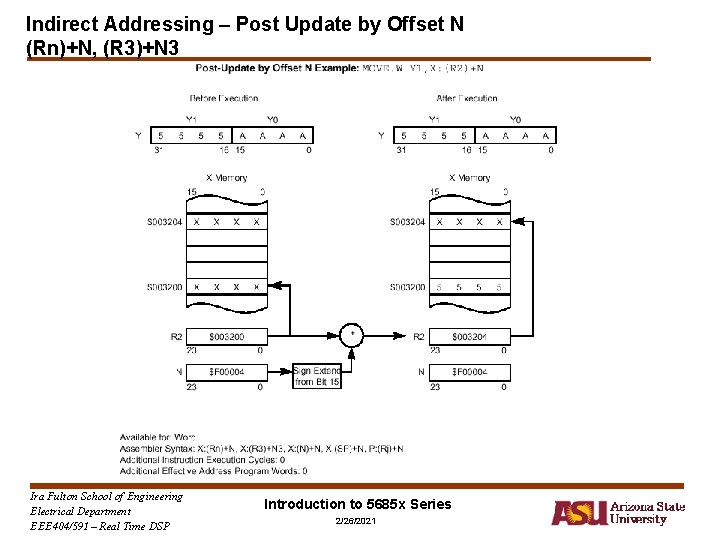

Indirect Addressing – Post Update by Offset N (Rn)+N, (R 3)+N 3 Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

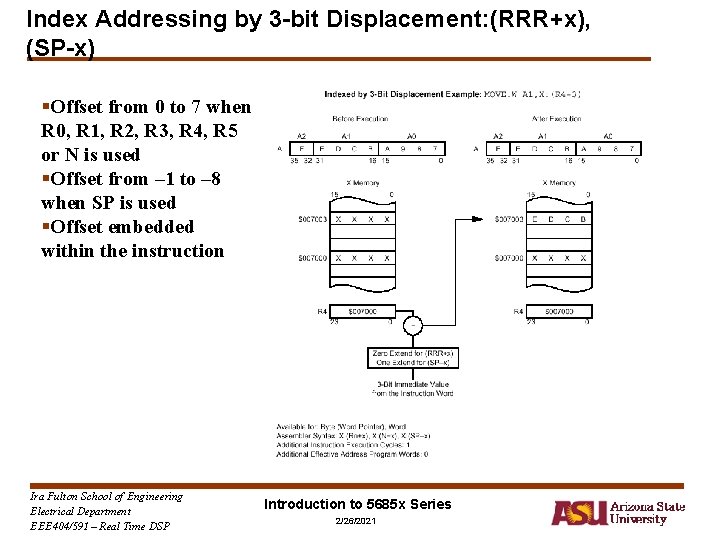

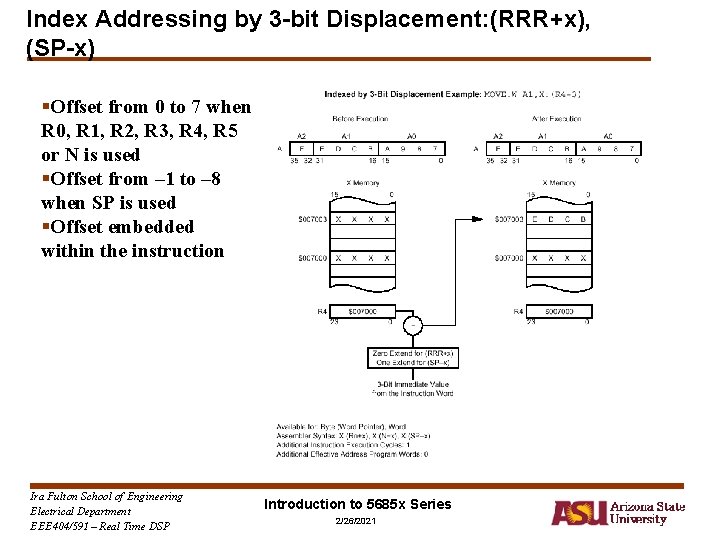

Index Addressing by 3 -bit Displacement: (RRR+x), (SP-x) §Offset from 0 to 7 when R 0, R 1, R 2, R 3, R 4, R 5 or N is used §Offset from – 1 to – 8 when SP is used §Offset embedded within the instruction Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

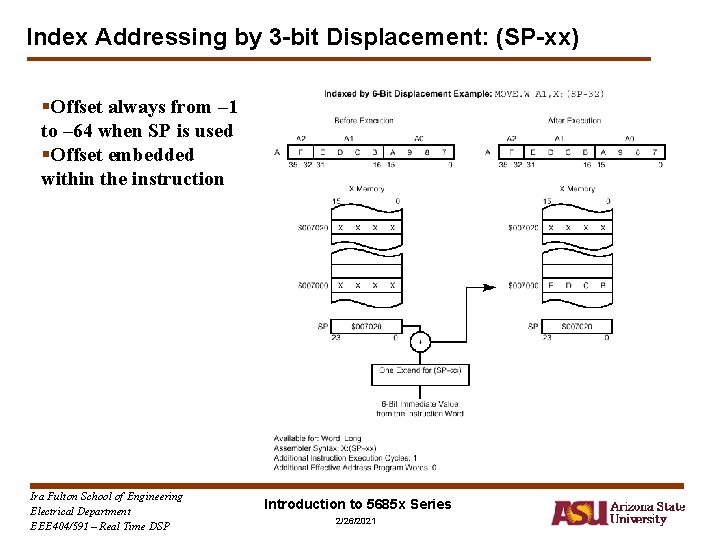

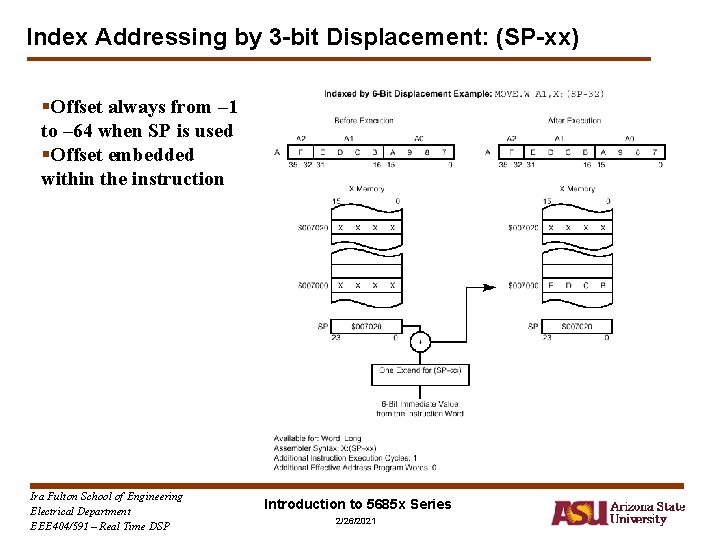

Index Addressing by 3 -bit Displacement: (SP-xx) §Offset always from – 1 to – 64 when SP is used §Offset embedded within the instruction Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

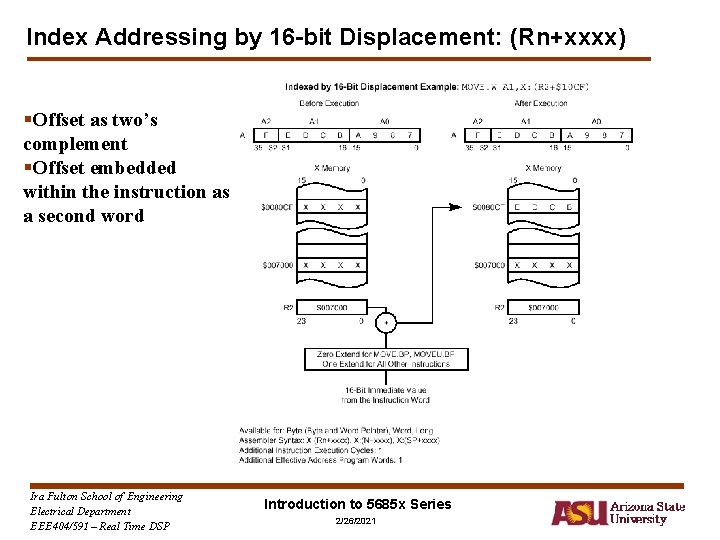

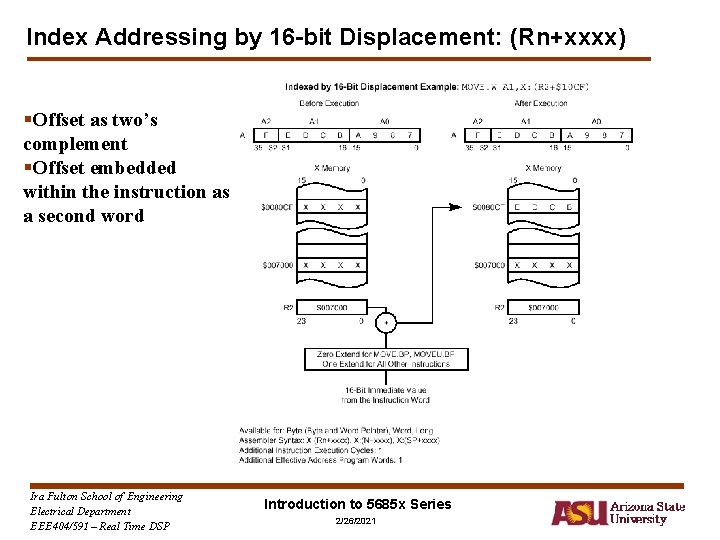

Index Addressing by 16 -bit Displacement: (Rn+xxxx) §Offset as two’s complement §Offset embedded within the instruction as a second word Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

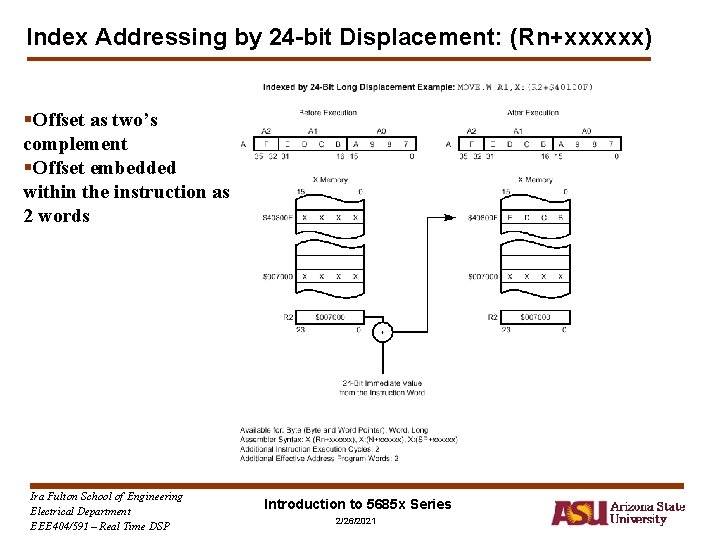

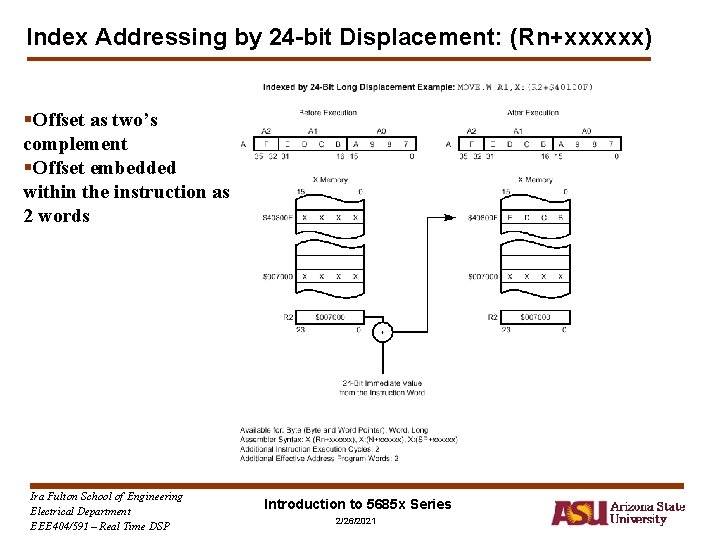

Index Addressing by 24 -bit Displacement: (Rn+xxxxxx) §Offset as two’s complement §Offset embedded within the instruction as 2 words Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Instructions Accessing Data Memory Signed & Unsigned Moves Example: MOVE. L A 10, X: (R 3+$1000) Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

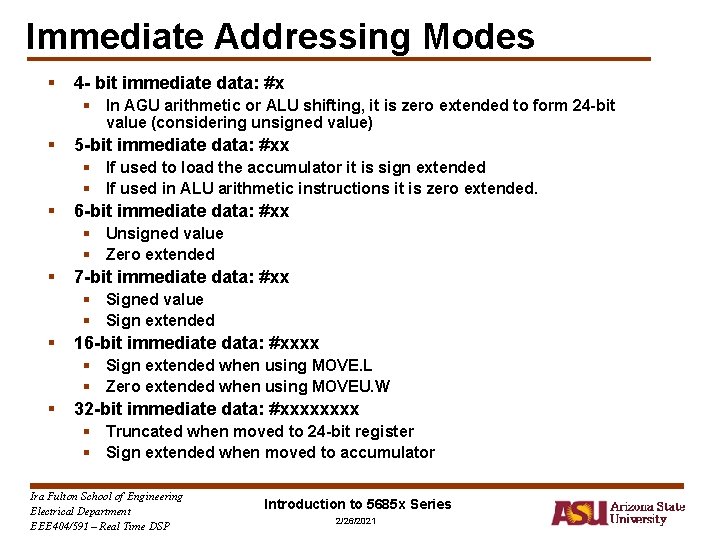

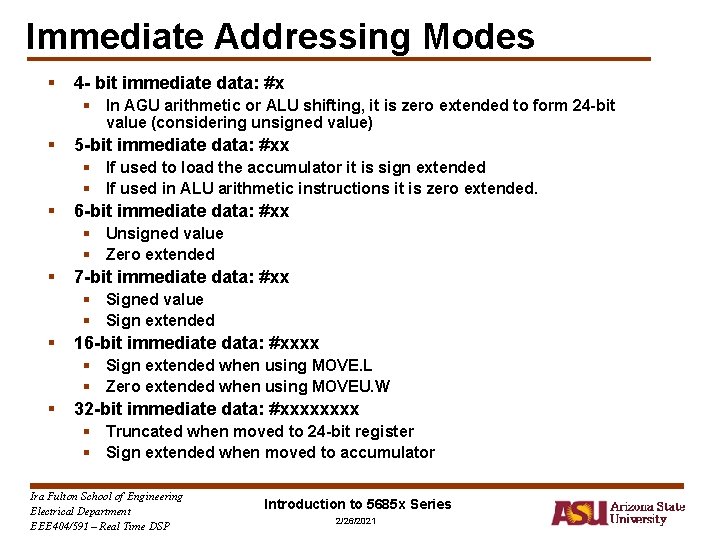

Immediate Addressing Modes § 4 - bit immediate data: #x § In AGU arithmetic or ALU shifting, it is zero extended to form 24 -bit value (considering unsigned value) § 5 -bit immediate data: #xx § If used to load the accumulator it is sign extended § If used in ALU arithmetic instructions it is zero extended. § 6 -bit immediate data: #xx § Unsigned value § Zero extended § 7 -bit immediate data: #xx § Signed value § Sign extended § 16 -bit immediate data: #xxxx § Sign extended when using MOVE. L § Zero extended when using MOVEU. W § 32 -bit immediate data: #xxxx § Truncated when moved to 24 -bit register § Sign extended when moved to accumulator Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

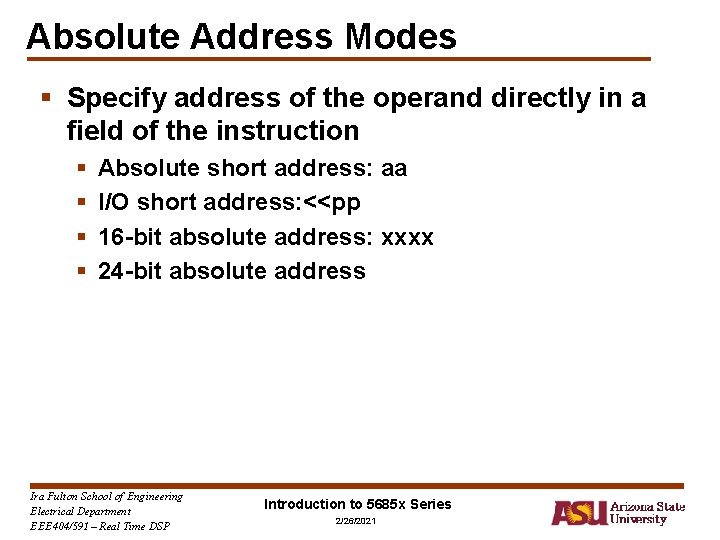

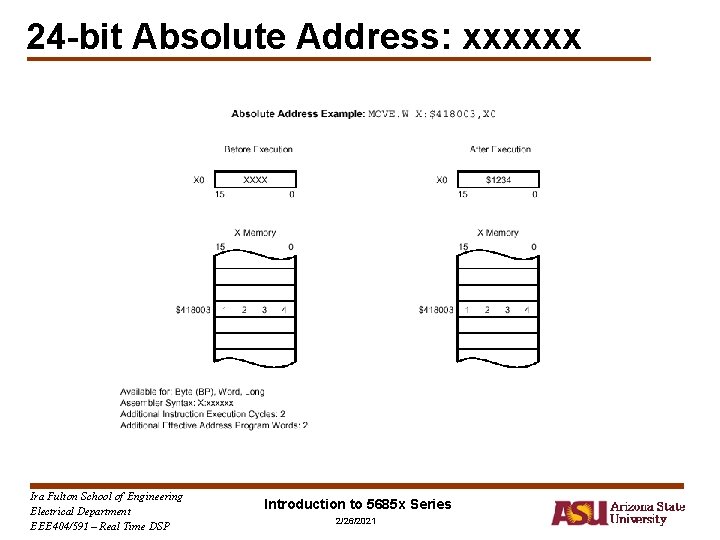

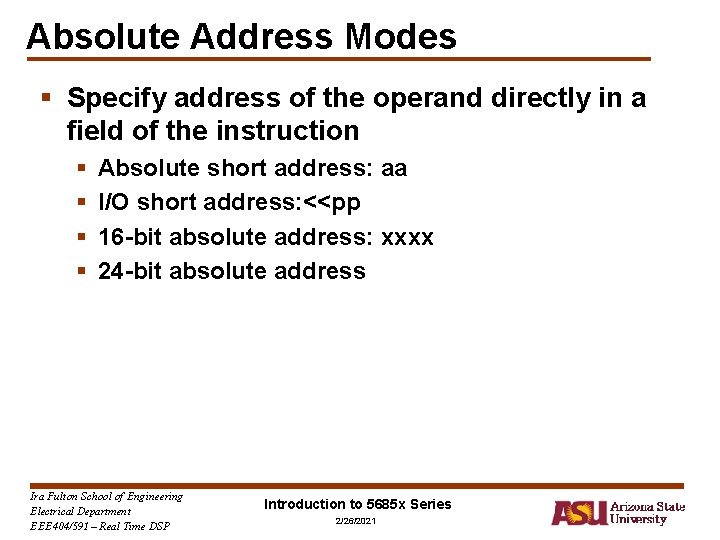

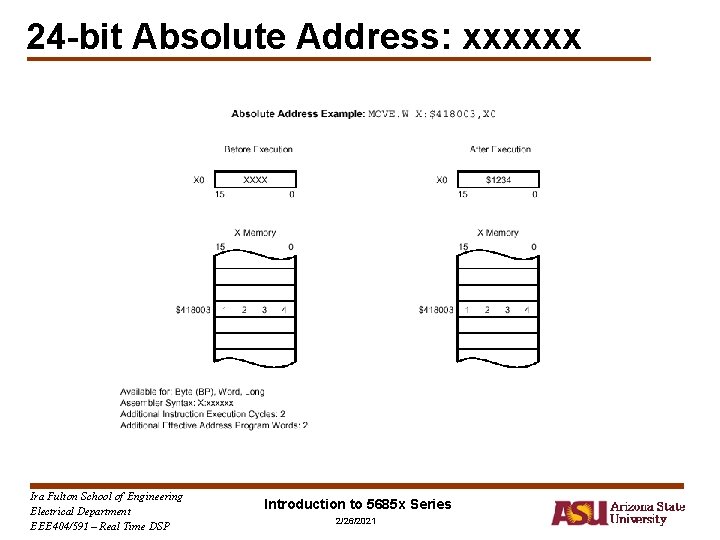

Absolute Address Modes § Specify address of the operand directly in a field of the instruction § § Absolute short address: aa I/O short address: <<pp 16 -bit absolute address: xxxx 24 -bit absolute address Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

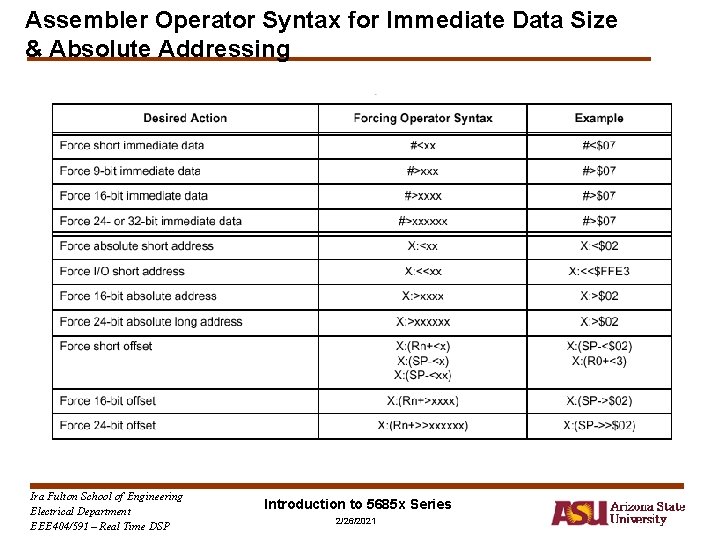

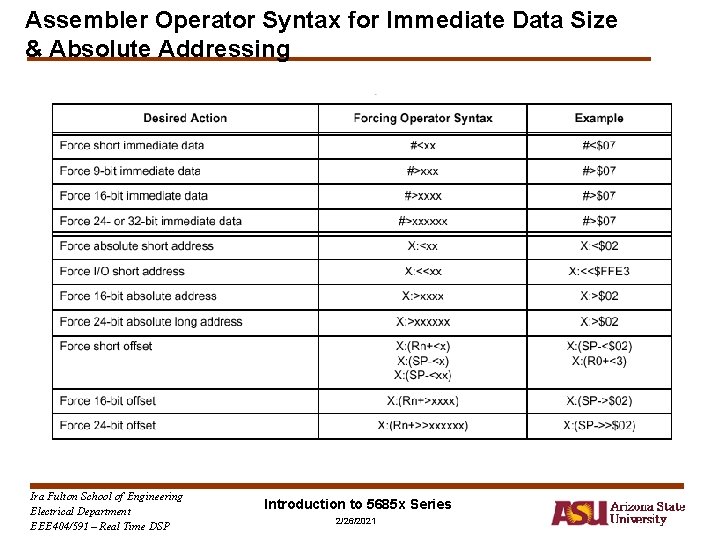

Assembler Operator Syntax for Immediate Data Size & Absolute Addressing Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

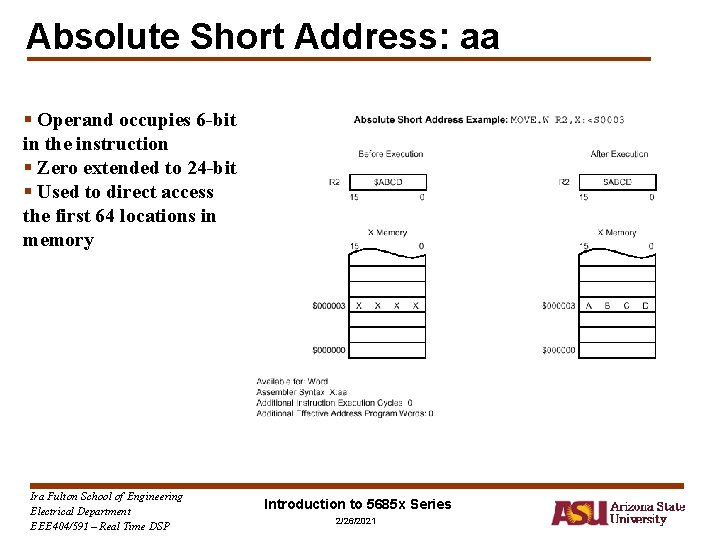

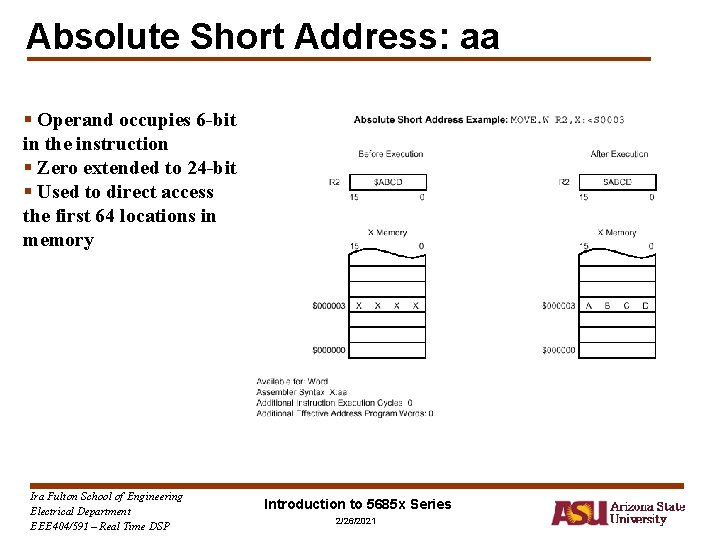

Absolute Short Address: aa § Operand occupies 6 -bit in the instruction § Zero extended to 24 -bit § Used to direct access the first 64 locations in memory Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

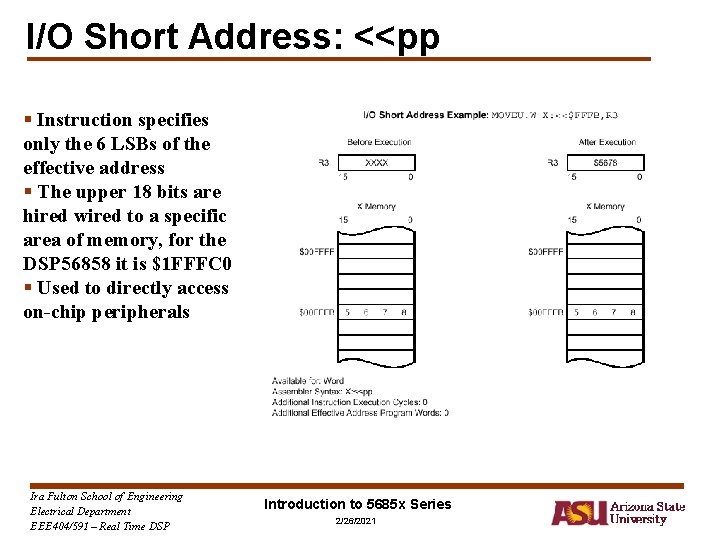

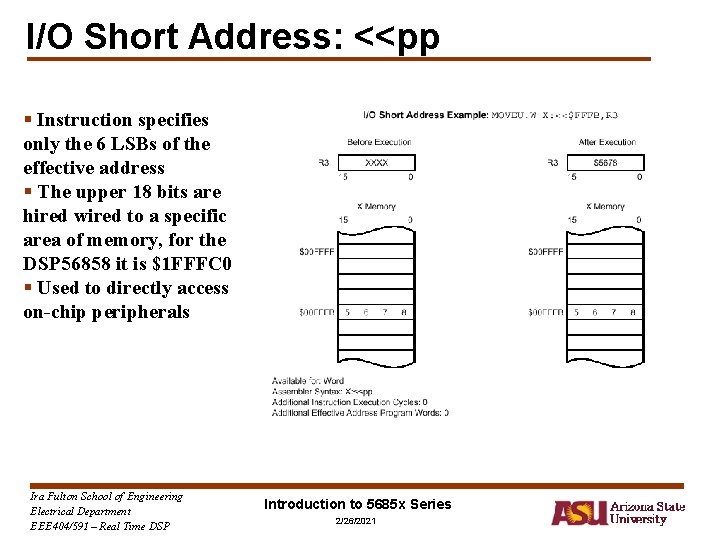

I/O Short Address: <<pp § Instruction specifies only the 6 LSBs of the effective address § The upper 18 bits are hired wired to a specific area of memory, for the DSP 56858 it is $1 FFFC 0 § Used to directly access on-chip peripherals Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

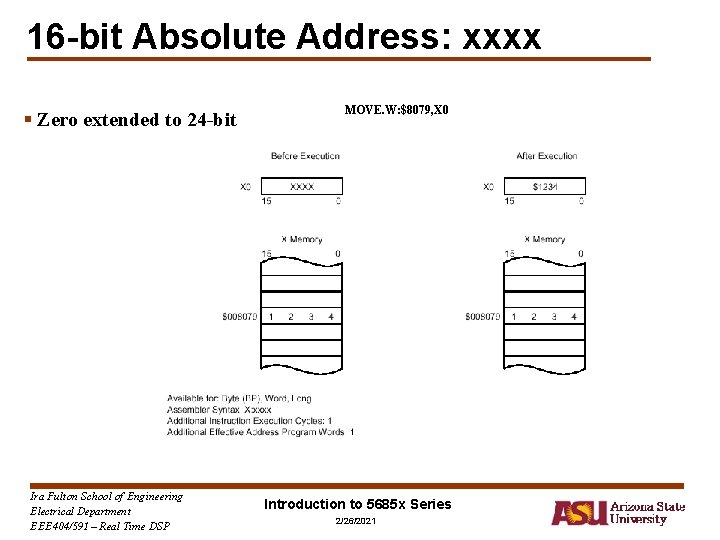

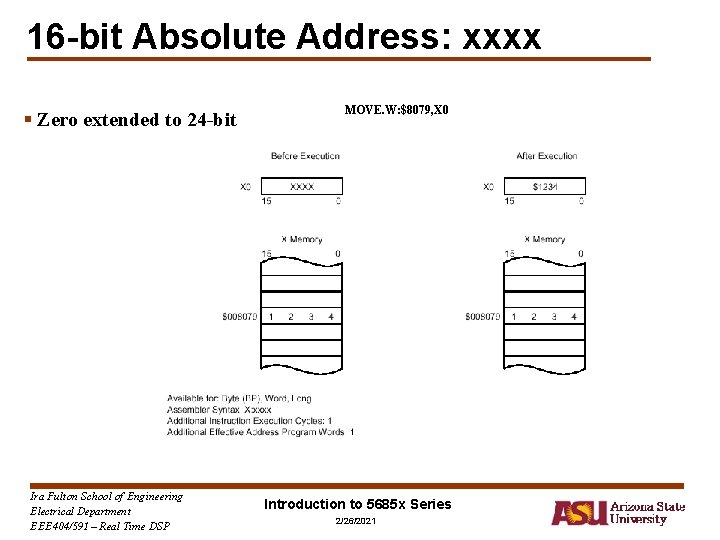

16 -bit Absolute Address: xxxx § Zero extended to 24 -bit Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP MOVE. W: $8079, X 0 Introduction to 5685 x Series 2/26/2021

24 -bit Absolute Address: xxxxxx Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Register Direct Mode § At least one of the operand is either in AGU, ALU, or control registers. § Example: § MOVE. W Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP R 0, X 0 Introduction to 5685 x Series 2/26/2021

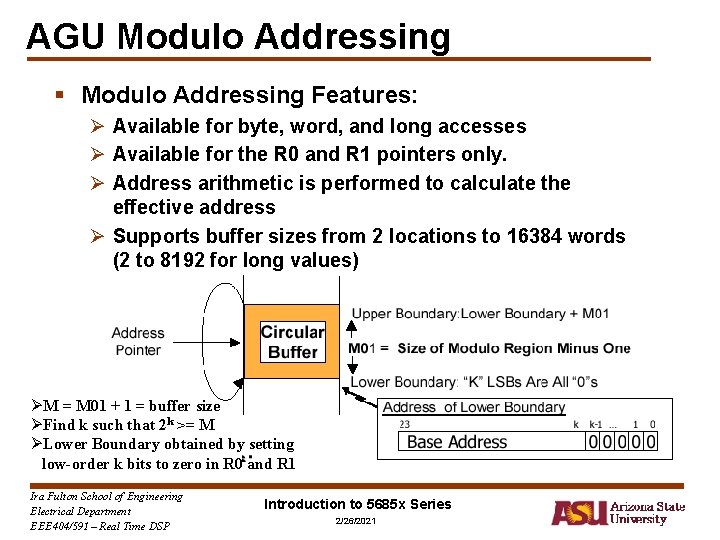

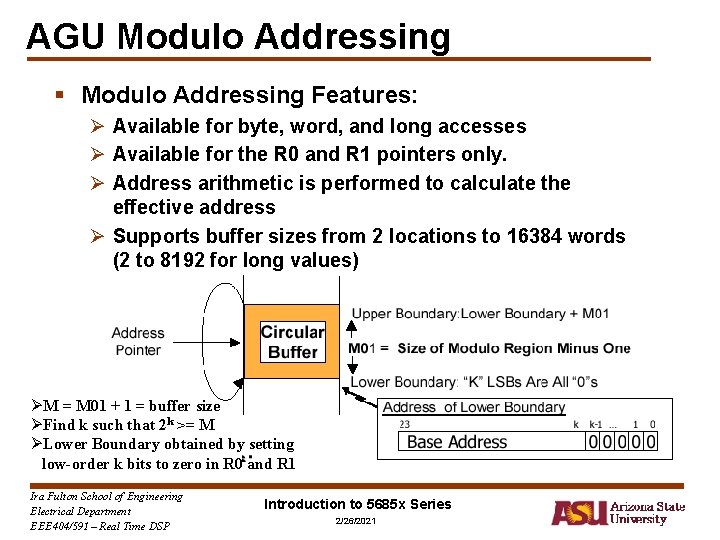

AGU Modulo Addressing § Modulo Addressing Features: Ø Available for byte, word, and long accesses Ø Available for the R 0 and R 1 pointers only. Ø Address arithmetic is performed to calculate the effective address Ø Supports buffer sizes from 2 locations to 16384 words (2 to 8192 for long values) ØM = M 01 + 1 = buffer size ØFind k such that 2 k >= M ØLower Boundary obtained by setting low-order k bits to zero in R 0 and R 1 Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

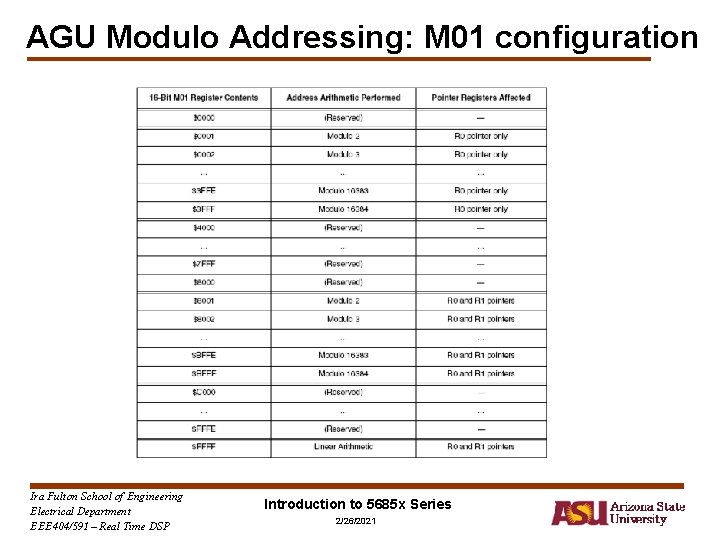

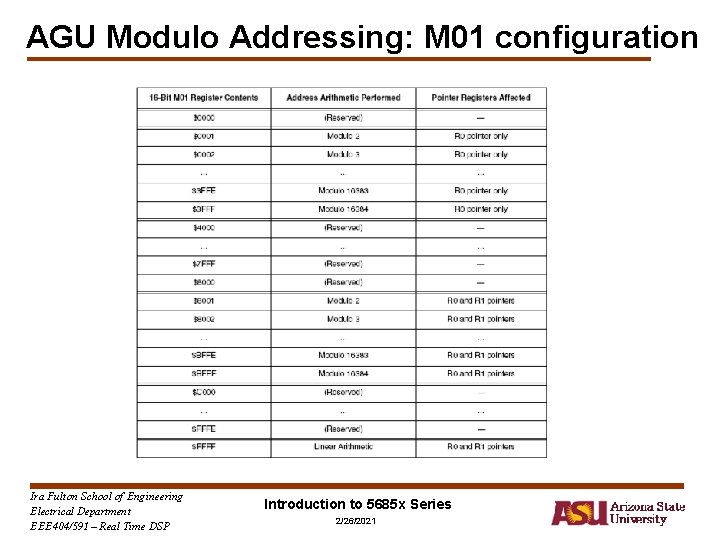

AGU Modulo Addressing: M 01 configuration Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

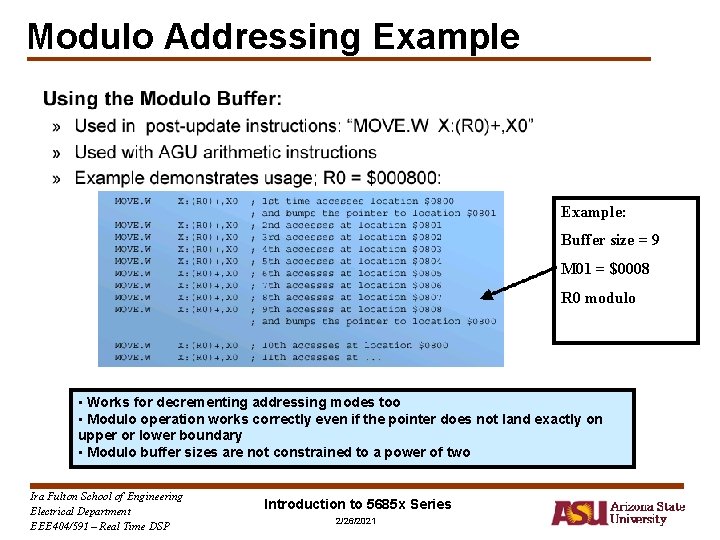

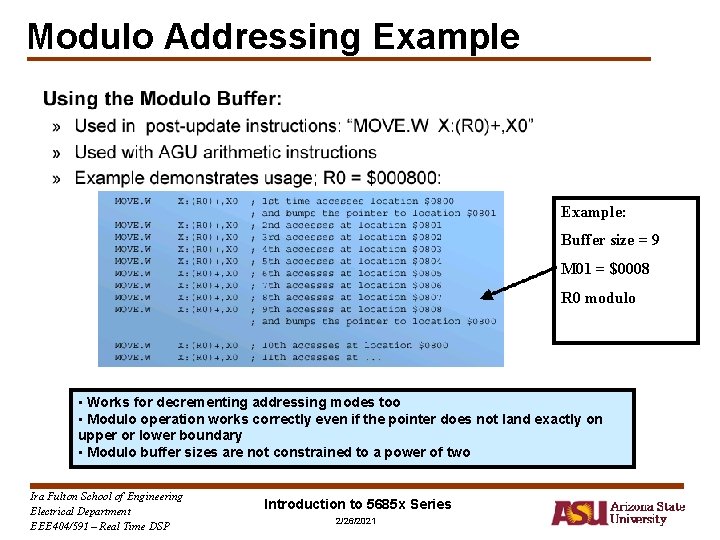

Modulo Addressing Example: Buffer size = 9 M 01 = $0008 R 0 modulo • Works for decrementing addressing modes too • Modulo operation works correctly even if the pointer does not land exactly on upper or lower boundary • Modulo buffer sizes are not constrained to a power of two Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Byte & Word Addressing § Word addressing can be used to access § Byte § Word § Long Word § Byte addressing can be used to access bytes only Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Byte Pointers Vs Word Pointers § Word pointers can be used to access a data element of any size, so they should be used when mixed data is accessed (such as in data structures) § Disadvantage: Word pointer in a post-update addressing mode may result in skipping some bytes that cannot be accessed. § Using byte pointers fixes this problem. Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

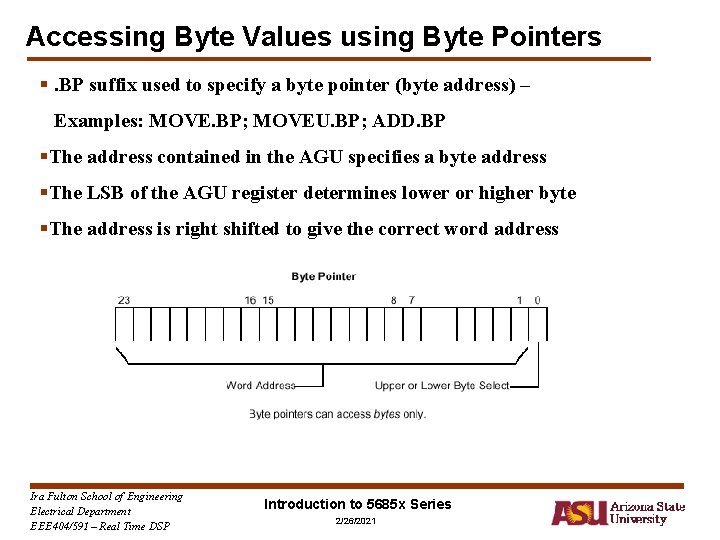

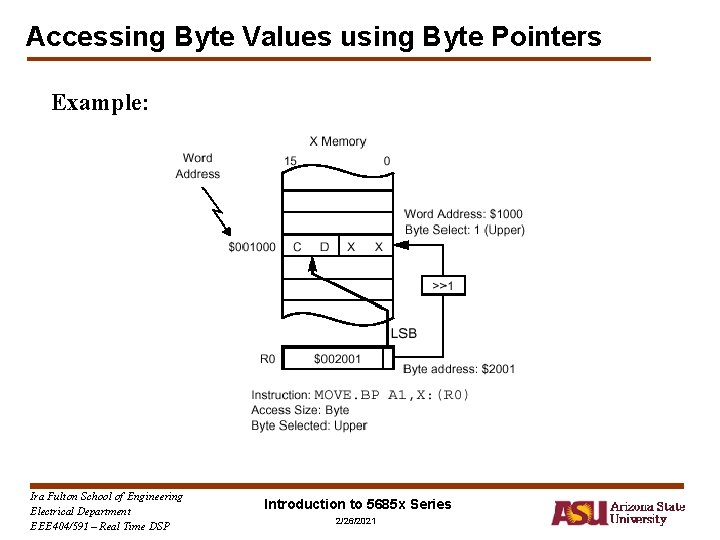

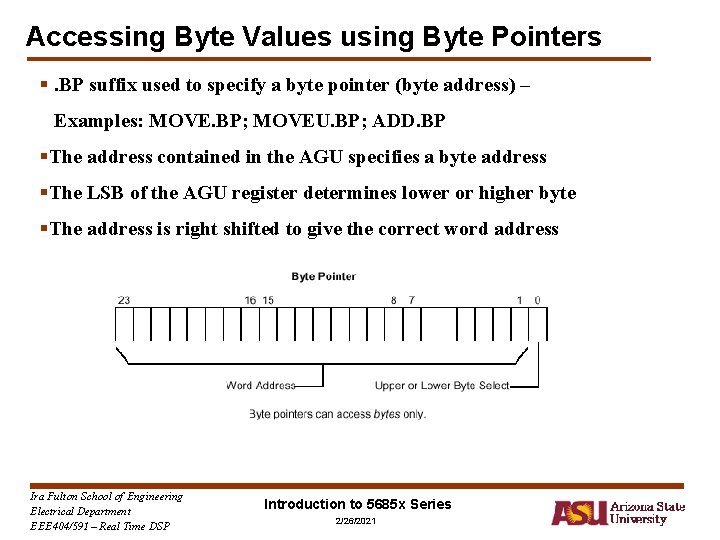

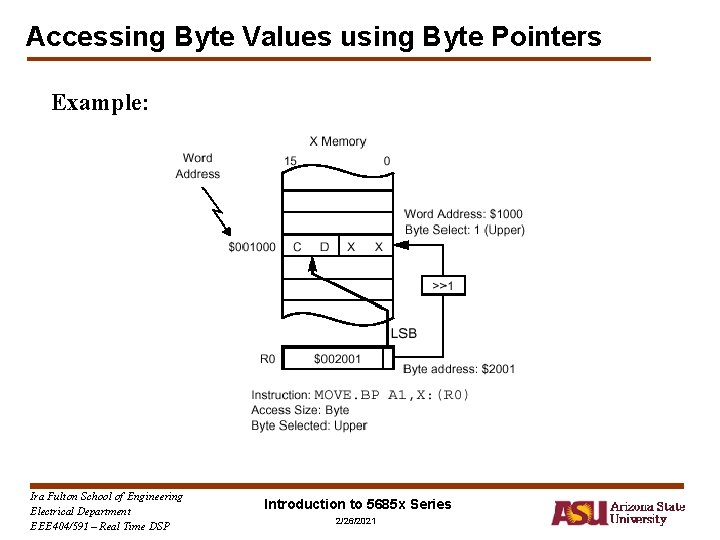

Accessing Byte Values using Byte Pointers §. BP suffix used to specify a byte pointer (byte address) – Examples: MOVE. BP; MOVEU. BP; ADD. BP §The address contained in the AGU specifies a byte address §The LSB of the AGU register determines lower or higher byte §The address is right shifted to give the correct word address Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Accessing Byte Values using Byte Pointers Example: Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

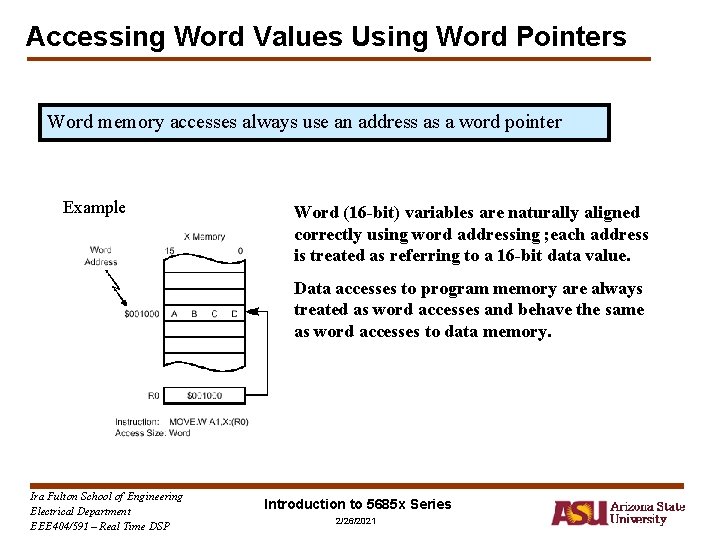

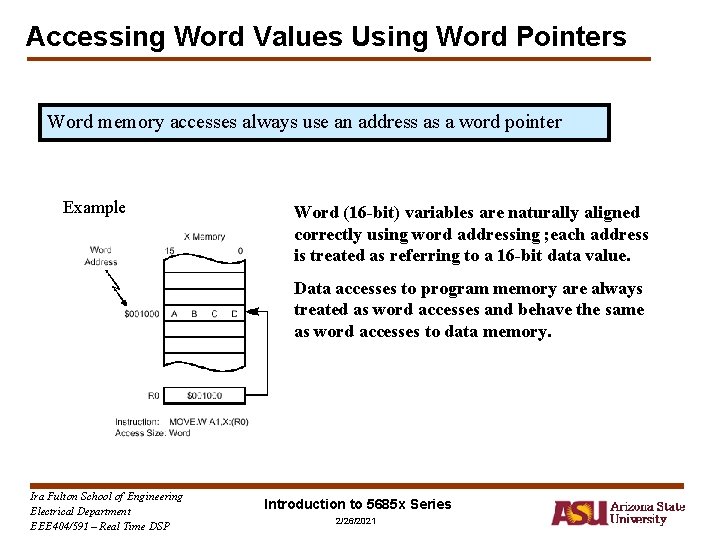

Accessing Word Values Using Word Pointers Word memory accesses always use an address as a word pointer Example Word (16 -bit) variables are naturally aligned correctly using word addressing ; each address is treated as referring to a 16 -bit data value. Data accesses to program memory are always treated as word accesses and behave the same as word accesses to data memory. Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

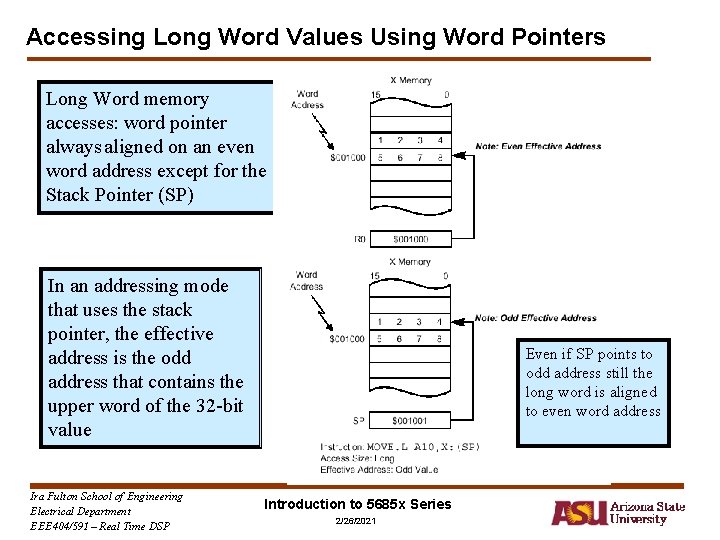

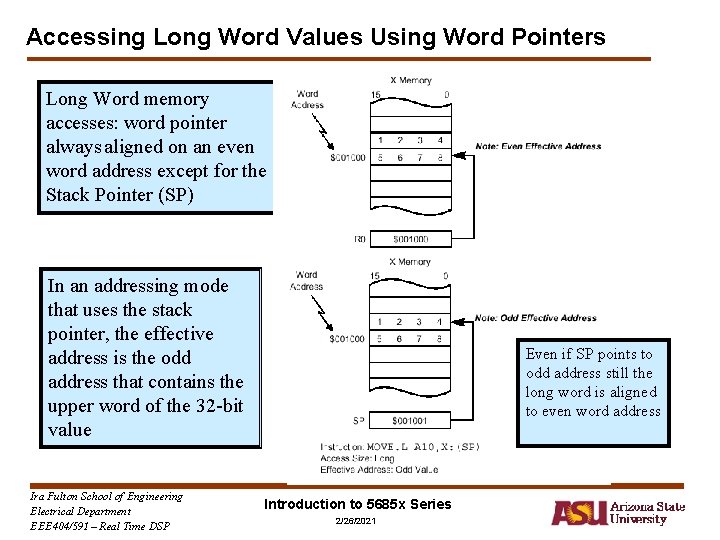

Accessing Long Word Values Using Word Pointers Long Word memory accesses: word pointer always aligned on an even word address except for the Stack Pointer (SP) In an addressing mode that uses the stack pointer, the effective address is the odd address that contains the upper word of the 32 -bit value Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Even if SP points to odd address still the long word is aligned to even word address Introduction to 5685 x Series 2/26/2021

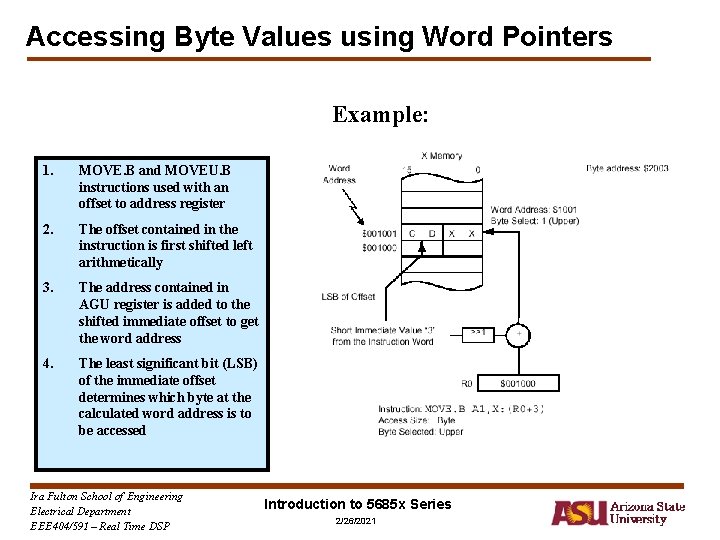

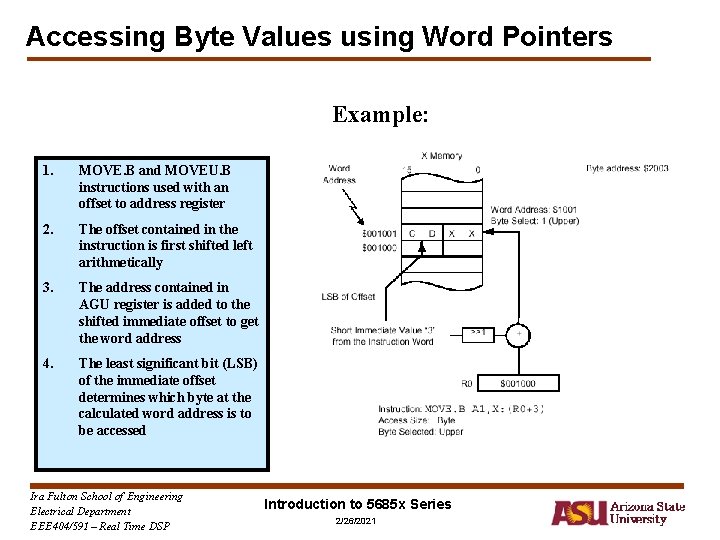

Accessing Byte Values using Word Pointers Example: 1. MOVE. B and MOVEU. B instructions used with an offset to address register 2. The offset contained in the instruction is first shifted left arithmetically 3. The address contained in AGU register is added to the shifted immediate offset to get the word address 4. The least significant bit (LSB) of the immediate offset determines which byte at the calculated word address is to be accessed Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

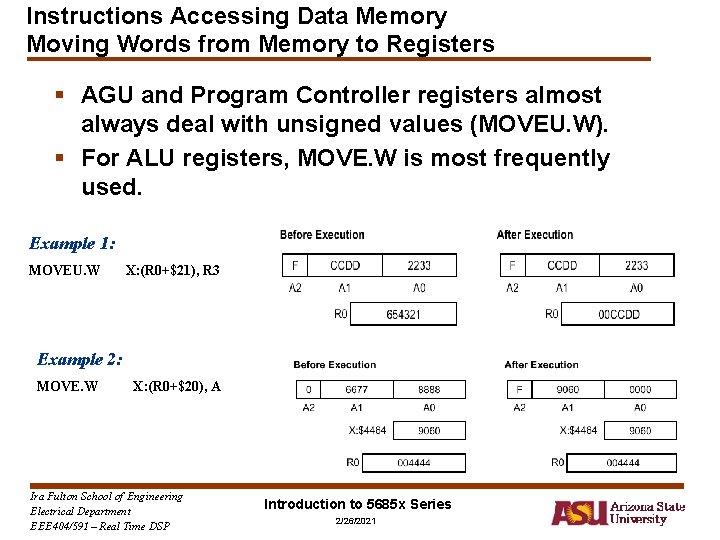

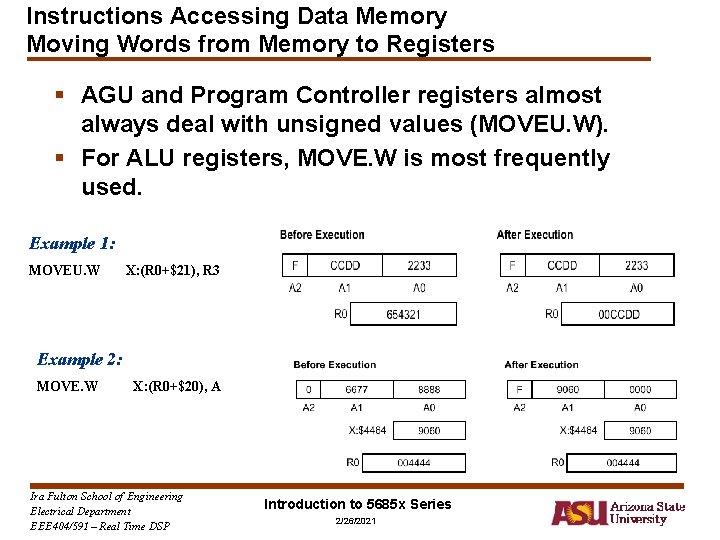

Instructions Accessing Data Memory Moving Words from Memory to Registers § AGU and Program Controller registers almost always deal with unsigned values (MOVEU. W). § For ALU registers, MOVE. W is most frequently used. Example 1: MOVEU. W X: (R 0+$21), R 3 Example 2: MOVE. W X: (R 0+$20), A Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Instructions Accessing Program Memory § Data size accessed from program memory is always 16 -bit. §. W suffix used in all times. § Rules are the same as the ones for accessing data memory § Examples: § MOVE. W P: (R 0)+, X 0 ; Read 16 -bit signed word from program memory § MOVEU. W P: (R 0)+, R 3 ; Read 16 -bit unsigned word from program memory § MOVE. W R 2, P: (R 0)+ ; Write 16 -bit word to program memory Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Instructions with Operand in Data Memory § Operand located in data memory. § Example: ADD. W X: $4000, A § Steps involved § Move operand from memory location to temporary register inside ALU § Add that to Accumulator A § Store result back in A Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

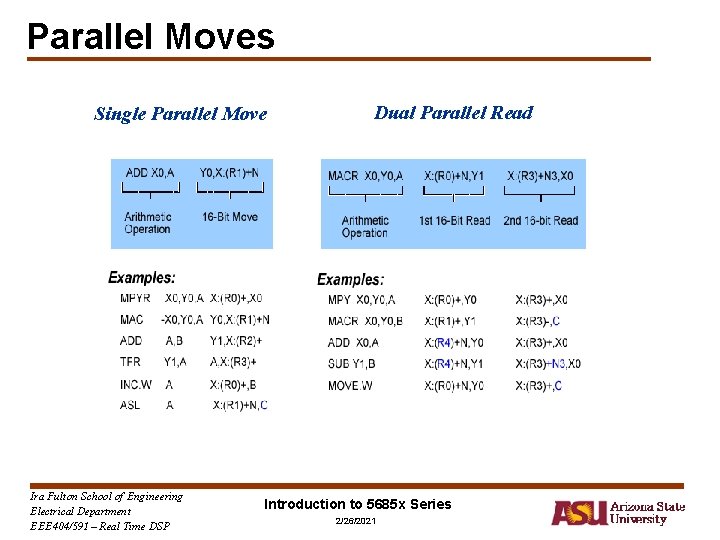

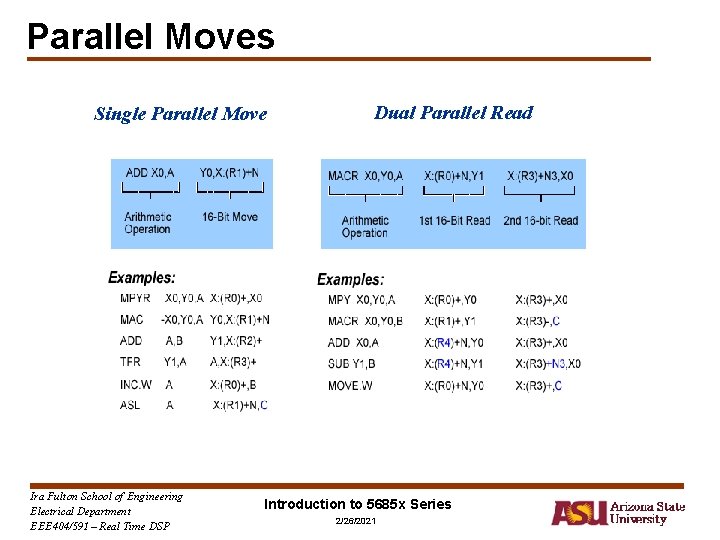

Parallel Moves § Two Types: § Single parallel move § Dual parallel read § One or two word-size moves occur in parallel with an arithmetic operation § One write (single parallel move) § One read (single parallel move) § Two read operations (dual parallel move) § Both allow execution using a single instruction and in one instruction cycle. § Restricted to arithmetic operations in the ALU. Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Parallel Moves Single Parallel Move Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Dual Parallel Read Introduction to 5685 x Series 2/26/2021

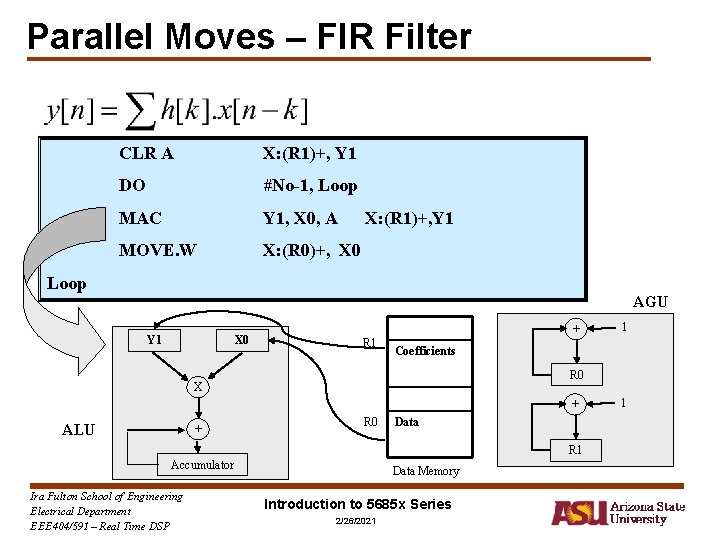

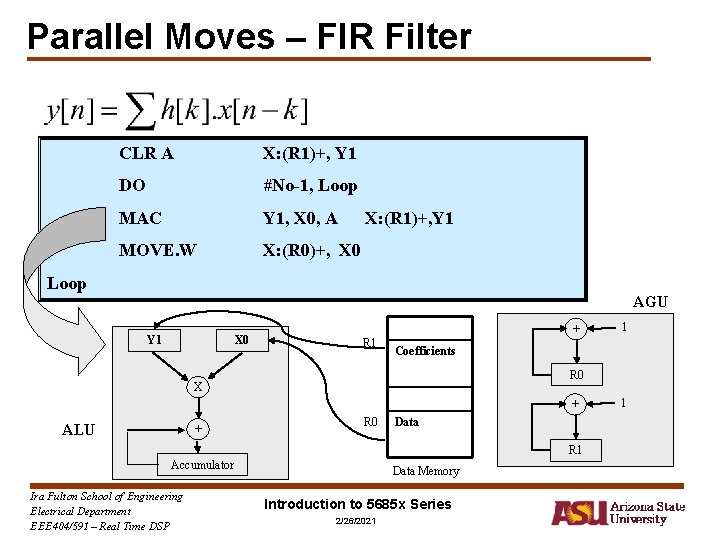

Parallel Moves – FIR Filter CLR A X: (R 1)+, Y 1 DO #No-1, Loop MAC Y 1, X 0, A MOVE. W X: (R 0)+, X 0 X: (R 1)+, Y 1 Loop AGU Y 1 X 0 + R 1 Coefficients R 0 X + ALU + R 0 Data R 1 Accumulator Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP 1 Data Memory Introduction to 5685 x Series 2/26/2021 1

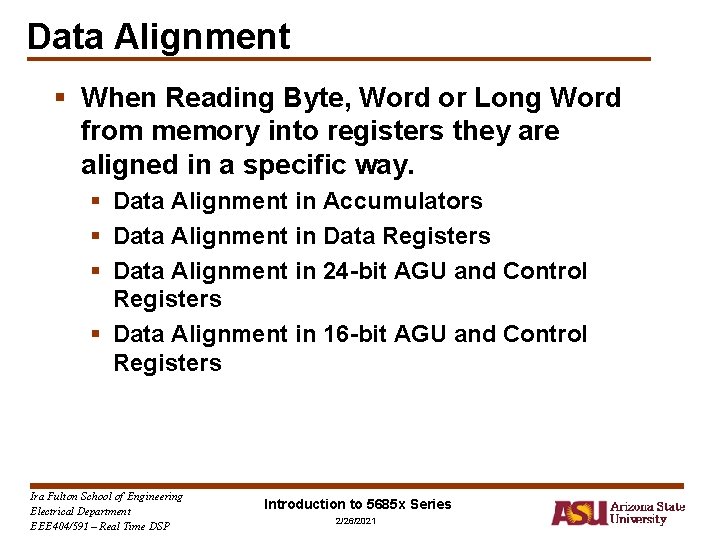

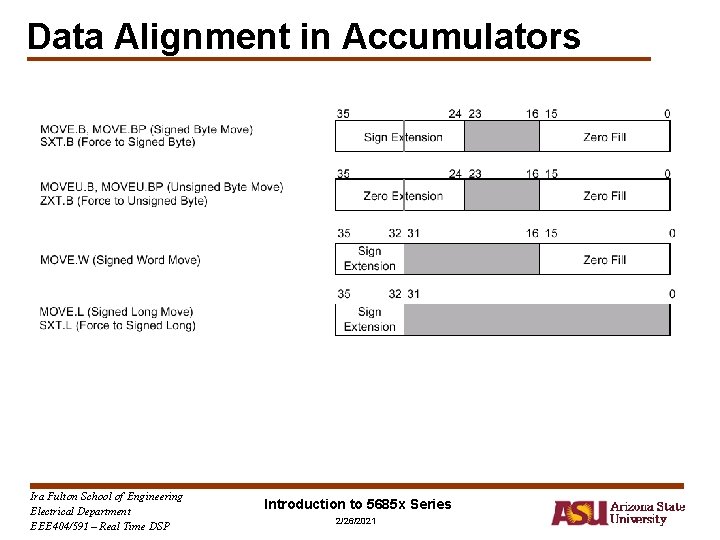

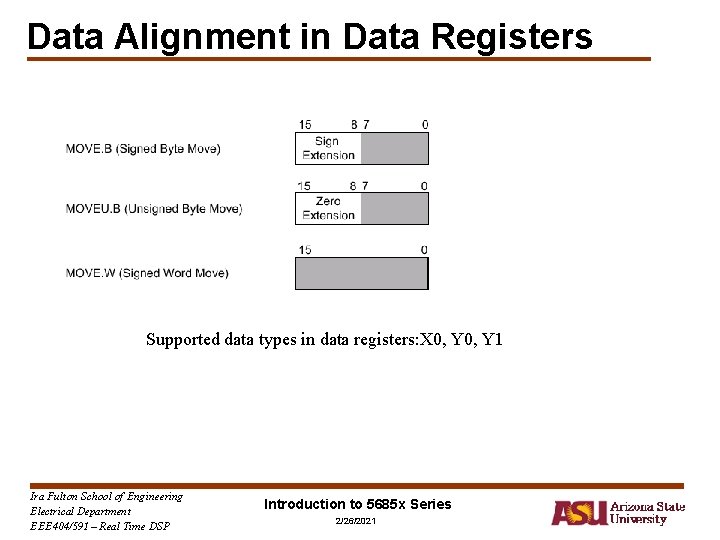

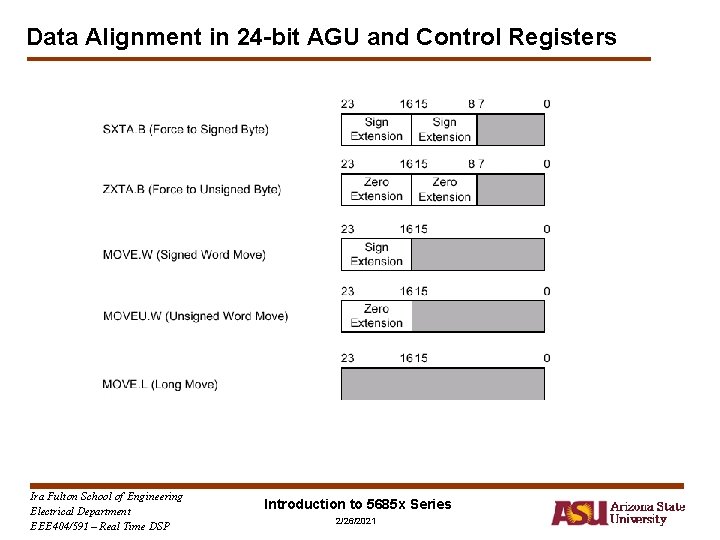

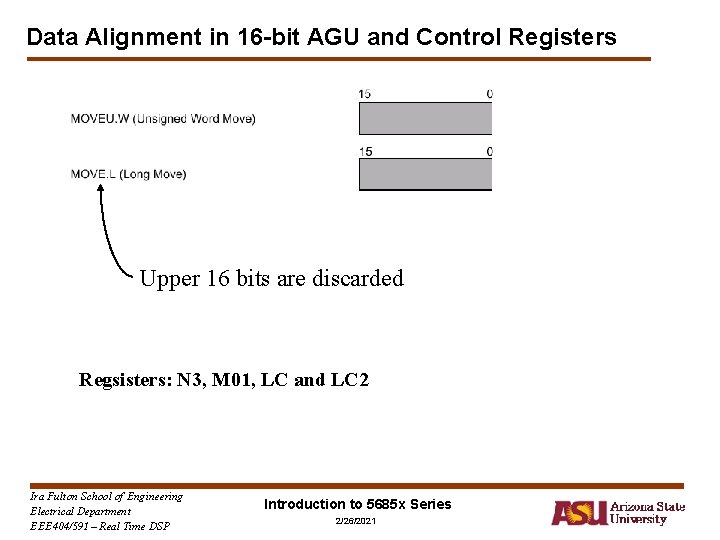

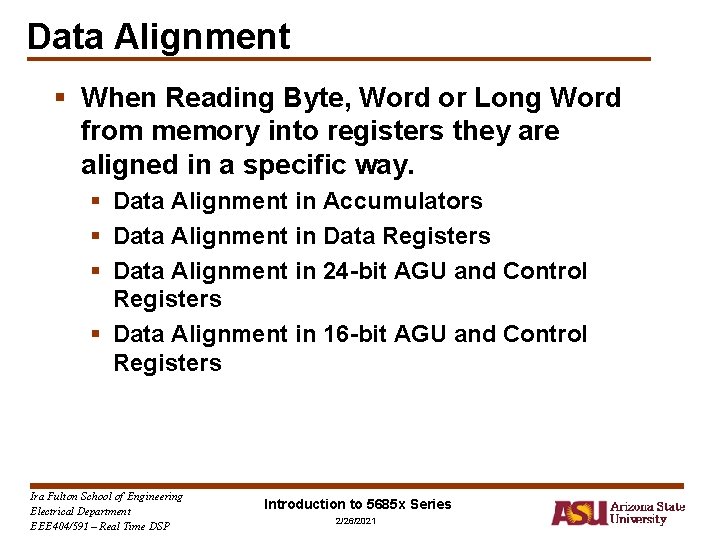

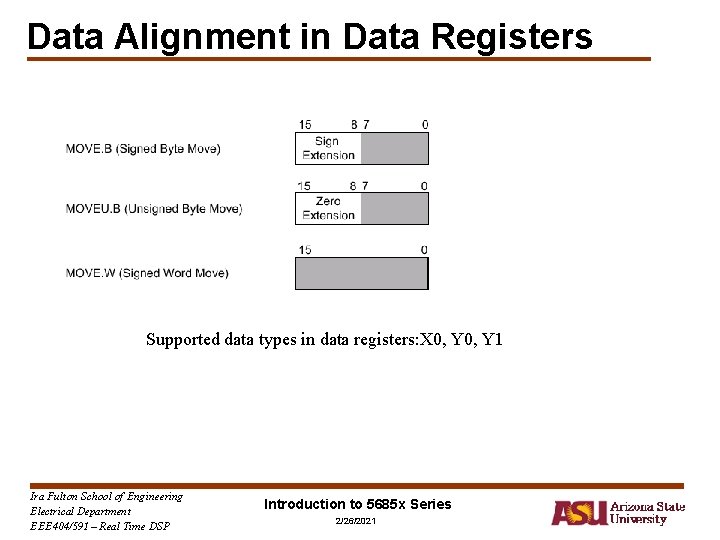

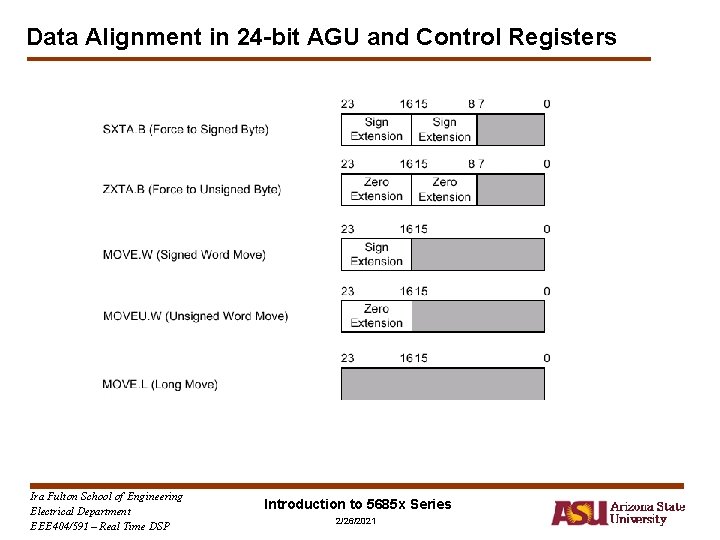

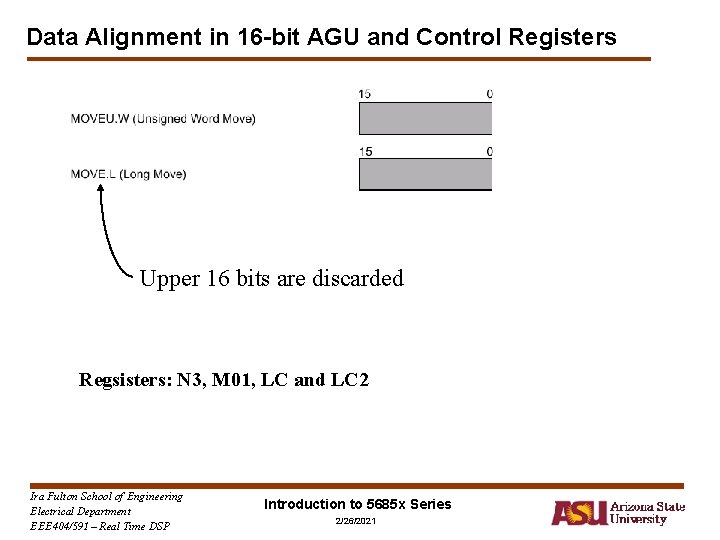

Data Alignment § When Reading Byte, Word or Long Word from memory into registers they are aligned in a specific way. § Data Alignment in Accumulators § Data Alignment in Data Registers § Data Alignment in 24 -bit AGU and Control Registers § Data Alignment in 16 -bit AGU and Control Registers Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

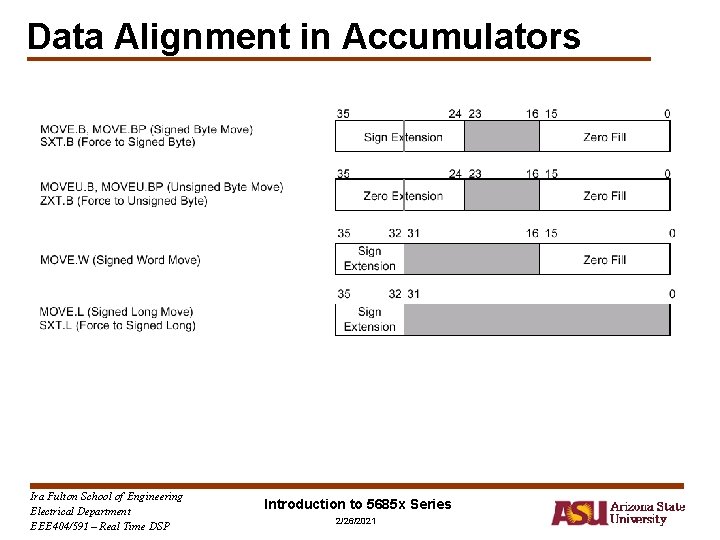

Data Alignment in Accumulators Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

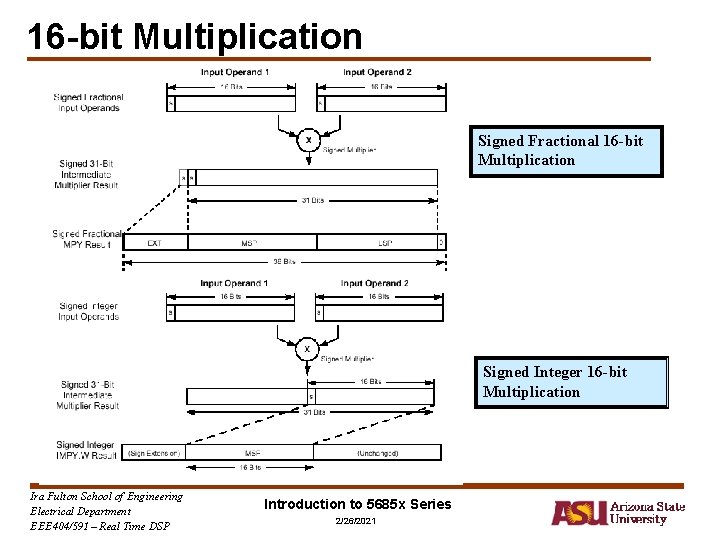

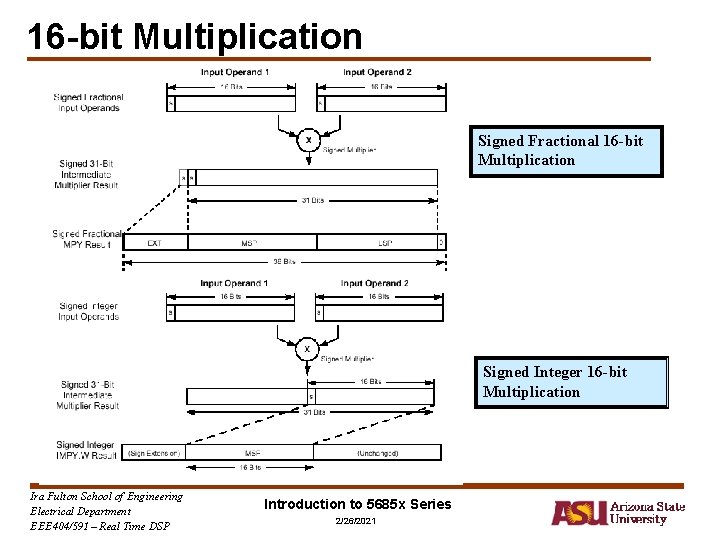

16 -bit Multiplication Signed Fractional 16 -bit Multiplication Signed Integer 16 -bit Multiplication Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Data Alignment in Data Registers Supported data types in data registers: X 0, Y 1 Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Data Alignment in 24 -bit AGU and Control Registers Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021

Data Alignment in 16 -bit AGU and Control Registers Upper 16 bits are discarded Regsisters: N 3, M 01, LC and LC 2 Ira Fulton School of Engineering Electrical Department EEE 404/591 – Real Time DSP Introduction to 5685 x Series 2/26/2021