Chapter 11 Multiple interrupts CEG 2400 Microcomputer Systems

![Interrupt details : chapter 5 of [1] from http: //www. nxp. com/acrobat_download/usermanuals/UM 10120_ 1. Interrupt details : chapter 5 of [1] from http: //www. nxp. com/acrobat_download/usermanuals/UM 10120_ 1.](https://slidetodoc.com/presentation_image_h2/7d50036e911c6dbf9de7770af3f9eb97/image-25.jpg)

- Slides: 26

Chapter 11 Multiple interrupts CEG 2400 - Microcomputer Systems http: //www. nxp. com/acrobat_download/usermanuals/UM 10120_1. pdf (software) CEG 2400 Ch 11 Multiple Interrupts V 7 a 1

Overview To demonstrate multiple interrupts timer_int_demo 1. c Control the on/off of the green LED by a switch CEG 2400 Ch 11 Multiple Interrupts V 7 a 2

To demonstrate multiple interrupts timer_int_demo 1. c Important parts 1) main(), 2) init_timer_Eint () //init timer 3) __irq isr_Eint 3() //external interrupt, blink green-led CEG 2400 Ch 11 Multiple Interrupts V 7 a 3

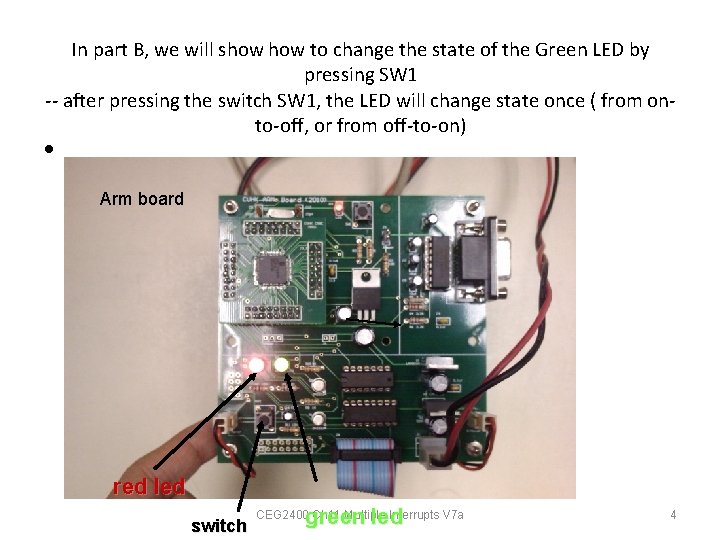

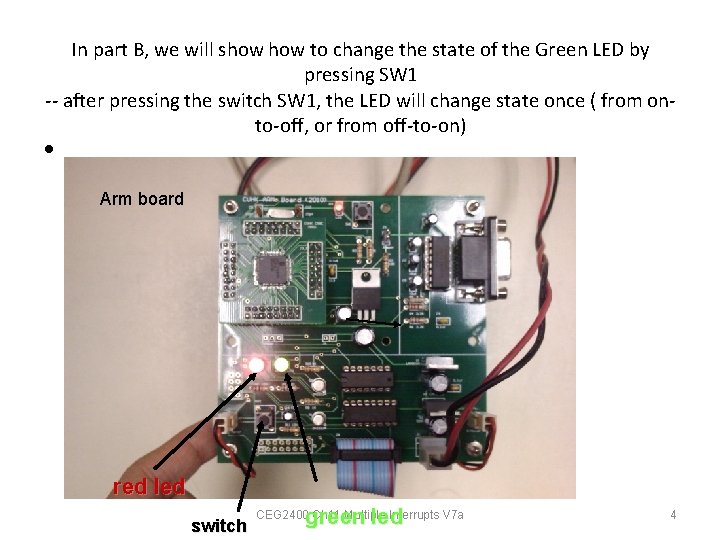

In part B, we will show to change the state of the Green LED by pressing SW 1 -- after pressing the switch SW 1, the LED will change state once ( from onto-off, or from off-to-on) • Arm board red led switch green led CEG 2400 Ch 11 Multiple Interrupts V 7 a 4

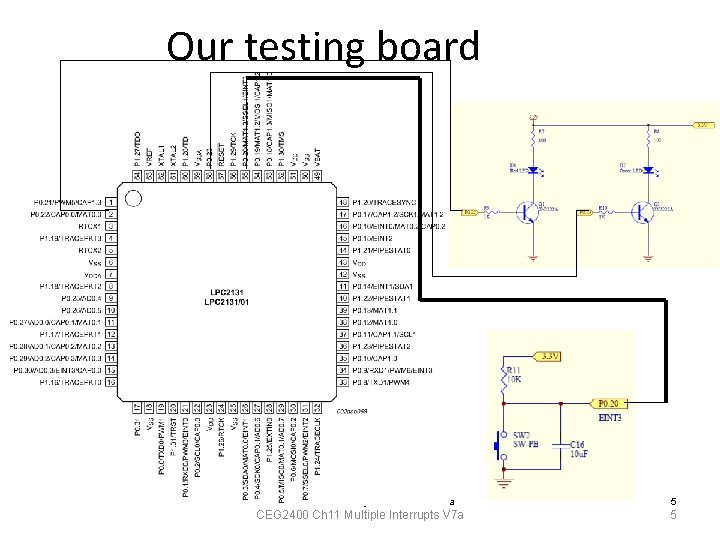

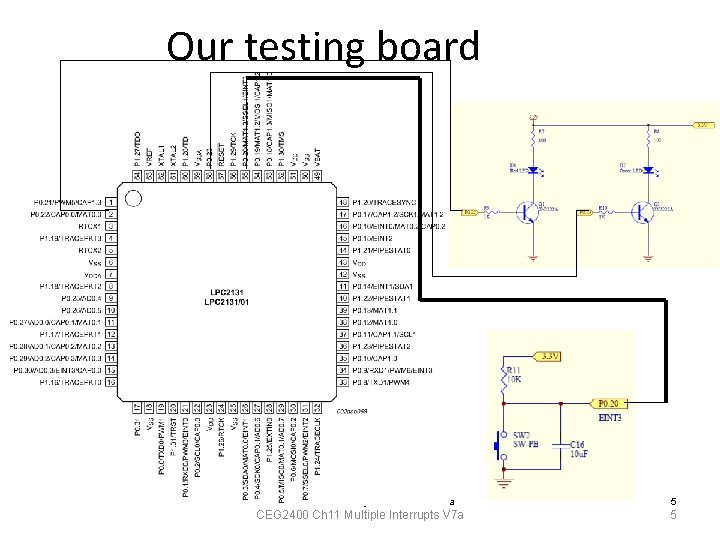

Our testing board • CEG 2400 Ch 7: Driving Parallel Loads V 1 a 5 CEG 2400 Ch 11 Multiple Interrupts V 7 a 5

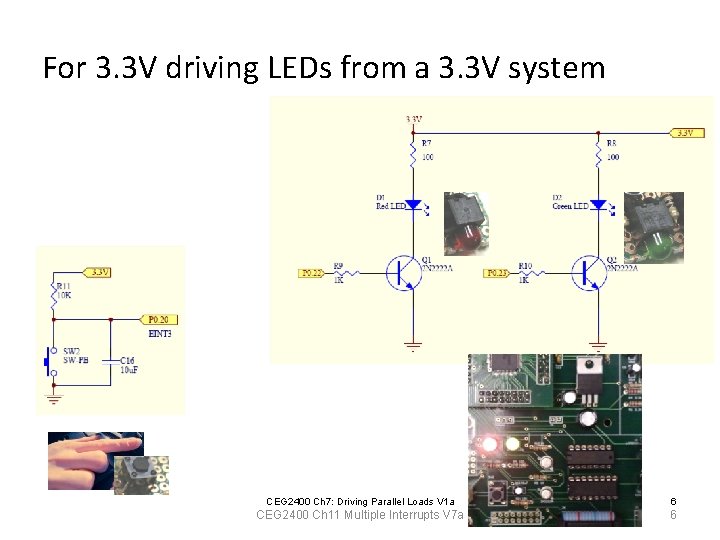

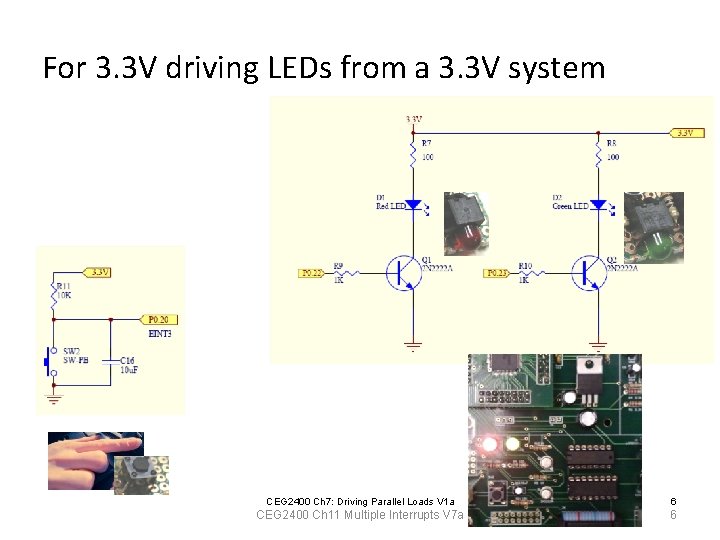

For 3. 3 V driving LEDs from a 3. 3 V system CEG 2400 Ch 7: Driving Parallel Loads V 1 a 6 CEG 2400 Ch 11 Multiple Interrupts V 7 a 6

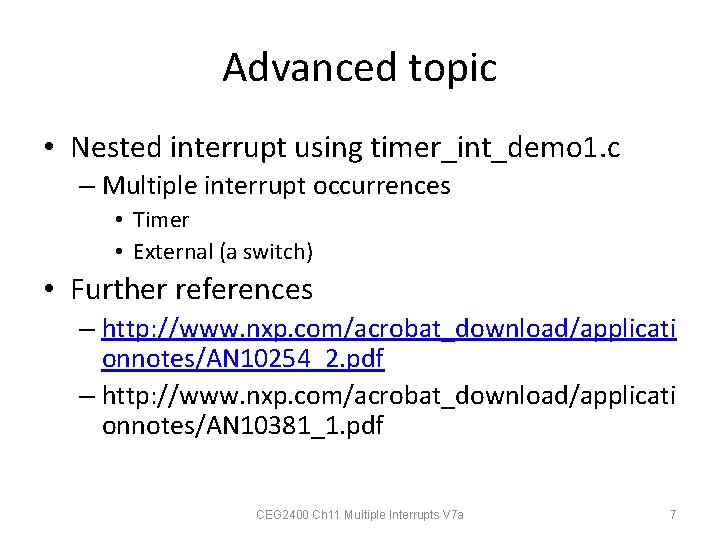

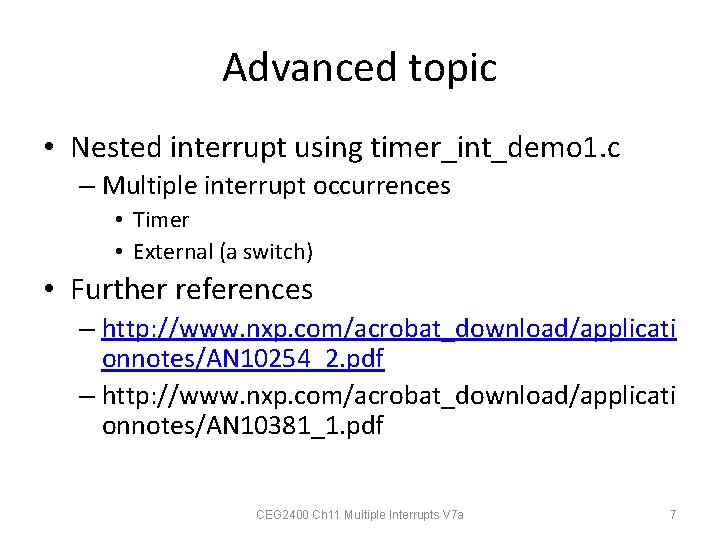

Advanced topic • Nested interrupt using timer_int_demo 1. c – Multiple interrupt occurrences • Timer • External (a switch) • Further references – http: //www. nxp. com/acrobat_download/applicati onnotes/AN 10254_2. pdf – http: //www. nxp. com/acrobat_download/applicati onnotes/AN 10381_1. pdf CEG 2400 Ch 11 Multiple Interrupts V 7 a 7

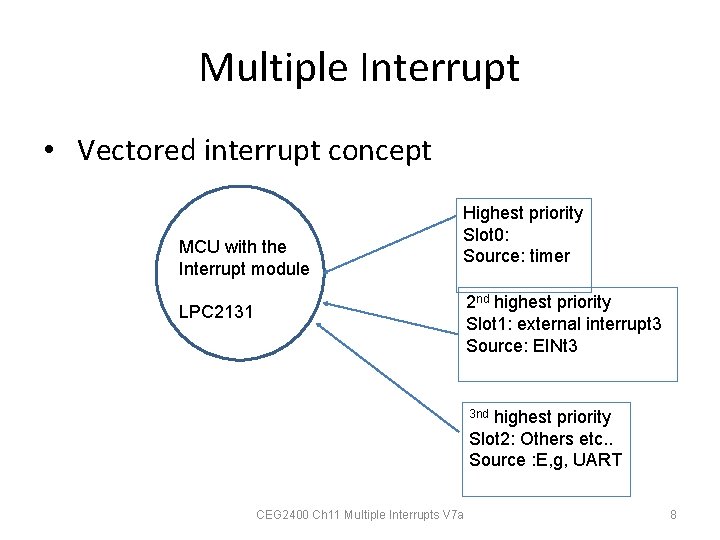

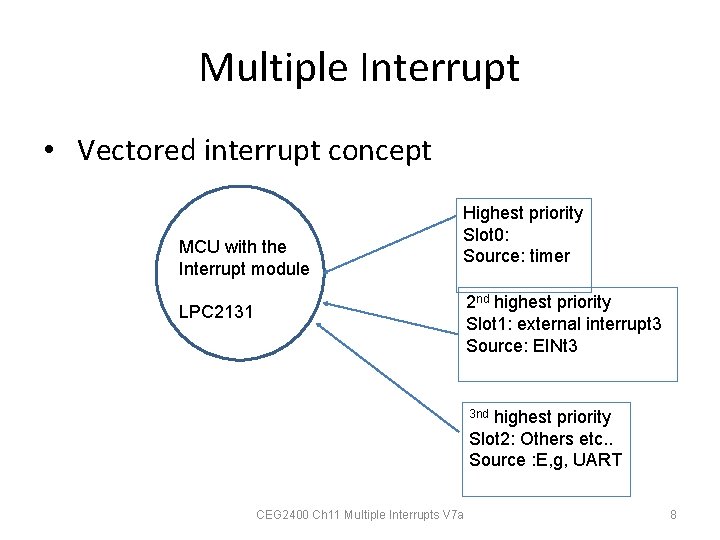

Multiple Interrupt • Vectored interrupt concept MCU with the Interrupt module Highest priority Slot 0: Source: timer 2 nd highest priority Slot 1: external interrupt 3 Source: EINt 3 LPC 2131 highest priority Slot 2: Others etc. . Source : E, g, UART 3 nd CEG 2400 Ch 11 Multiple Interrupts V 7 a 8

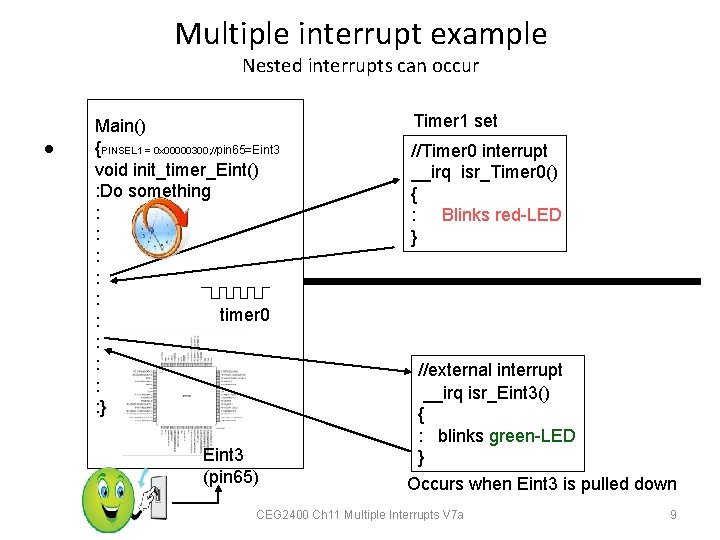

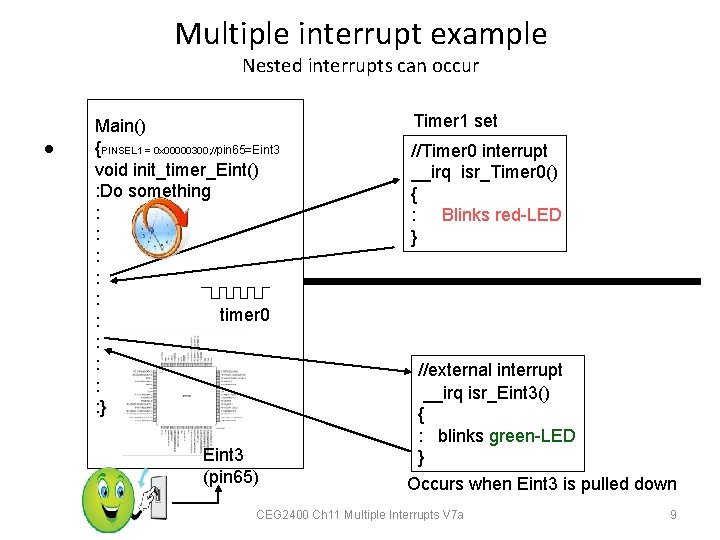

Multiple interrupt example Nested interrupts can occur • Main() {PINSEL 1 = 0 x 00000300; //pin 65=Eint 3 void init_timer_Eint() : Do something : : : timer 0 : : : } Eint 3 (pin 65) Timer 1 set //Timer 0 interrupt __irq isr_Timer 0() { : Blinks red-LED } //external interrupt __irq isr_Eint 3() { : blinks green-LED } Occurs when Eint 3 is pulled down CEG 2400 Ch 11 Multiple Interrupts V 7 a 9

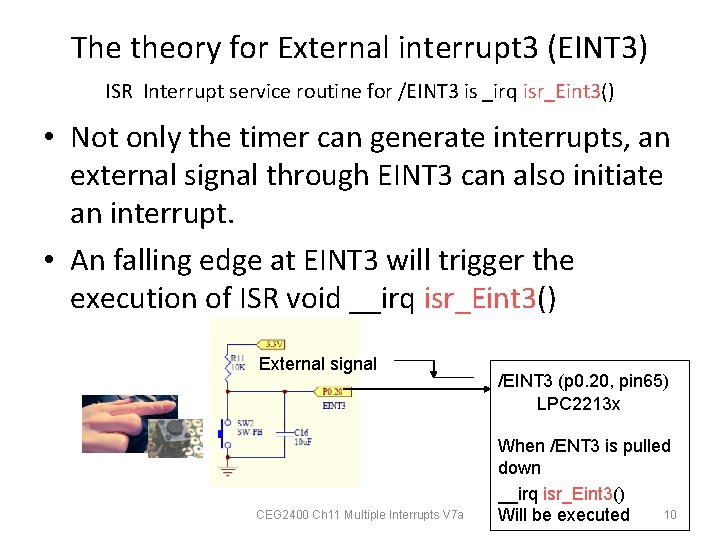

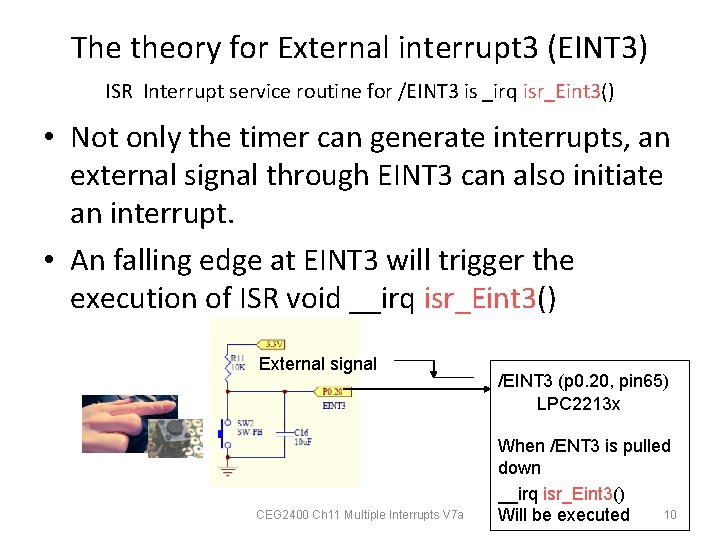

The theory for External interrupt 3 (EINT 3) ISR Interrupt service routine for /EINT 3 is _irq isr_Eint 3() • Not only the timer can generate interrupts, an external signal through EINT 3 can also initiate an interrupt. • An falling edge at EINT 3 will trigger the execution of ISR void __irq isr_Eint 3() External signal CEG 2400 Ch 11 Multiple Interrupts V 7 a /EINT 3 (p 0. 20, pin 65) LPC 2213 x When /ENT 3 is pulled down __irq isr_Eint 3() 10 Will be executed

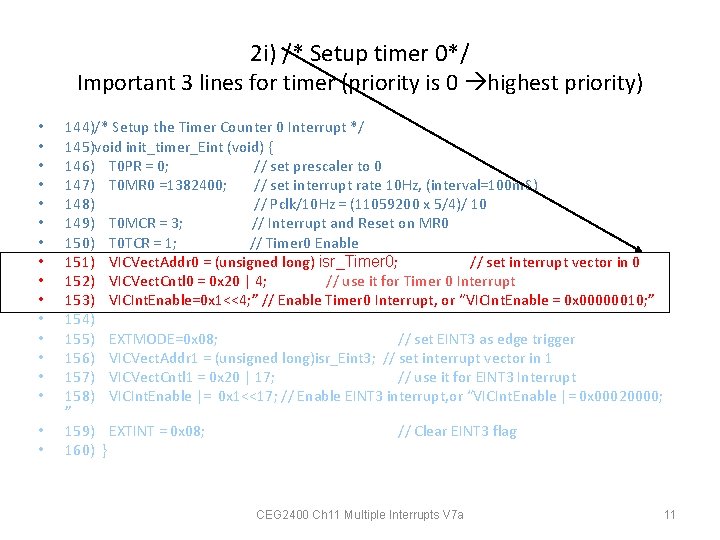

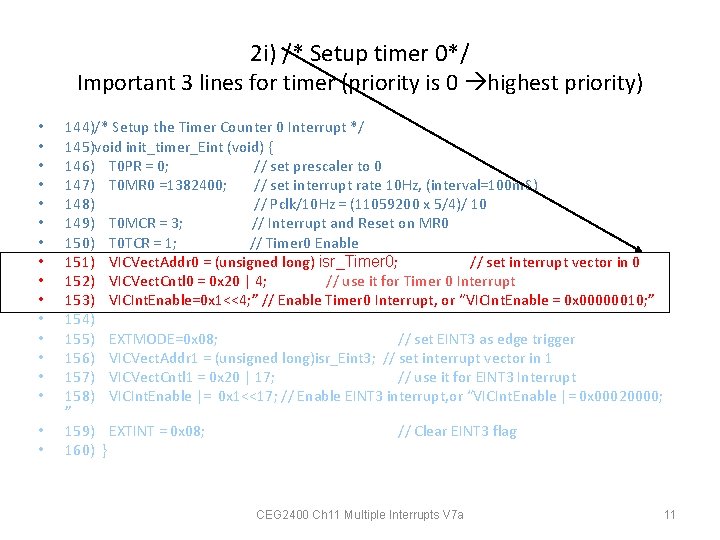

2 i) /* Setup timer 0*/ Important 3 lines for timer (priority is 0 highest priority) • • • • • 144)/* Setup the Timer Counter 0 Interrupt */ 145)void init_timer_Eint (void) { 146) T 0 PR = 0; // set prescaler to 0 147) T 0 MR 0 =1382400; // set interrupt rate 10 Hz, (interval=100 m. S) 148) // Pclk/10 Hz = (11059200 x 5/4)/ 10 149) T 0 MCR = 3; // Interrupt and Reset on MR 0 150) T 0 TCR = 1; // Timer 0 Enable 151) VICVect. Addr 0 = (unsigned long) isr_Timer 0; // set interrupt vector in 0 152) VICVect. Cntl 0 = 0 x 20 | 4; // use it for Timer 0 Interrupt 153) VICInt. Enable=0 x 1<<4; ” // Enable Timer 0 Interrupt, or “VICInt. Enable = 0 x 00000010; ” 154) 155) EXTMODE=0 x 08; // set EINT 3 as edge trigger 156) VICVect. Addr 1 = (unsigned long)isr_Eint 3; // set interrupt vector in 1 157) VICVect. Cntl 1 = 0 x 20 | 17; // use it for EINT 3 Interrupt 158) VICInt. Enable |= 0 x 1<<17; // Enable EINT 3 interrupt, or “VICInt. Enable |= 0 x 00020000; ” 159) EXTINT = 0 x 08; // Clear EINT 3 flag 160) } CEG 2400 Ch 11 Multiple Interrupts V 7 a 11

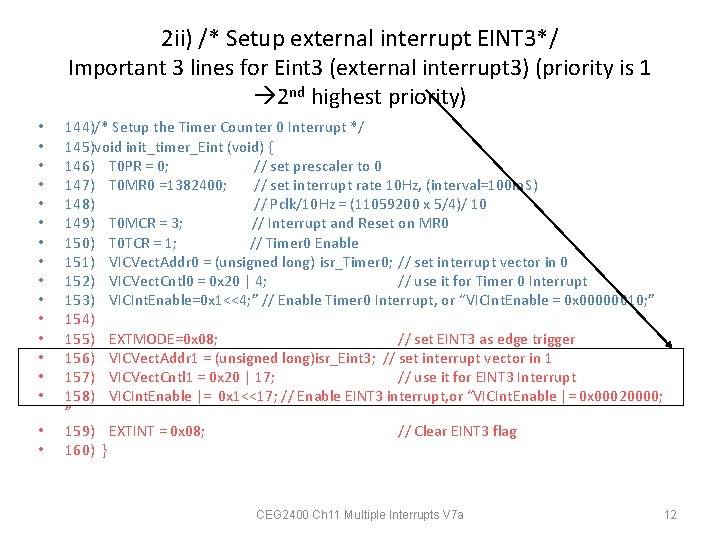

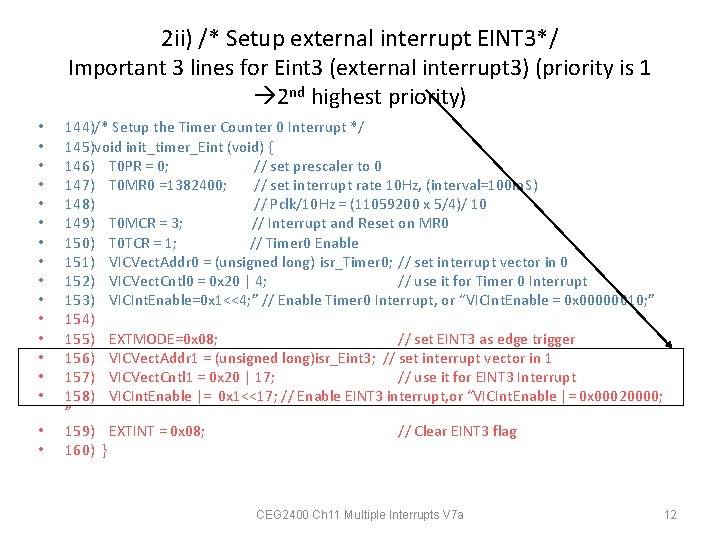

2 ii) /* Setup external interrupt EINT 3*/ Important 3 lines for Eint 3 (external interrupt 3) (priority is 1 2 nd highest priority) • • • • • 144)/* Setup the Timer Counter 0 Interrupt */ 145)void init_timer_Eint (void) { 146) T 0 PR = 0; // set prescaler to 0 147) T 0 MR 0 =1382400; // set interrupt rate 10 Hz, (interval=100 m. S) 148) // Pclk/10 Hz = (11059200 x 5/4)/ 10 149) T 0 MCR = 3; // Interrupt and Reset on MR 0 150) T 0 TCR = 1; // Timer 0 Enable 151) VICVect. Addr 0 = (unsigned long) isr_Timer 0; // set interrupt vector in 0 152) VICVect. Cntl 0 = 0 x 20 | 4; // use it for Timer 0 Interrupt 153) VICInt. Enable=0 x 1<<4; ” // Enable Timer 0 Interrupt, or “VICInt. Enable = 0 x 00000010; ” 154) 155) EXTMODE=0 x 08; // set EINT 3 as edge trigger 156) VICVect. Addr 1 = (unsigned long)isr_Eint 3; // set interrupt vector in 1 157) VICVect. Cntl 1 = 0 x 20 | 17; // use it for EINT 3 Interrupt 158) VICInt. Enable |= 0 x 1<<17; // Enable EINT 3 interrupt, or “VICInt. Enable |= 0 x 00020000; ” 159) EXTINT = 0 x 08; // Clear EINT 3 flag 160) } CEG 2400 Ch 11 Multiple Interrupts V 7 a 12

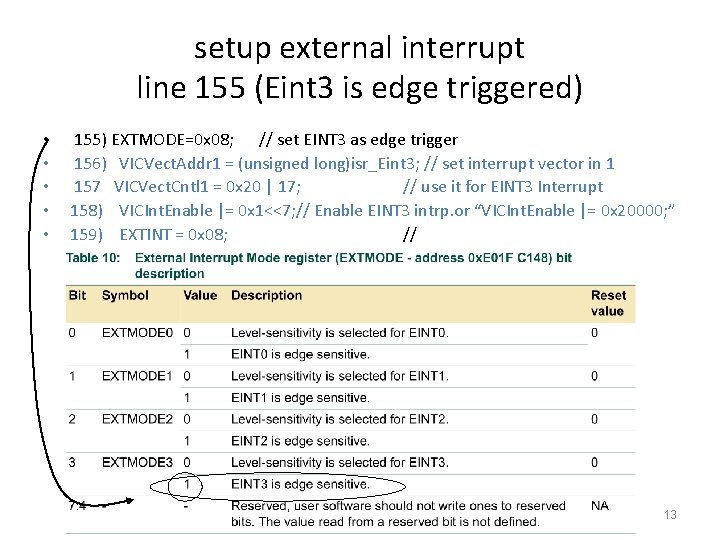

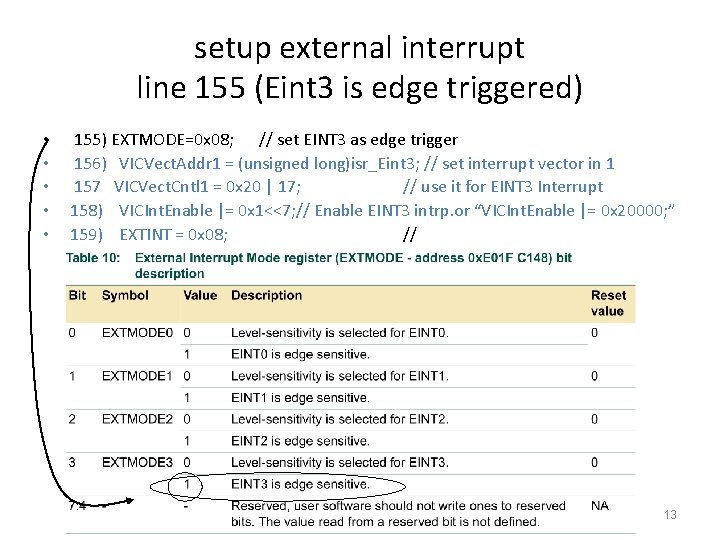

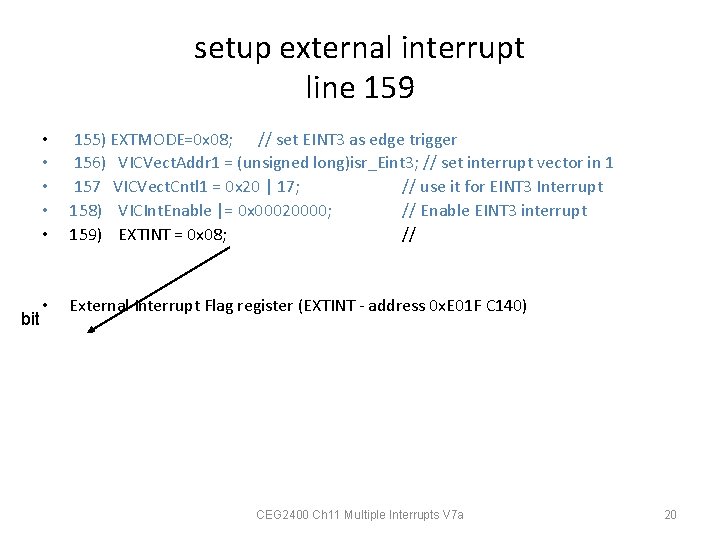

setup external interrupt line 155 (Eint 3 is edge triggered) • • • 155) EXTMODE=0 x 08; // set EINT 3 as edge trigger 156) VICVect. Addr 1 = (unsigned long)isr_Eint 3; // set interrupt vector in 1 157 VICVect. Cntl 1 = 0 x 20 | 17; // use it for EINT 3 Interrupt 158) VICInt. Enable |= 0 x 1<<7; // Enable EINT 3 intrp. or “VICInt. Enable |= 0 x 20000; ” 159) EXTINT = 0 x 08; // CEG 2400 Ch 11 Multiple Interrupts V 7 a 13

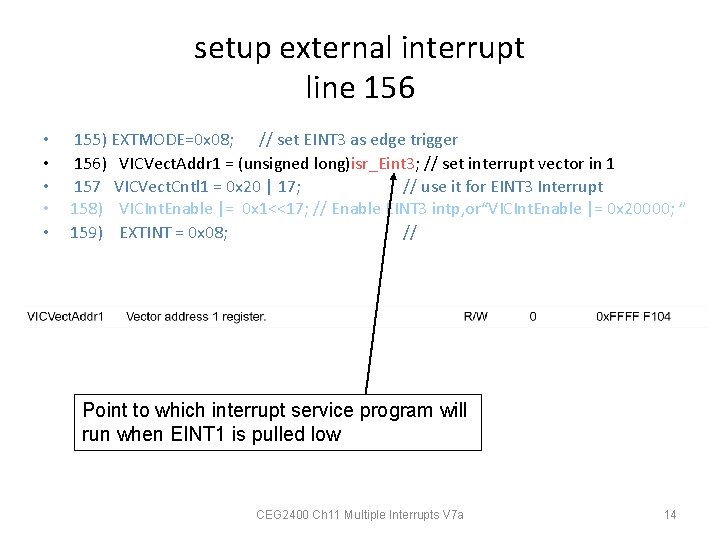

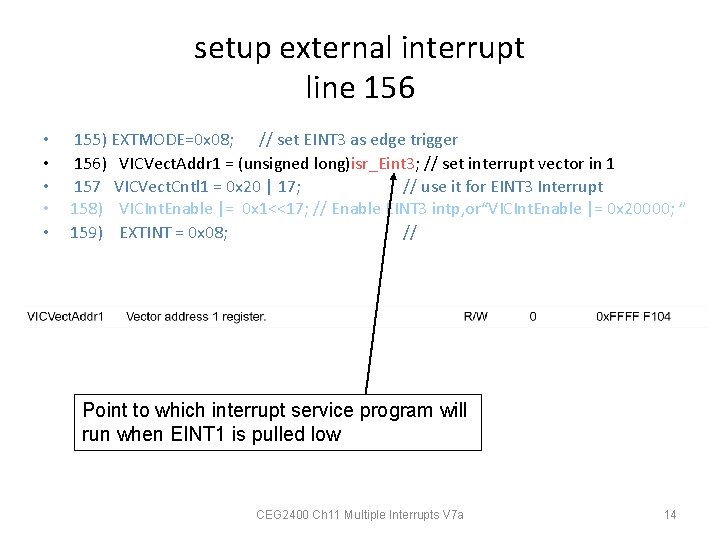

setup external interrupt line 156 • • • 155) EXTMODE=0 x 08; // set EINT 3 as edge trigger 156) VICVect. Addr 1 = (unsigned long)isr_Eint 3; // set interrupt vector in 1 157 VICVect. Cntl 1 = 0 x 20 | 17; // use it for EINT 3 Interrupt 158) VICInt. Enable |= 0 x 1<<17; // Enable EINT 3 intp, or“VICInt. Enable |= 0 x 20000; ” 159) EXTINT = 0 x 08; // Point to which interrupt service program will run when EINT 1 is pulled low CEG 2400 Ch 11 Multiple Interrupts V 7 a 14

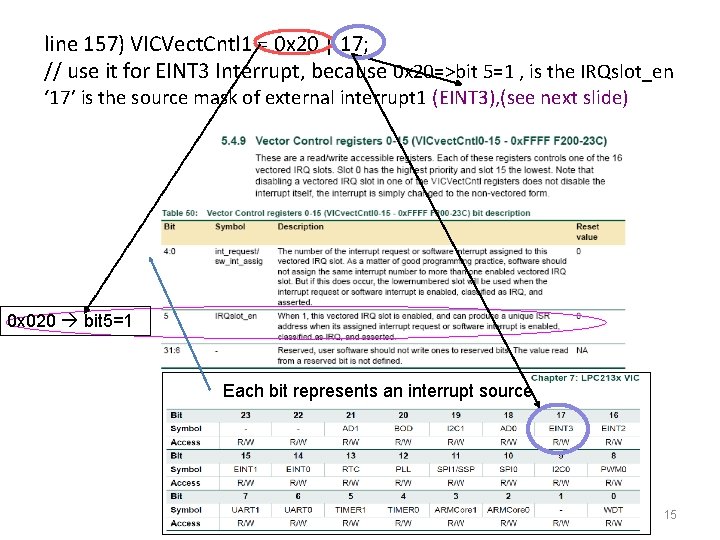

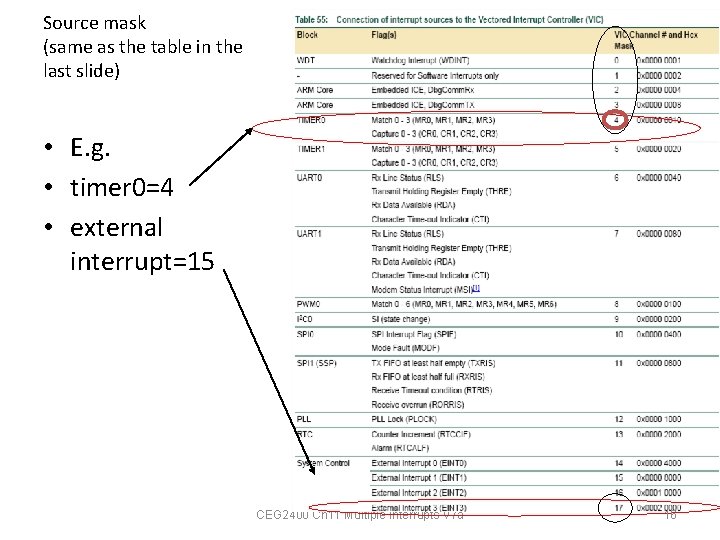

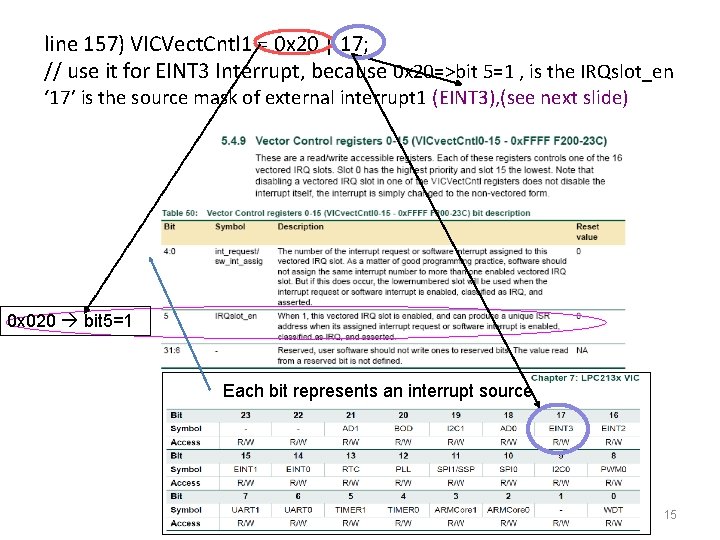

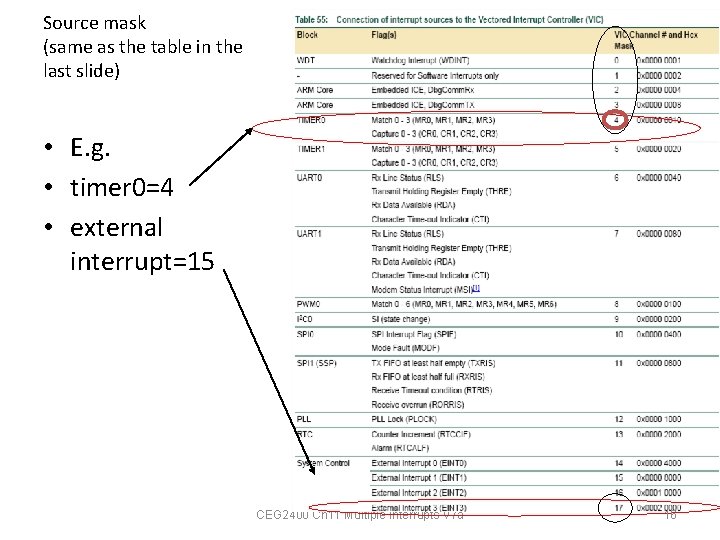

line 157) VICVect. Cntl 1 = 0 x 20 | 17; // use it for EINT 3 Interrupt, because 0 x 20=>bit 5=1 , is the IRQslot_en ‘ 17’ is the source mask of external interrupt 1 (EINT 3), (see next slide) 0 x 020 bit 5=1 Each bit represents an interrupt source CEG 2400 Ch 11 Multiple Interrupts V 7 a 15

Source mask (same as the table in the last slide) • E. g. • timer 0=4 • external interrupt=15 CEG 2400 Ch 11 Multiple Interrupts V 7 a 16

Exercise 11. 1 Student ID: ______, Date: _______ Name: _________________ • What is the interrupt source mask for UART 1? • Answer: ? ___________ • How do you setup the pirorty of different interrupts? • Answer: • ? ______________ CEG 2400 Ch 11 Multiple Interrupts V 7 a 17

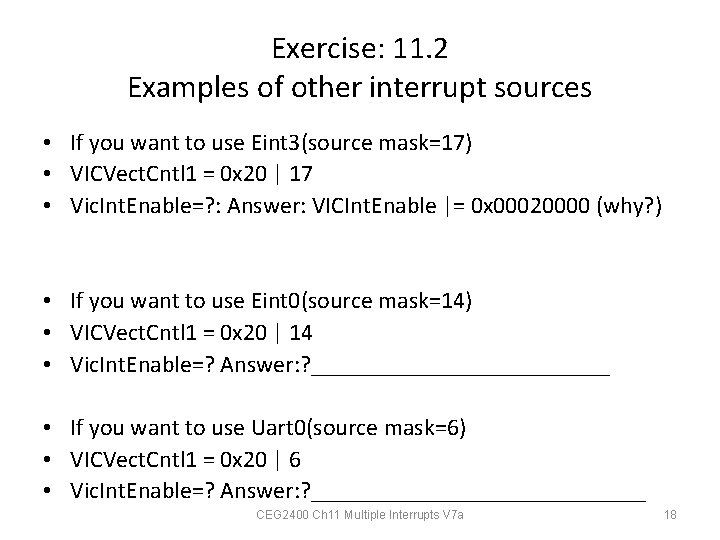

Exercise: 11. 2 Examples of other interrupt sources • If you want to use Eint 3(source mask=17) • VICVect. Cntl 1 = 0 x 20 | 17 • Vic. Int. Enable=? : Answer: VICInt. Enable |= 0 x 00020000 (why? ) • If you want to use Eint 0(source mask=14) • VICVect. Cntl 1 = 0 x 20 | 14 • Vic. Int. Enable=? Answer: ? _____________ • If you want to use Uart 0(source mask=6) • VICVect. Cntl 1 = 0 x 20 | 6 • Vic. Int. Enable=? Answer: ? ______________ CEG 2400 Ch 11 Multiple Interrupts V 7 a 18

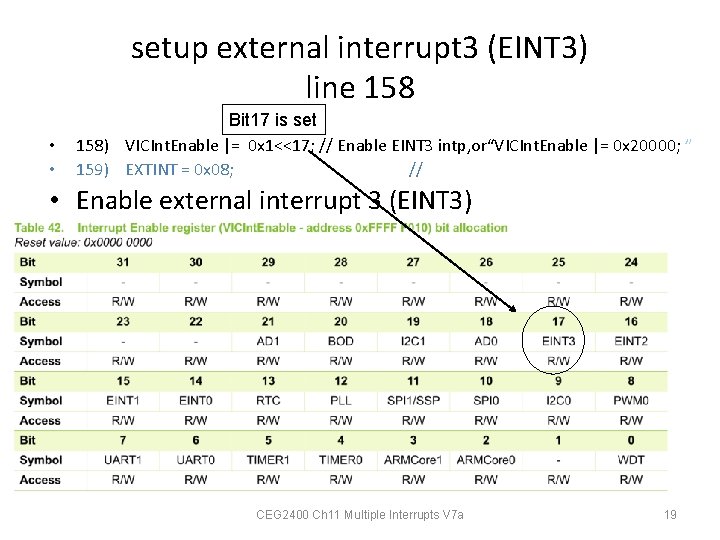

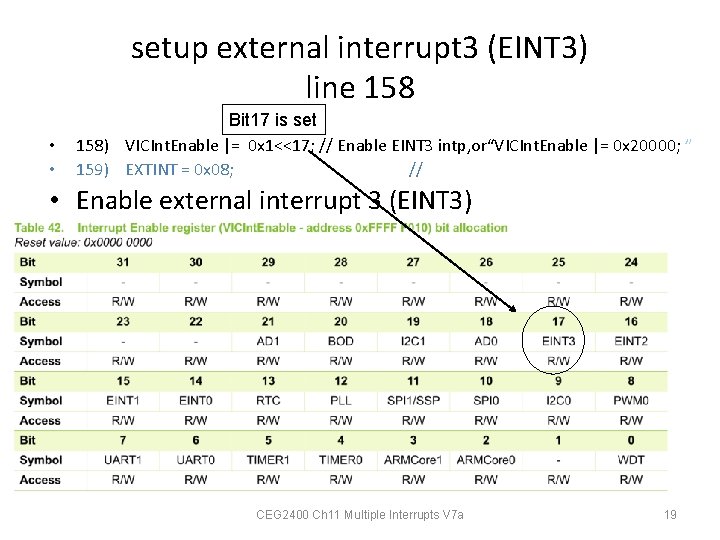

setup external interrupt 3 (EINT 3) line 158 • • Bit 17 is set 158) VICInt. Enable |= 0 x 1<<17; // Enable EINT 3 intp, or“VICInt. Enable |= 0 x 20000; ” 159) EXTINT = 0 x 08; // • Enable external interrupt 3 (EINT 3) CEG 2400 Ch 11 Multiple Interrupts V 7 a 19

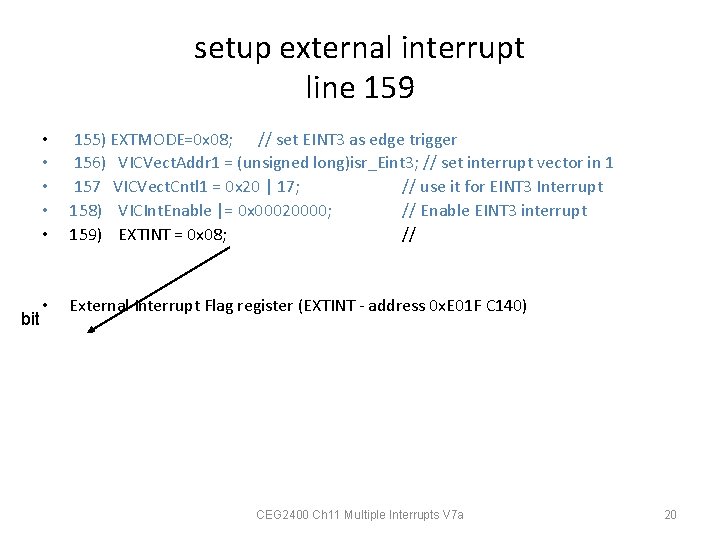

setup external interrupt line 159 bit • • • 155) EXTMODE=0 x 08; // set EINT 3 as edge trigger 156) VICVect. Addr 1 = (unsigned long)isr_Eint 3; // set interrupt vector in 1 157 VICVect. Cntl 1 = 0 x 20 | 17; // use it for EINT 3 Interrupt 158) VICInt. Enable |= 0 x 00020000; // Enable EINT 3 interrupt 159) EXTINT = 0 x 08; // • External Interrupt Flag register (EXTINT - address 0 x. E 01 F C 140) CEG 2400 Ch 11 Multiple Interrupts V 7 a 20

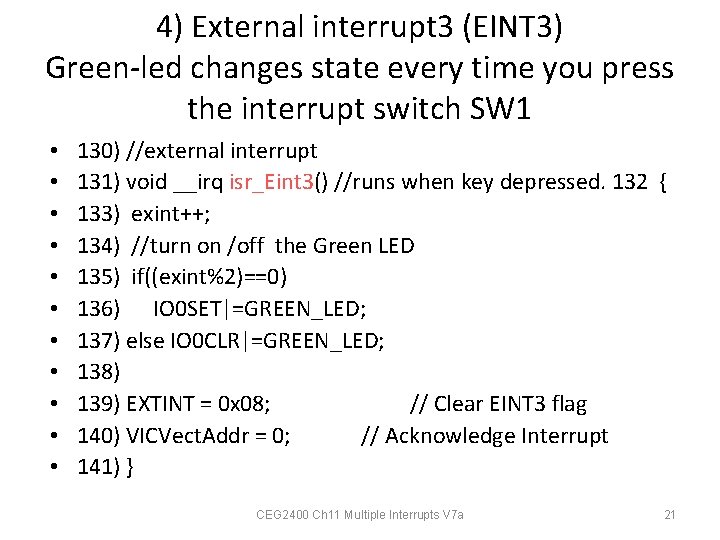

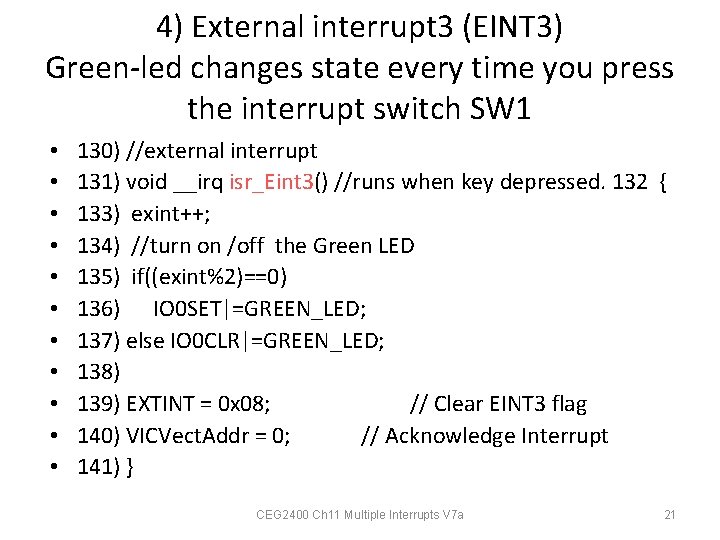

4) External interrupt 3 (EINT 3) Green-led changes state every time you press the interrupt switch SW 1 • • • 130) //external interrupt 131) void __irq isr_Eint 3() //runs when key depressed. 132 { 133) exint++; 134) //turn on /off the Green LED 135) if((exint%2)==0) 136) IO 0 SET|=GREEN_LED; 137) else IO 0 CLR|=GREEN_LED; 138) 139) EXTINT = 0 x 08; // Clear EINT 3 flag 140) VICVect. Addr = 0; // Acknowledge Interrupt 141) } CEG 2400 Ch 11 Multiple Interrupts V 7 a 21

Programming Exercise: study the following programs • GPIO. c is a polling software program and a switch (SW 1) to change the state of the Green LED • timer_int_demo 1. c is a program uses hardware external interrupt 3 (EINT 3) and a switch (SW 1) to change the state of the Green LED. • Compare the difference between timer_int_demo 1. c and GPIO. c in terms of technology and performance CEG 2400 Ch 11 Multiple Interrupts V 7 a 22

Summary • Learned how to initialize an ARM system • Learned how to use timer interrupt • timer_int_demo 1. c can be used as a template for building interrupt driven programs. CEG 2400 Ch 11 Multiple Interrupts V 7 a 23

Appendix (ESTR 2100 students should study this) CEG 2400 Ch 11 Multiple Interrupts V 7 a 24

![Interrupt details chapter 5 of 1 from http www nxp comacrobatdownloadusermanualsUM 10120 1 Interrupt details : chapter 5 of [1] from http: //www. nxp. com/acrobat_download/usermanuals/UM 10120_ 1.](https://slidetodoc.com/presentation_image_h2/7d50036e911c6dbf9de7770af3f9eb97/image-25.jpg)

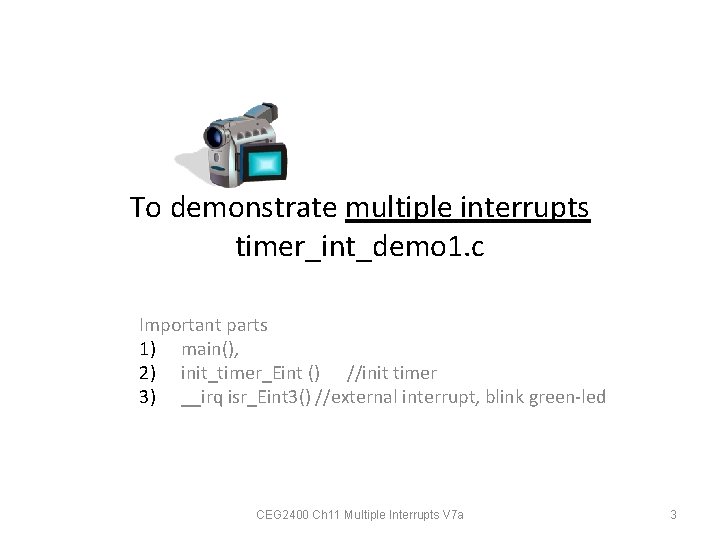

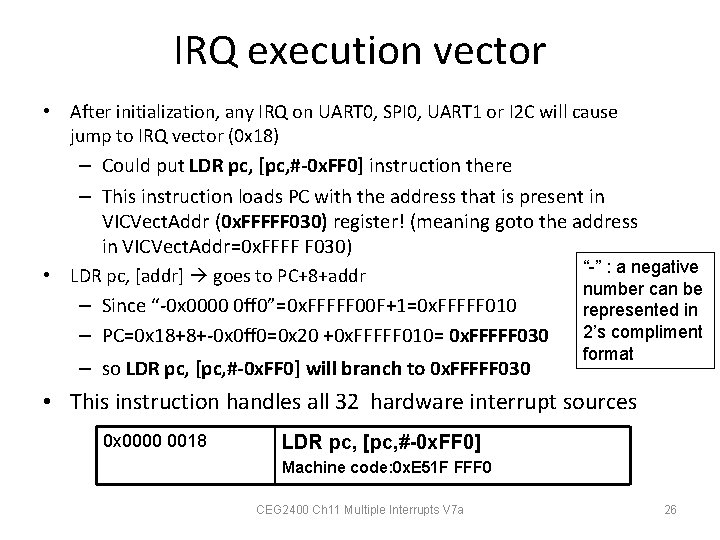

Interrupt details : chapter 5 of [1] from http: //www. nxp. com/acrobat_download/usermanuals/UM 10120_ 1. pdf Example UART generates an interrupt request and has the highest priory VICVect. Addr reg contans, 0 xffff f 030 • Interrupt service routine starting address of ISR_UART() ISR_UART (software to handle UART) starting : : address is at VICVect. Addr 0 x 0000 0018 LDR pc, [pc, #-0 x. FF 0] address reg 0 x. FFFF F 030 Machine code: 0 x. E 51 F FFF 0 • At 0 x 18, the instruction is LDR pc, [pc, #-0 x. FF 0] which VIC places the address there automatically will redirect Arm to VIC executed ISR_UART() when IRQ UART interrupt request is Or IRQ_vector= function received 0 x 18 Other interrupt sources UART Serial interface ARM 7 TDMI Processor End of transmission CEG 2400 Ch 11 Multiple Interrupts. Logic_or V 7 a all requests 25

IRQ execution vector • After initialization, any IRQ on UART 0, SPI 0, UART 1 or I 2 C will cause jump to IRQ vector (0 x 18) – Could put LDR pc, [pc, #-0 x. FF 0] instruction there – This instruction loads PC with the address that is present in VICVect. Addr (0 x. FFFFF 030) register! (meaning goto the address in VICVect. Addr=0 x. FFFF F 030) “-” : a negative • LDR pc, [addr] goes to PC+8+addr number can be – Since “-0 x 0000 0 ff 0”=0 x. FFFFF 00 F+1=0 x. FFFFF 010 represented in 2’s compliment – PC=0 x 18+8+-0 x 0 ff 0=0 x 20 +0 x. FFFFF 010= 0 x. FFFFF 030 – so LDR pc, [pc, #-0 x. FF 0] will branch to 0 x. FFFFF 030 format • This instruction handles all 32 hardware interrupt sources 0 x 0000 0018 LDR pc, [pc, #-0 x. FF 0] Machine code: 0 x. E 51 F FFF 0 CEG 2400 Ch 11 Multiple Interrupts V 7 a 26