Advanced Implantation Detector Array AIDA Update Issues presented

- Slides: 25

Advanced Implantation Detector Array (AIDA): Update & Issues presented by Tom Davinson on behalf of the AIDA collaboration (Edinburgh – Liverpool – STFC DL & RAL) Tom Davinson School of Physics The University of Edinburgh

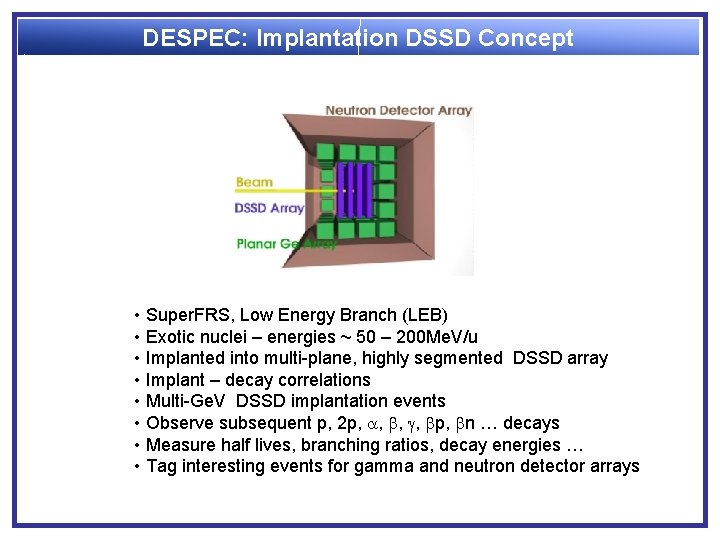

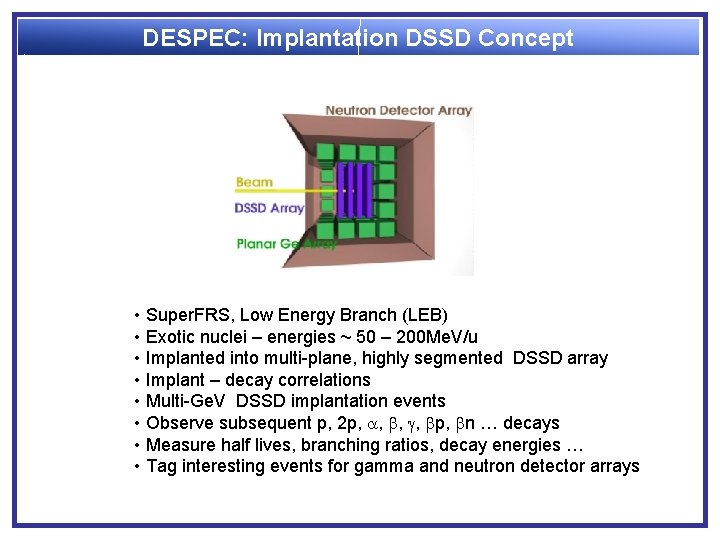

DESPEC: Implantation DSSD Concept • Super. FRS, Low Energy Branch (LEB) • Exotic nuclei – energies ~ 50 – 200 Me. V/u • Implanted into multi-plane, highly segmented DSSD array • Implant – decay correlations • Multi-Ge. V DSSD implantation events • Observe subsequent p, 2 p, a, b, g, bp, bn … decays • Measure half lives, branching ratios, decay energies … • Tag interesting events for gamma and neutron detector arrays

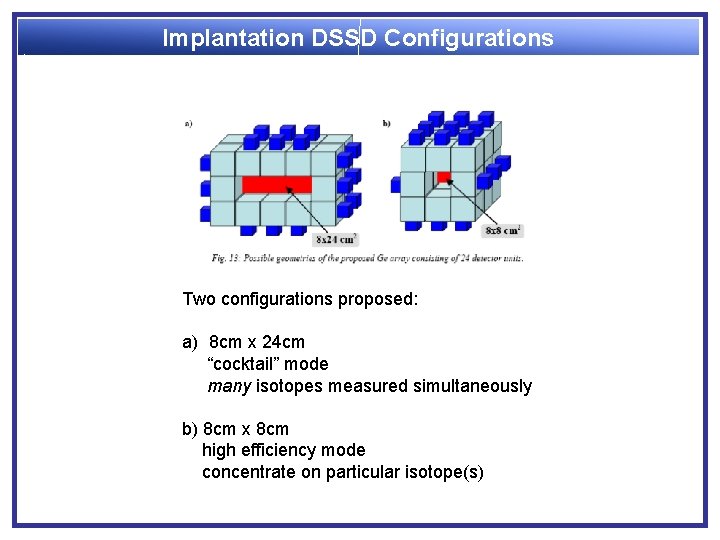

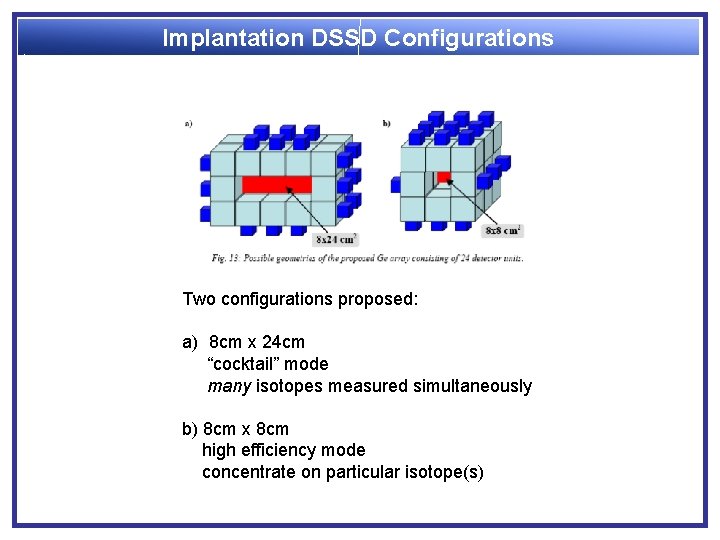

Implantation DSSD Configurations Two configurations proposed: a) 8 cm x 24 cm “cocktail” mode many isotopes measured simultaneously b) 8 cm x 8 cm high efficiency mode concentrate on particular isotope(s)

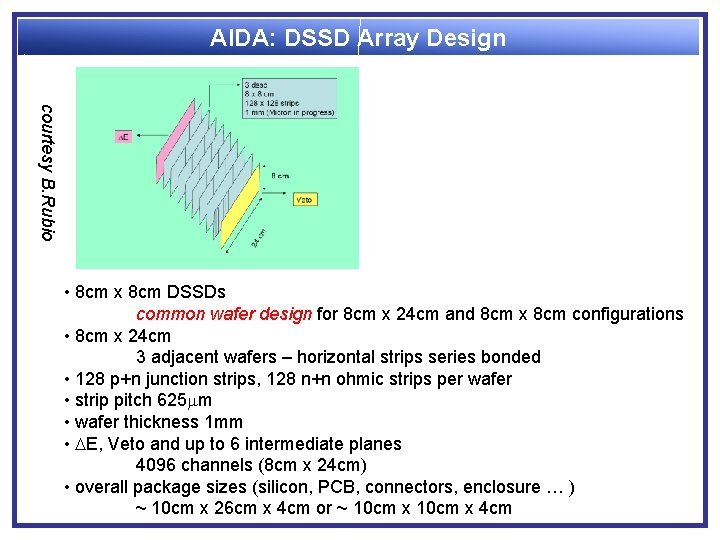

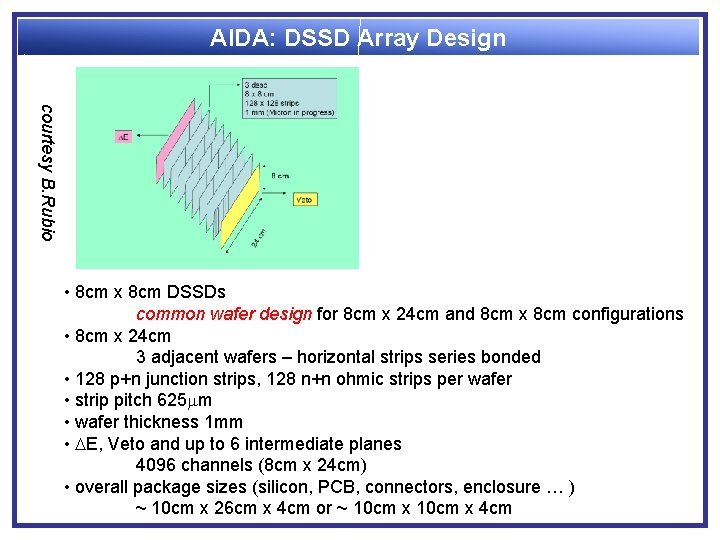

AIDA: DSSD Array Design courtesy B. Rubio • 8 cm x 8 cm DSSDs common wafer design for 8 cm x 24 cm and 8 cm x 8 cm configurations • 8 cm x 24 cm 3 adjacent wafers – horizontal strips series bonded • 128 p+n junction strips, 128 n+n ohmic strips per wafer • strip pitch 625 mm • wafer thickness 1 mm • DE, Veto and up to 6 intermediate planes 4096 channels (8 cm x 24 cm) • overall package sizes (silicon, PCB, connectors, enclosure … ) ~ 10 cm x 26 cm x 4 cm or ~ 10 cm x 4 cm

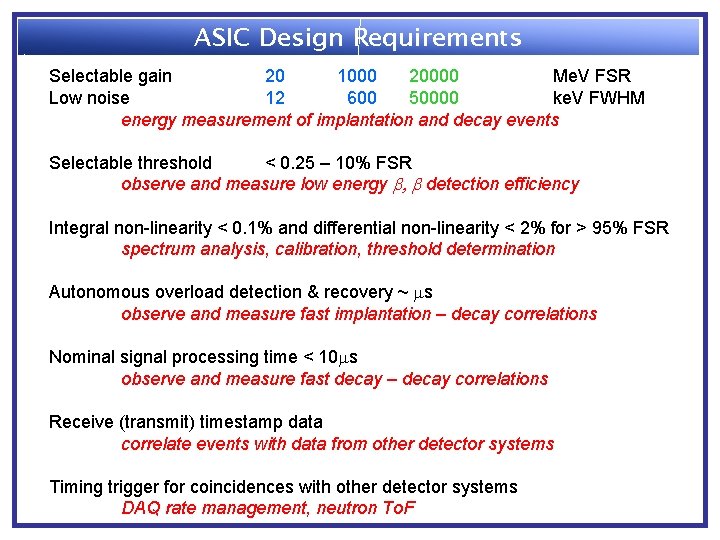

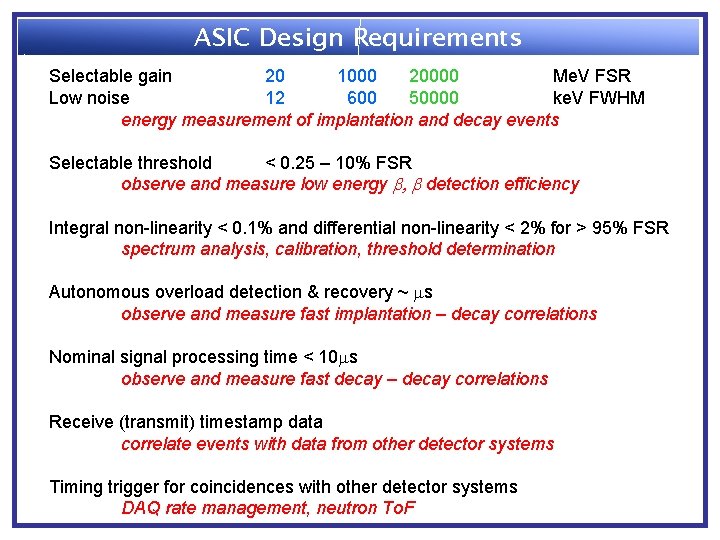

ASIC Design Requirements Selectable gain 20 1000 20000 Me. V FSR Low noise 12 600 50000 ke. V FWHM energy measurement of implantation and decay events Selectable threshold < 0. 25 – 10% FSR observe and measure low energy b, b detection efficiency Integral non-linearity < 0. 1% and differential non-linearity < 2% for > 95% FSR spectrum analysis, calibration, threshold determination Autonomous overload detection & recovery ~ ms observe and measure fast implantation – decay correlations Nominal signal processing time < 10 ms observe and measure fast decay – decay correlations Receive (transmit) timestamp data correlate events with data from other detector systems Timing trigger for coincidences with other detector systems DAQ rate management, neutron To. F

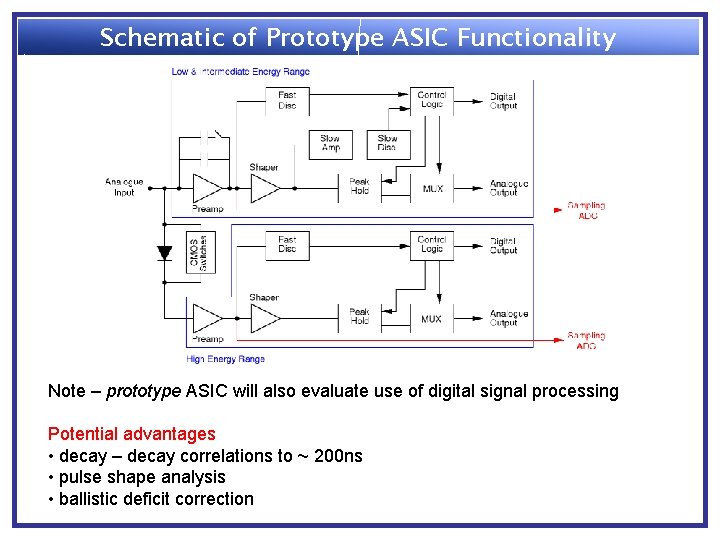

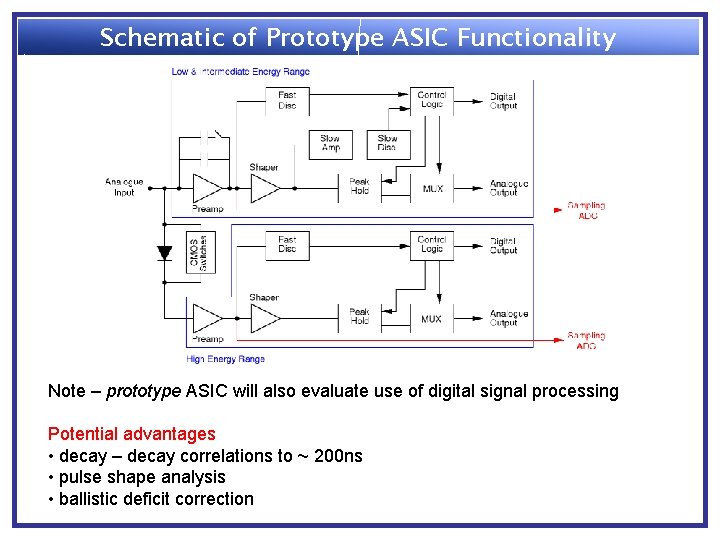

Schematic of Prototype ASIC Functionality Note – prototype ASIC will also evaluate use of digital signal processing Potential advantages • decay – decay correlations to ~ 200 ns • pulse shape analysis • ballistic deficit correction

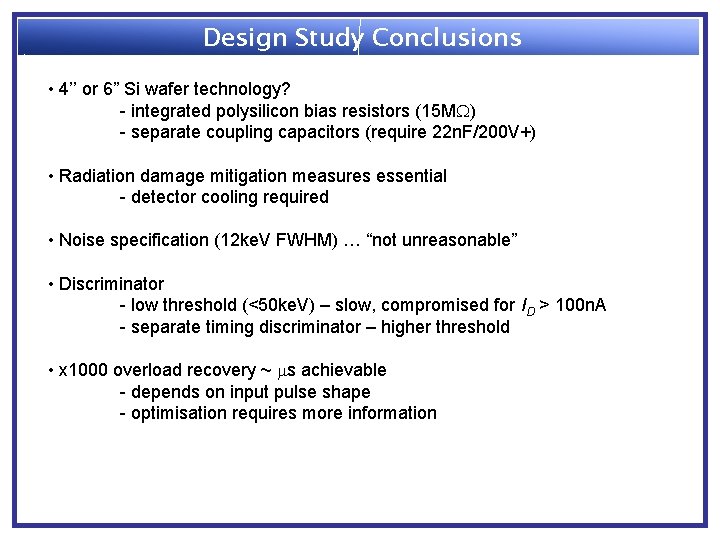

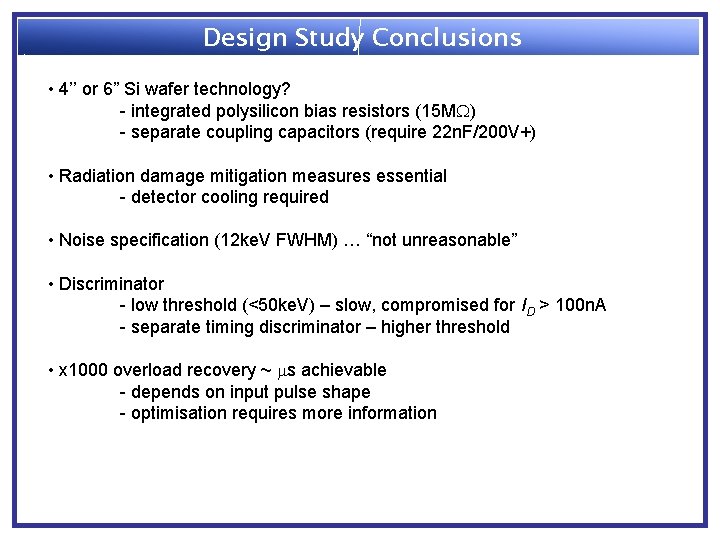

Design Study Conclusions • 4’’ or 6” Si wafer technology? - integrated polysilicon bias resistors (15 MW) - separate coupling capacitors (require 22 n. F/200 V+) • Radiation damage mitigation measures essential - detector cooling required • Noise specification (12 ke. V FWHM) … “not unreasonable” • Discriminator - low threshold (<50 ke. V) – slow, compromised for ID > 100 n. A - separate timing discriminator – higher threshold • x 1000 overload recovery ~ ms achievable - depends on input pulse shape - optimisation requires more information

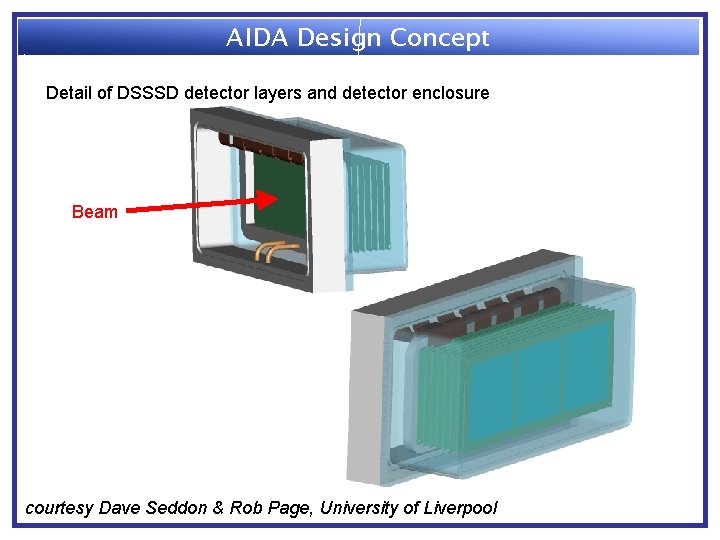

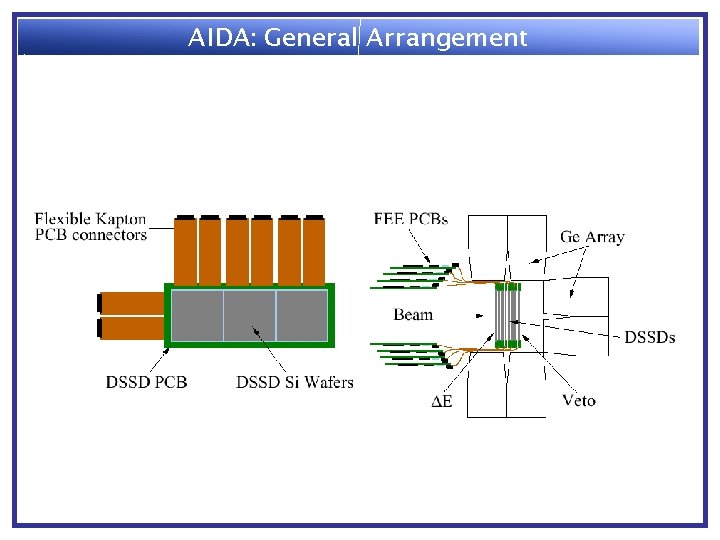

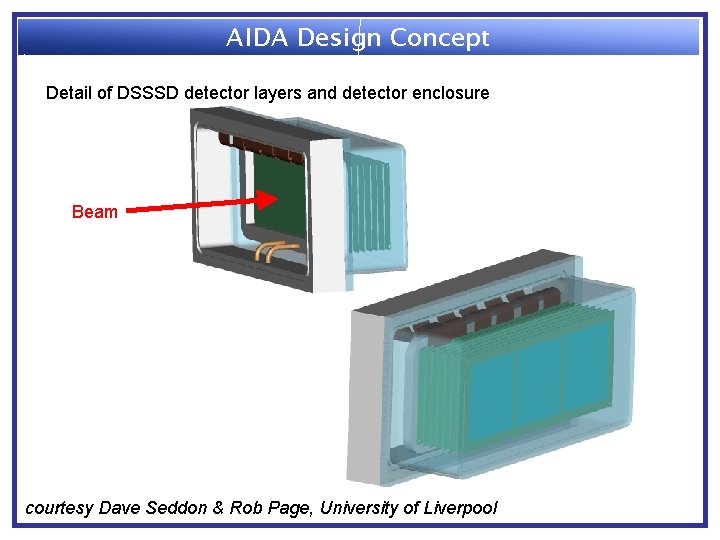

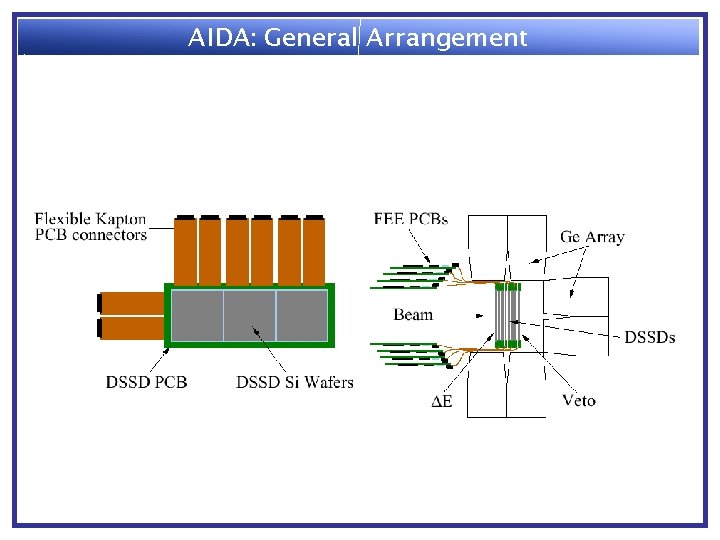

AIDA Design Concept Detail of DSSSD detector layers and detector enclosure Beam courtesy Dave Seddon & Rob Page, University of Liverpool

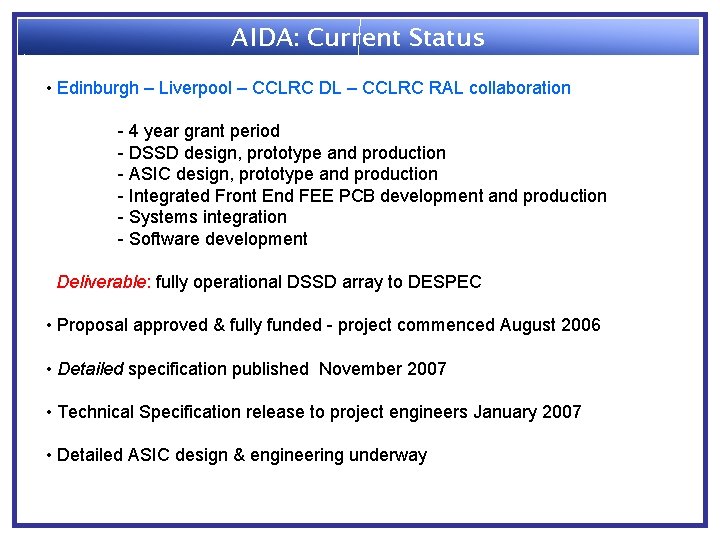

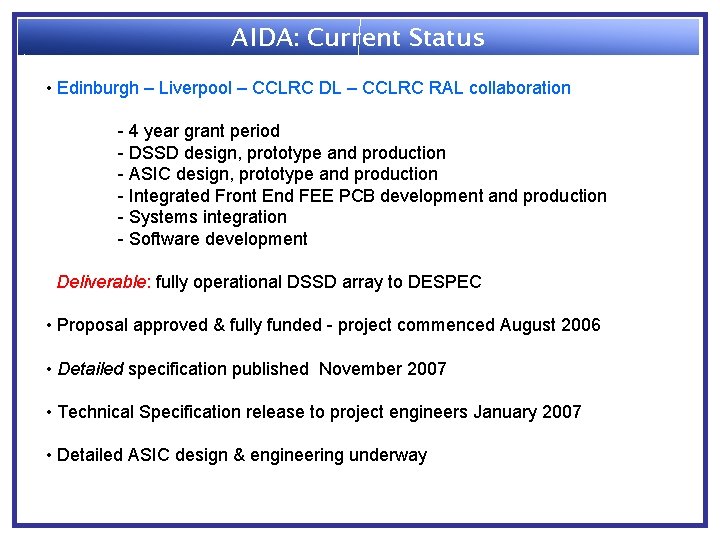

AIDA: Current Status • Edinburgh – Liverpool – CCLRC DL – CCLRC RAL collaboration - 4 year grant period - DSSD design, prototype and production - ASIC design, prototype and production - Integrated Front End FEE PCB development and production - Systems integration - Software development Deliverable: fully operational DSSD array to DESPEC • Proposal approved & fully funded - project commenced August 2006 • Detailed specification published November 2007 • Technical Specification release to project engineers January 2007 • Detailed ASIC design & engineering underway

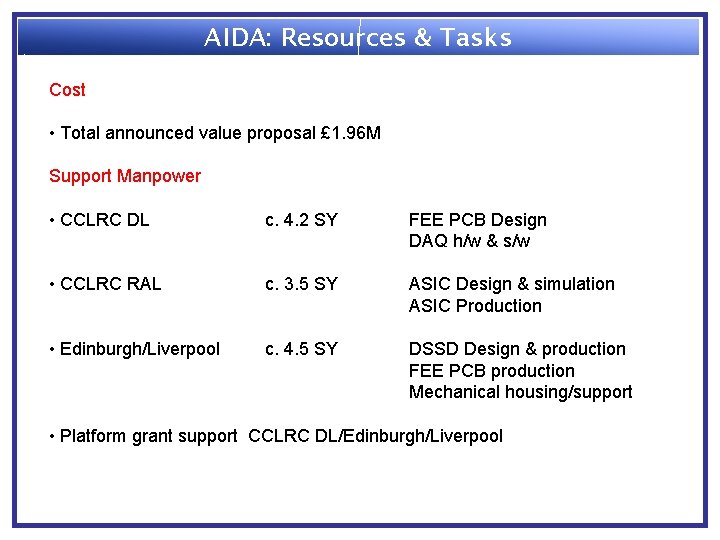

AIDA: Resources & Tasks Cost • Total announced value proposal £ 1. 96 M Support Manpower • CCLRC DL c. 4. 2 SY FEE PCB Design DAQ h/w & s/w • CCLRC RAL c. 3. 5 SY ASIC Design & simulation ASIC Production • Edinburgh/Liverpool c. 4. 5 SY DSSD Design & production FEE PCB production Mechanical housing/support • Platform grant support CCLRC DL/Edinburgh/Liverpool

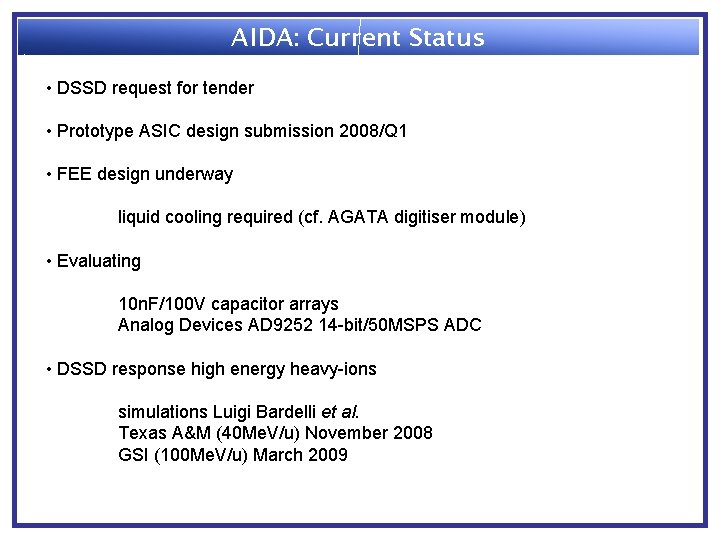

AIDA: Current Status • DSSD request for tender • Prototype ASIC design submission 2008/Q 1 • FEE design underway liquid cooling required (cf. AGATA digitiser module) • Evaluating 10 n. F/100 V capacitor arrays Analog Devices AD 9252 14 -bit/50 MSPS ADC • DSSD response high energy heavy-ions simulations Luigi Bardelli et al. Texas A&M (40 Me. V/u) November 2008 GSI (100 Me. V/u) March 2009

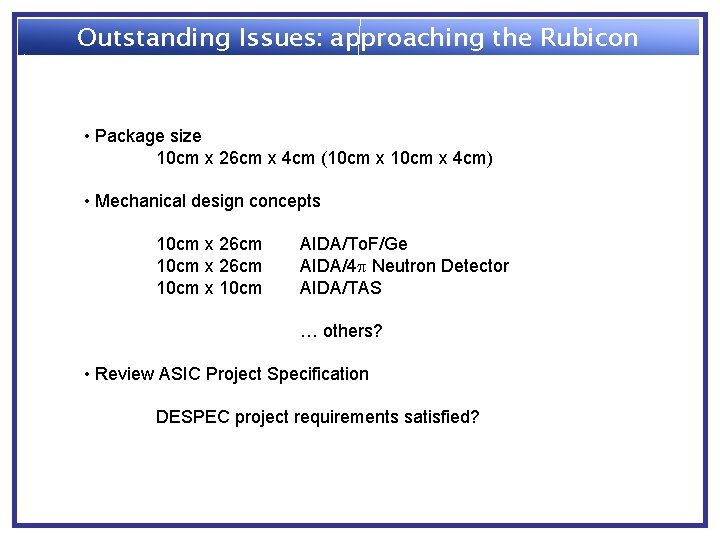

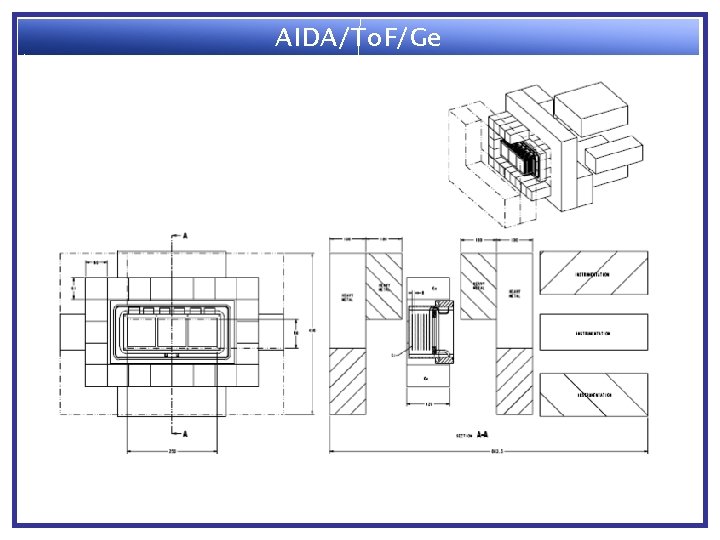

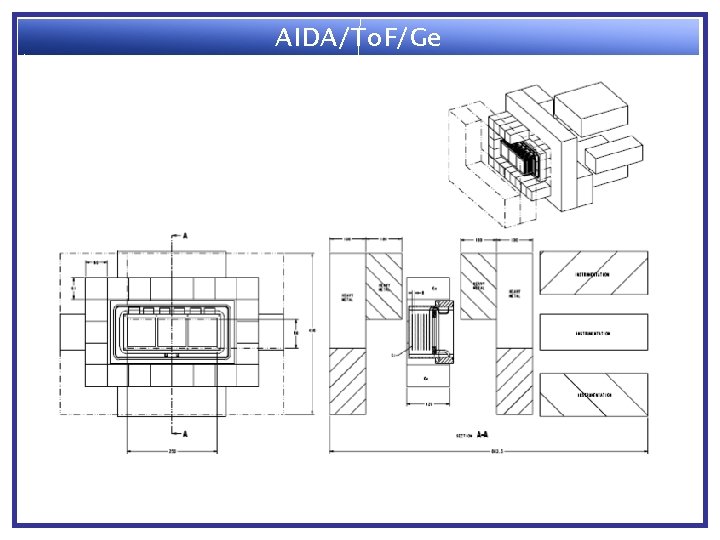

Outstanding Issues: approaching the Rubicon • Package size 10 cm x 26 cm x 4 cm (10 cm x 4 cm) • Mechanical design concepts 10 cm x 26 cm 10 cm x 10 cm AIDA/To. F/Ge AIDA/4 p Neutron Detector AIDA/TAS … others? • Review ASIC Project Specification DESPEC project requirements satisfied?

AIDA/To. F/Ge

AIDA/4 p Neutron (NERO)

AIDA/TAS

AIDA Project Information Project web site http: //www. ph. ed. ac. uk/~td/AIDA/welcome. html Design Documents http: //www. ph. ed. ac. uk/~td/AIDA/Design/design. html Project Technical Specification ASIC Project Specification v 1. 3 FEE Specification v 0. 5 The University of Edinburgh (lead RO) Phil Woods et al. The University of Liverpool Rob Page et al. STFC DL & RAL John Simpson et al. Project Manager: Tom Davinson

Acknowledgements This presentation includes material from other people Thanks to: Ian Lazarus & Patrick Coleman-Smith (STFC DL) Steve Thomas (STFC RAL) Dave Seddon & Rob Page (University of Liverpool) Berta Rubio (IFIC, CSIC University of Valencia)

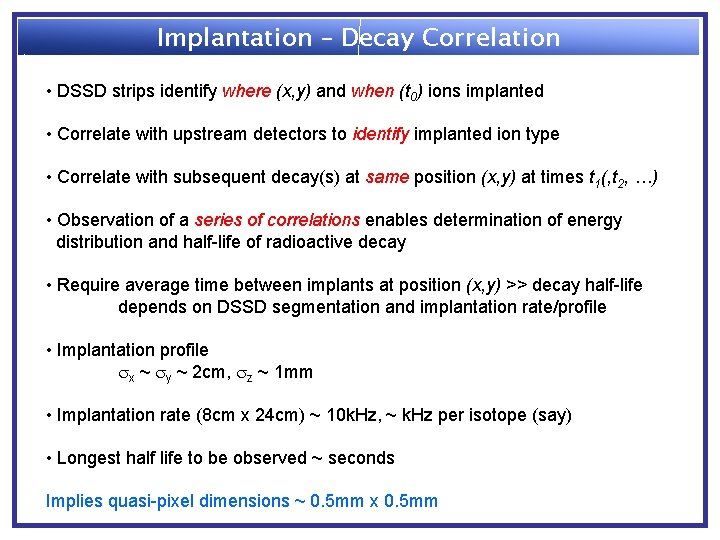

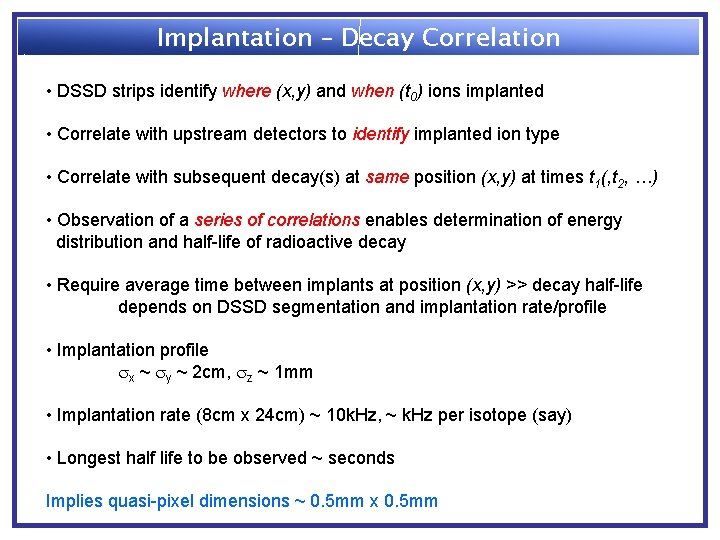

Implantation – Decay Correlation • DSSD strips identify where (x, y) and when (t 0) ions implanted • Correlate with upstream detectors to identify implanted ion type • Correlate with subsequent decay(s) at same position (x, y) at times t 1(, t 2, …) • Observation of a series of correlations enables determination of energy distribution and half-life of radioactive decay • Require average time between implants at position (x, y) >> decay half-life depends on DSSD segmentation and implantation rate/profile • Implantation profile sx ~ sy ~ 2 cm, sz ~ 1 mm • Implantation rate (8 cm x 24 cm) ~ 10 k. Hz, ~ k. Hz per isotope (say) • Longest half life to be observed ~ seconds Implies quasi-pixel dimensions ~ 0. 5 mm x 0. 5 mm

AIDA: General Arrangement

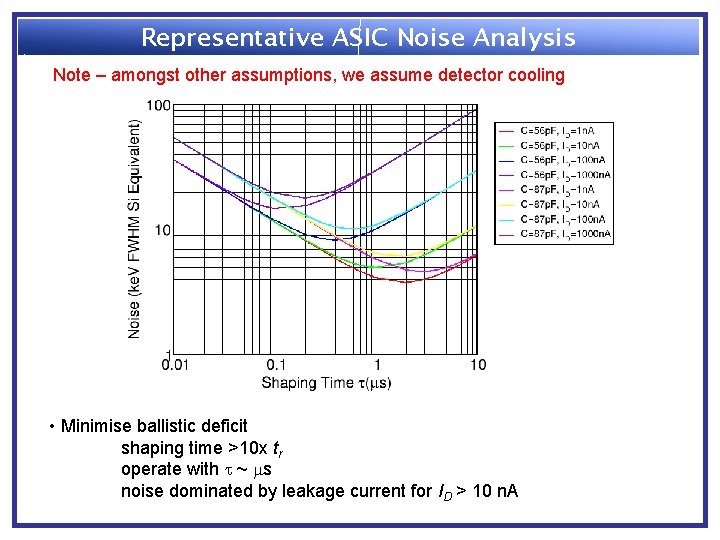

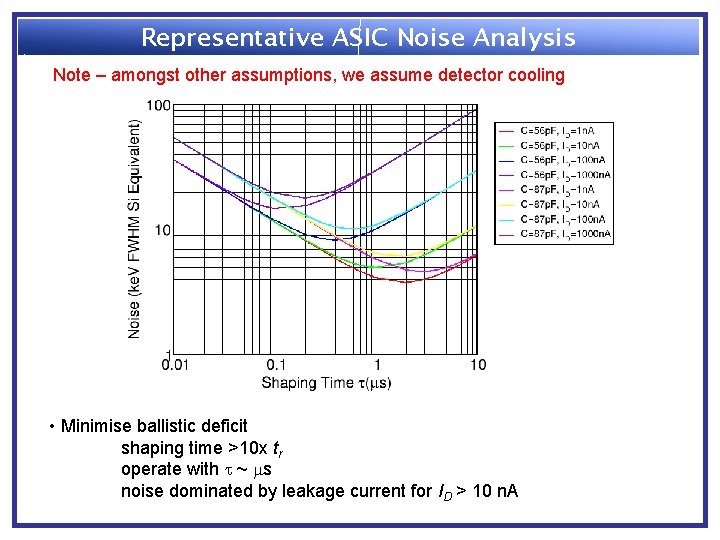

Representative ASIC Noise Analysis Note – amongst other assumptions, we assume detector cooling • Minimise ballistic deficit shaping time >10 x tr operate with t ~ ms noise dominated by leakage current for ID > 10 n. A

AIDA: Workplan

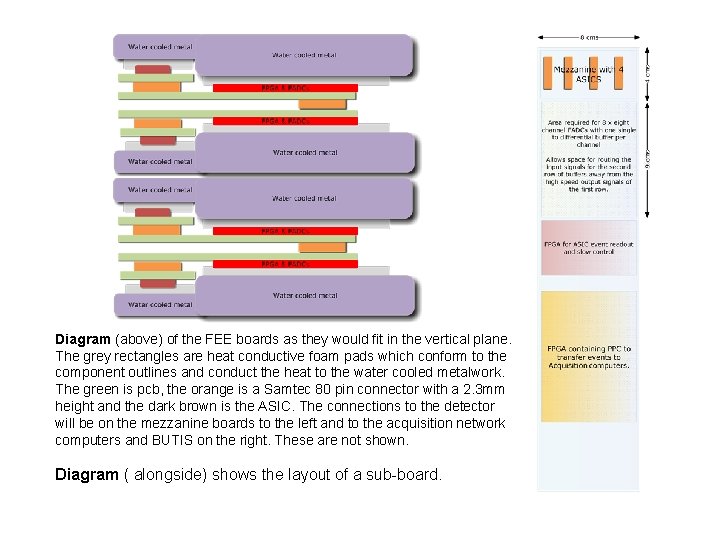

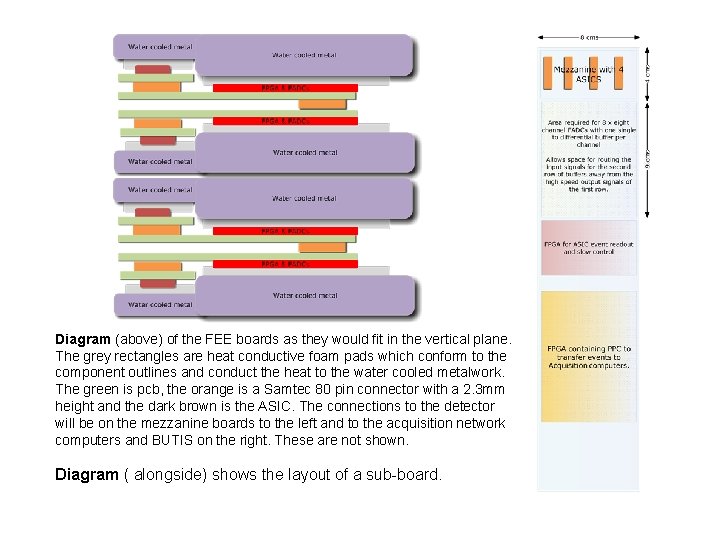

Diagram (above) of the FEE boards as they would fit in the vertical plane. The grey rectangles are heat conductive foam pads which conform to the component outlines and conduct the heat to the water cooled metalwork. The green is pcb, the orange is a Samtec 80 pin connector with a 2. 3 mm height and the dark brown is the ASIC. The connections to the detector will be on the mezzanine boards to the left and to the acquisition network computers and BUTIS on the right. These are not shown. Diagram ( alongside) shows the layout of a sub-board.