Tutorial ITI 1100 Dewan Tanvir Ahmed SITE Uof

- Slides: 32

Tutorial: ITI 1100 Dewan Tanvir Ahmed SITE, Uof. O 1

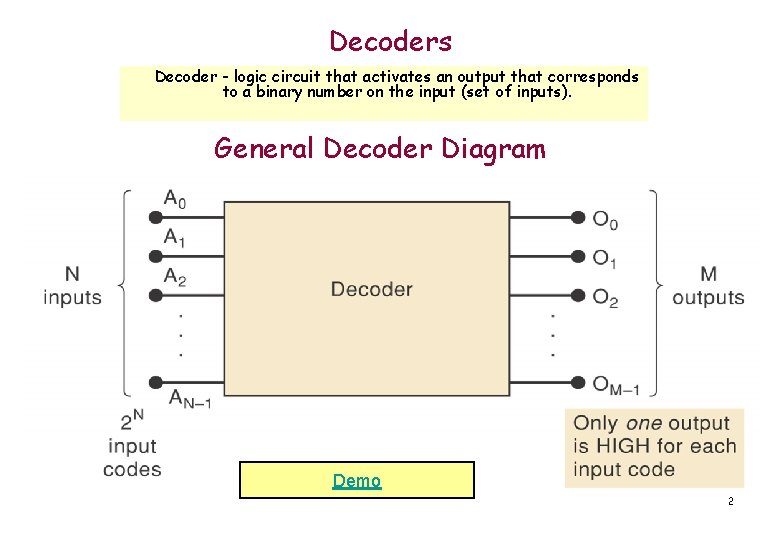

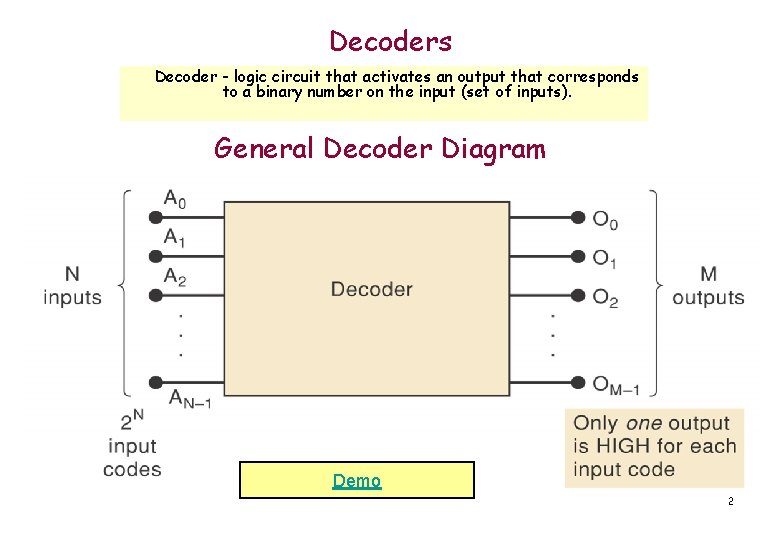

Decoders Decoder - logic circuit that activates an output that corresponds to a binary number on the input (set of inputs). General Decoder Diagram Demo 2

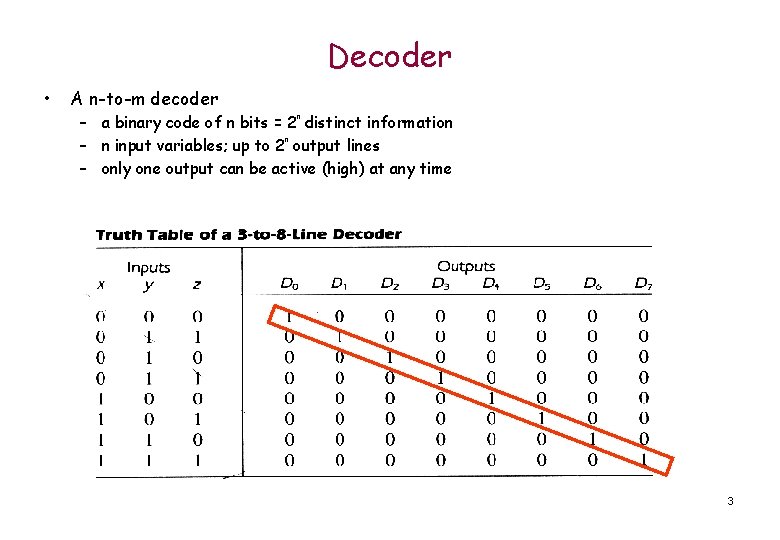

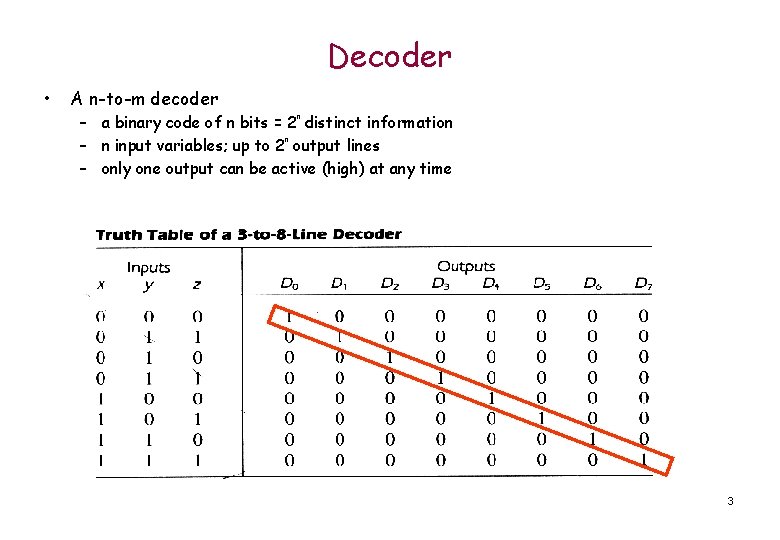

Decoder • A n-to-m decoder n – a binary code of n bits = 2 distinct information n – n input variables; up to 2 output lines – only one output can be active (high) at any time 3

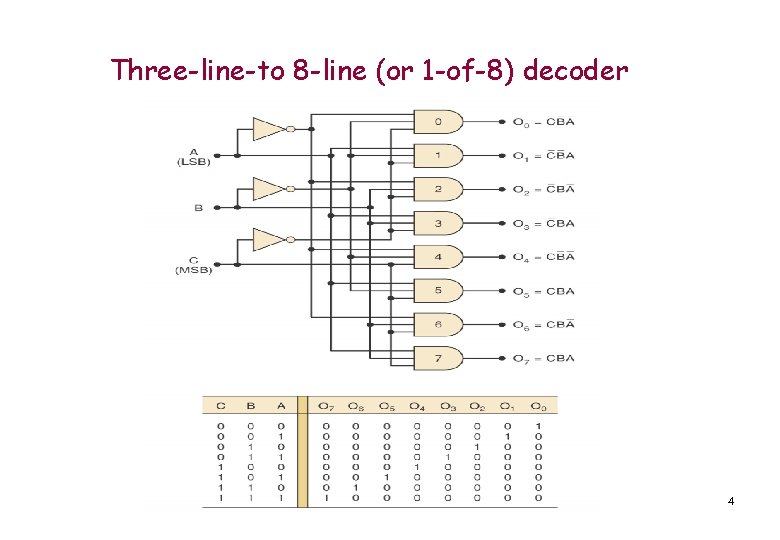

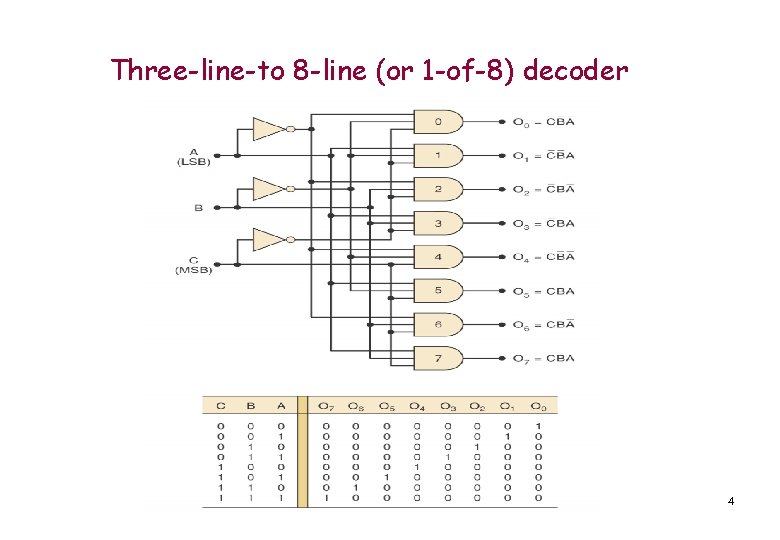

Three-line-to 8 -line (or 1 -of-8) decoder 4

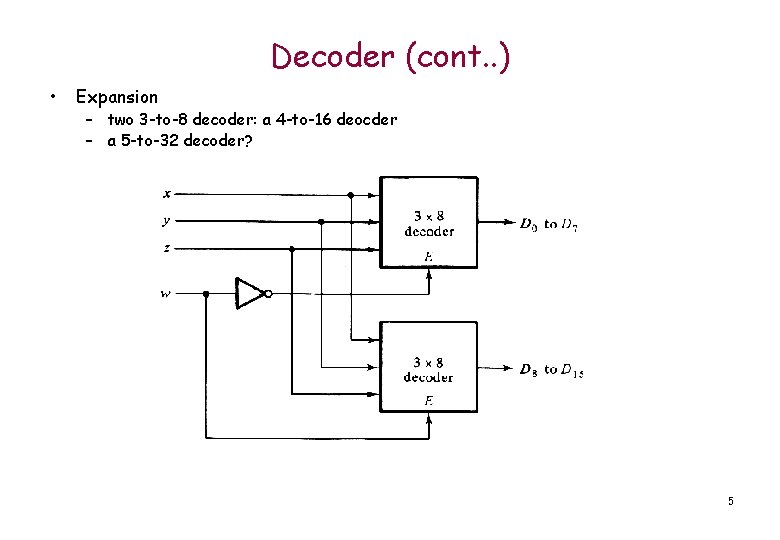

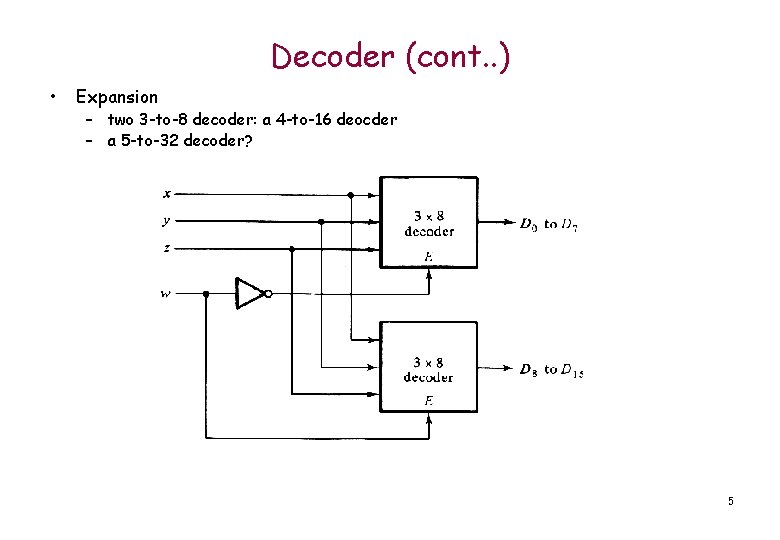

Decoder (cont. . ) • Expansion – two 3 -to-8 decoder: a 4 -to-16 deocder – a 5 -to-32 decoder? 5

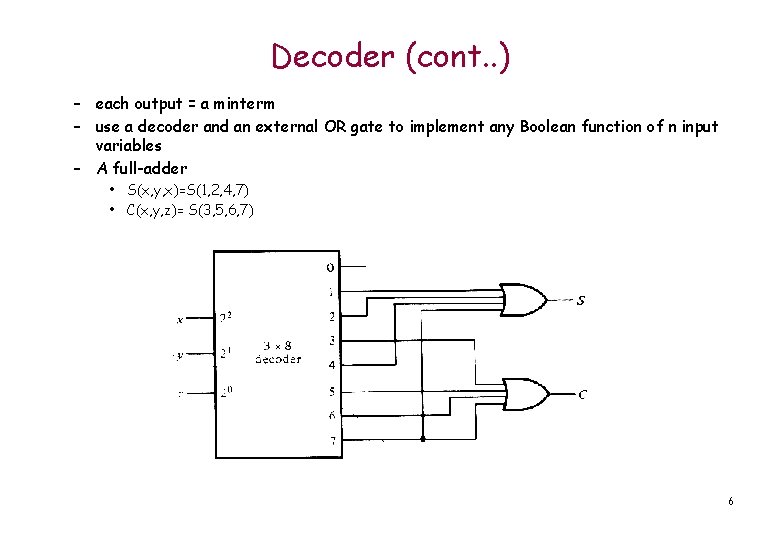

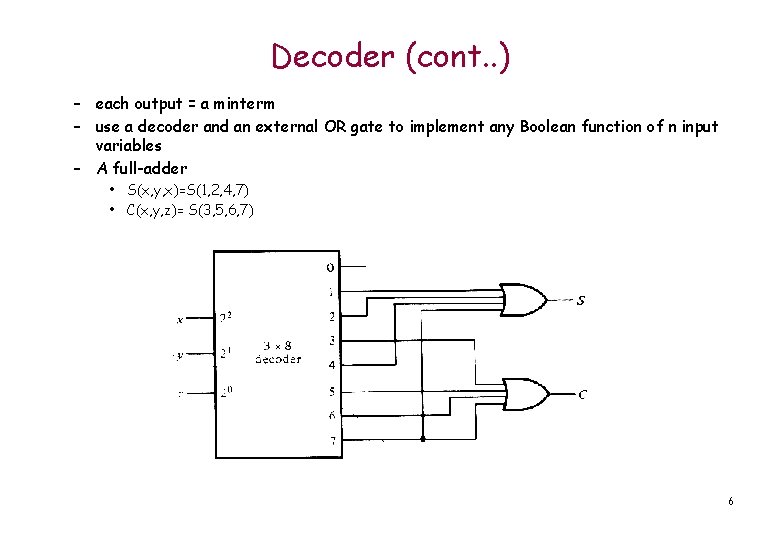

Decoder (cont. . ) – each output = a minterm – use a decoder and an external OR gate to implement any Boolean function of n input variables – A full-adder • S(x, y, x)=S(1, 2, 4, 7) • C(x, y, z)= S(3, 5, 6, 7) 6

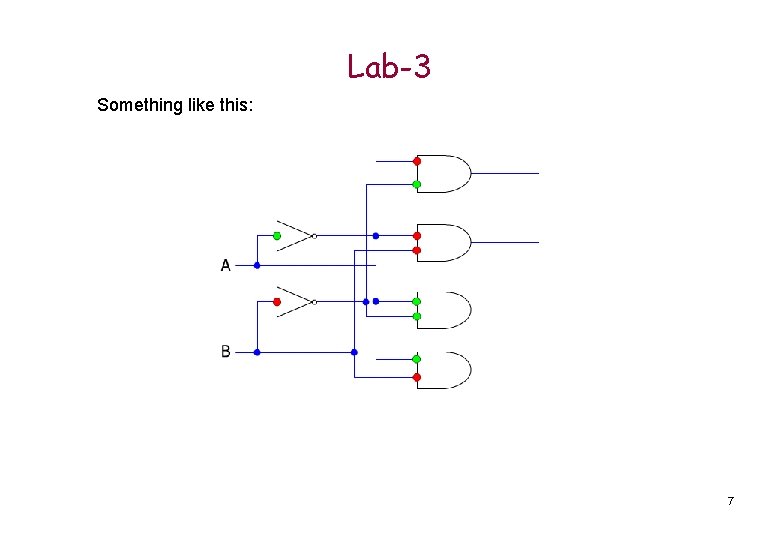

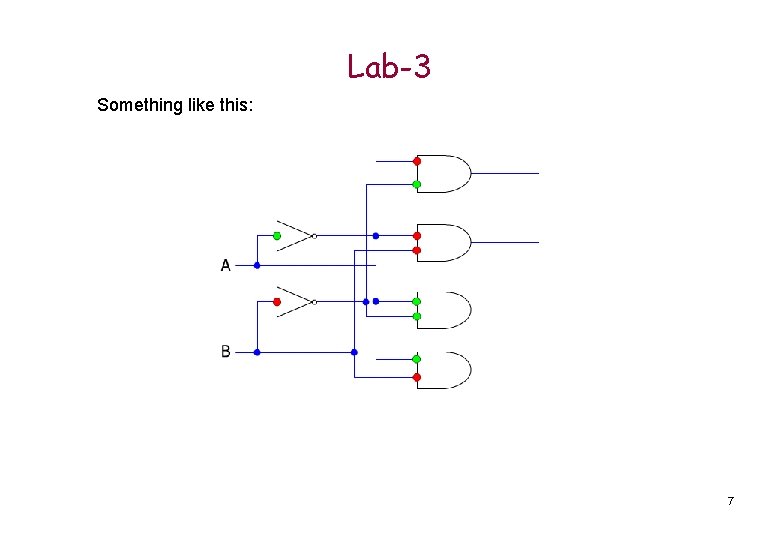

Lab-3 Something like this: 7

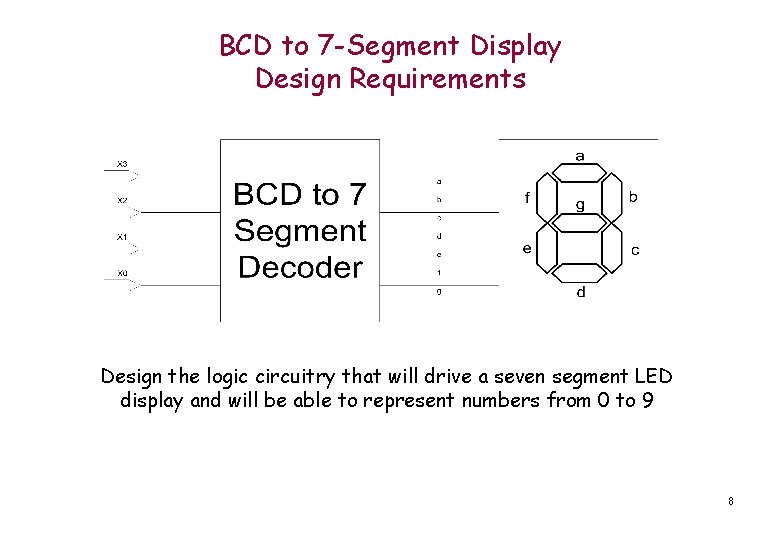

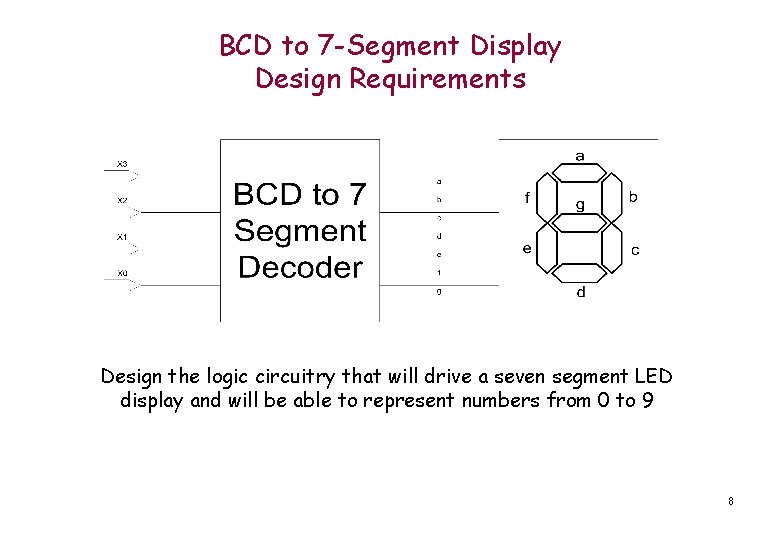

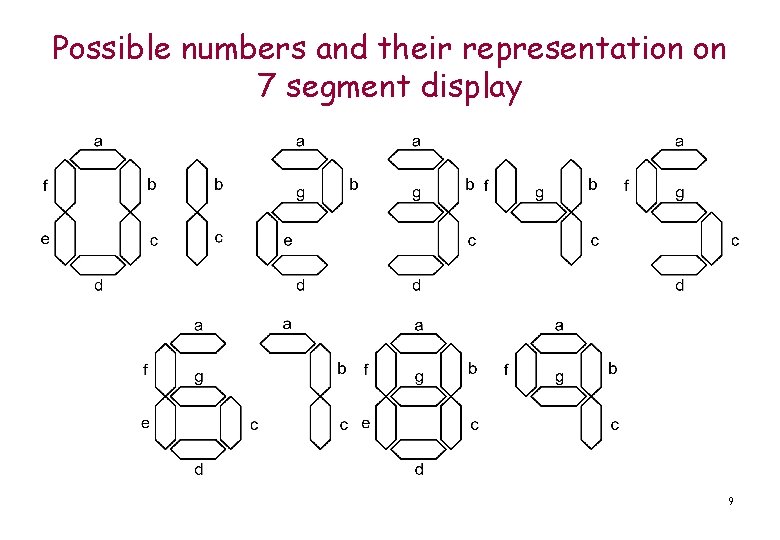

BCD to 7 -Segment Display Design Requirements Design the logic circuitry that will drive a seven segment LED display and will be able to represent numbers from 0 to 9 8

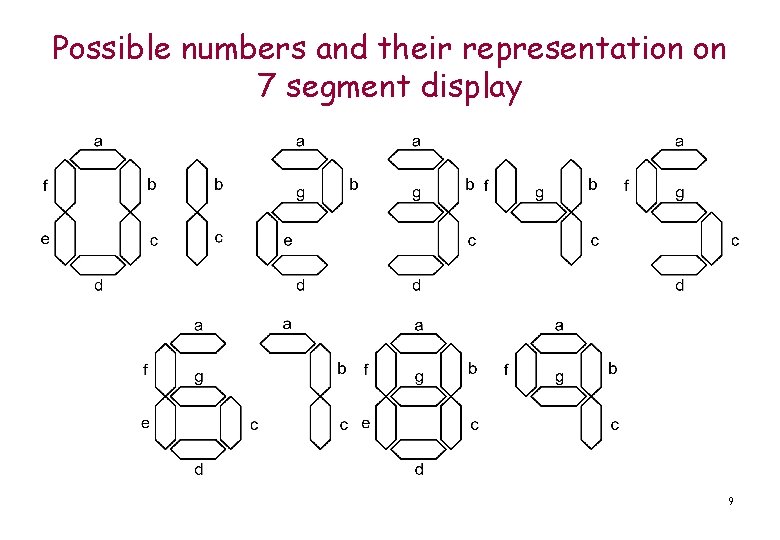

Possible numbers and their representation on 7 segment display 9

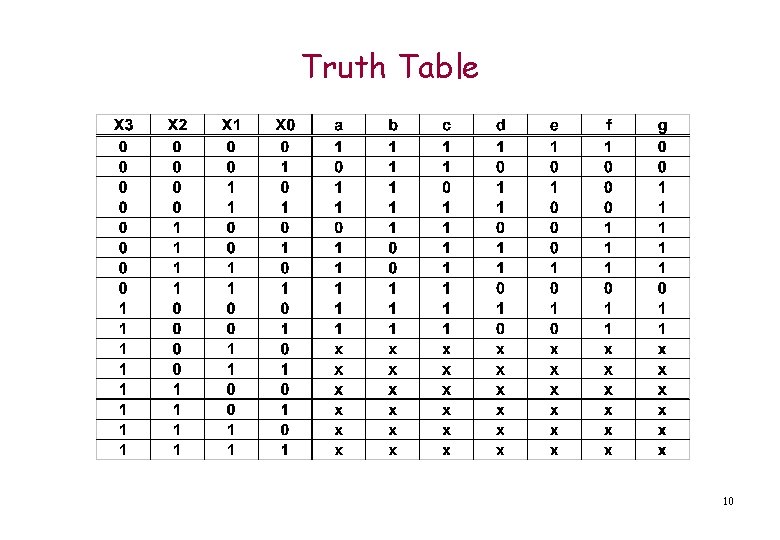

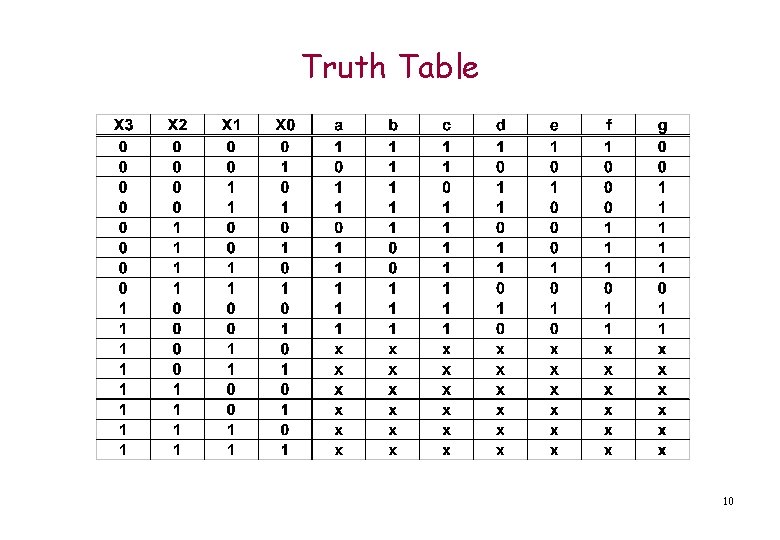

Truth Table 10

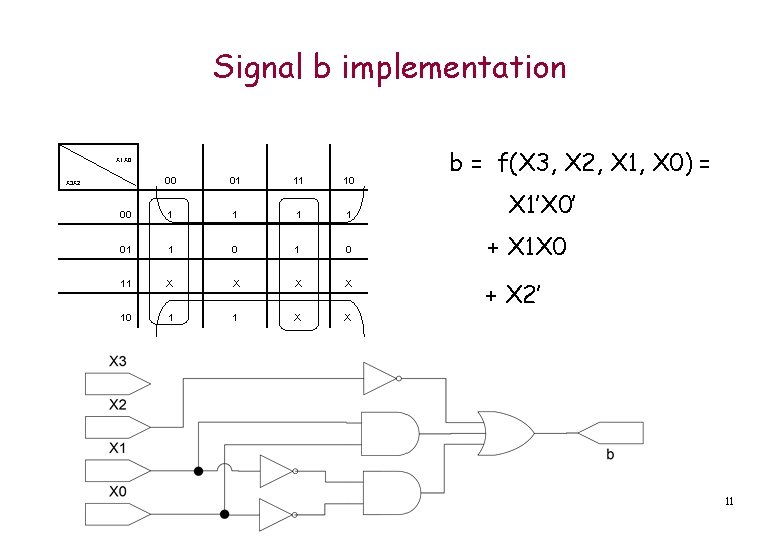

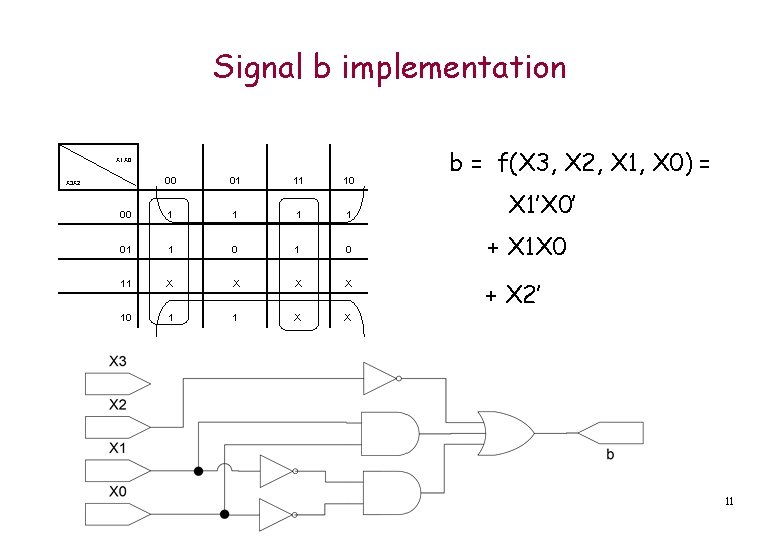

Signal b implementation X 1 X 0 00 01 11 10 00 1 1 1 01 1 0 1 11 X X X X 10 1 X X X 3 X 2 1 1 0 b = f(X 3, X 2, X 1, X 0) = X 1’X 0’ + X 1 X 0 + X 2’ 11

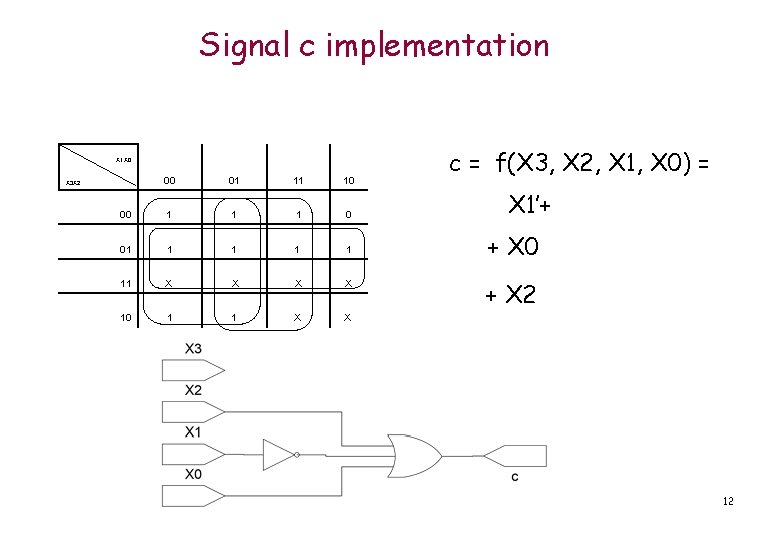

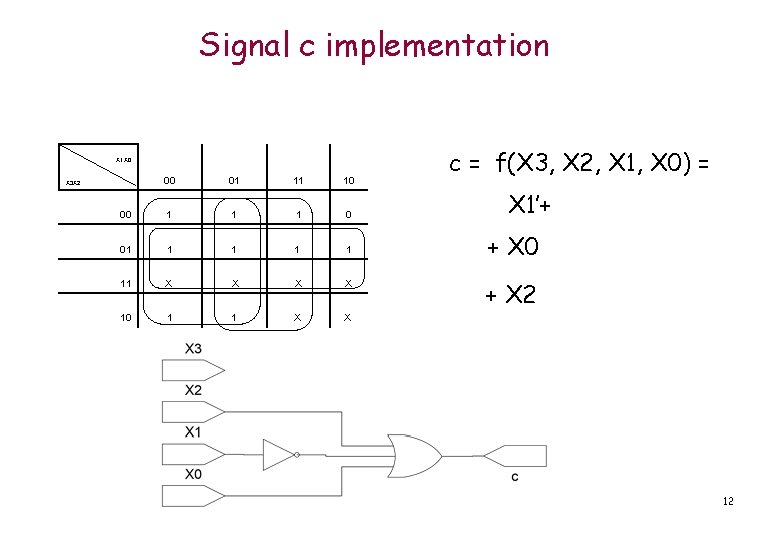

Signal c implementation X 1 X 0 00 01 11 10 00 1 1 1 01 1 11 X X X X 10 1 X X X 3 X 2 1 0 1 c = f(X 3, X 2, X 1, X 0) = X 1’+ + X 0 + X 2 12

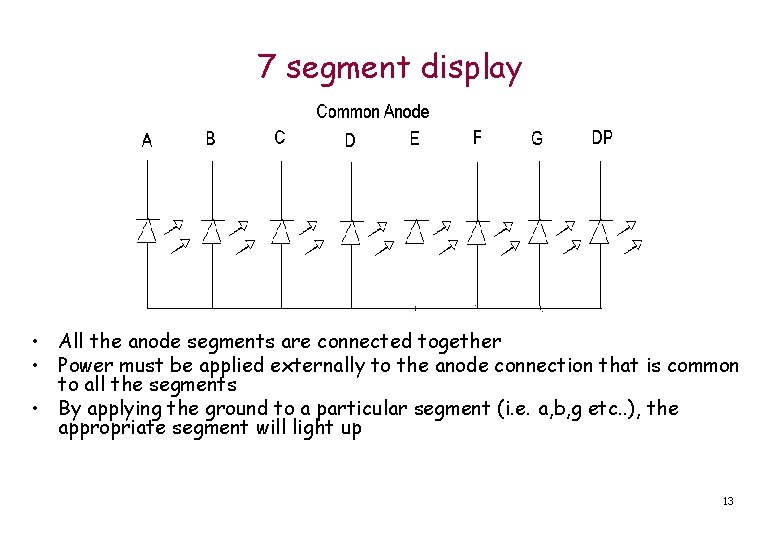

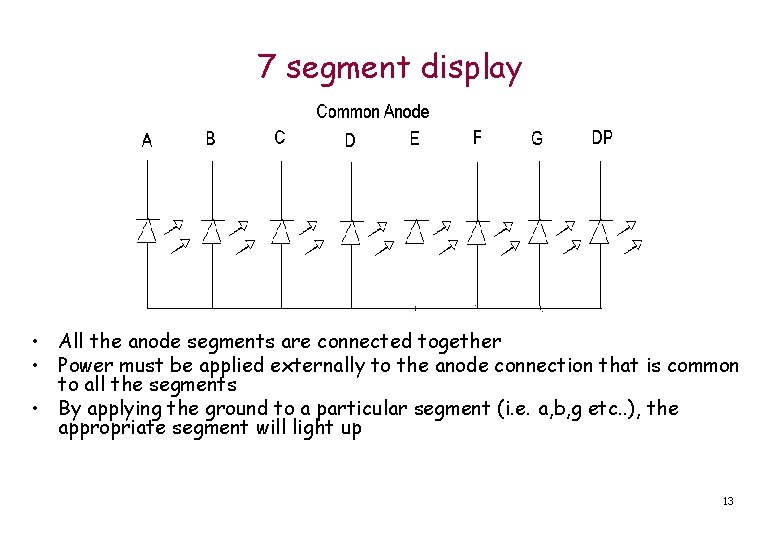

7 segment display • All the anode segments are connected together • Power must be applied externally to the anode connection that is common to all the segments • By applying the ground to a particular segment (i. e. a, b, g etc. . ), the appropriate segment will light up 13

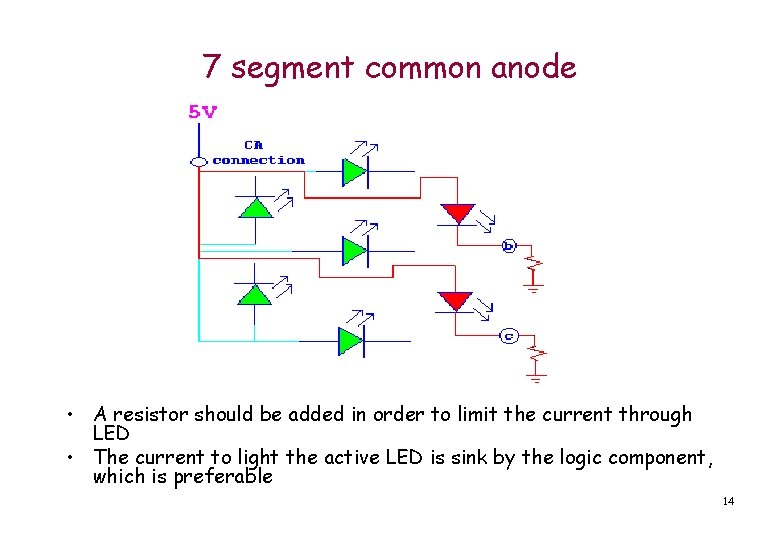

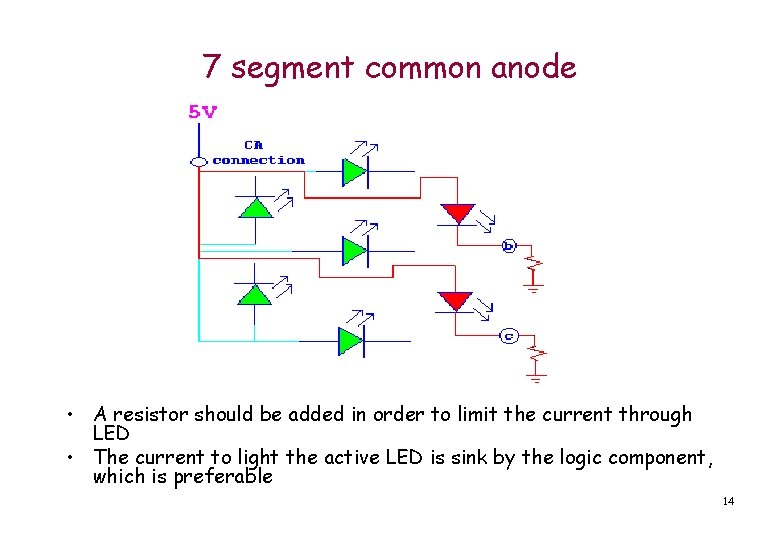

7 segment common anode • A resistor should be added in order to limit the current through LED • The current to light the active LED is sink by the logic component, which is preferable 14

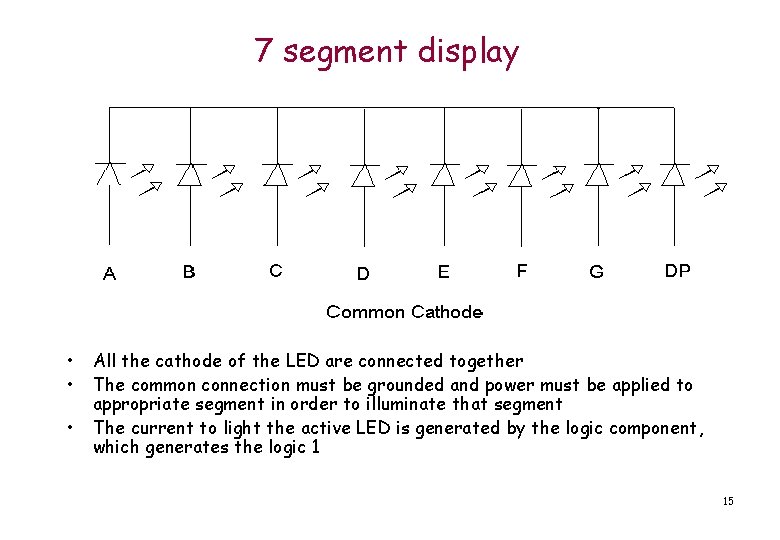

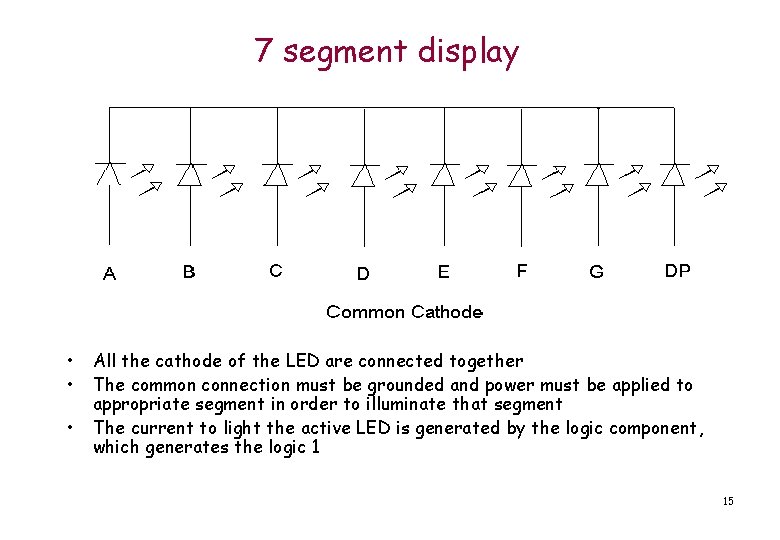

7 segment display • • • All the cathode of the LED are connected together The common connection must be grounded and power must be applied to appropriate segment in order to illuminate that segment The current to light the active LED is generated by the logic component, which generates the logic 1 15

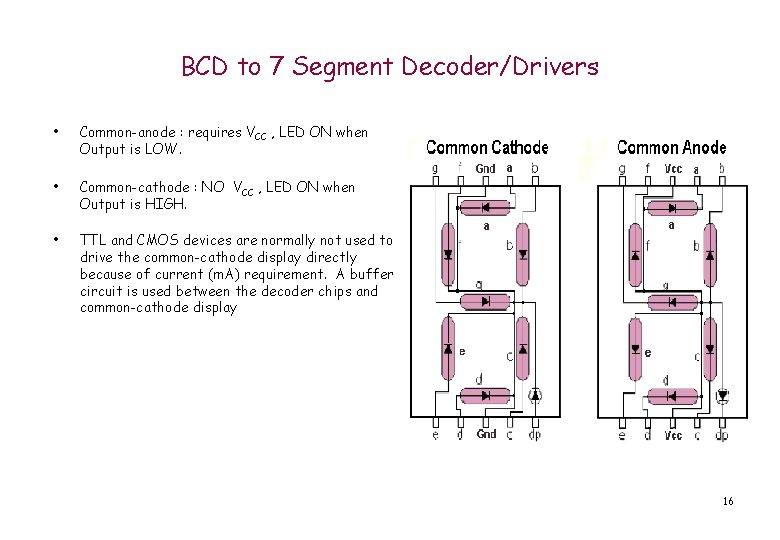

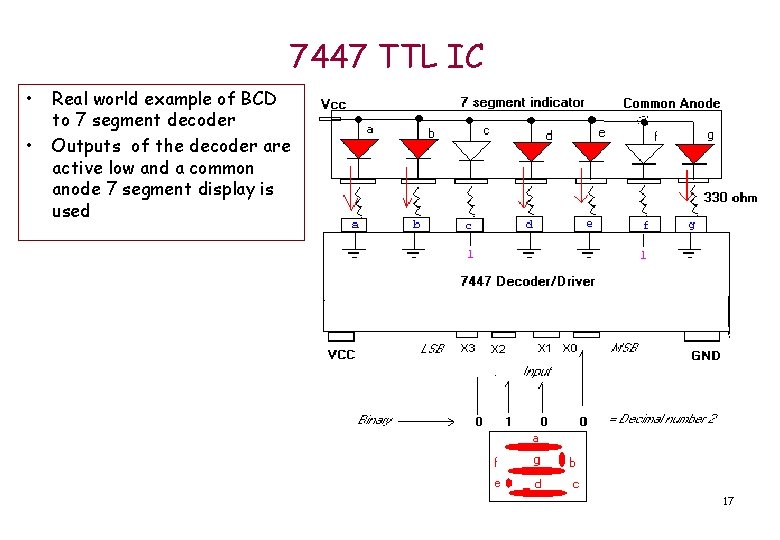

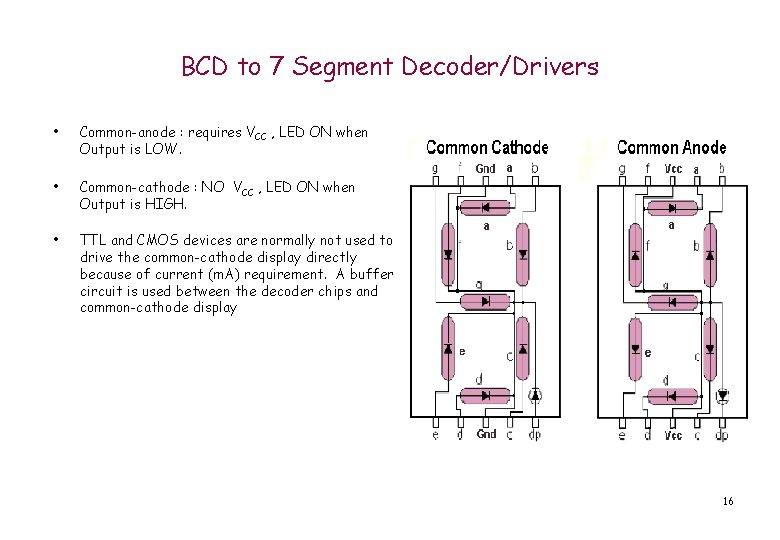

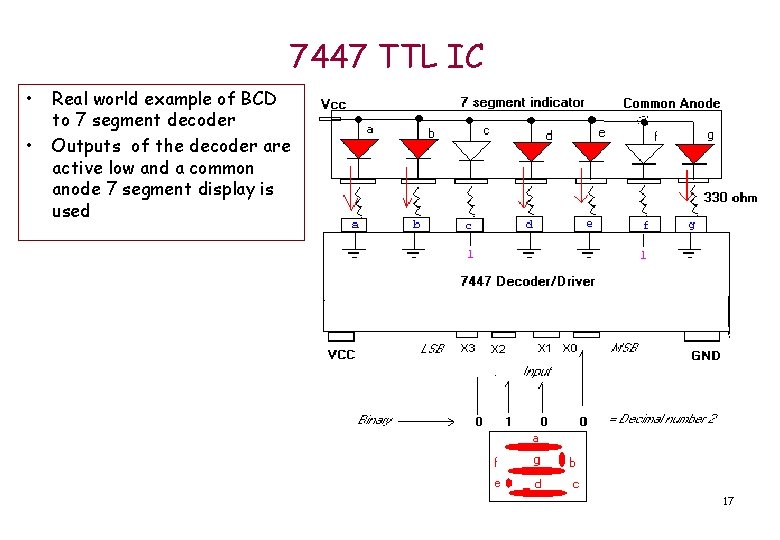

BCD to 7 Segment Decoder/Drivers • Common-anode : requires VCC , LED ON when Output is LOW. • Common-cathode : NO VCC , LED ON when Output is HIGH. • TTL and CMOS devices are normally not used to drive the common-cathode display directly because of current (m. A) requirement. A buffer circuit is used between the decoder chips and common-cathode display 16

7447 TTL IC • • Real world example of BCD to 7 segment decoder Outputs of the decoder are active low and a common anode 7 segment display is used 17

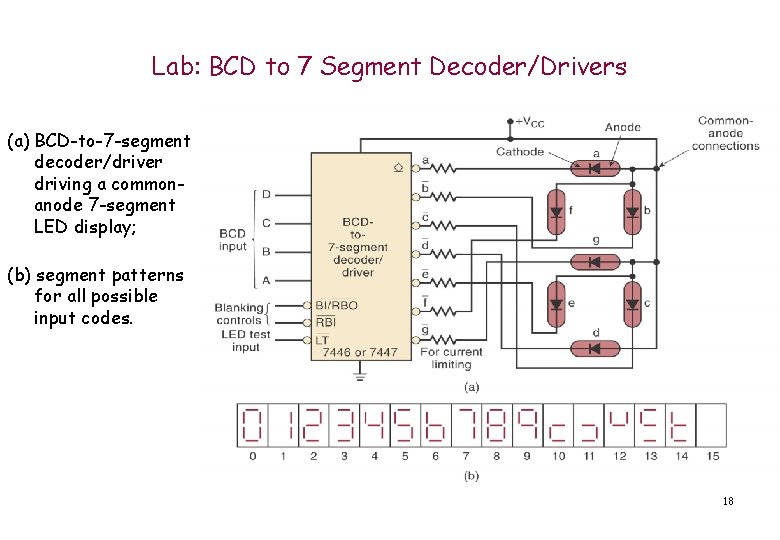

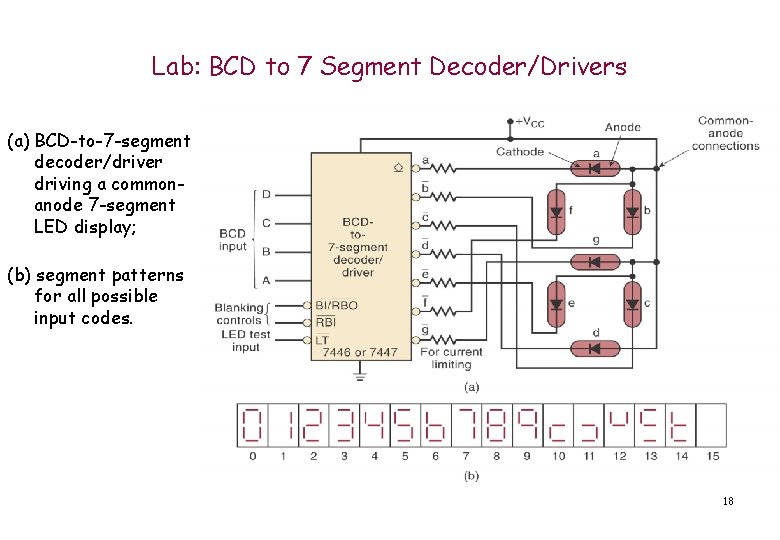

Lab: BCD to 7 Segment Decoder/Drivers (a) BCD-to-7 -segment decoder/driver driving a commonanode 7 -segment LED display; (b) segment patterns for all possible input codes. 18

Multiplexers (Data Selectors) • • A multiplexer (MUX) selects one of multiple input signals and passes it to the output. The basic two input multiplexer The four input multiplexer The eight input multiplexer 19

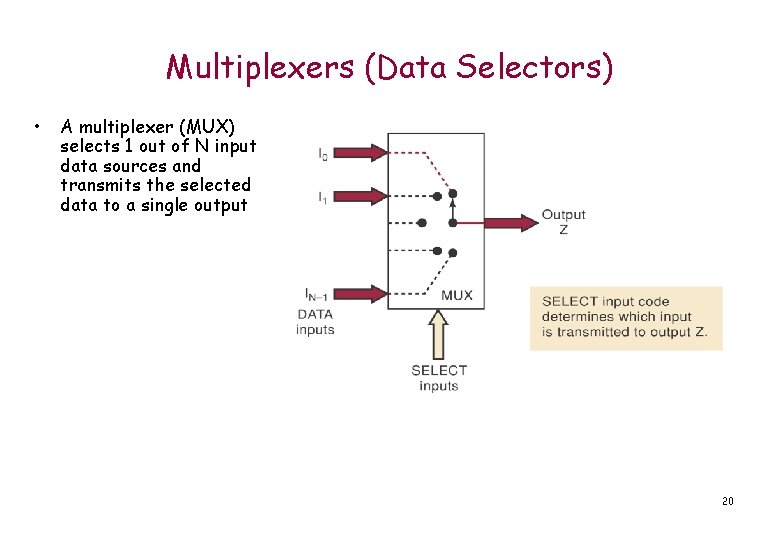

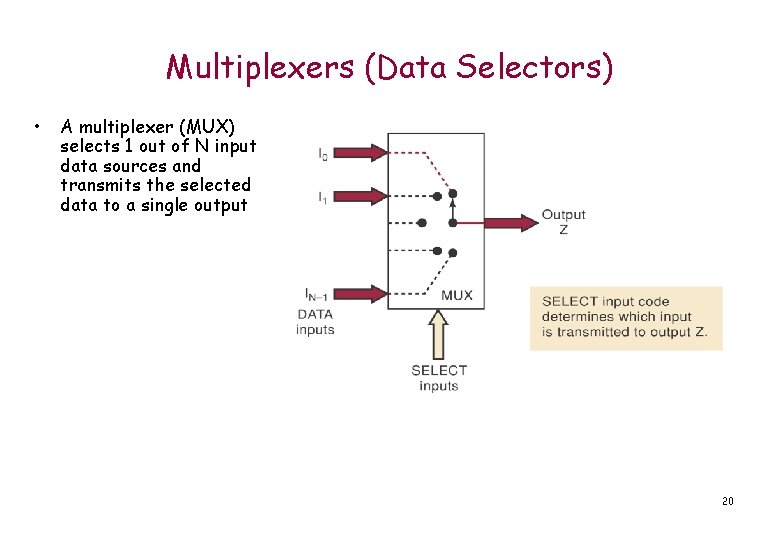

Multiplexers (Data Selectors) • A multiplexer (MUX) selects 1 out of N input data sources and transmits the selected data to a single output 20

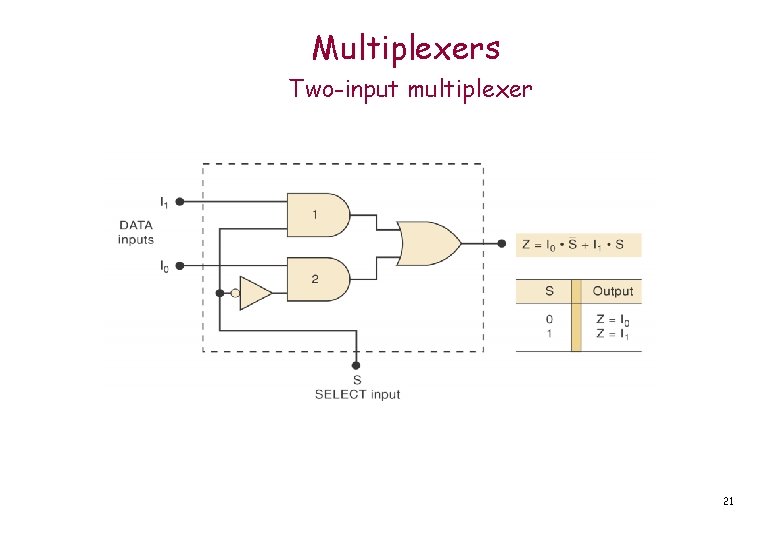

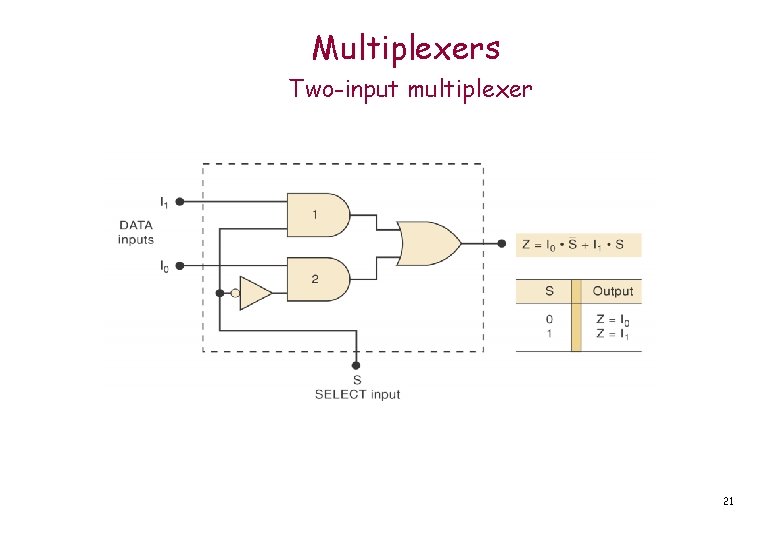

Multiplexers Two-input multiplexer 21

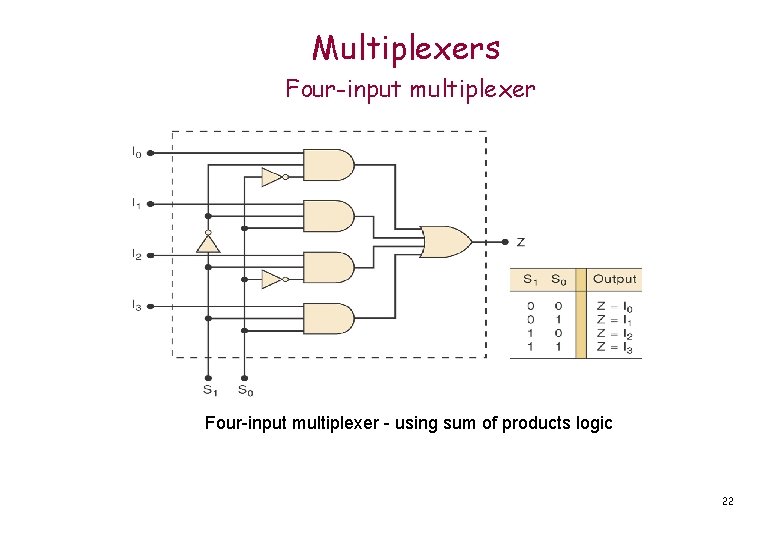

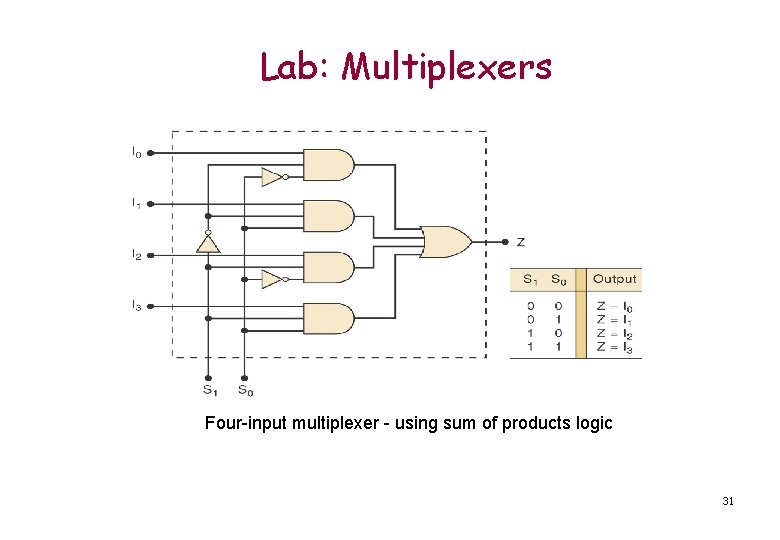

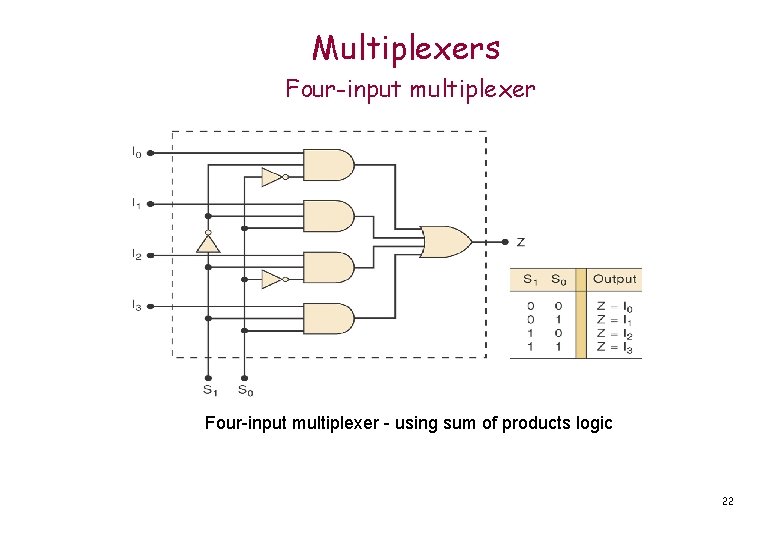

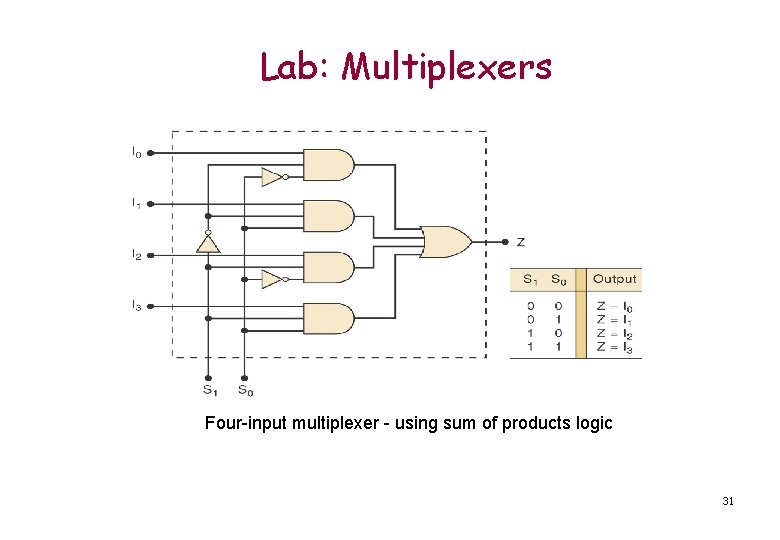

Multiplexers Four-input multiplexer - using sum of products logic 22

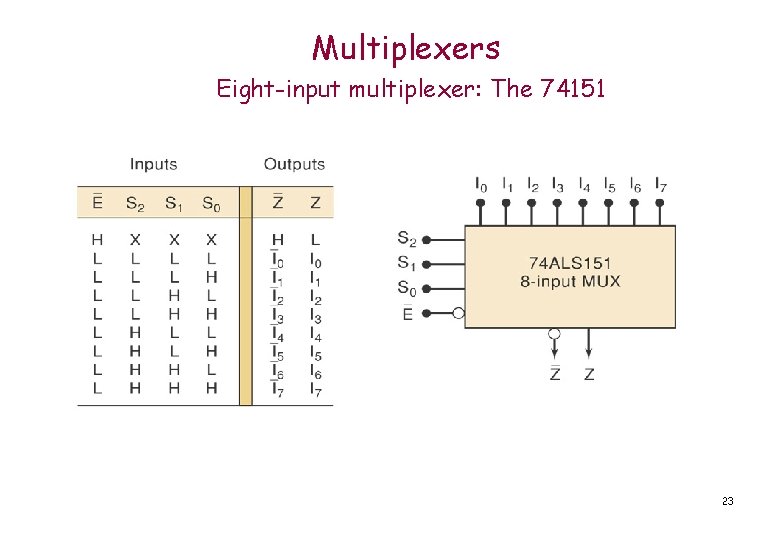

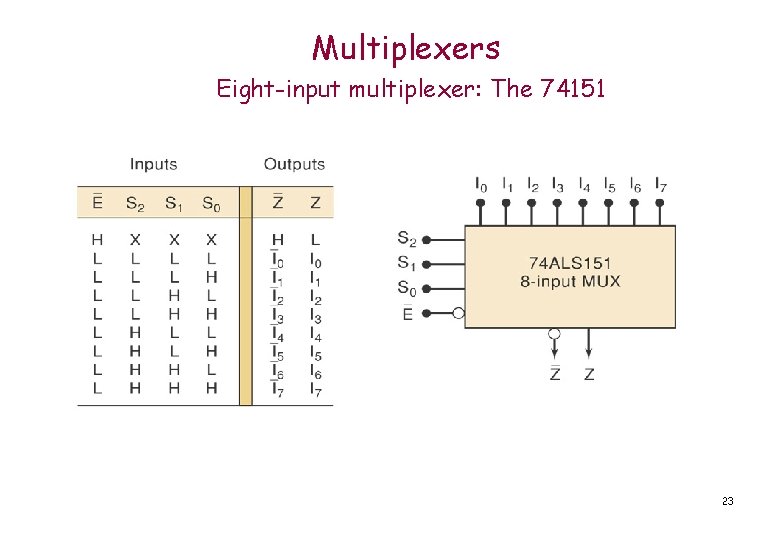

Multiplexers Eight-input multiplexer: The 74151 23

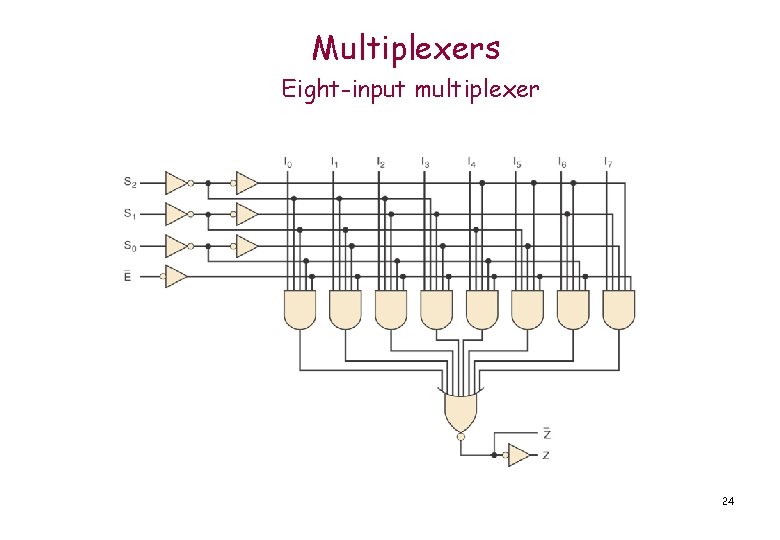

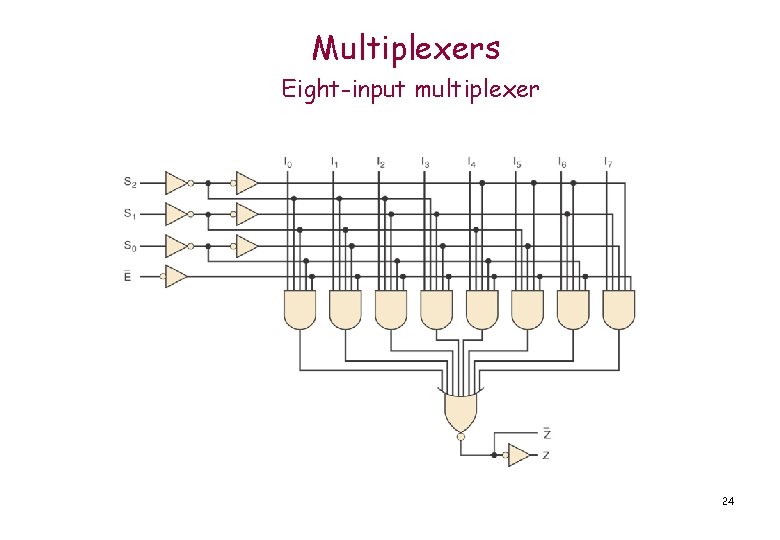

Multiplexers Eight-input multiplexer 24

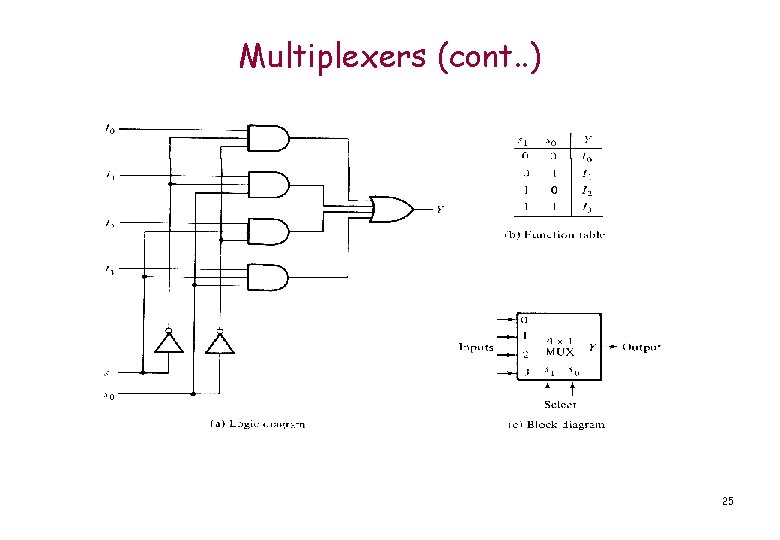

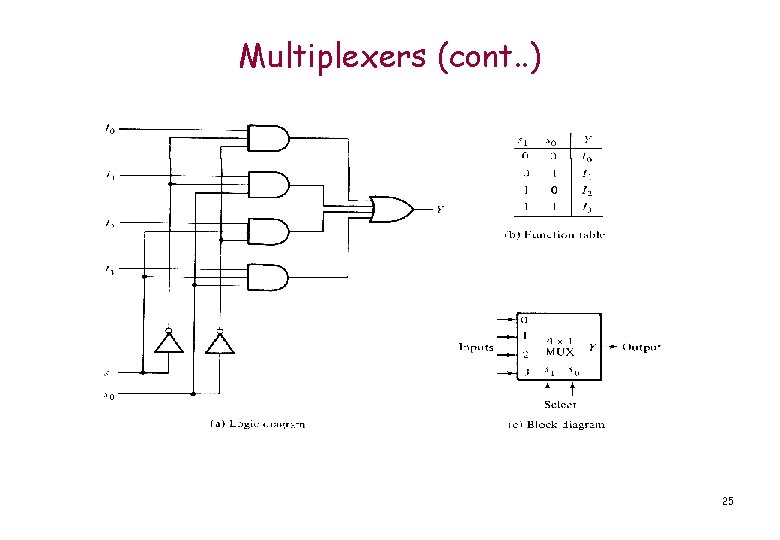

Multiplexers (cont. . ) 25

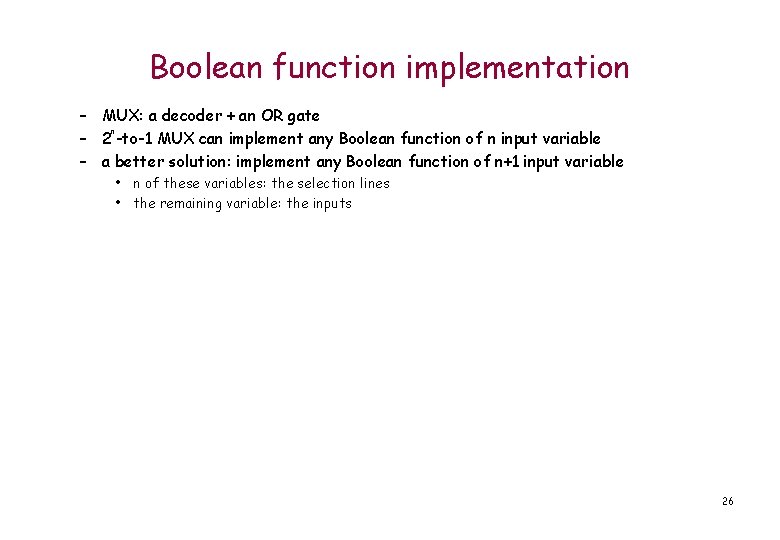

Boolean function implementation – MUX: a decoder + an OR gate n – 2 -to-1 MUX can implement any Boolean function of n input variable – a better solution: implement any Boolean function of n+1 input variable • n of these variables: the selection lines • the remaining variable: the inputs 26

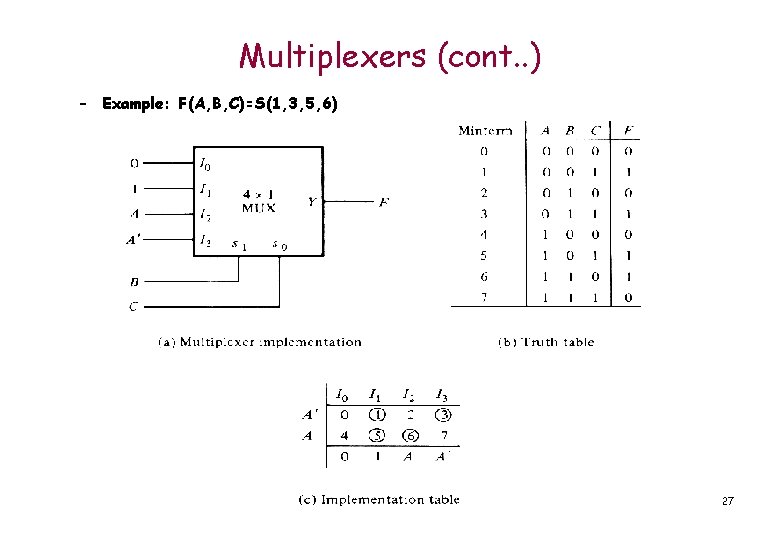

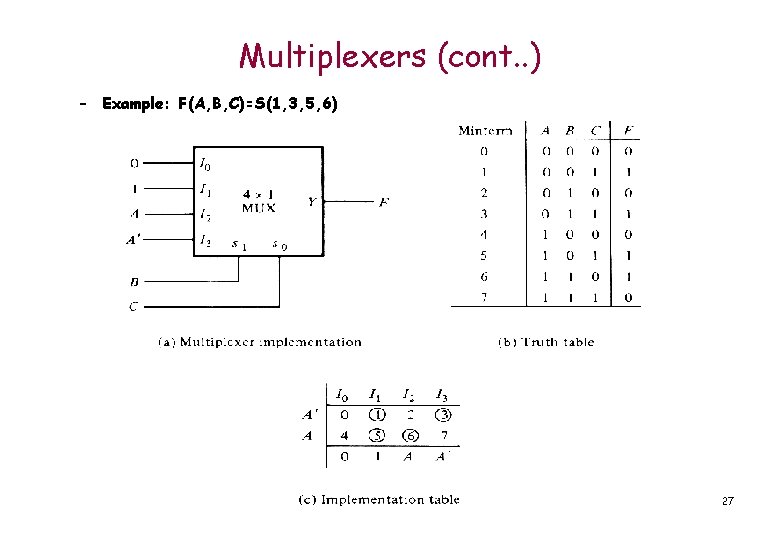

Multiplexers (cont. . ) – Example: F(A, B, C)=S(1, 3, 5, 6) 27

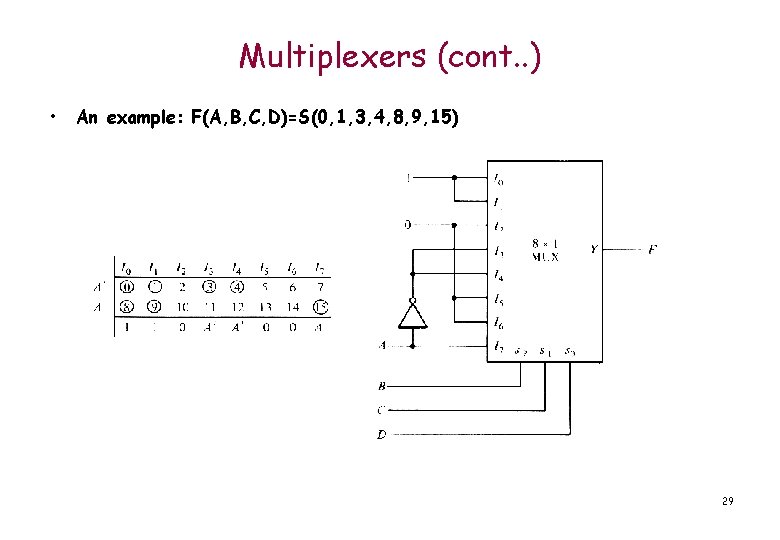

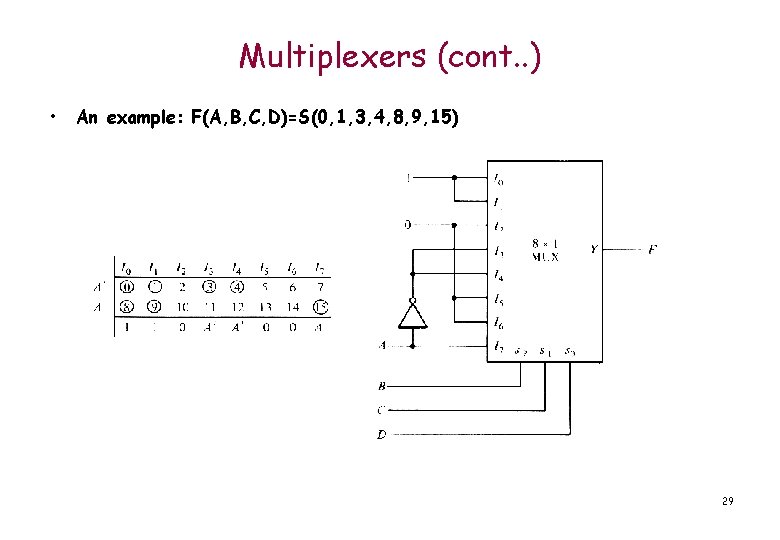

Multiplexers (cont. . ) • Procedure: – assign an ordering sequence of the input variable – the leftmost variable (A) will be used for the input lines – assign the remaining n-1 variables to the selection lines w. r. t. their corresponding sequence – list all the minterms in two rows (A' and A) – circle all the minterms of the function – determine the input lines 28

Multiplexers (cont. . ) • An example: F(A, B, C, D)=S(0, 1, 3, 4, 8, 9, 15) 29

Exercise • • Try to build an inverter using 2 -1 MUX Try to build XOR gate using 4 -1 MUX 30

Lab: Multiplexers Four-input multiplexer - using sum of products logic 31

Thank You! 32