Systems Architecture II CS 282 001 Lecture 5

- Slides: 32

Systems Architecture II (CS 282 -001) Lecture 5: Dealing with Pipeline Hazards* Jeremy R. Johnson *This lecture was derived from material in the text (Chap. 6). All figures from Computer Organization and Design: The Hardware/Software Approach, Second Edition, by David Patterson and John Hennessy, are copyrighted material (COPYRIGHT 1998 MORGAN KAUFMANN PUBLISHERS, INC. ALL RIGHTS RESERVED). July 2, 2001 Systems Architecture II 1

Introduction • Objective: In the previous lecture we saw the modifications necessary to the single-cycle implementation of MIPS to support pipelining. However, we ignored the possibility of pipeline hazards. In today’s lecture we show to deal with pipeline hazards. • A pipeline hazard is a situation where the next instruction cannot execute in the following clock cycle • Topics – Data hazards and forwarding – Data hazards and stalls – Control (branch) hazards • stall and reducing the delay of branches • dynamic branch prediction • delayed branch – Exceptions July 2, 2001 Systems Architecture II 2

Data Hazards and Forwarding • Problem: Instruction depends on the result of a previous instruction still in the pipeline • Example • • • sub $2, $1, $3 and $12, $5 or $13, $6, $2 add $14, $2 sw $15, 100($2) July 2, 2001 Systems Architecture II 3

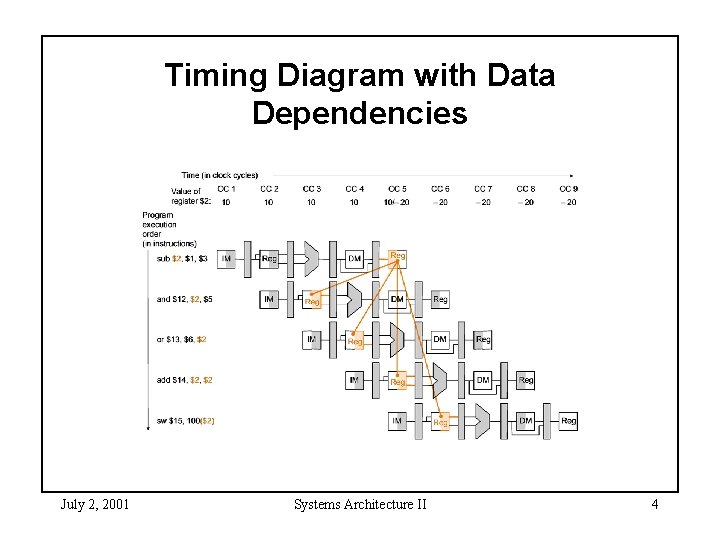

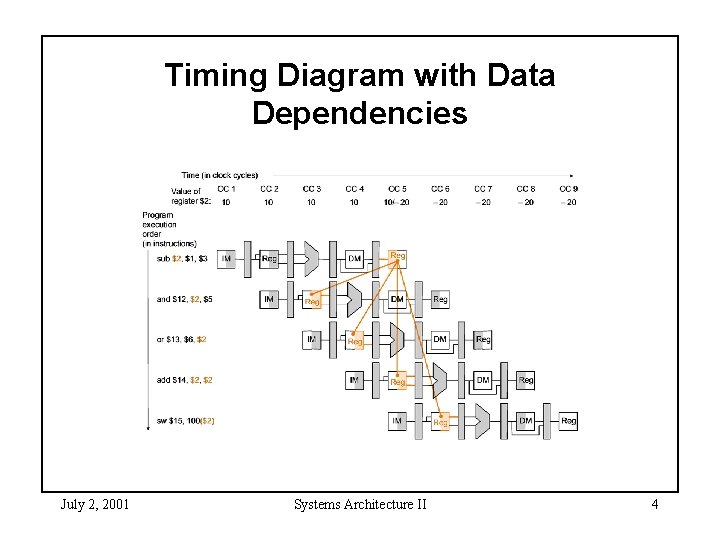

Timing Diagram with Data Dependencies July 2, 2001 Systems Architecture II 4

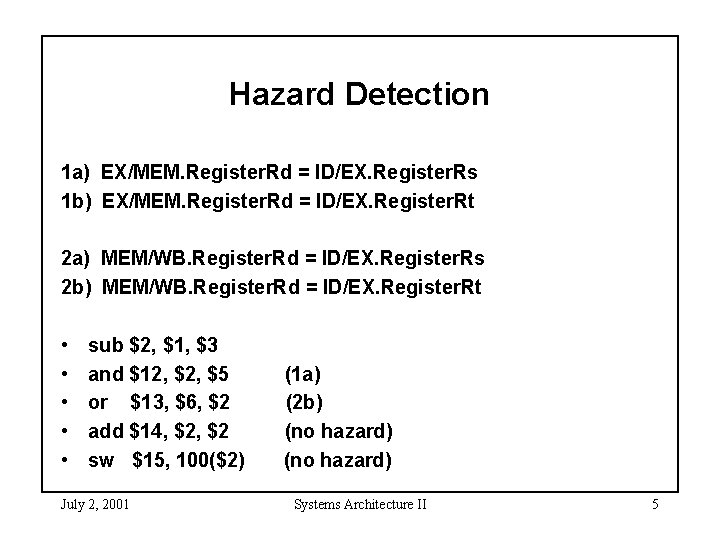

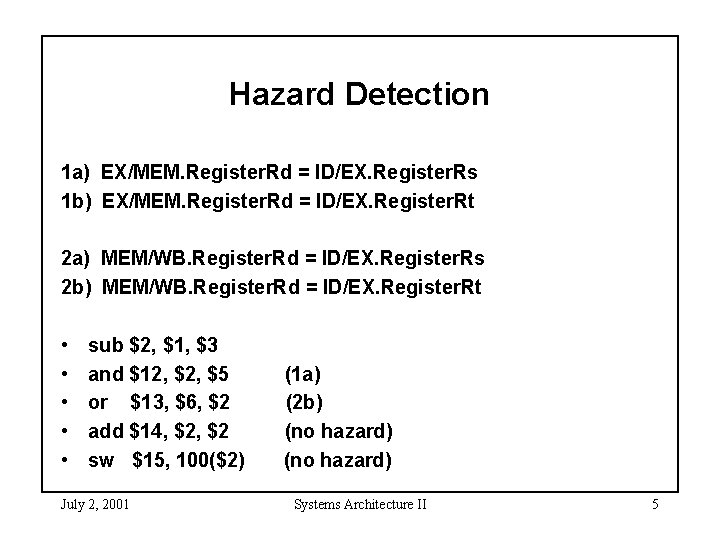

Hazard Detection 1 a) EX/MEM. Register. Rd = ID/EX. Register. Rs 1 b) EX/MEM. Register. Rd = ID/EX. Register. Rt 2 a) MEM/WB. Register. Rd = ID/EX. Register. Rs 2 b) MEM/WB. Register. Rd = ID/EX. Register. Rt • • • sub $2, $1, $3 and $12, $5 or $13, $6, $2 add $14, $2 sw $15, 100($2) July 2, 2001 (1 a) (2 b) (no hazard) Systems Architecture II 5

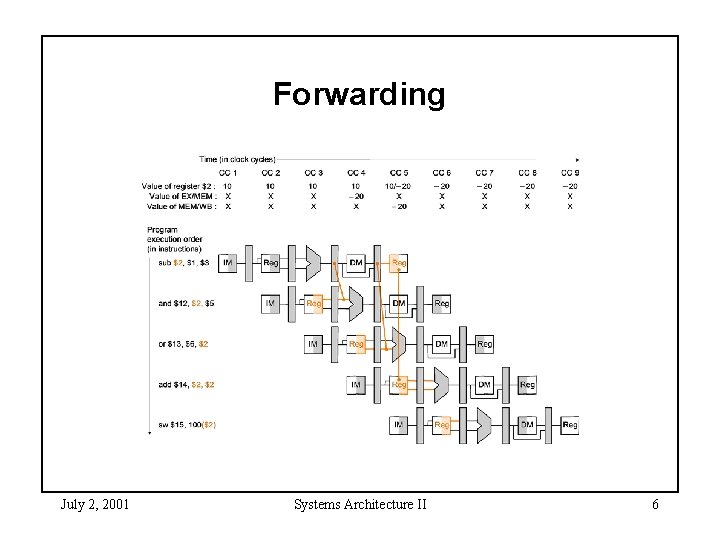

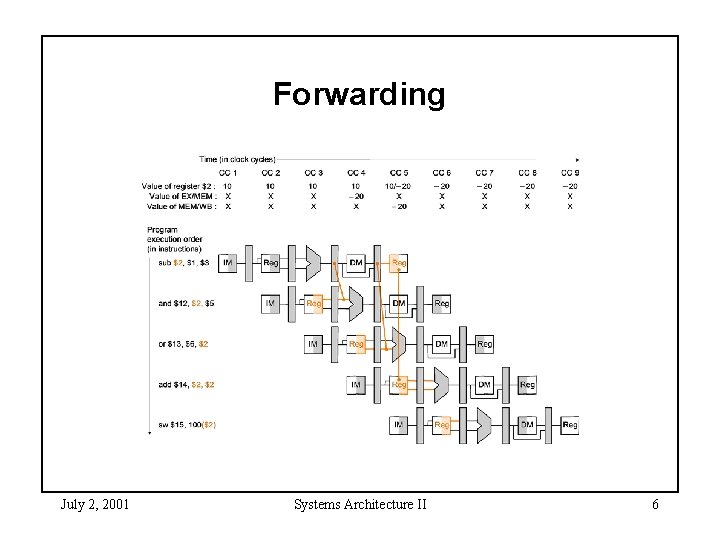

Forwarding July 2, 2001 Systems Architecture II 6

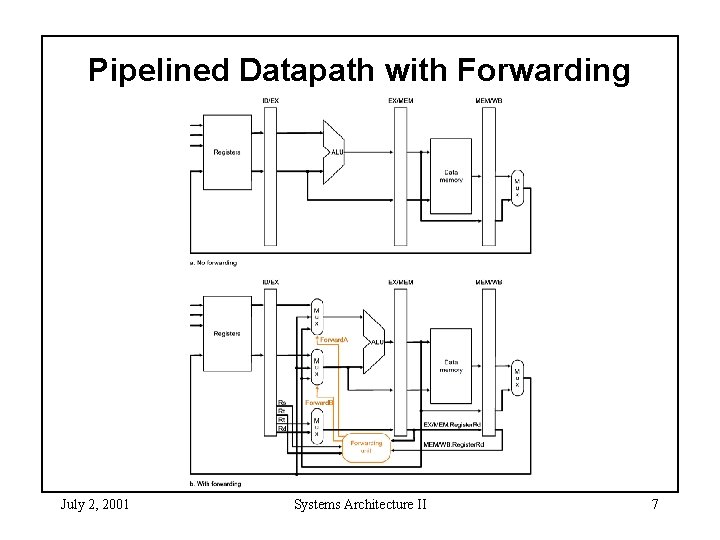

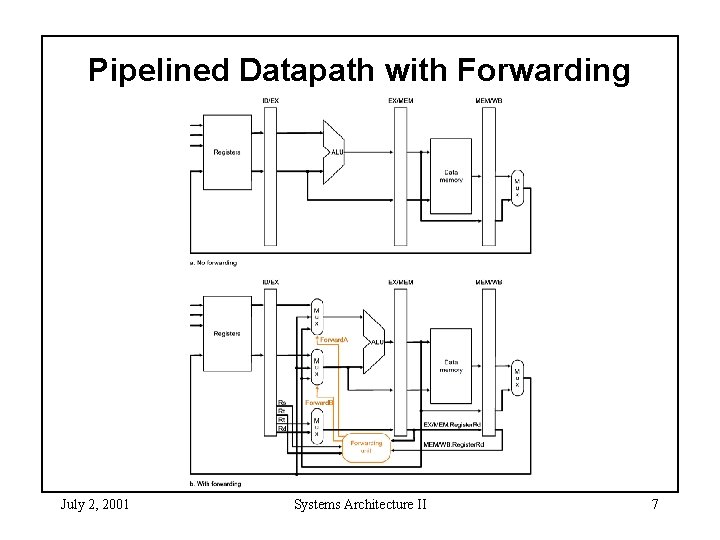

Pipelined Datapath with Forwarding July 2, 2001 Systems Architecture II 7

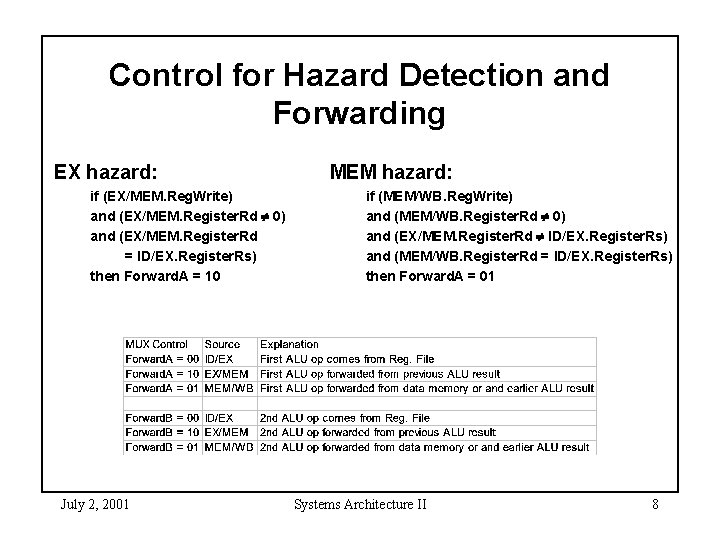

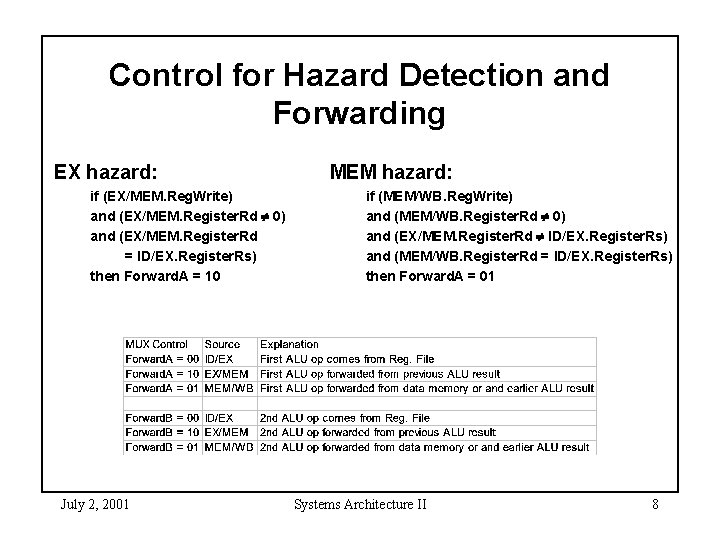

Control for Hazard Detection and Forwarding EX hazard: if (EX/MEM. Reg. Write) and (EX/MEM. Register. Rd 0) and (EX/MEM. Register. Rd = ID/EX. Register. Rs) then Forward. A = 10 July 2, 2001 MEM hazard: if (MEM/WB. Reg. Write) and (MEM/WB. Register. Rd 0) and (EX/MEM. Register. Rd ID/EX. Register. Rs) and (MEM/WB. Register. Rd = ID/EX. Register. Rs) then Forward. A = 01 Systems Architecture II 8

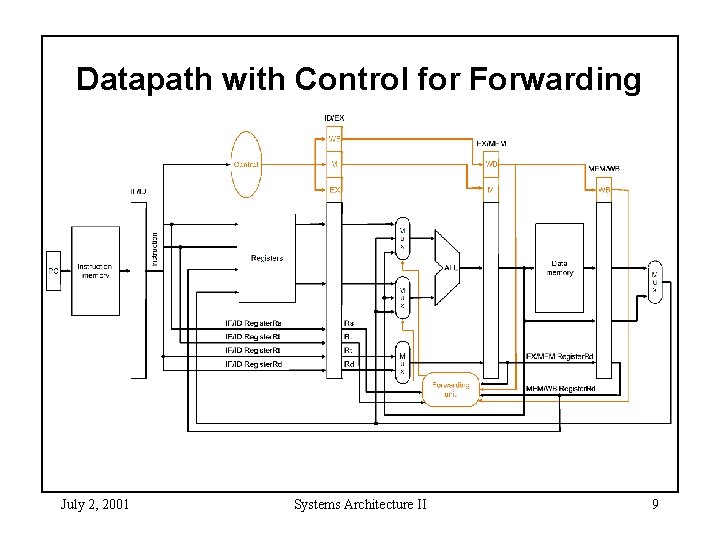

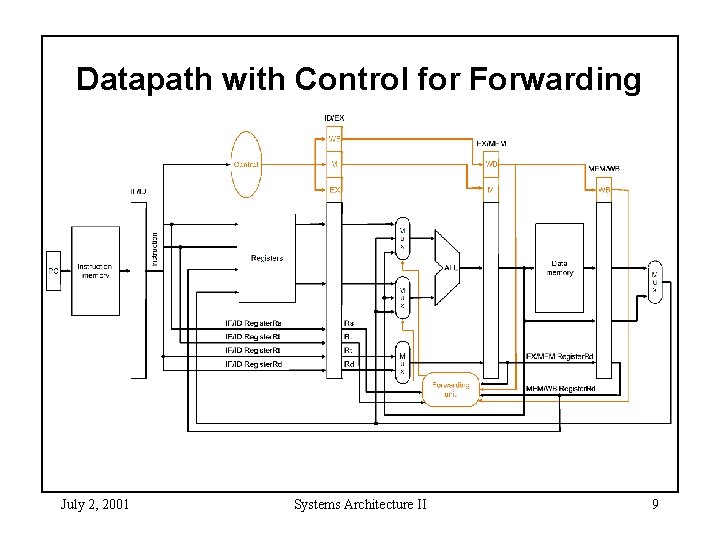

Datapath with Control for Forwarding July 2, 2001 Systems Architecture II 9

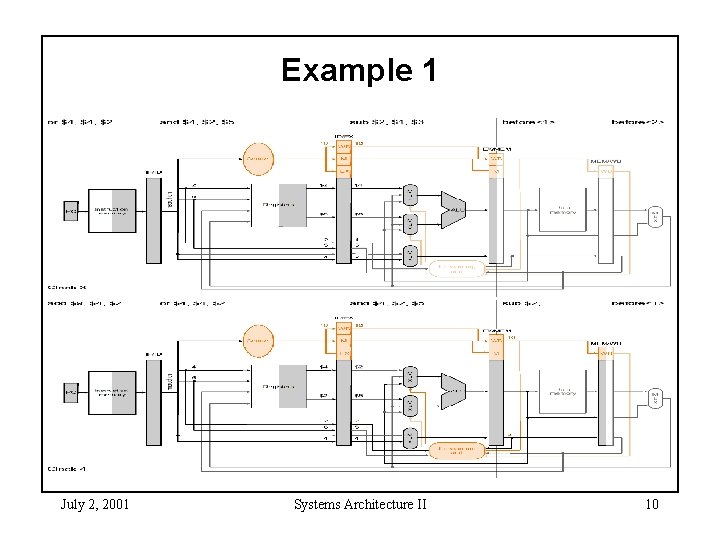

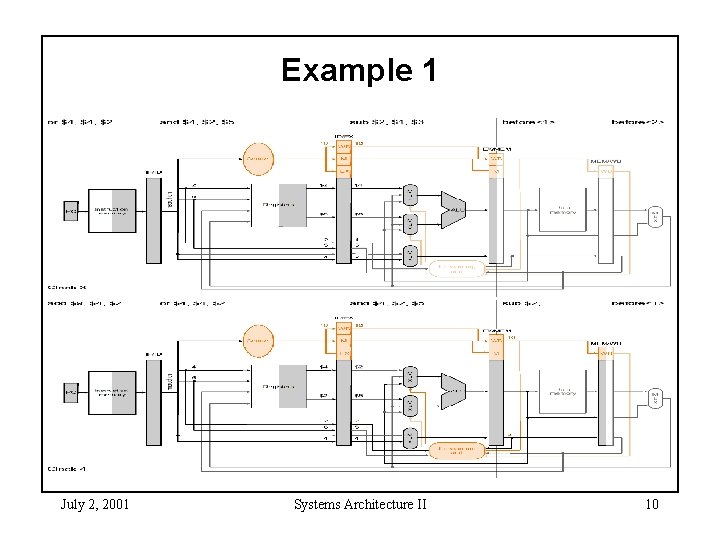

Example 1 July 2, 2001 Systems Architecture II 10

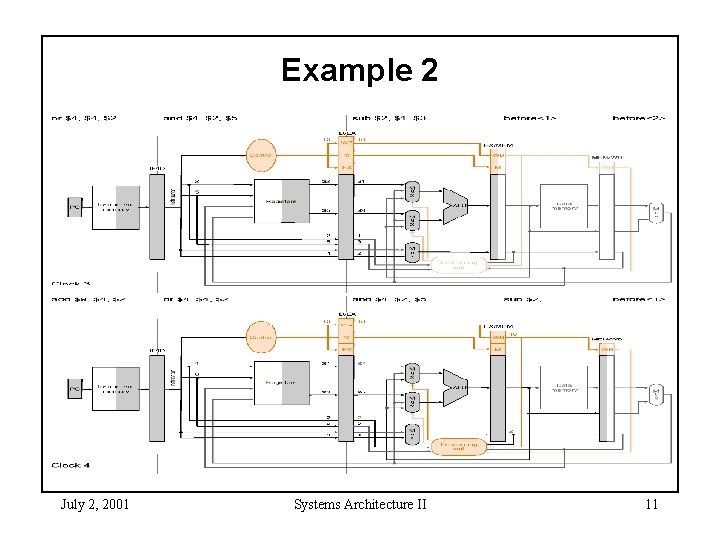

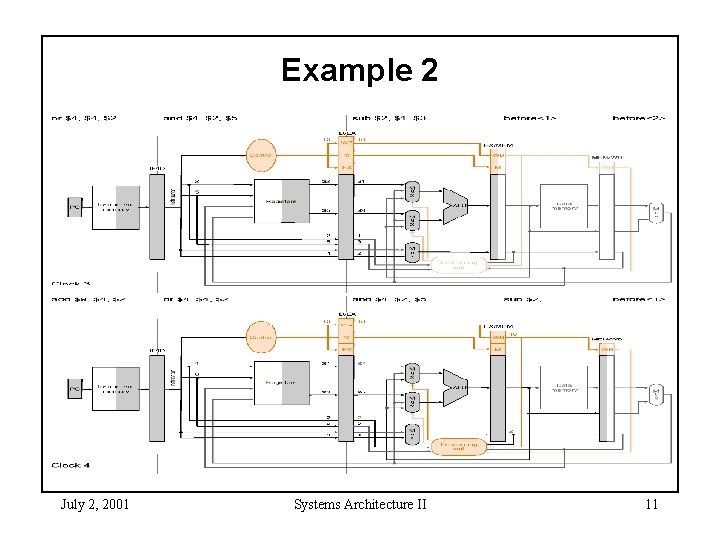

Example 2 July 2, 2001 Systems Architecture II 11

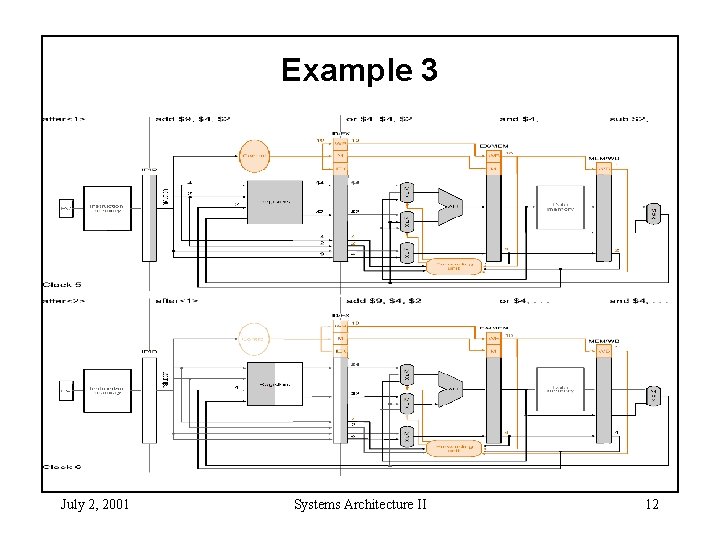

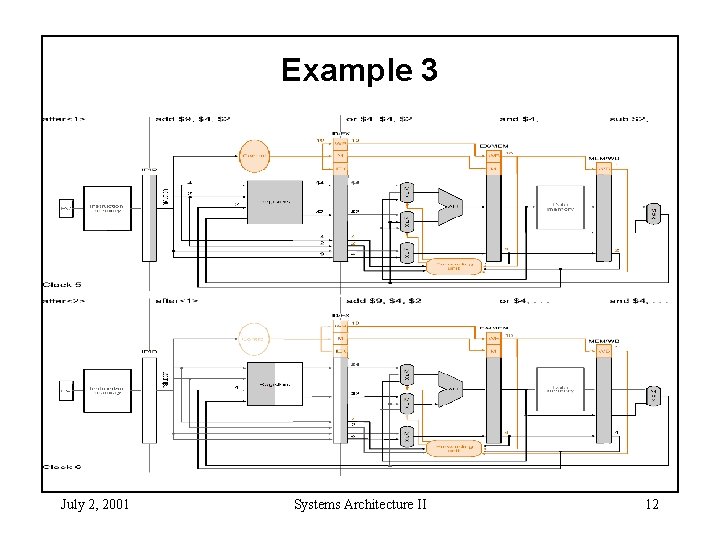

Example 3 July 2, 2001 Systems Architecture II 12

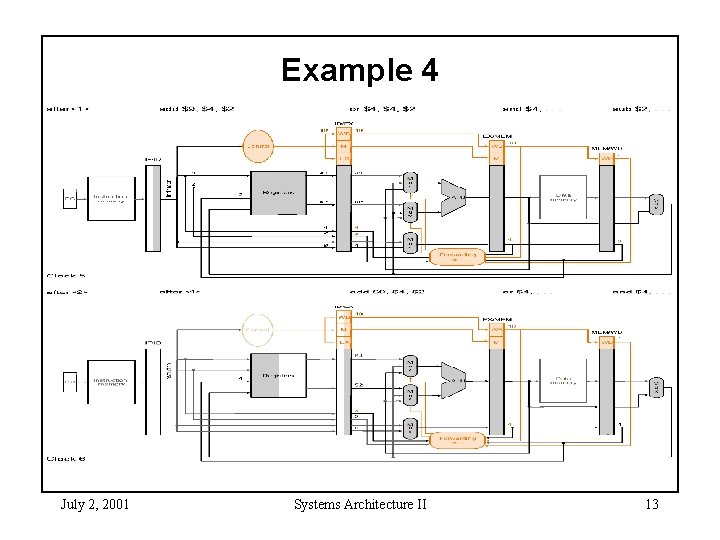

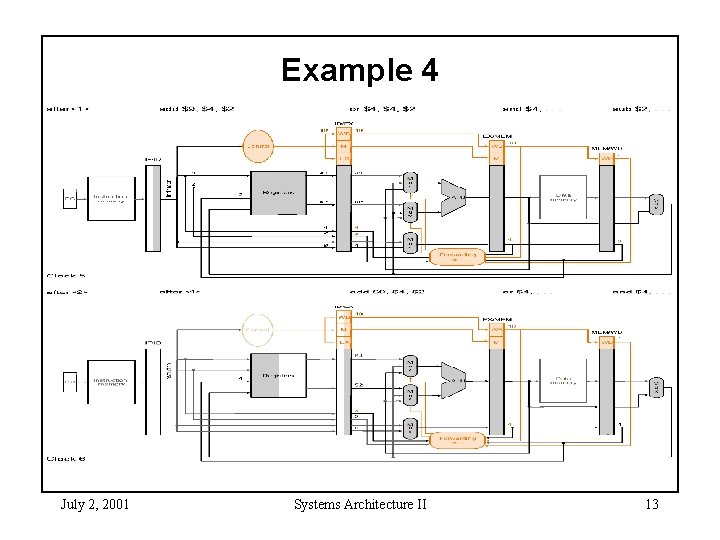

Example 4 July 2, 2001 Systems Architecture II 13

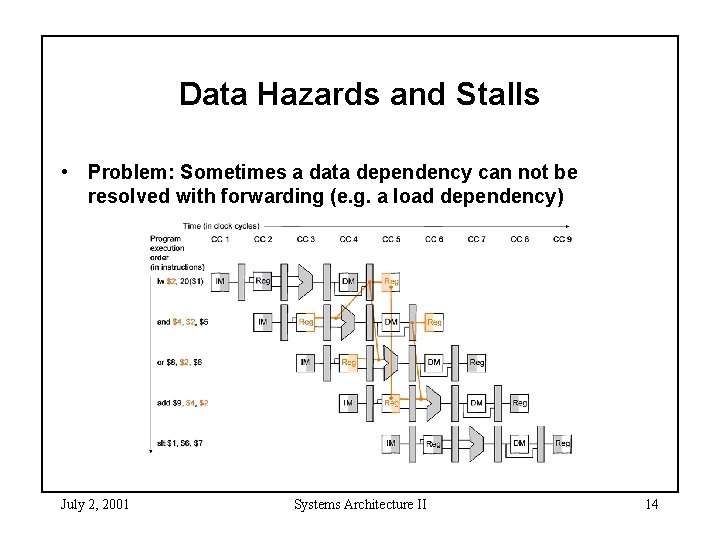

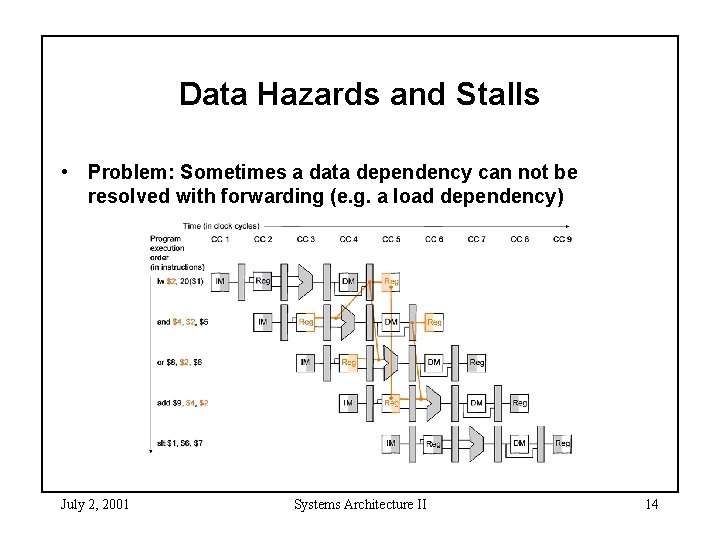

Data Hazards and Stalls • Problem: Sometimes a data dependency can not be resolved with forwarding (e. g. a load dependency) July 2, 2001 Systems Architecture II 14

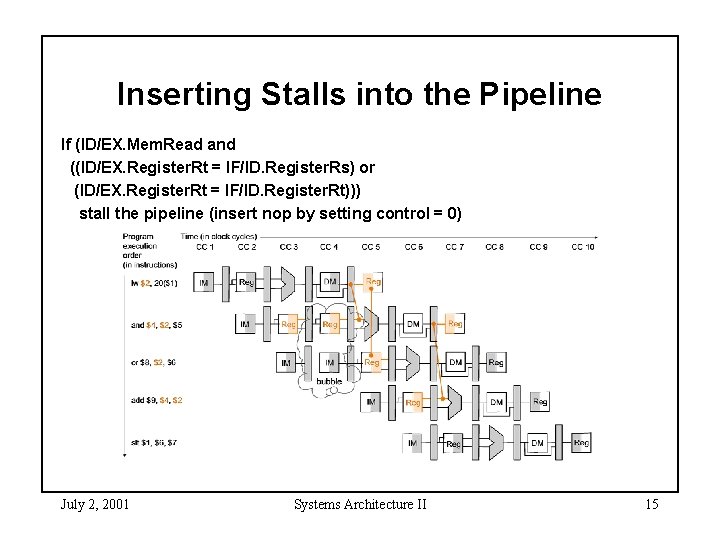

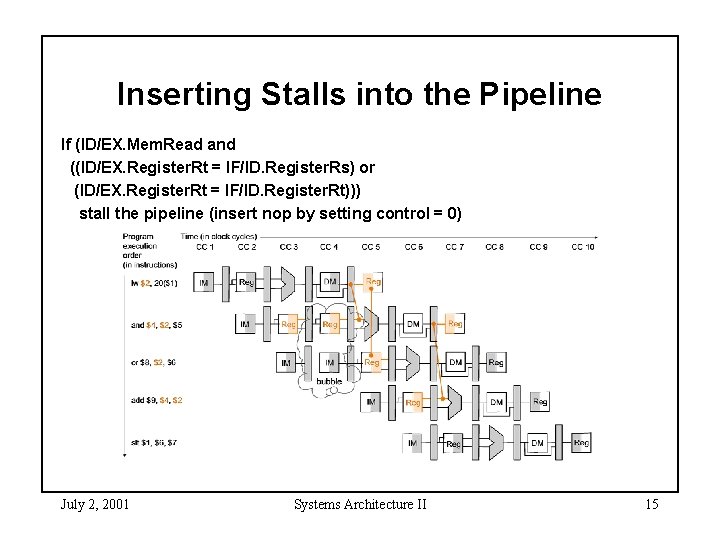

Inserting Stalls into the Pipeline If (ID/EX. Mem. Read and ((ID/EX. Register. Rt = IF/ID. Register. Rs) or (ID/EX. Register. Rt = IF/ID. Register. Rt))) stall the pipeline (insert nop by setting control = 0) July 2, 2001 Systems Architecture II 15

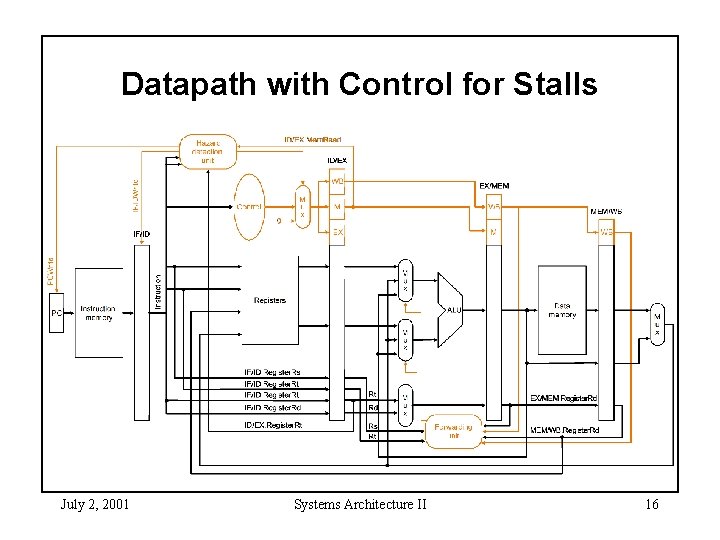

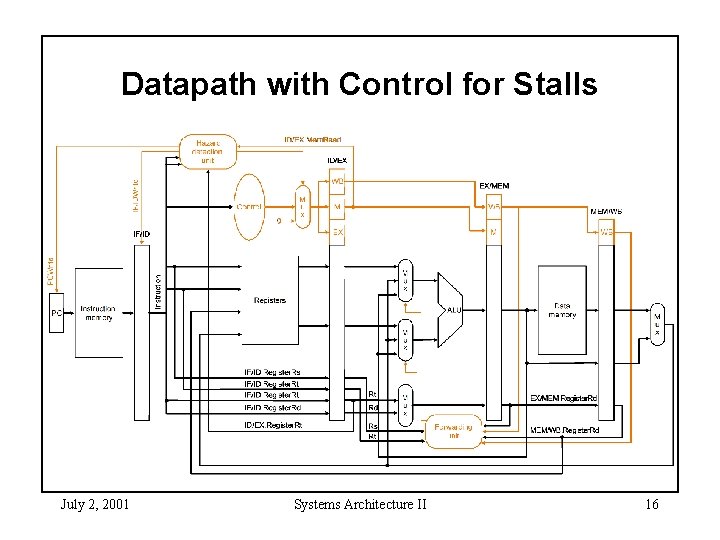

Datapath with Control for Stalls July 2, 2001 Systems Architecture II 16

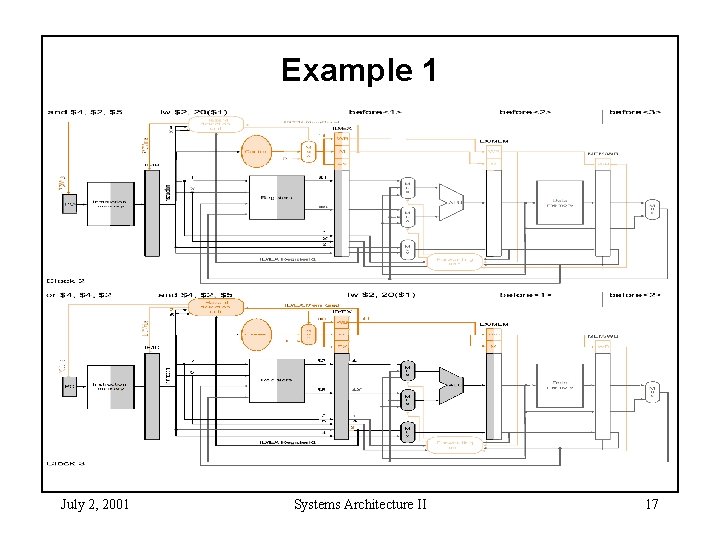

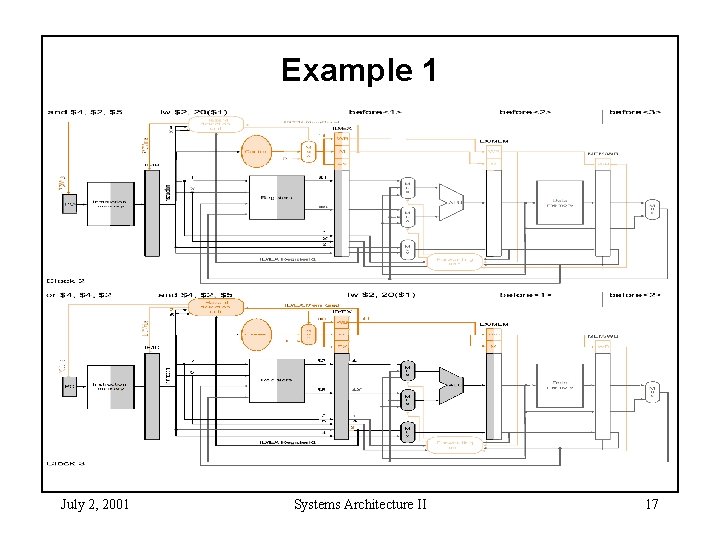

Example 1 July 2, 2001 Systems Architecture II 17

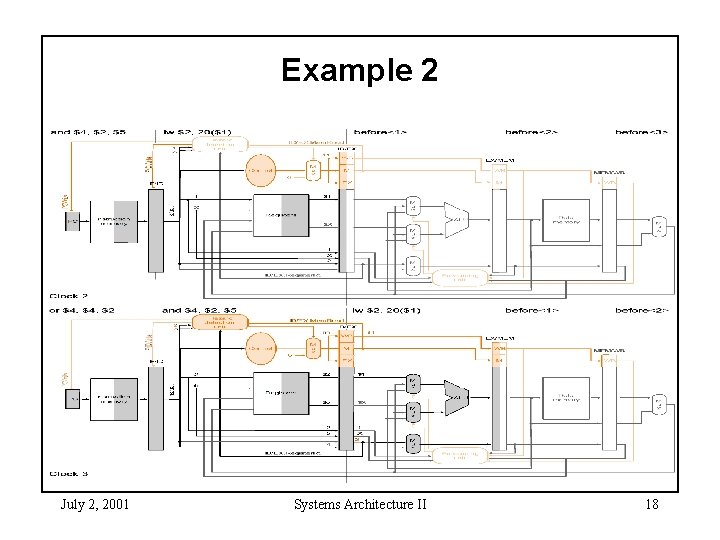

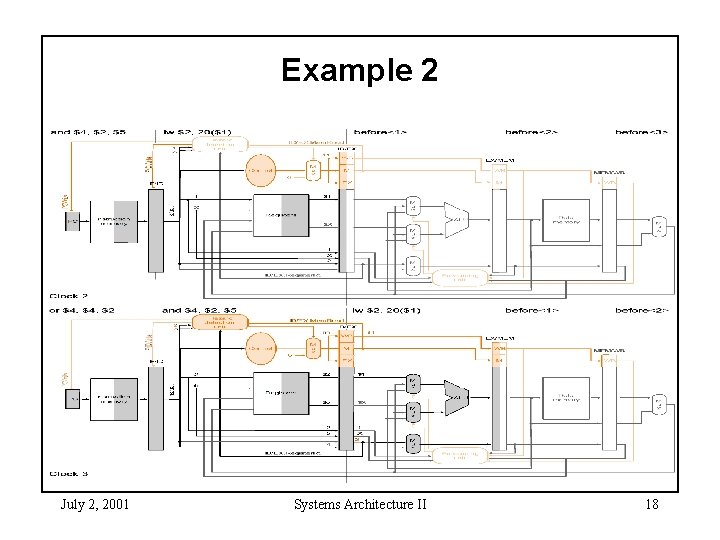

Example 2 July 2, 2001 Systems Architecture II 18

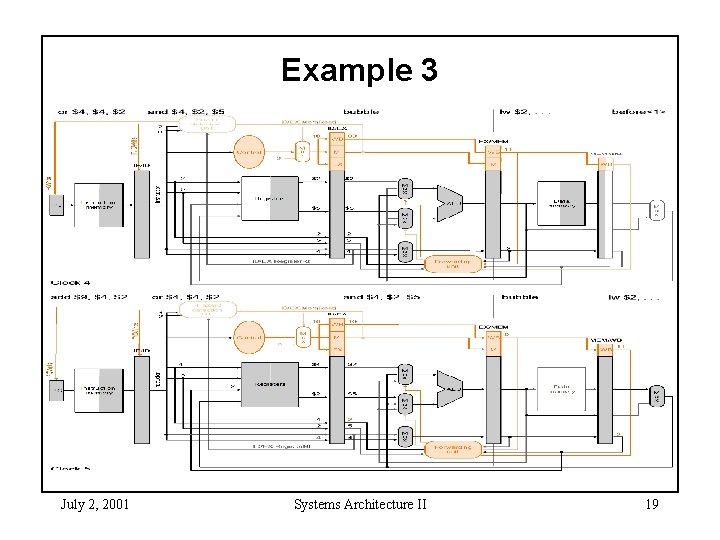

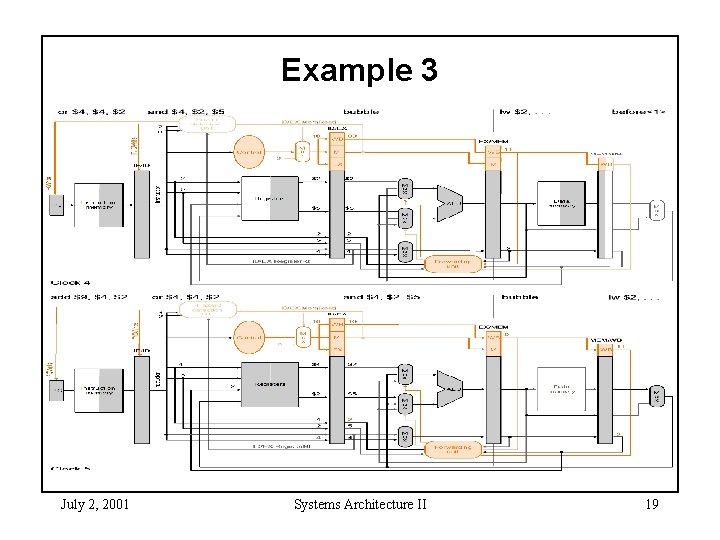

Example 3 July 2, 2001 Systems Architecture II 19

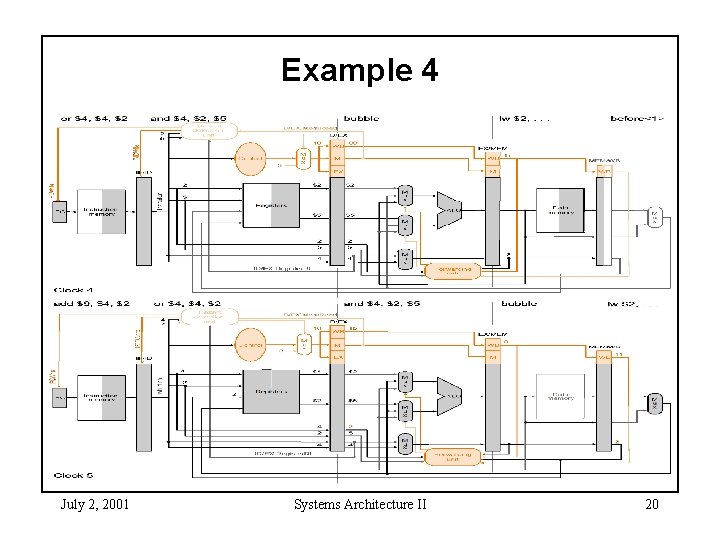

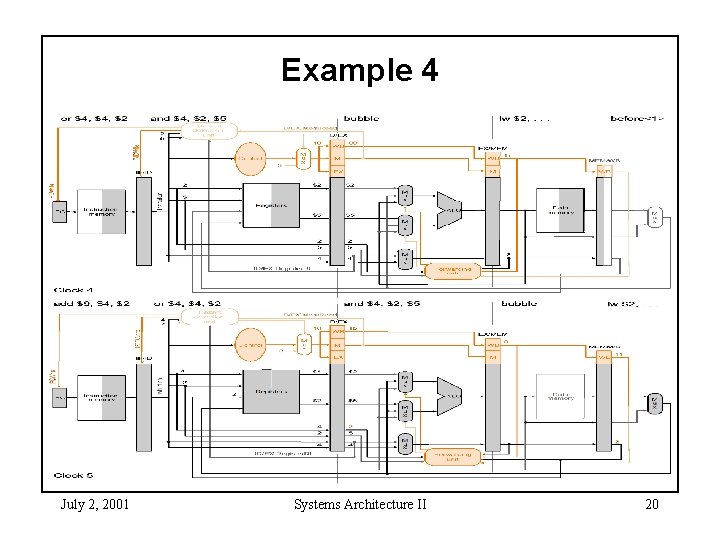

Example 4 July 2, 2001 Systems Architecture II 20

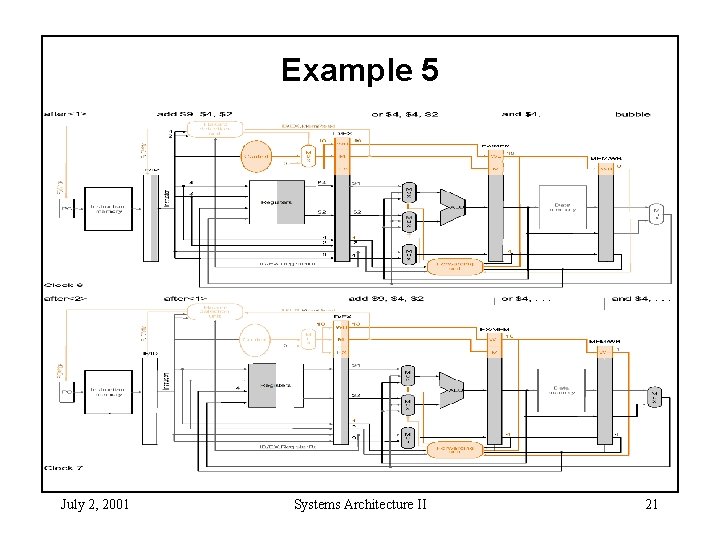

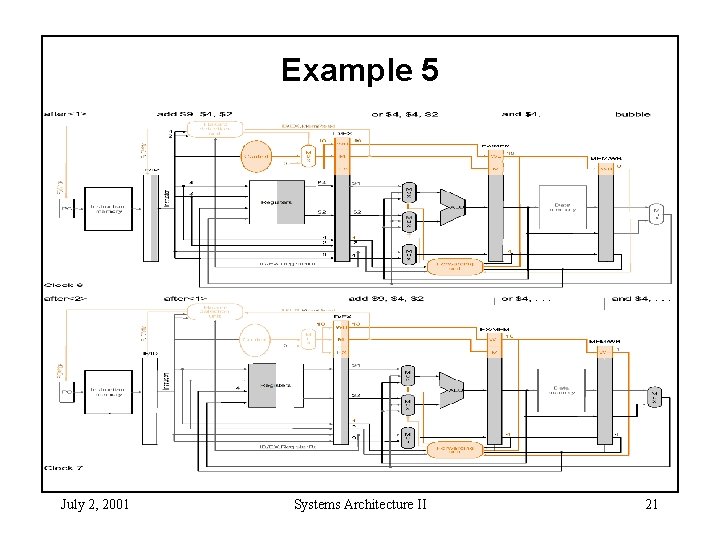

Example 5 July 2, 2001 Systems Architecture II 21

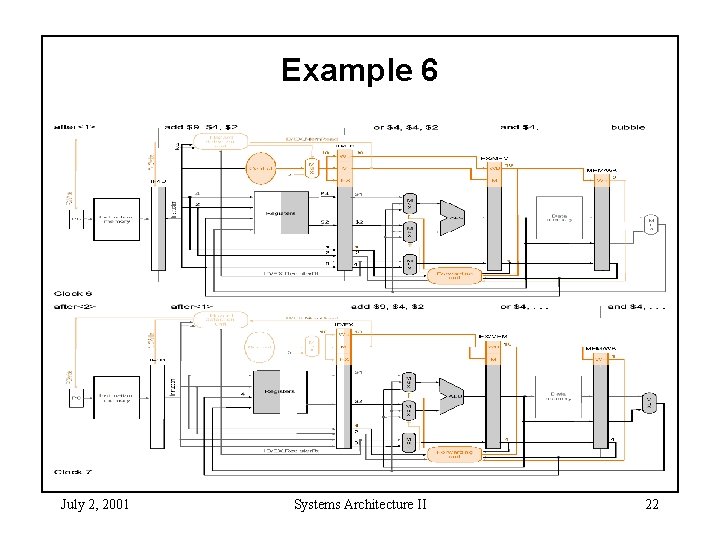

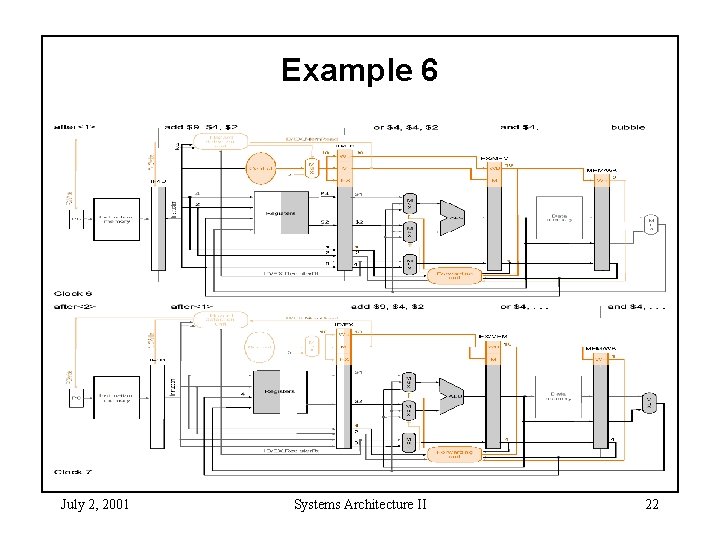

Example 6 July 2, 2001 Systems Architecture II 22

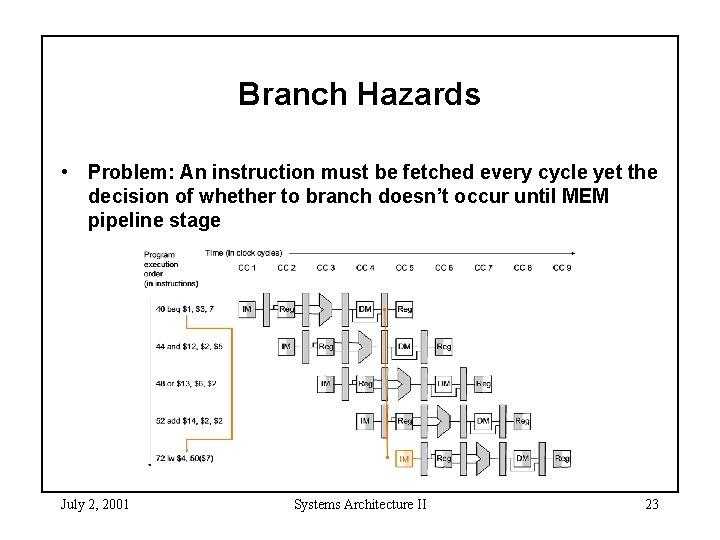

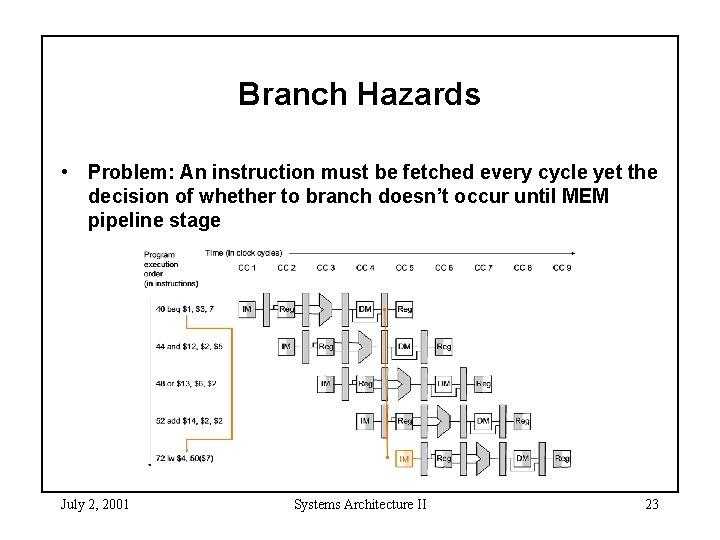

Branch Hazards • Problem: An instruction must be fetched every cycle yet the decision of whether to branch doesn’t occur until MEM pipeline stage July 2, 2001 Systems Architecture II 23

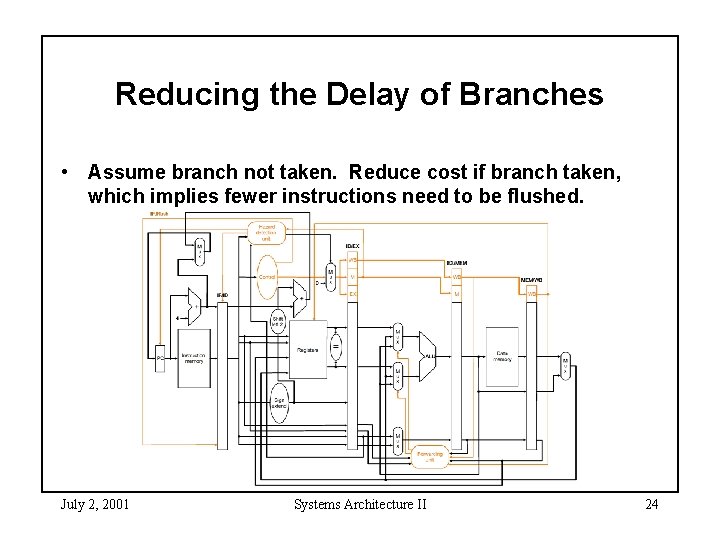

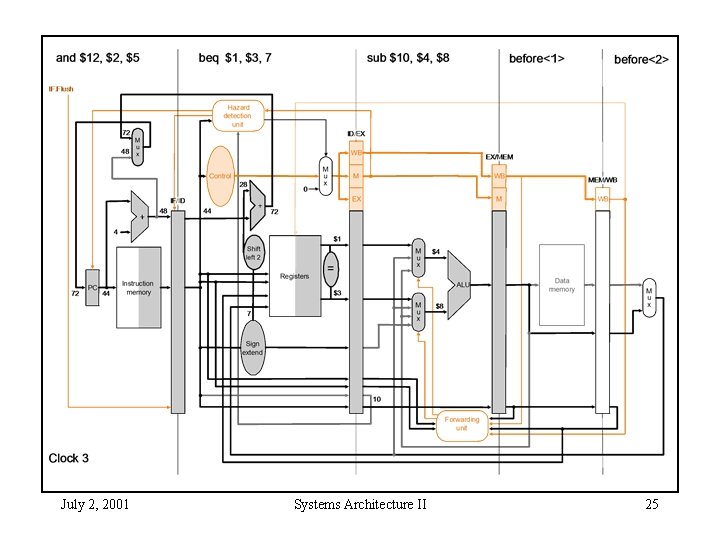

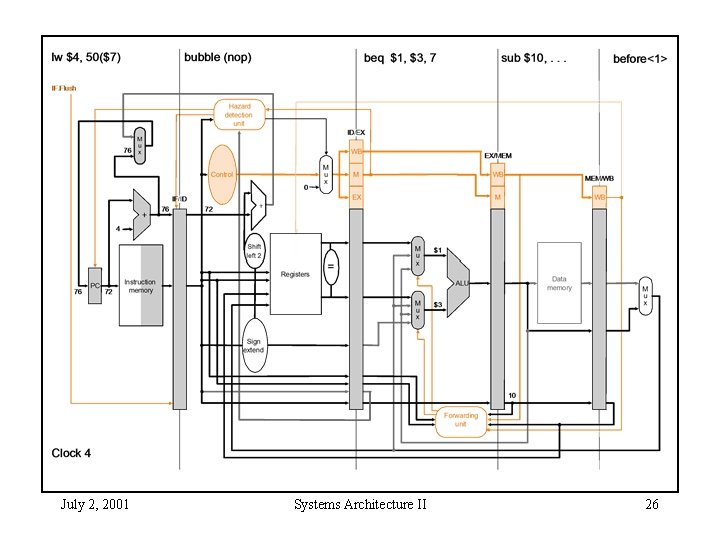

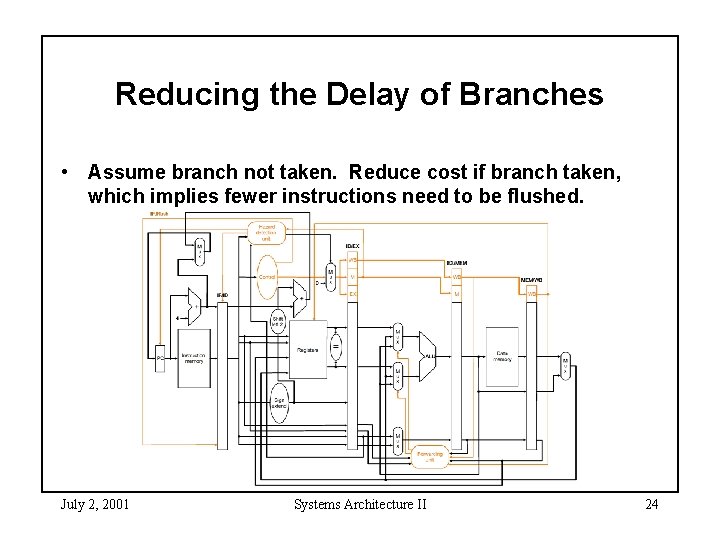

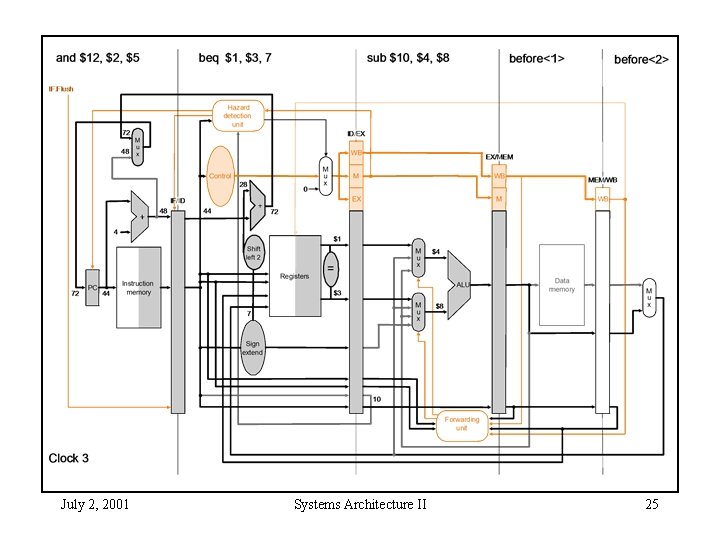

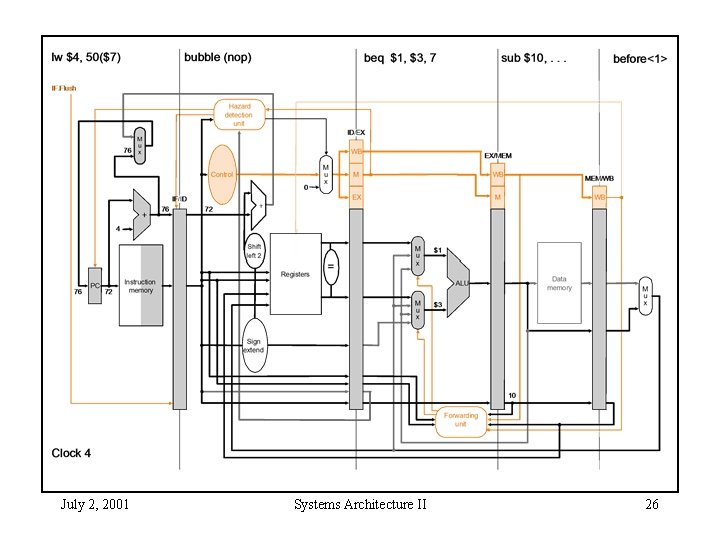

Reducing the Delay of Branches • Assume branch not taken. Reduce cost if branch taken, which implies fewer instructions need to be flushed. July 2, 2001 Systems Architecture II 24

July 2, 2001 Systems Architecture II 25

July 2, 2001 Systems Architecture II 26

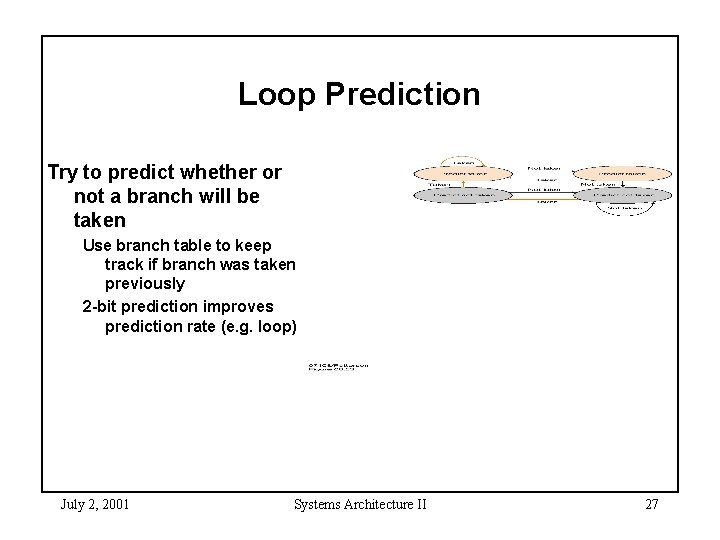

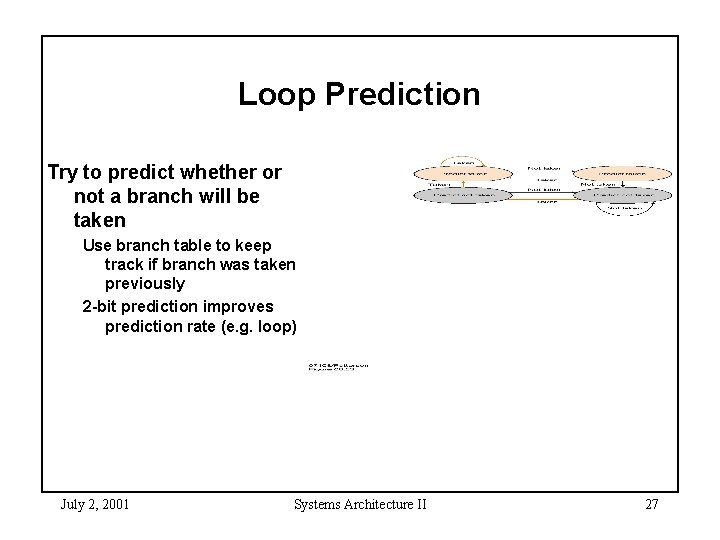

Loop Prediction Try to predict whether or not a branch will be taken Use branch table to keep track if branch was taken previously 2 -bit prediction improves prediction rate (e. g. loop) July 2, 2001 Systems Architecture II 27

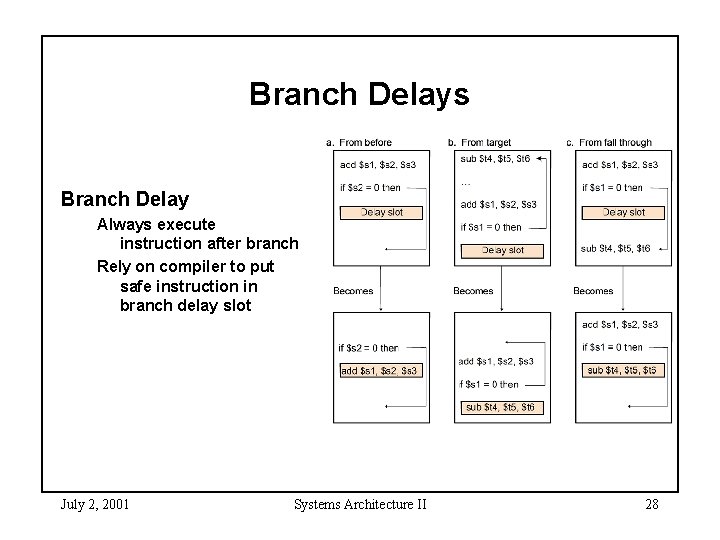

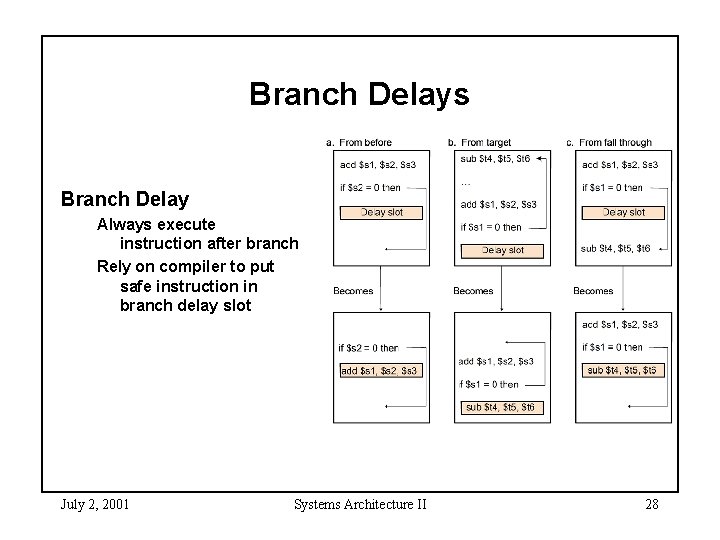

Branch Delays Branch Delay Always execute instruction after branch Rely on compiler to put safe instruction in branch delay slot July 2, 2001 Systems Architecture II 28

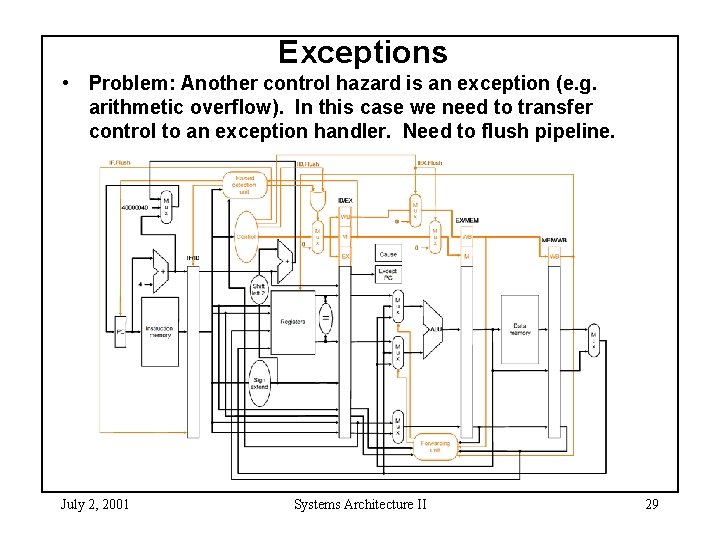

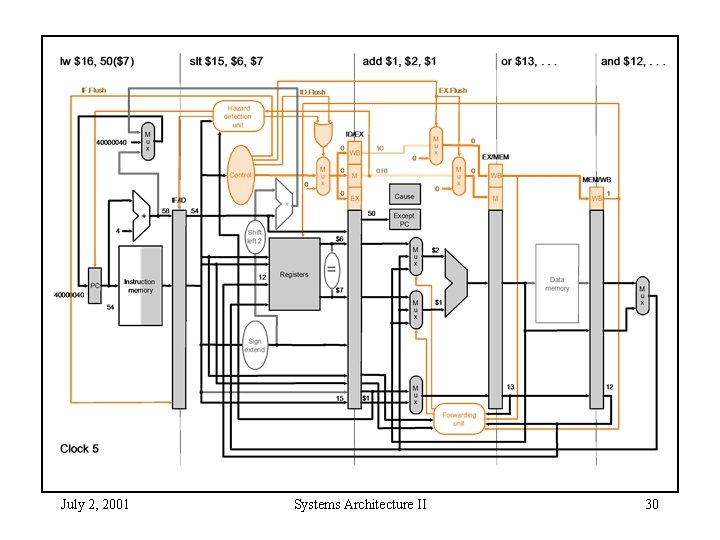

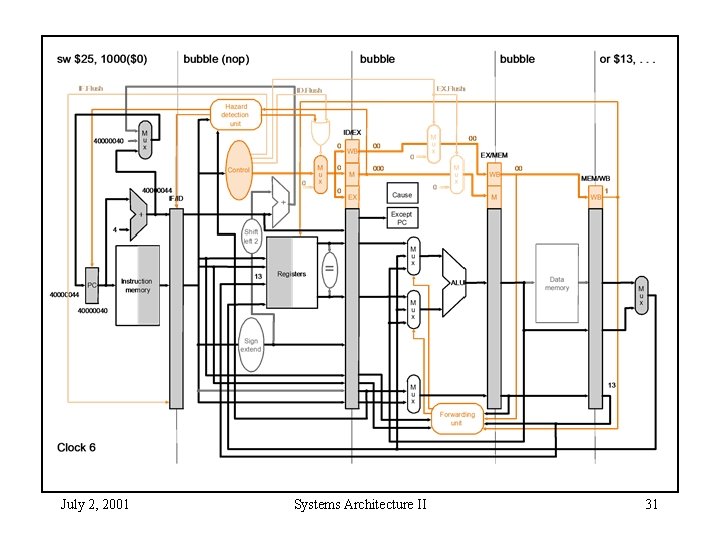

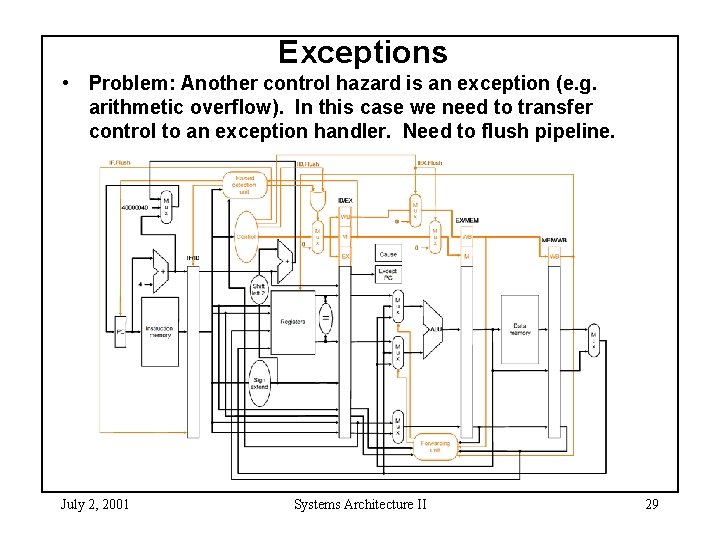

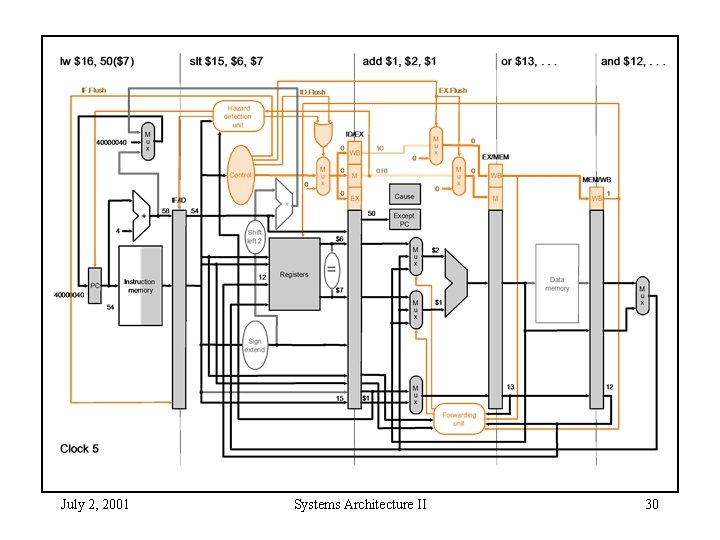

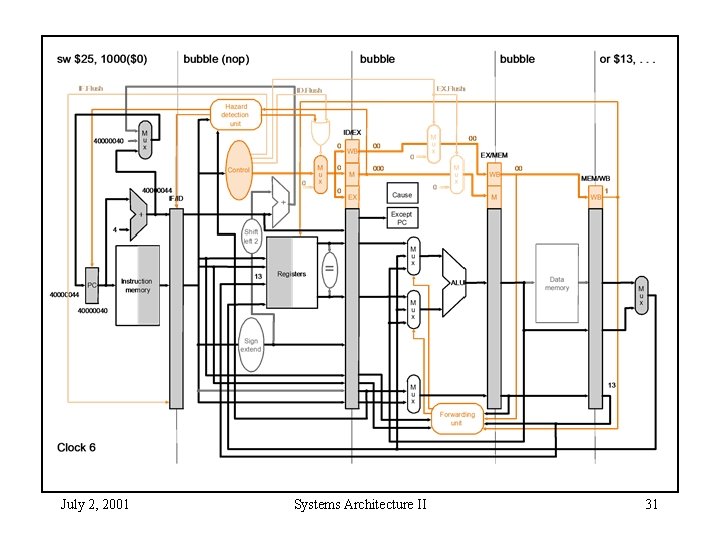

Exceptions • Problem: Another control hazard is an exception (e. g. arithmetic overflow). In this case we need to transfer control to an exception handler. Need to flush pipeline. July 2, 2001 Systems Architecture II 29

July 2, 2001 Systems Architecture II 30

July 2, 2001 Systems Architecture II 31

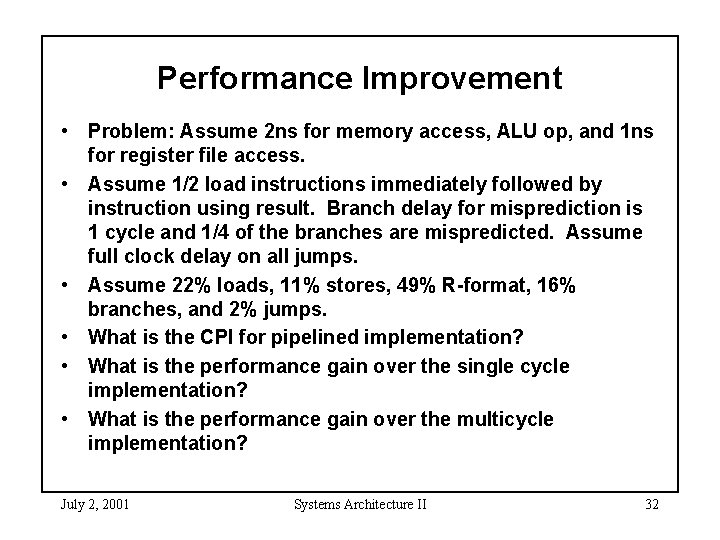

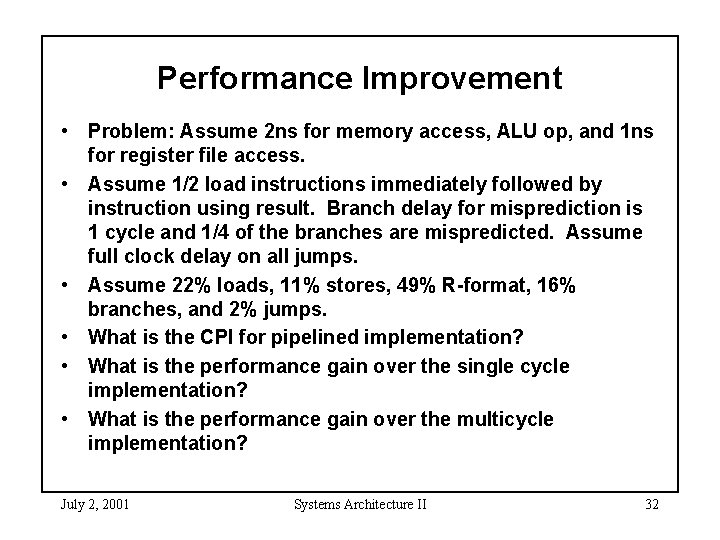

Performance Improvement • Problem: Assume 2 ns for memory access, ALU op, and 1 ns for register file access. • Assume 1/2 load instructions immediately followed by instruction using result. Branch delay for misprediction is 1 cycle and 1/4 of the branches are mispredicted. Assume full clock delay on all jumps. • Assume 22% loads, 11% stores, 49% R-format, 16% branches, and 2% jumps. • What is the CPI for pipelined implementation? • What is the performance gain over the single cycle implementation? • What is the performance gain over the multicycle implementation? July 2, 2001 Systems Architecture II 32