SEMISYNTHETIC CIRCUIT GENERATION FOR TESTING INCREMENTAL PLACE AND

- Slides: 26

SEMI-SYNTHETIC CIRCUIT GENERATION FOR TESTING INCREMENTAL PLACE AND ROUTE TOOLS David Grant Guy Lemieux University of British Columbia Vancouver, BC

Overview Introduction Circuit Generation Method 1 (FPL) doesn’t work well Circuit Generation Method 2 (FPT) simple, works very well Circuit Scaling Extension Conclusions 2

Introduction Problem (Free) Large digital circuits are rare FPGA CAD tools need large circuits Solution Generate random circuits But is random realistic? Goal Generate realistic random circuits (synthetic) Useful for testing place and route tools 3

Introduction Past approaches Generate a complete synthetic circuit Tools: ccirc+cgen, gnl New problem Real world development is iterative, incremental FPGA tools commonly used in incremental mode Need circuits with incremental changes 4

Introduction Our Approach Start with a real circuit Generate a small synthetic change Result is a semi-synthetic circuit Four steps to generate a semi-synthetic circuit 1. Identify 2. Remove 3. Generate 4. Stitch (difficult? ) 5

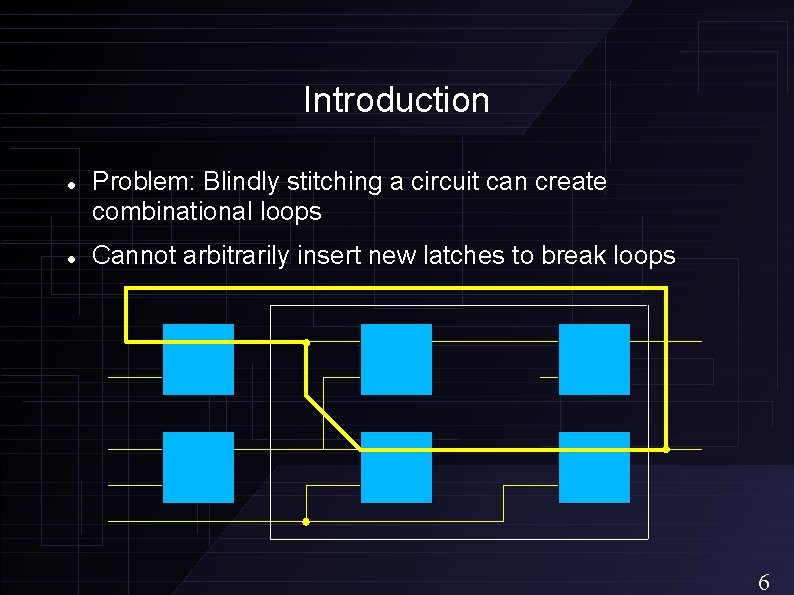

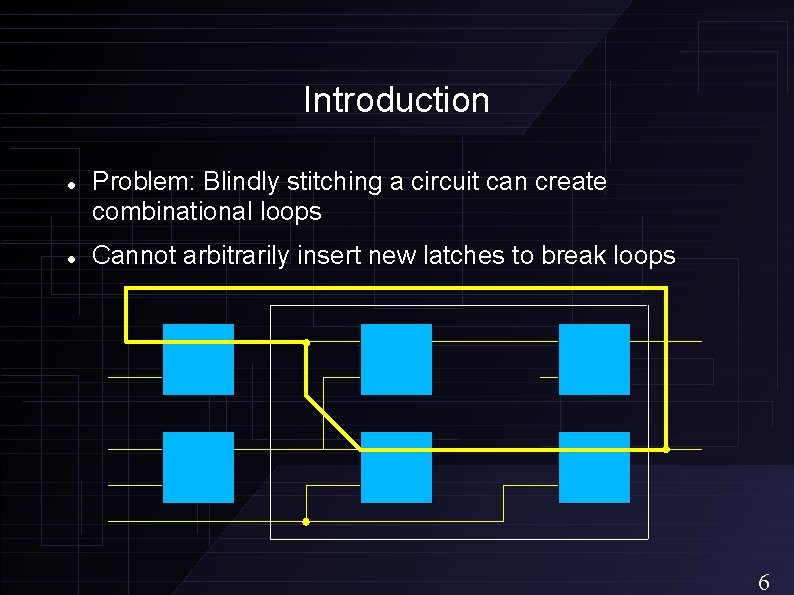

Introduction Problem: Blindly stitching a circuit can create combinational loops Cannot arbitrarily insert new latches to break loops 6

Overview Introduction Circuit Generation Method 1 (FPL) Circuit Generation Method 2 (FPT) Circuit Scaling Conclusions 7

Method 1: Introduction Four steps to generate a semi-synthetic circuit 1. Identify sub-circuit (T-VPack) 2. Remove sub-circuit 3. Generate clone (ccirc+gnl, ccirc+cgen) 4. Stitch Steps 1, 2, 3 are easy… Stitching is difficult !! 8

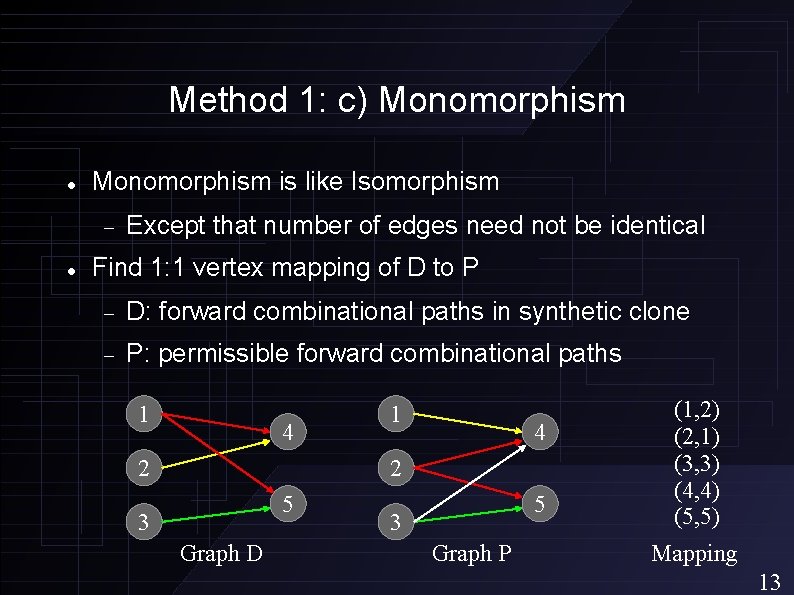

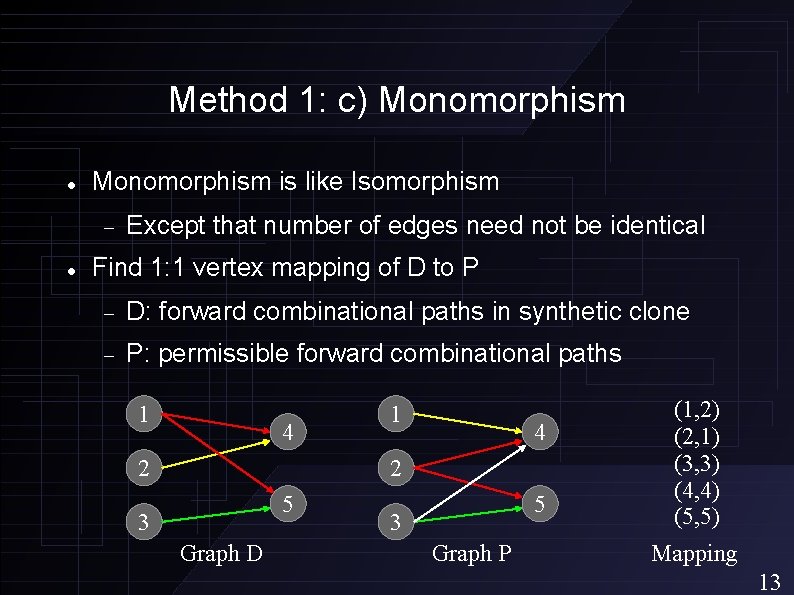

Method 1: c) Monomorphism is like Isomorphism Except that number of edges need not be identical Find 1: 1 vertex mapping of D to P D: forward combinational paths in synthetic clone P: permissible forward combinational paths 1 4 2 5 3 Graph D 5 3 Graph P (1, 2) (2, 1) (3, 3) (4, 4) (5, 5) Mapping 13

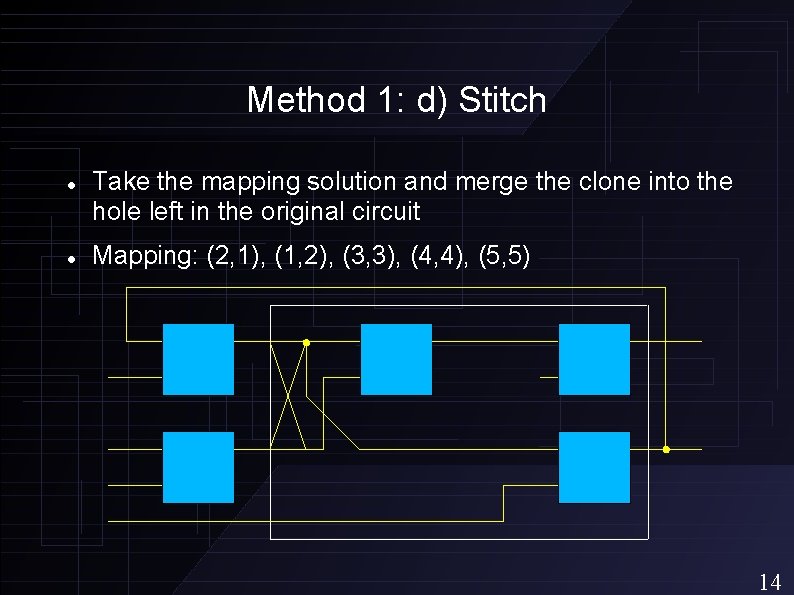

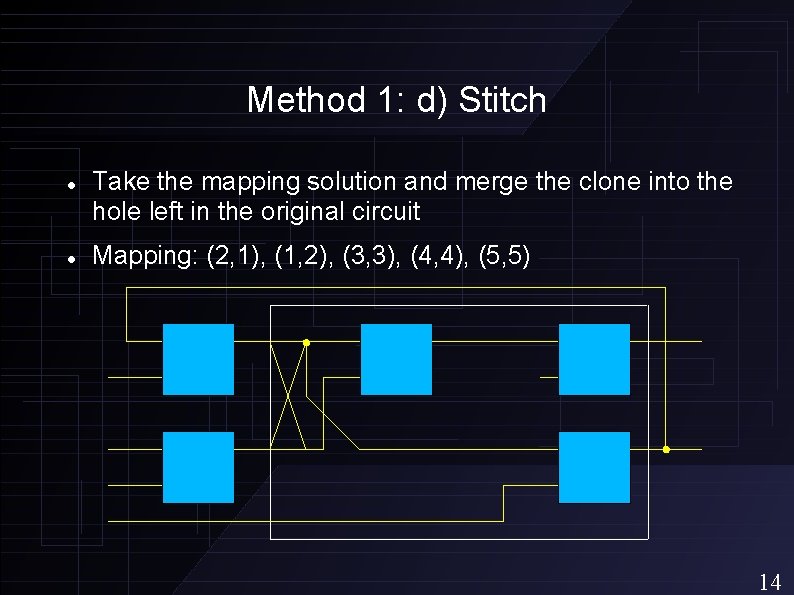

Method 1: d) Stitch Take the mapping solution and merge the clone into the hole left in the original circuit Mapping: (2, 1), (1, 2), (3, 3), (4, 4), (5, 5) 14

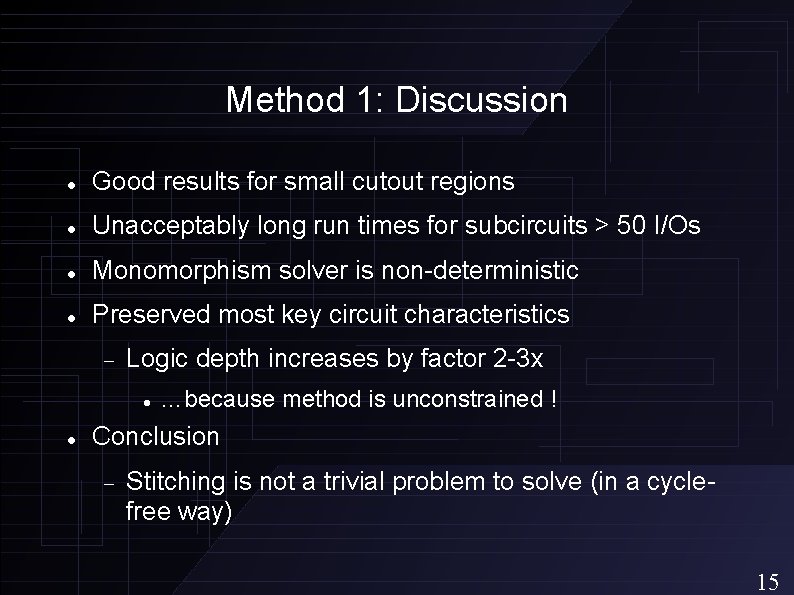

Method 1: Discussion Good results for small cutout regions Unacceptably long run times for subcircuits > 50 I/Os Monomorphism solver is non-deterministic Preserved most key circuit characteristics Logic depth increases by factor 2 -3 x …because method is unconstrained ! Conclusion Stitching is not a trivial problem to solve (in a cyclefree way) 15

Overview Introduction Circuit Generation Method 1 (FPL) Circuit Generation Method 2 (FPT) Circuit Scaling Conclusions 16

Method 2: Introduction Four steps to generate a semi-synthetic circuit 1. Identify sub-circuit (T-VPack) 2. Remove sub-circuit 3. Generate clone (perturber) 4. Stitch The perturber does not “profile and generate” Instead, it “perturbs” the existing circuit Stitching is trivialized using this method 17

Method 2: Perturbing a Circuit Perturber Algorithm a) Levelize the complete circuit b) Select a random edge in the sub-circuit (1 source and 1 sink) c) Select a second edge in sub-circuit under certain constraints * d) Swap the sinks e) Repeat 18

Method 2: Perturbing a Circuit Perturber Algorithm (cont'd) * Constraints guiding second edge selection 1. Source and sink levels must match 2. Source node cannot be sub-circuit input 19

Method 2: Advantages of Perturber Algorithm Key circuit characteristics are exactly preserved Number of nodes and edges Fanout distribution Depth profile Strengths No combinational loops are created Because the levelization is preserved Very fast execution time Very simple approach 20

Method 2: Ancestor Control Method to preserve locality Add additional edge selection constraint 1. Source and sink levels must match 2. Source node may not be sub-circuit input 3. Both edges must share a common ancestor through combinational logic within a certain ancestor depth Stop at sub-circuit inputs and flops 22

Method 2: Testing Know all the key circuit characteristics are preserved Focus comparisons on post-routing results Test 20 largest MCNC circuits Metrics: channel width, delay, and wirelength goodness of result == closeness to original MCNC result Test 1: Sanity test, full-circuit compare w/ ccirc+cgen Test 2: Incremental semi-synthetic circuits 23

Method 2: Discussion Sanity Check Complete circuit result error < ccirc+cgen error (error reduced by ~1/3) Incremental Circuits Close to original (1%-6%) using 5%, 10% cutouts More deviation (4%-9%) at 20% cutout 31

Overview Introduction Circuit Generation Method 1 (FPL) Circuit Generation Method 2 (FPT) Circuit Scaling Conclusions 32

Circuit Scaling Reduce the size of the cutout region Increase the size of the cutout region so the tools have to fill in holes so the tools have to make room for larger circuit Approach Scale a circuit (mutator), then perturb it 33

Circuit Scaling Reduction Shotgun approach: delete nodes at random Sometimes need to delete chains of logic Enlargement Duplicate circuit in parallel Multiplex inputs and outputs with LUTs Doubles (…, triples, etc) circuit Enlargement+reduction to achieve arbitrary scaling 34

Circuit Scaling: Results Test 5%, 10%, 20% cutout Scale cutout size to 50%, 75%, 200%, 400% original No unexpected changes in post-routing characteristics from MCNC original Some expected changes Eg, wirelength increased as cutout size enlarged 35

Conclusions Have shown how to create a semi-synthetic circuit Method 2 is a superior method over past approaches Runtime, simplicity Preservation of key circuit properties Preserve them first, find ways to alter them later… Quality of result Scaling is able to change the circuit size without changing the post-routing characteristics in unexpected ways 36

Future Work Critical Path Lengthen the critical path to force the tools to shuffle nodes along the critical path Mutate other circuit properties? Node depth profile Fanout distribution Fanin distribution Wire lengths 37

It's Over Questions? Comments? Concerns? 38