RS232 Port Lecture L 9 3 RS232 voltage

- Slides: 21

RS-232 Port Lecture L 9. 3

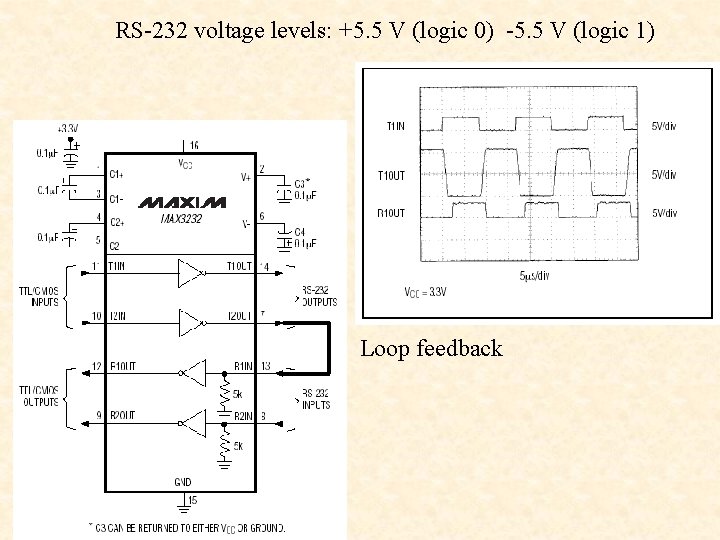

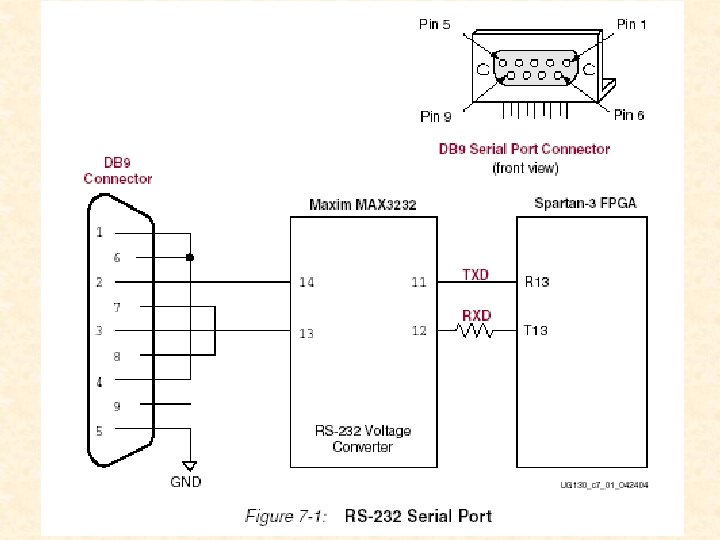

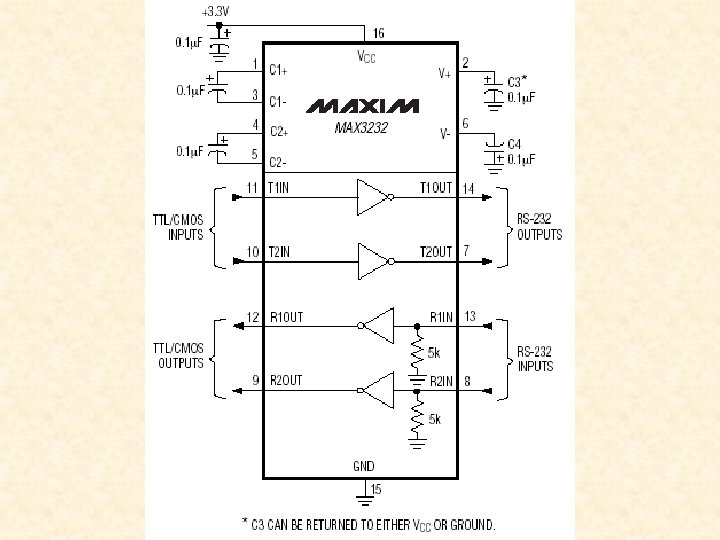

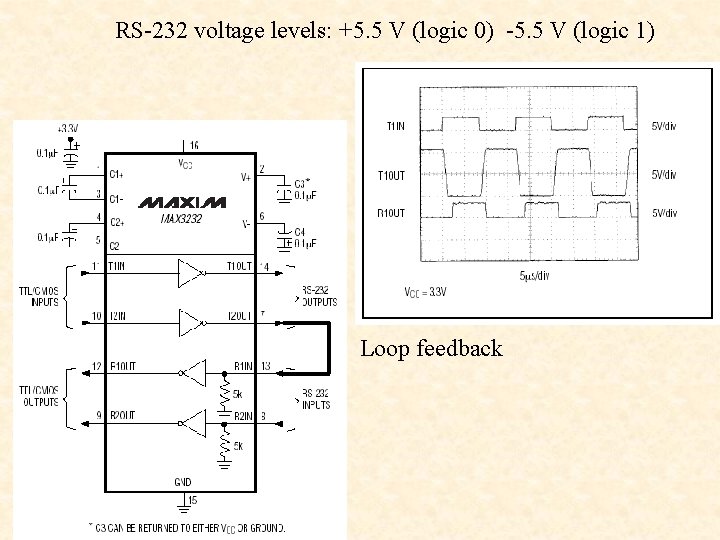

RS-232 voltage levels: +5. 5 V (logic 0) -5. 5 V (logic 1) Loop feedback

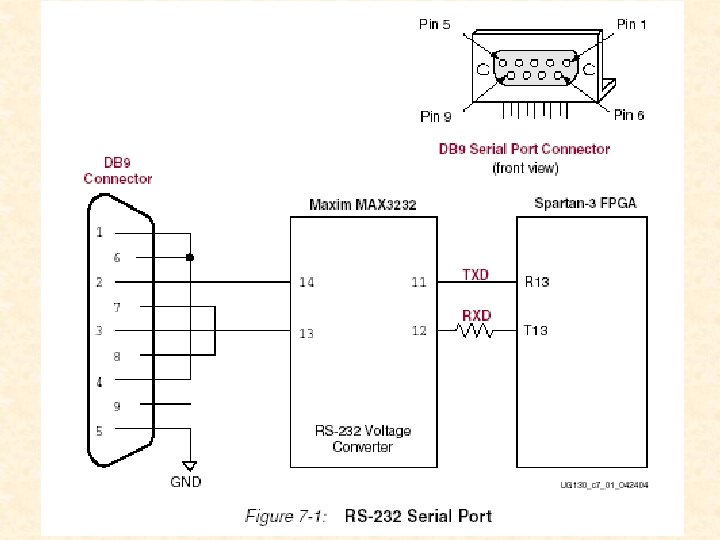

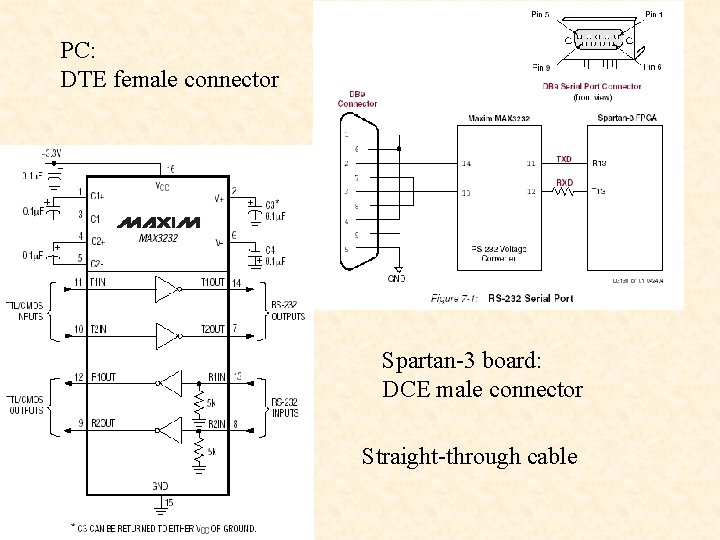

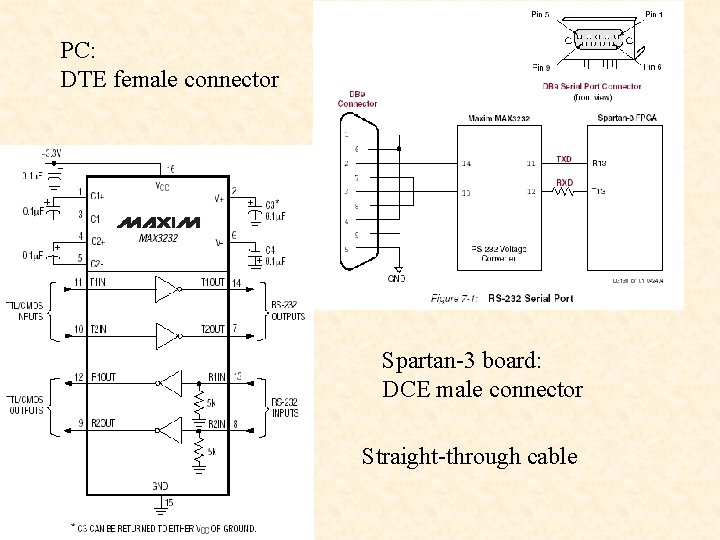

PC: DTE female connector Spartan-3 board: DCE male connector Straight-through cable

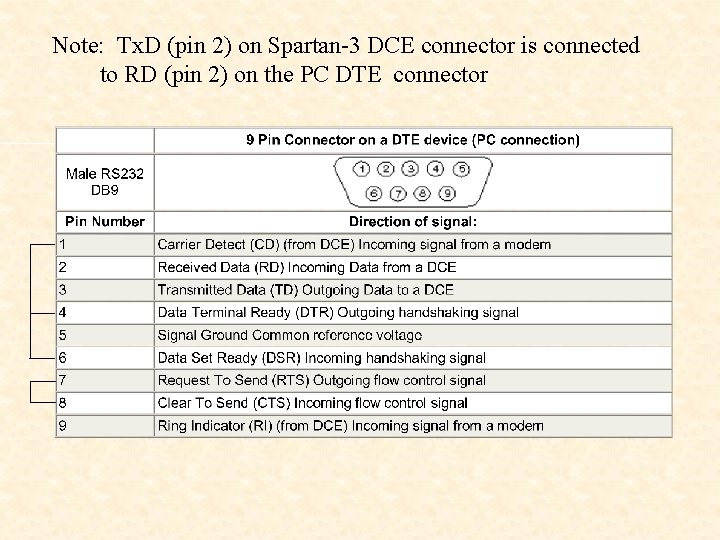

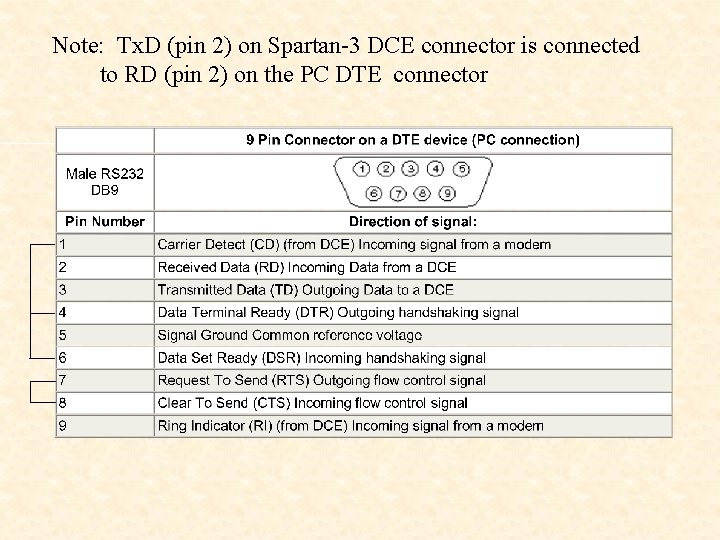

Note: Tx. D (pin 2) on Spartan-3 DCE connector is connected to RD (pin 2) on the PC DTE connector

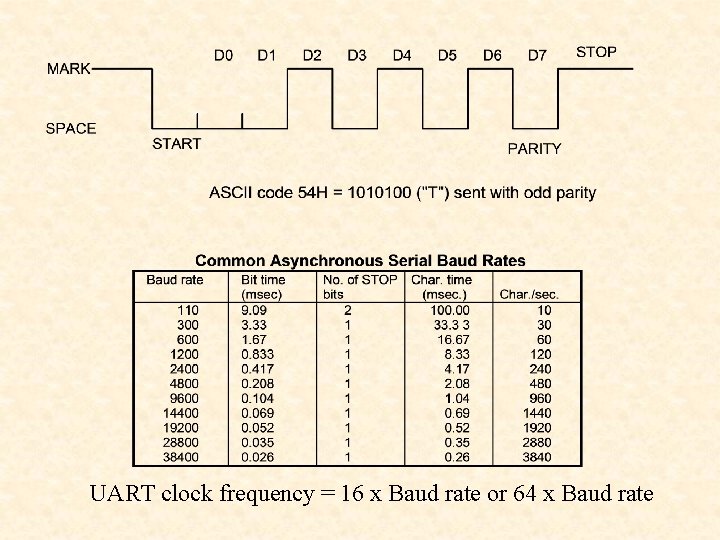

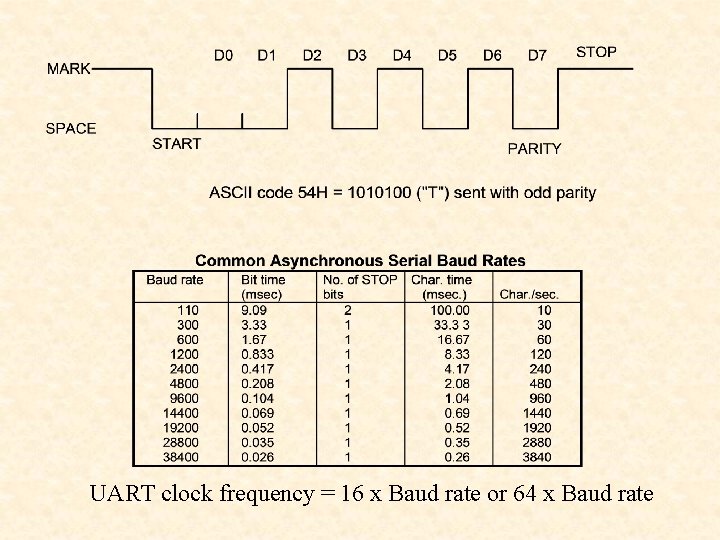

UART clock frequency = 16 x Baud rate or 64 x Baud rate

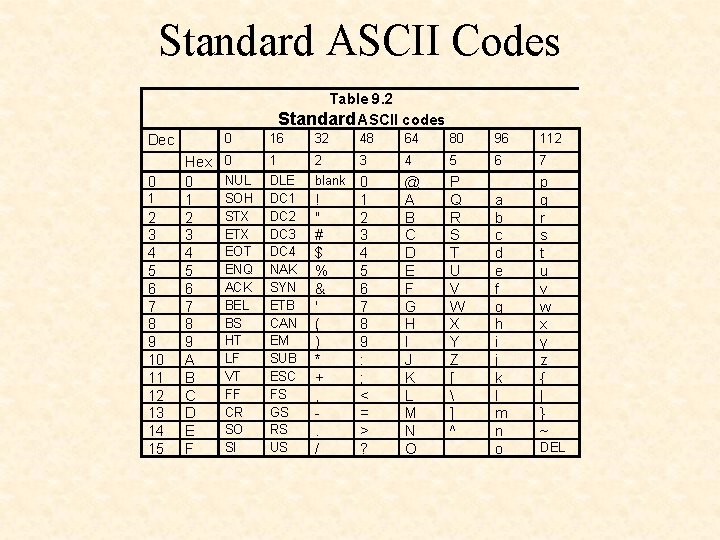

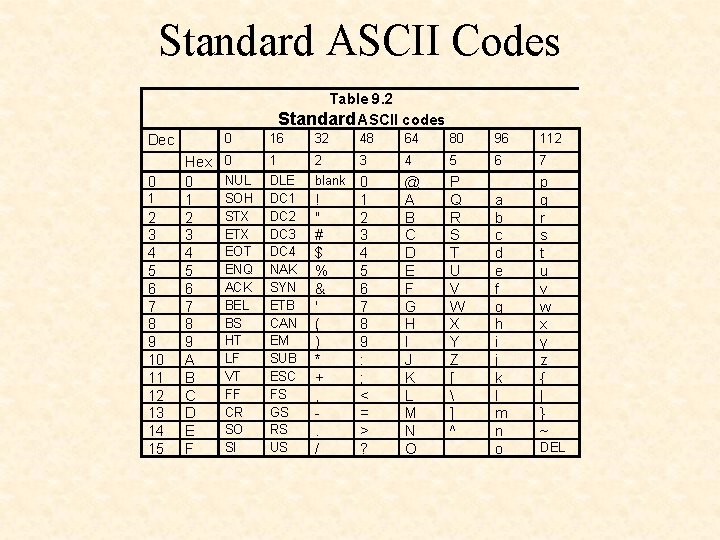

Standard ASCII Codes Table 9. 2 Standard ASCII codes Dec 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Hex 0 1 2 3 4 5 6 7 8 9 A B C D E F 0 16 32 48 64 80 96 112 0 1 2 3 4 5 6 7 NUL SOH STX EOT ENQ ACK BEL BS HT LF VT FF CR SO SI DLE DC 1 DC 2 DC 3 DC 4 NAK SYN ETB CAN EM SUB ESC FS GS RS US blank 0 1 2 3 4 5 6 7 8 9 : ; < = > ? @ A B C D E F G H I J K L M N O P Q R S T U V W X Y Z [ ] ^ _ ! " # $ % & ' ( ) * + , . / a b c d e f g h i j k l m n o p q r s t u v w x y z { | } ~ DEL

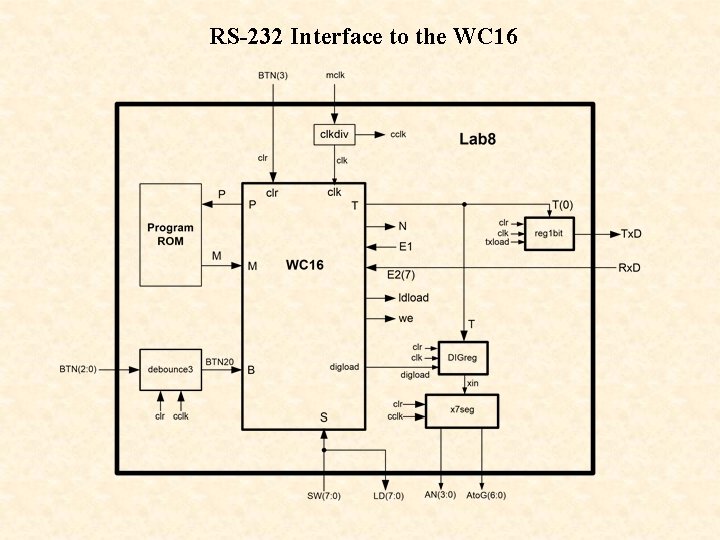

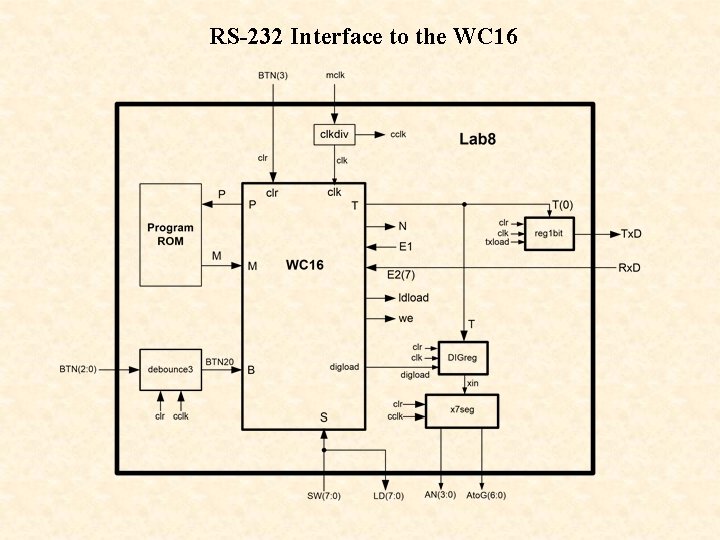

RS-232 Interface to the WC 16

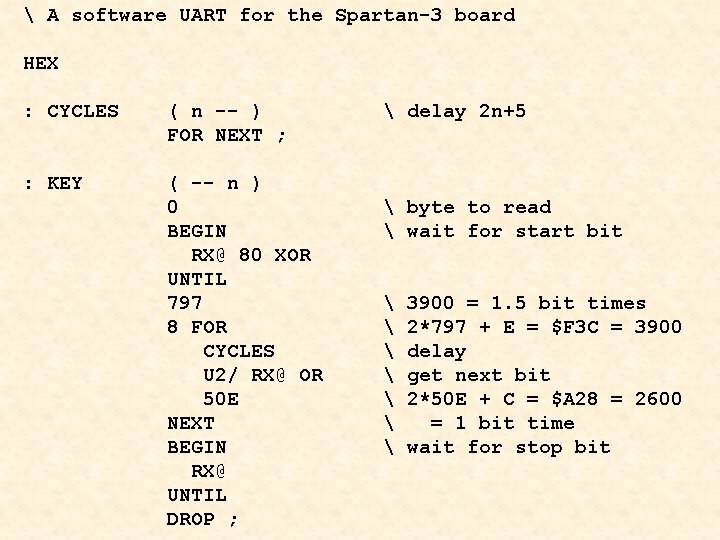

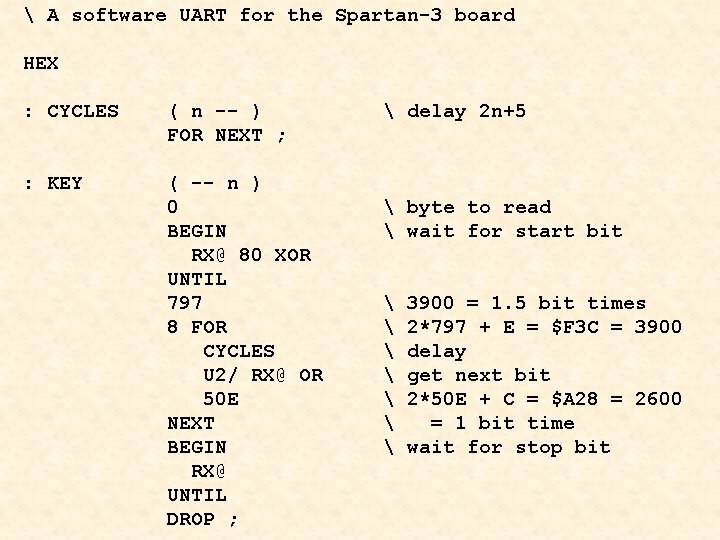

A software UART for the Spartan-3 board HEX : CYCLES ( n -- ) FOR NEXT ; : KEY ( -- n ) 0 BEGIN RX@ 80 XOR UNTIL 797 8 FOR CYCLES U 2/ RX@ OR 50 E NEXT BEGIN RX@ UNTIL DROP ; delay 2 n+5 byte to read wait for start bit 3900 = 1. 5 bit times 2*797 + E = $F 3 C = 3900 delay get next bit 2*50 E + C = $A 28 = 2600 = 1 bit time wait for stop bit

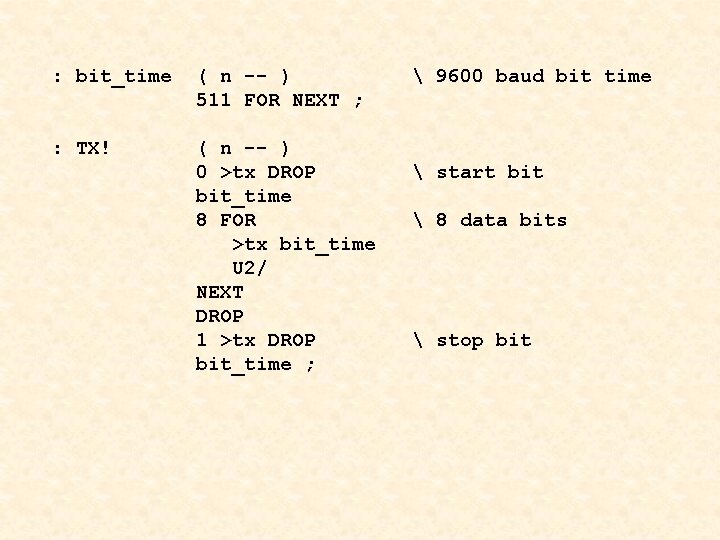

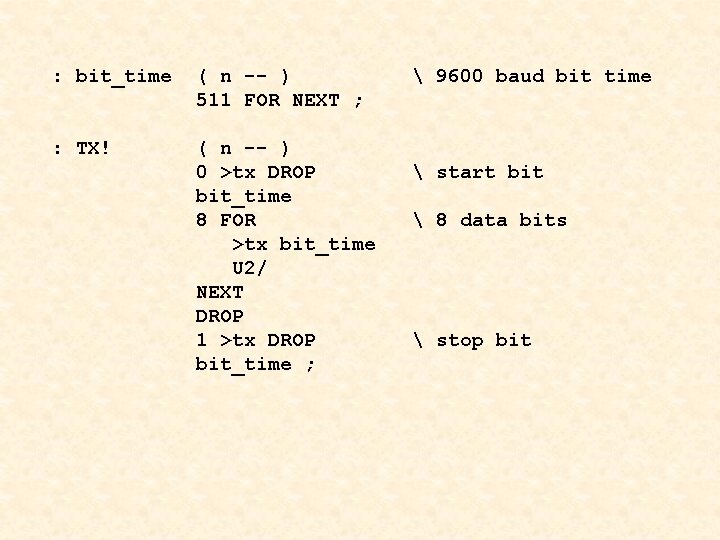

: bit_time ( n -- ) 511 FOR NEXT ; : TX! ( n -- ) 0 >tx DROP bit_time 8 FOR >tx bit_time U 2/ NEXT DROP 1 >tx DROP bit_time ; 9600 baud bit time start bit 8 data bits stop bit

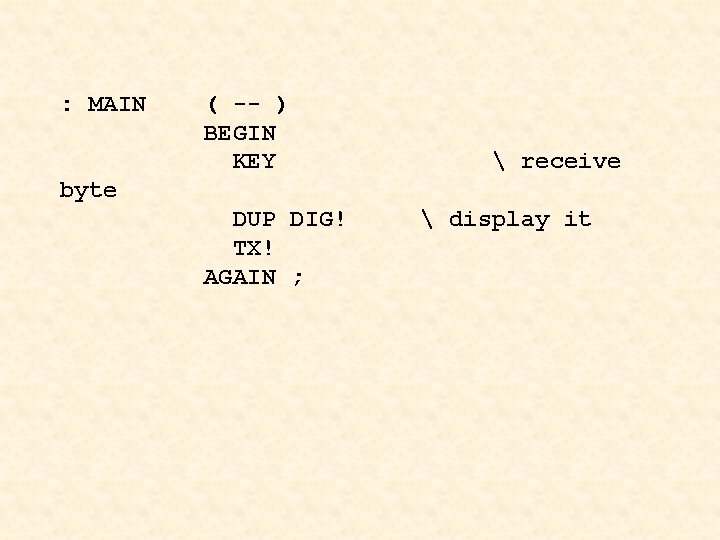

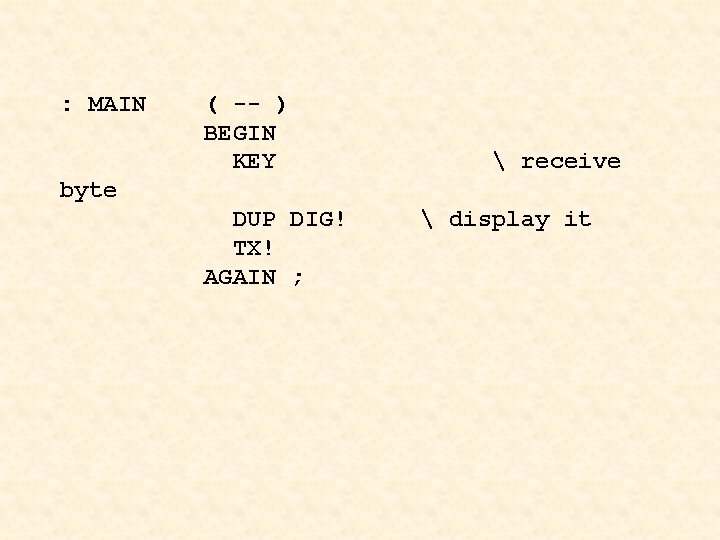

: MAIN ( -- ) BEGIN KEY receive byte DUP DIG! TX! AGAIN ; display it

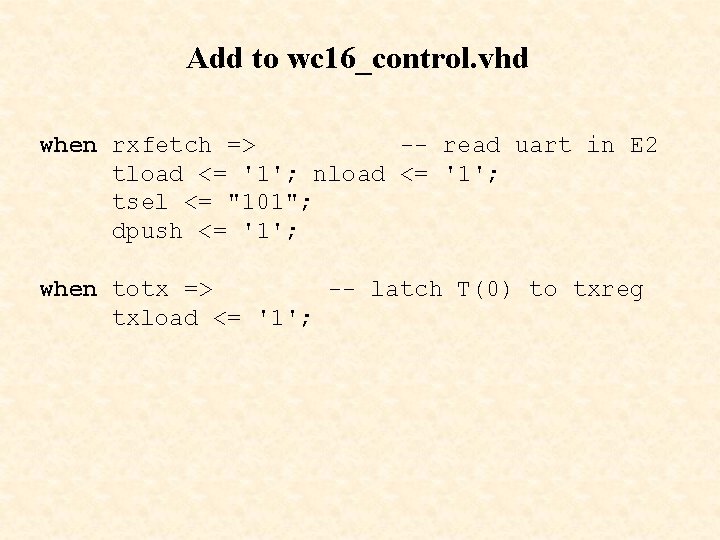

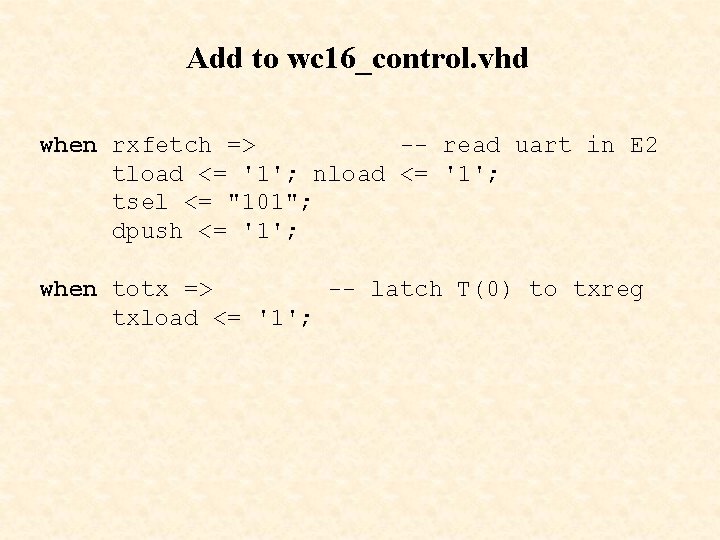

Add to wc 16_control. vhd when rxfetch => -- read uart in E 2 tload <= '1'; nload <= '1'; tsel <= "101"; dpush <= '1'; when totx => -- latch T(0) to txreg txload <= '1';

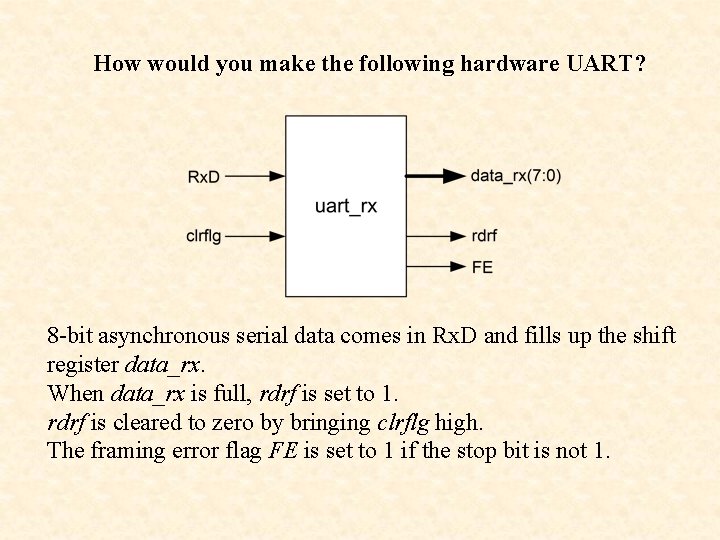

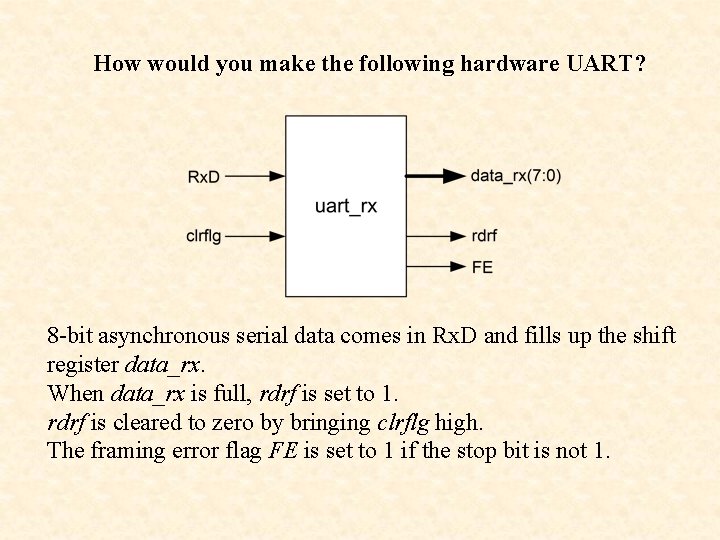

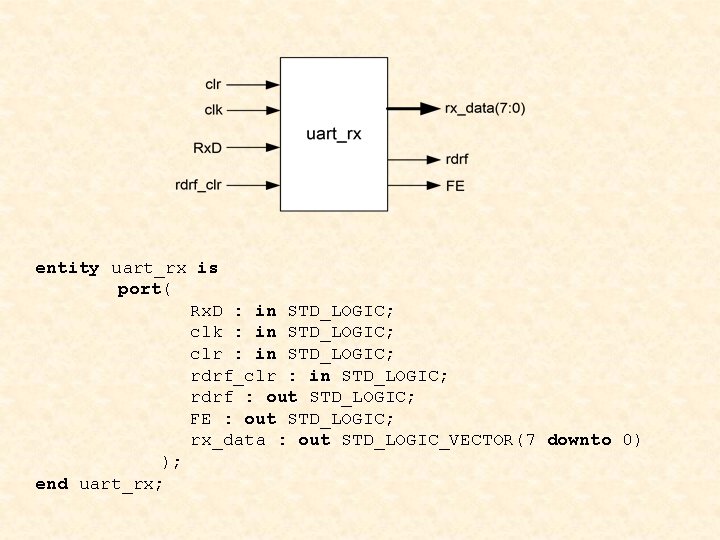

How would you make the following hardware UART? 8 -bit asynchronous serial data comes in Rx. D and fills up the shift register data_rx. When data_rx is full, rdrf is set to 1. rdrf is cleared to zero by bringing clrflg high. The framing error flag FE is set to 1 if the stop bit is not 1.

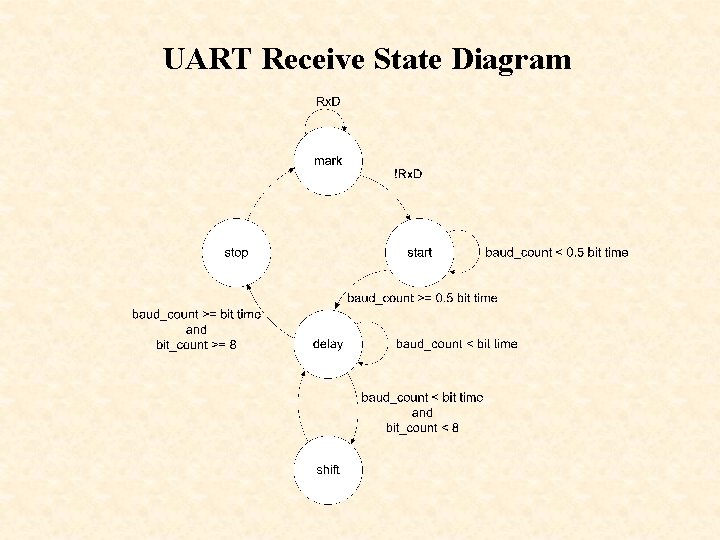

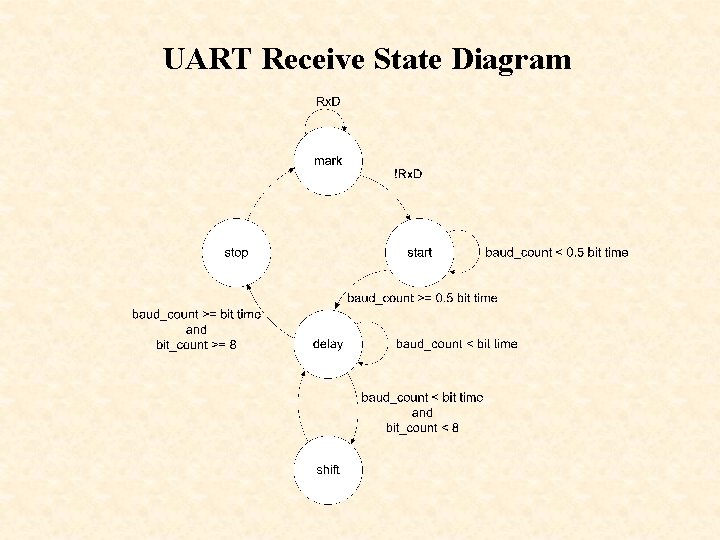

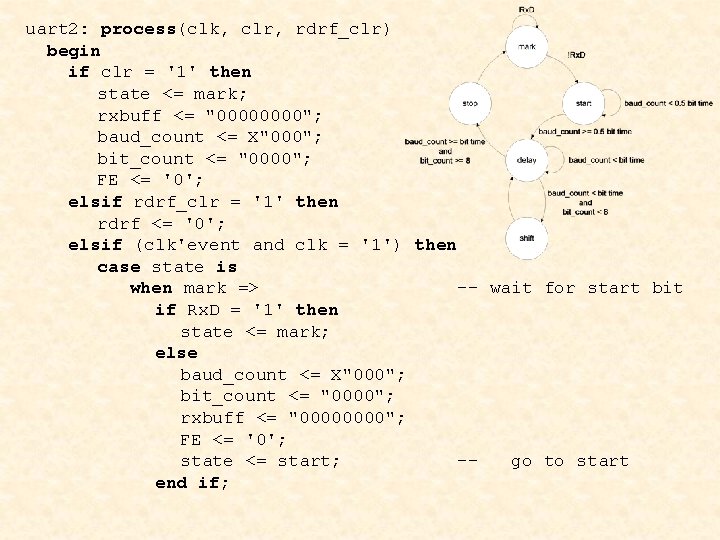

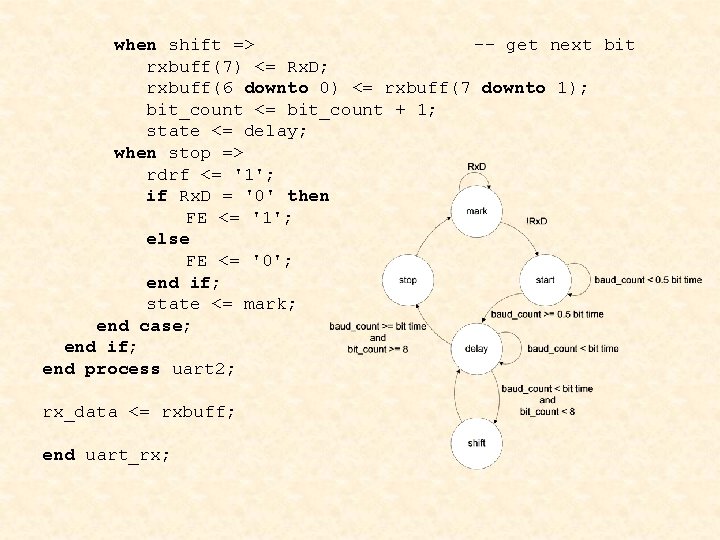

UART Receive State Diagram

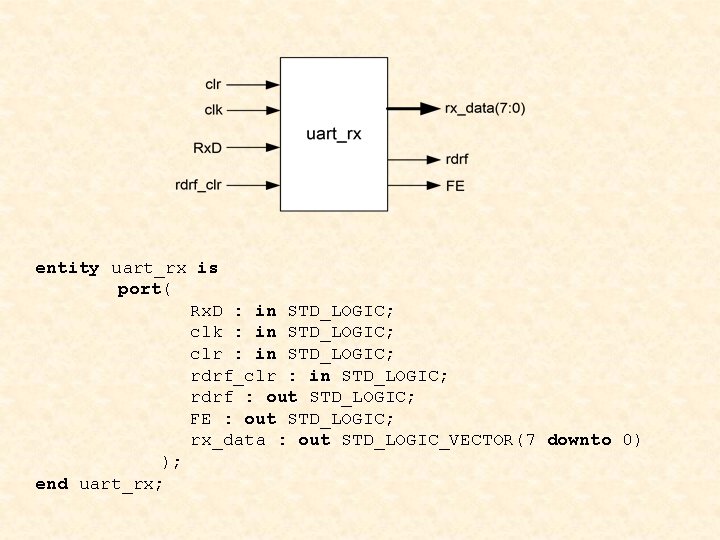

entity uart_rx is port( Rx. D : in STD_LOGIC; clk : in STD_LOGIC; clr : in STD_LOGIC; rdrf_clr : in STD_LOGIC; rdrf : out STD_LOGIC; FE : out STD_LOGIC; rx_data : out STD_LOGIC_VECTOR(7 downto 0) ); end uart_rx;

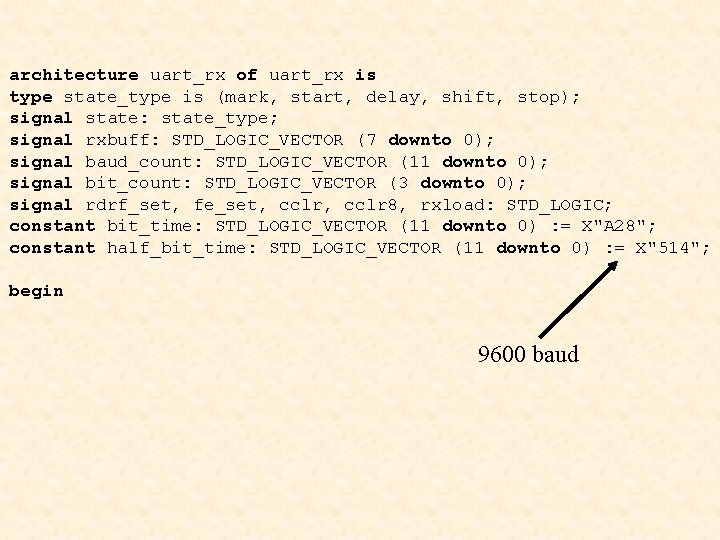

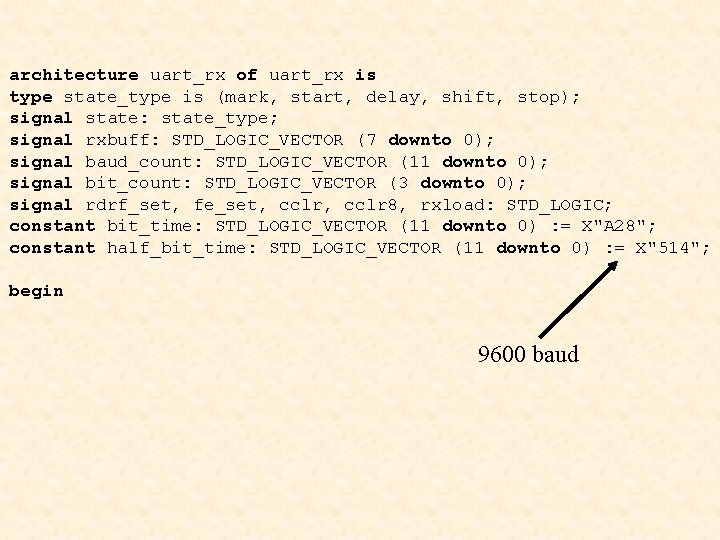

architecture uart_rx of uart_rx is type state_type is (mark, start, delay, shift, stop); signal state: state_type; signal rxbuff: STD_LOGIC_VECTOR (7 downto 0); signal baud_count: STD_LOGIC_VECTOR (11 downto 0); signal bit_count: STD_LOGIC_VECTOR (3 downto 0); signal rdrf_set, fe_set, cclr 8, rxload: STD_LOGIC; constant bit_time: STD_LOGIC_VECTOR (11 downto 0) : = X"A 28"; constant half_bit_time: STD_LOGIC_VECTOR (11 downto 0) : = X"514"; begin 9600 baud

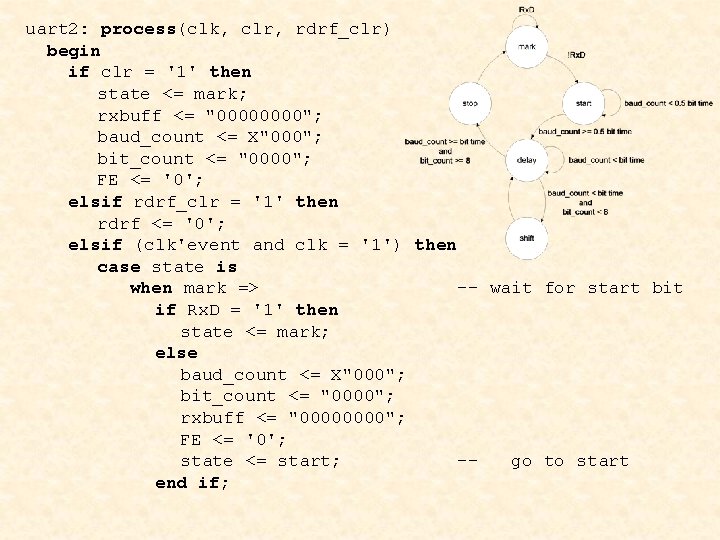

uart 2: process(clk, clr, rdrf_clr) begin if clr = '1' then state <= mark; rxbuff <= "0000"; baud_count <= X"000"; bit_count <= "0000"; FE <= '0'; elsif rdrf_clr = '1' then rdrf <= '0'; elsif (clk'event and clk = '1') then case state is when mark => -- wait for start bit if Rx. D = '1' then state <= mark; else baud_count <= X"000"; bit_count <= "0000"; rxbuff <= "0000"; FE <= '0'; state <= start; -go to start end if;

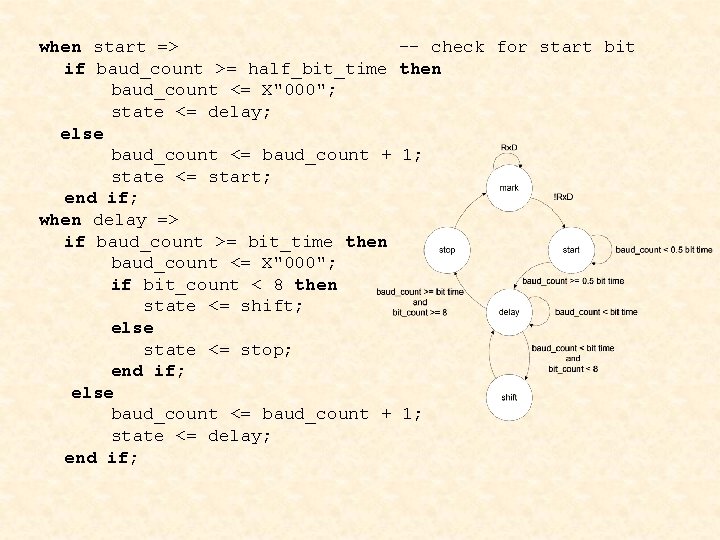

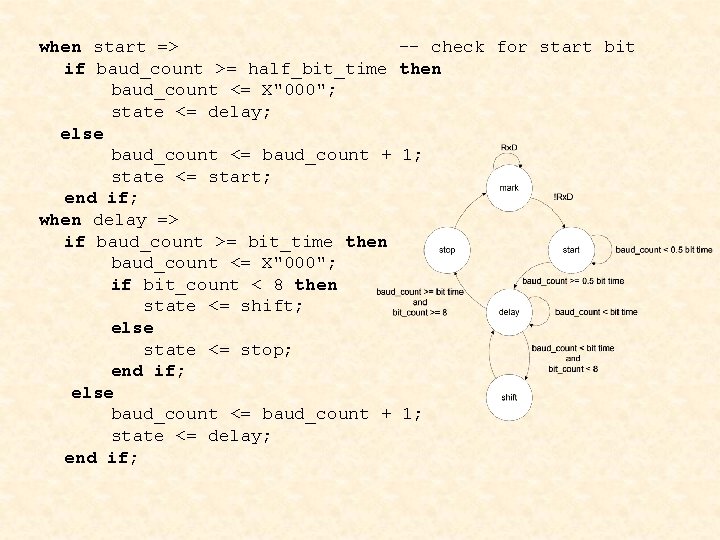

when start => if baud_count >= half_bit_time baud_count <= X"000"; state <= delay; else baud_count <= baud_count + state <= start; end if; when delay => if baud_count >= bit_time then baud_count <= X"000"; if bit_count < 8 then state <= shift; else state <= stop; end if; else baud_count <= baud_count + state <= delay; end if; -- check for start bit then 1;

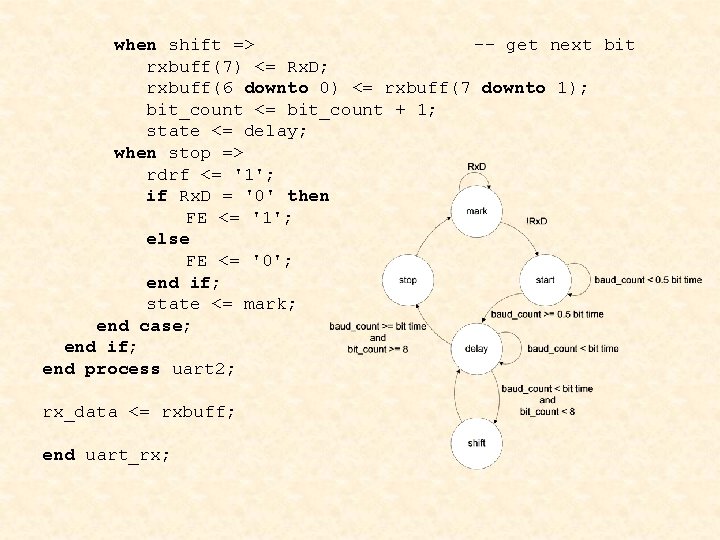

when shift => -- get next bit rxbuff(7) <= Rx. D; rxbuff(6 downto 0) <= rxbuff(7 downto 1); bit_count <= bit_count + 1; state <= delay; when stop => rdrf <= '1'; if Rx. D = '0' then FE <= '1'; else FE <= '0'; end if; state <= mark; end case; end if; end process uart 2; rx_data <= rxbuff; end uart_rx;

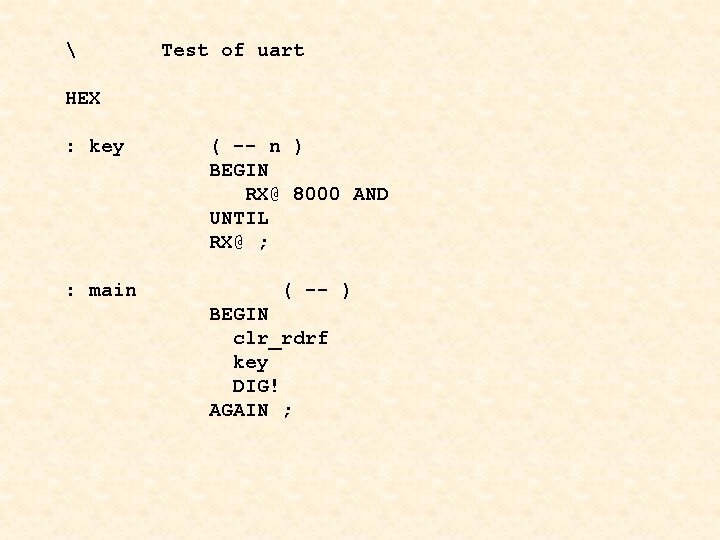

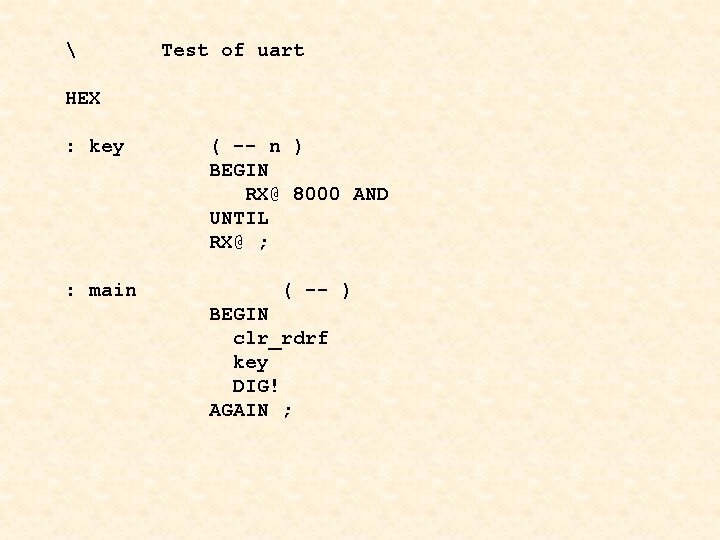

Test of uart HEX : key : main ( -- n ) BEGIN RX@ 8000 AND UNTIL RX@ ; ( -- ) BEGIN clr_rdrf key DIG! AGAIN ;