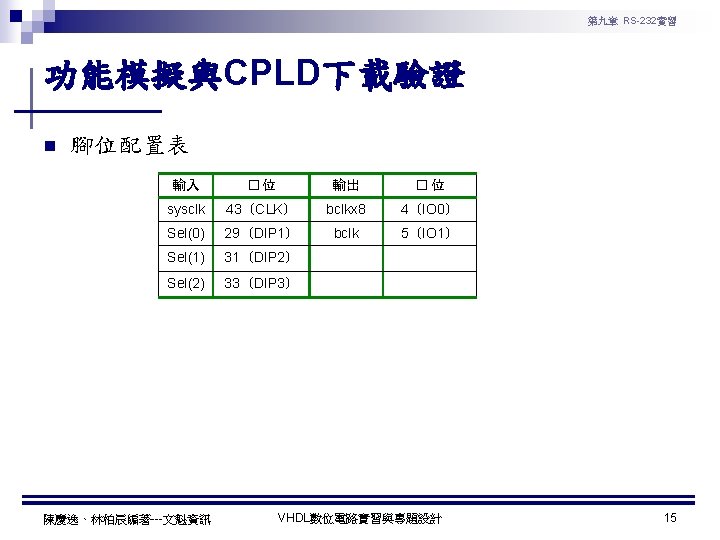

RS232 1 2 RS232 3 brgen vhd 4

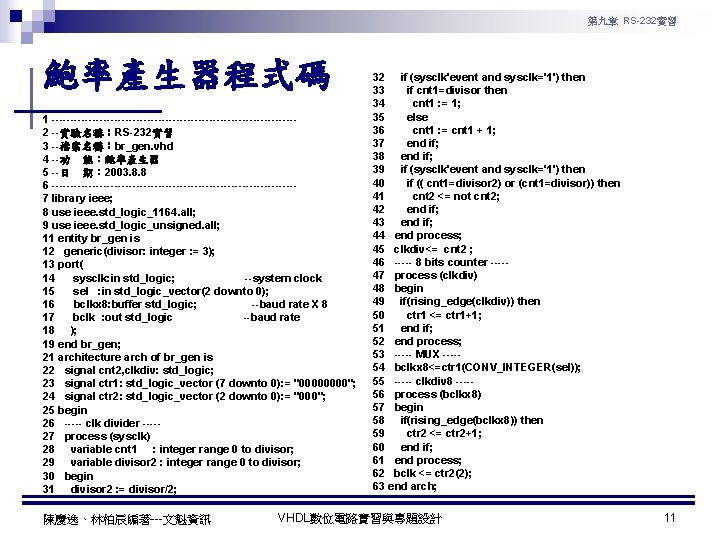

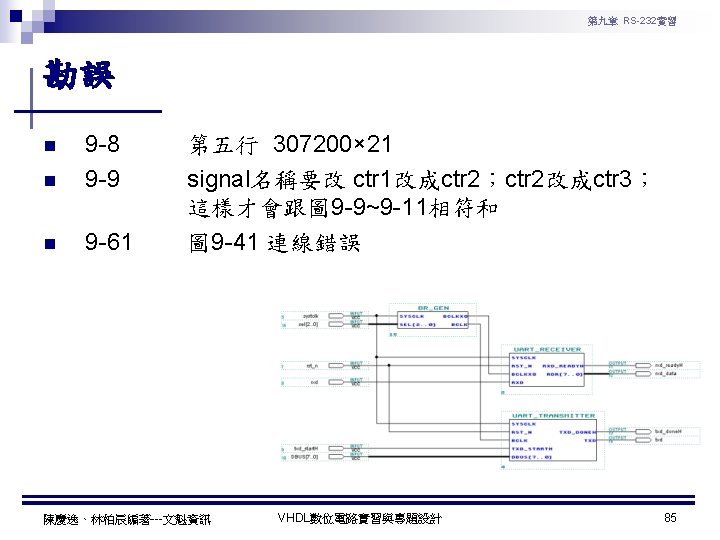

第九章 RS-232實習 鮑率產生器程式碼 1 ---------------------------------2 --實驗名稱:RS-232實習 3 --檔案名稱:br_gen. vhd 4 --功 能:鮑率產生器 5 --日 期: 2003. 8. 8 6 ---------------------------------7 library ieee; 8 use ieee. std_logic_1164. all; 9 use ieee. std_logic_unsigned. all; 11 entity br_gen is 12 generic(divisor: integer : = 3); 13 port( 14 sysclk: in std_logic; --system clock 15 sel : in std_logic_vector(2 downto 0); 16 bclkx 8: buffer std_logic; --baud rate X 8 17 bclk : out std_logic --baud rate 18 ); 19 end br_gen; 21 architecture arch of br_gen is 22 signal cnt 2, clkdiv: std_logic; 23 signal ctr 1: std_logic_vector (7 downto 0): = "0000"; 24 signal ctr 2: std_logic_vector (2 downto 0): = "000"; 25 begin 26 ----- clk divider ----27 process (sysclk) 28 variable cnt 1 : integer range 0 to divisor; 29 variable divisor 2 : integer range 0 to divisor; 30 begin 31 divisor 2 : = divisor/2; 陳慶逸、林柏辰編著---文魁資訊 32 if (sysclk'event and sysclk='1') then 33 if cnt 1=divisor then 34 cnt 1 : = 1; 35 else 36 cnt 1 : = cnt 1 + 1; 37 end if; 38 end if; 39 if (sysclk'event and sysclk='1') then 40 if (( cnt 1=divisor 2) or (cnt 1=divisor)) then 41 cnt 2 <= not cnt 2; 42 end if; 43 end if; 44 end process; 45 clkdiv<= cnt 2 ; 46 ----- 8 bits counter ----47 process (clkdiv) 48 begin 49 if(rising_edge(clkdiv)) then 50 ctr 1 <= ctr 1+1; 51 end if; 52 end process; 53 ----- MUX ----54 bclkx 8<=ctr 1(CONV_INTEGER(sel)); 55 ----- clkdiv 8 ----56 process (bclkx 8) 57 begin 58 if(rising_edge(bclkx 8)) then 59 ctr 2 <= ctr 2+1; 60 end if; 61 end process; 62 bclk <= ctr 2(2); 63 end arch; VHDL數位電路實習與專題設計 11

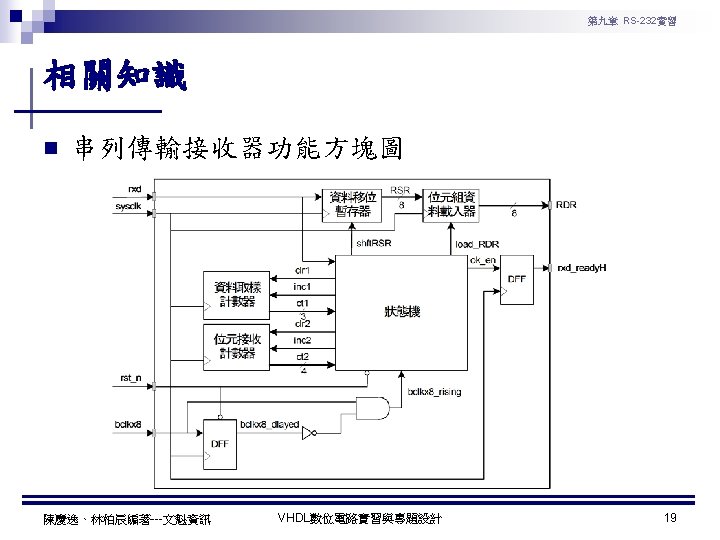

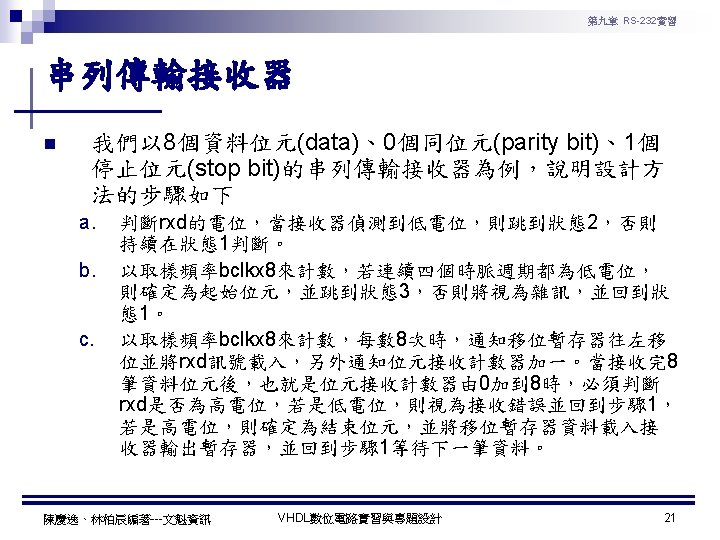

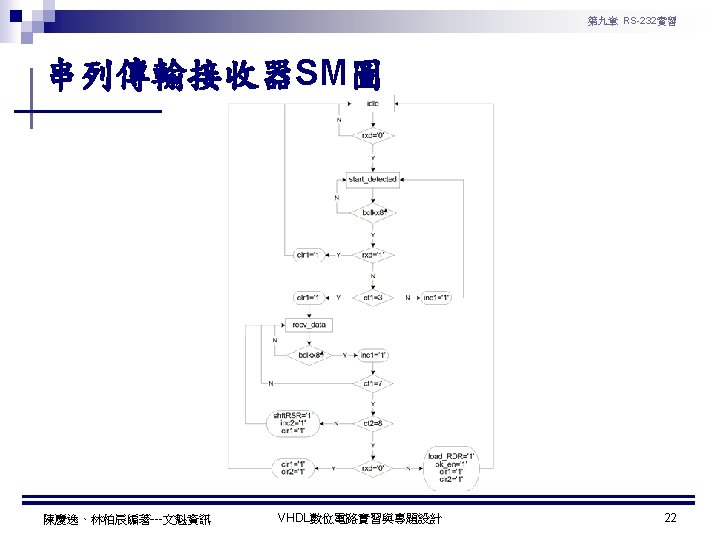

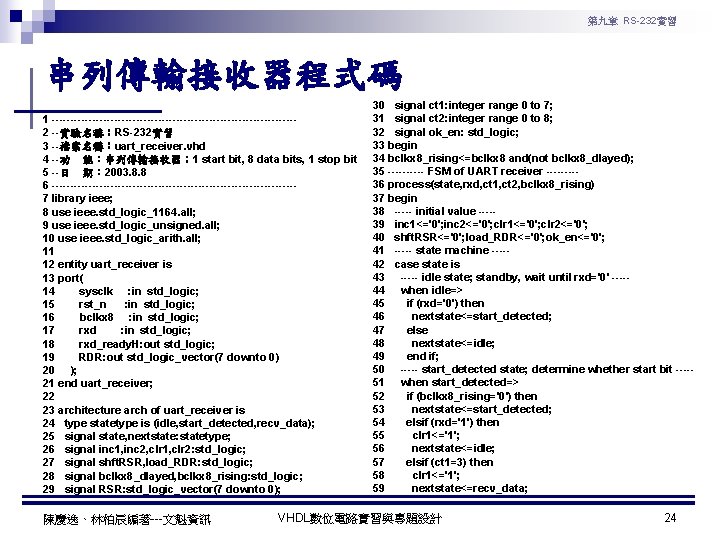

第九章 RS-232實習 串列傳輸接收器程式碼 1 ---------------------------------2 --實驗名稱:RS-232實習 3 --檔案名稱:uart_receiver. vhd 4 --功 能:串列傳輸接收器; 1 start bit, 8 data bits, 1 stop bit 5 --日 期: 2003. 8. 8 6 ---------------------------------7 library ieee; 8 use ieee. std_logic_1164. all; 9 use ieee. std_logic_unsigned. all; 10 use ieee. std_logic_arith. all; 11 12 entity uart_receiver is 13 port( 14 sysclk : in std_logic; 15 rst_n : in std_logic; 16 bclkx 8 : in std_logic; 17 rxd : in std_logic; 18 rxd_ready. H: out std_logic; 19 RDR: out std_logic_vector(7 downto 0) 20 ); 21 end uart_receiver; 22 23 architecture arch of uart_receiver is 24 type statetype is (idle, start_detected, recv_data); 25 signal state, nextstate: statetype; 26 signal inc 1, inc 2, clr 1, clr 2: std_logic; 27 signal shft. RSR, load_RDR: std_logic; 28 signal bclkx 8_dlayed, bclkx 8_rising: std_logic; 29 signal RSR: std_logic_vector(7 downto 0); 陳慶逸、林柏辰編著---文魁資訊 30 signal ct 1: integer range 0 to 7; 31 signal ct 2: integer range 0 to 8; 32 signal ok_en: std_logic; 33 begin 34 bclkx 8_rising<=bclkx 8 and(not bclkx 8_dlayed); 35 ----- FSM of UART receiver ----36 process(state, rxd, ct 1, ct 2, bclkx 8_rising) 37 begin 38 ----- initial value ----39 inc 1<='0'; inc 2<='0'; clr 1<='0'; clr 2<='0'; 40 shft. RSR<='0'; load_RDR<='0'; ok_en<='0'; 41 ----- state machine ----42 case state is 43 ----- idle state; standby, wait until rxd='0' ----44 when idle=> 45 if (rxd='0') then 46 nextstate<=start_detected; 47 else 48 nextstate<=idle; 49 end if; 50 ----- start_detected state; determine whether start bit ----51 when start_detected=> 52 if (bclkx 8_rising='0') then 53 nextstate<=start_detected; 54 elsif (rxd='1') then 55 clr 1<='1'; 56 nextstate<=idle; 57 elsif (ct 1=3) then 58 clr 1<='1'; 59 nextstate<=recv_data; VHDL數位電路實習與專題設計 24

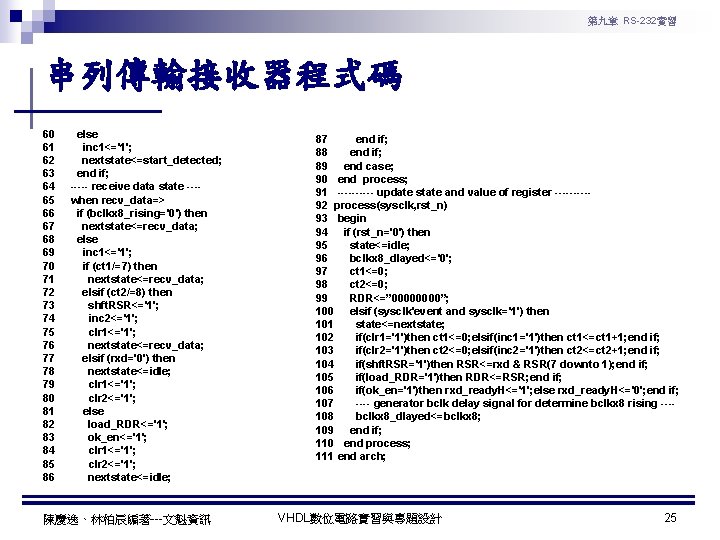

第九章 RS-232實習 串列傳輸接收器程式碼 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 84 85 86 else inc 1<='1'; nextstate<=start_detected; end if; ----- receive data state ---when recv_data=> if (bclkx 8_rising='0') then nextstate<=recv_data; else inc 1<='1'; if (ct 1/=7) then nextstate<=recv_data; elsif (ct 2/=8) then shft. RSR<='1'; inc 2<='1'; clr 1<='1'; nextstate<=recv_data; elsif (rxd='0') then nextstate<=idle; clr 1<='1'; clr 2<='1'; else load_RDR<='1'; ok_en<='1'; clr 1<='1'; clr 2<='1'; nextstate<=idle; 陳慶逸、林柏辰編著---文魁資訊 87 end if; 88 end if; 89 end case; 90 end process; 91 ----- update state and value of register -----92 process(sysclk, rst_n) 93 begin 94 if (rst_n='0') then 95 state<=idle; 96 bclkx 8_dlayed<='0'; 97 ct 1<=0; 98 ct 2<=0; 99 RDR<=” 0000”; 100 elsif (sysclk'event and sysclk='1') then 101 state<=nextstate; 102 if(clr 1='1')then ct 1<=0; elsif(inc 1='1')then ct 1<=ct 1+1; end if; 103 if(clr 2='1')then ct 2<=0; elsif(inc 2='1')then ct 2<=ct 2+1; end if; 104 if(shft. RSR='1')then RSR<=rxd & RSR(7 downto 1); end if; 105 if(load_RDR='1')then RDR<=RSR; end if; 106 if(ok_en='1')then rxd_ready. H<='1'; else rxd_ready. H<='0'; end if; 107 ---- generator bclk delay signal for determine bclkx 8 rising ---108 bclkx 8_dlayed<=bclkx 8; 109 end if; 110 end process; 111 end arch; VHDL數位電路實習與專題設計 25

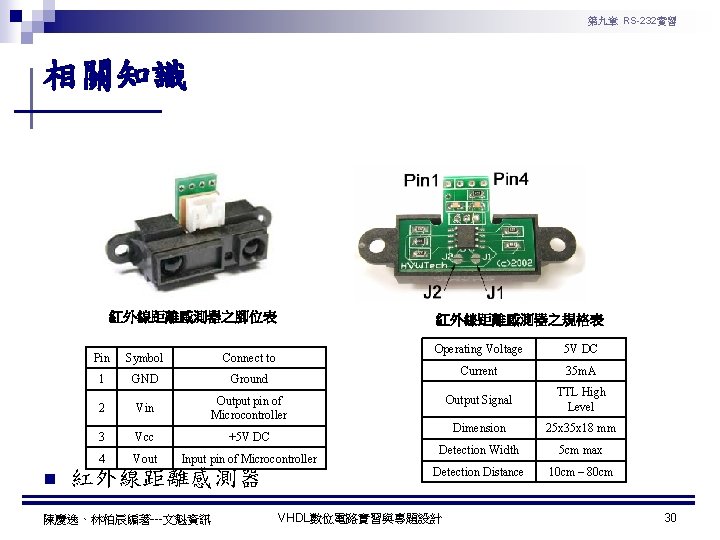

第九章 RS-232實習 相關知識 紅外線距離感測器之腳位表 n 紅外線距離感測器之規格表 Pin Symbol Connect to 1 GND Ground 2 Vin Output pin of Microcontroller 3 Vcc +5 V DC 4 Vout Input pin of Microcontroller 紅外線距離感測器 陳慶逸、林柏辰編著---文魁資訊 Operating Voltage 5 V DC Current 35 m. A Output Signal TTL High Level Dimension 25 x 35 x 18 mm Detection Width 5 cm max Detection Distance 10 cm – 80 cm VHDL數位電路實習與專題設計 30

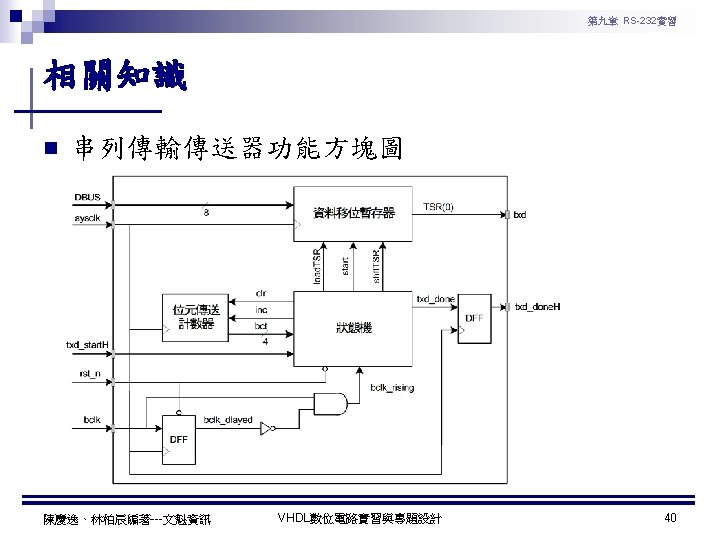

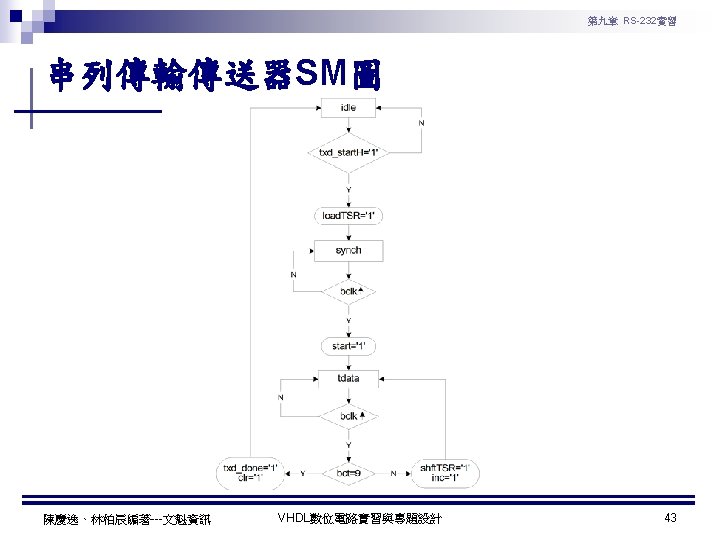

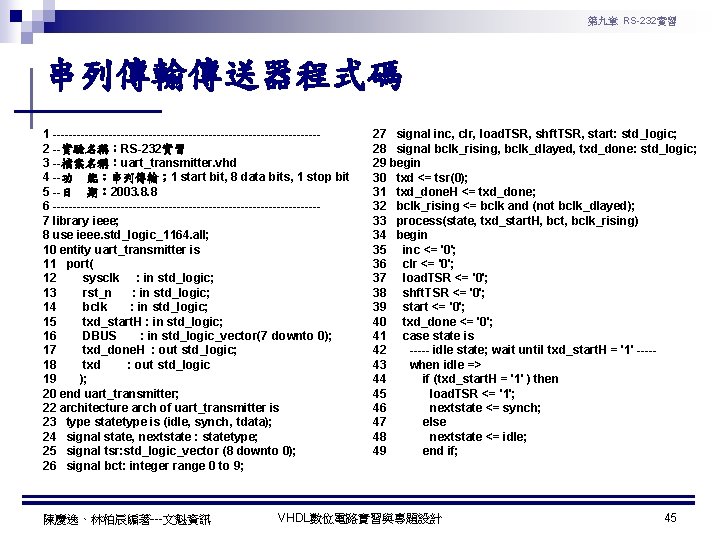

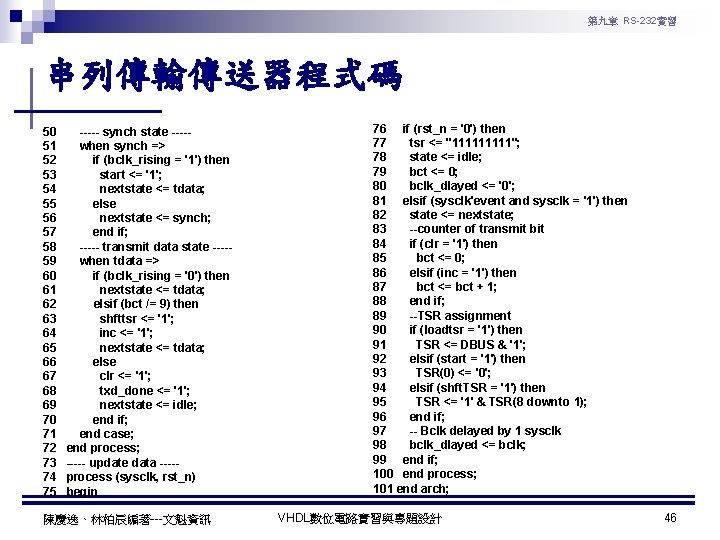

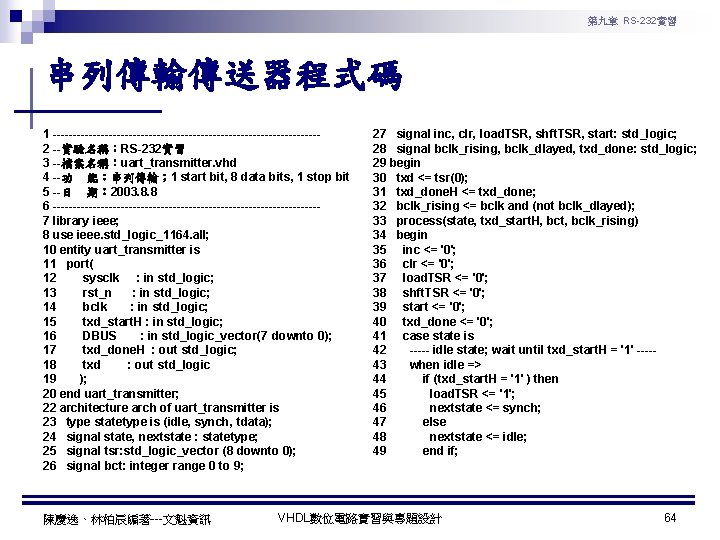

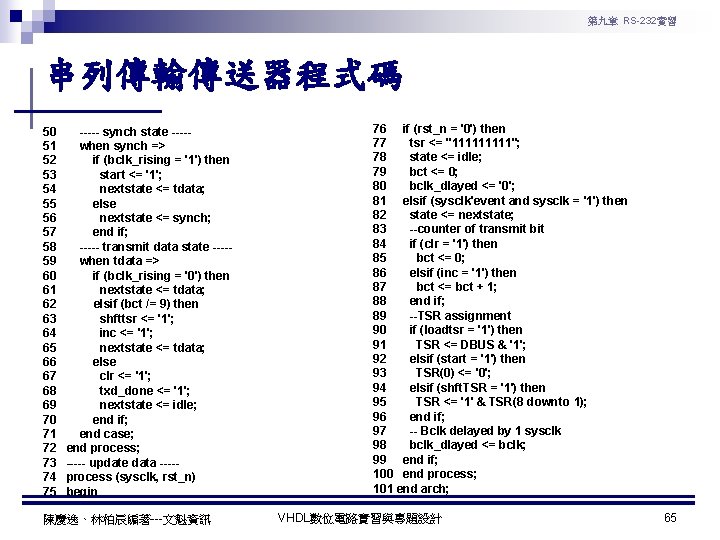

第九章 RS-232實習 串列傳輸傳送器程式碼 1 ---------------------------------2 --實驗名稱:RS-232實習 3 --檔案名稱:uart_transmitter. vhd 4 --功 能:串列傳輸; 1 start bit, 8 data bits, 1 stop bit 5 --日 期: 2003. 8. 8 6 ---------------------------------7 library ieee; 8 use ieee. std_logic_1164. all; 10 entity uart_transmitter is 11 port( 12 sysclk : in std_logic; 13 rst_n : in std_logic; 14 bclk : in std_logic; 15 txd_start. H : in std_logic; 16 DBUS : in std_logic_vector(7 downto 0); 17 txd_done. H : out std_logic; 18 txd : out std_logic 19 ); 20 end uart_transmitter; 22 architecture arch of uart_transmitter is 23 type statetype is (idle, synch, tdata); 24 signal state, nextstate : statetype; 25 signal tsr: std_logic_vector (8 downto 0); 26 signal bct: integer range 0 to 9; 陳慶逸、林柏辰編著---文魁資訊 27 signal inc, clr, load. TSR, shft. TSR, start: std_logic; 28 signal bclk_rising, bclk_dlayed, txd_done: std_logic; 29 begin 30 txd <= tsr(0); 31 txd_done. H <= txd_done; 32 bclk_rising <= bclk and (not bclk_dlayed); 33 process(state, txd_start. H, bct, bclk_rising) 34 begin 35 inc <= '0'; 36 clr <= '0'; 37 load. TSR <= '0'; 38 shft. TSR <= '0'; 39 start <= '0'; 40 txd_done <= '0'; 41 case state is 42 ----- idle state; wait until txd_start. H = '1' ----43 when idle => 44 if (txd_start. H = '1' ) then 45 load. TSR <= '1'; 46 nextstate <= synch; 47 else 48 nextstate <= idle; 49 end if; VHDL數位電路實習與專題設計 45

第九章 RS-232實習 串列傳輸傳送器程式碼 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 ----- synch state ----when synch => if (bclk_rising = '1') then start <= '1'; nextstate <= tdata; else nextstate <= synch; end if; ----- transmit data state ----when tdata => if (bclk_rising = '0') then nextstate <= tdata; elsif (bct /= 9) then shfttsr <= '1'; inc <= '1'; nextstate <= tdata; else clr <= '1'; txd_done <= '1'; nextstate <= idle; end if; end case; end process; ----- update data ----process (sysclk, rst_n) begin 陳慶逸、林柏辰編著---文魁資訊 76 if (rst_n = '0') then 77 tsr <= "11111"; 78 state <= idle; 79 bct <= 0; 80 bclk_dlayed <= '0'; 81 elsif (sysclk'event and sysclk = '1') then 82 state <= nextstate; 83 --counter of transmit bit 84 if (clr = '1') then 85 bct <= 0; 86 elsif (inc = '1') then 87 bct <= bct + 1; 88 end if; 89 --TSR assignment 90 if (loadtsr = '1') then 91 TSR <= DBUS & '1'; 92 elsif (start = '1') then 93 TSR(0) <= '0'; 94 elsif (shft. TSR = '1') then 95 TSR <= '1' & TSR(8 downto 1); 96 end if; 97 -- Bclk delayed by 1 sysclk 98 bclk_dlayed <= bclk; 99 end if; 100 end process; 101 end arch; VHDL數位電路實習與專題設計 46

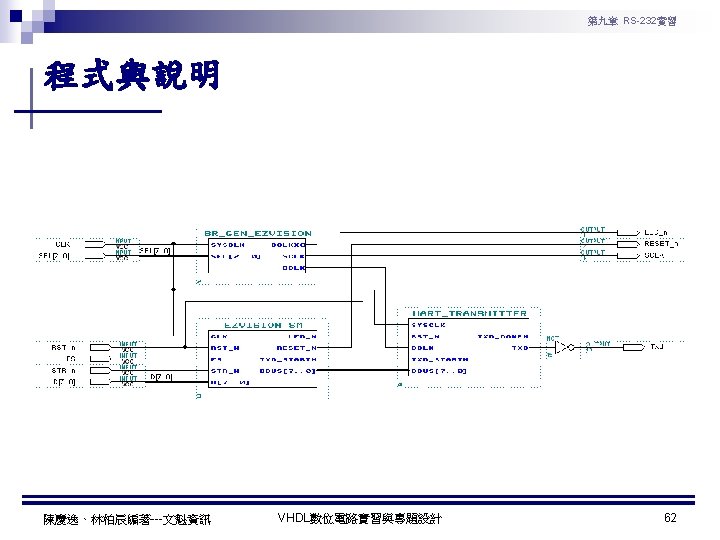

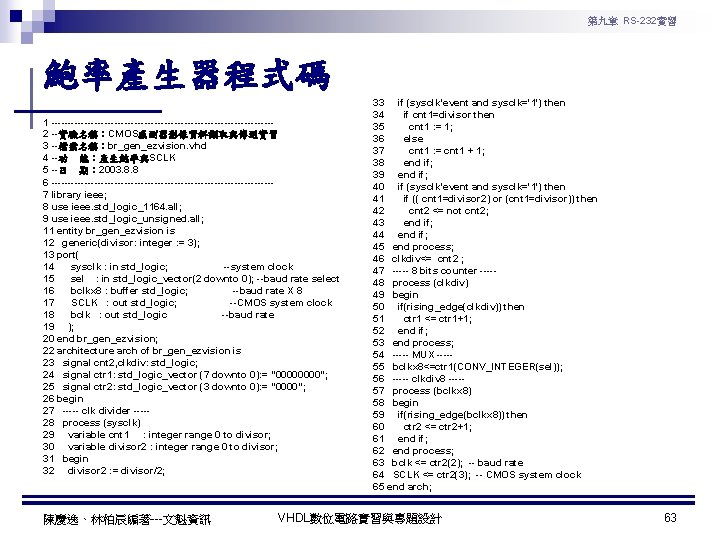

第九章 RS-232實習 鮑率產生器程式碼 1 ---------------------------------2 --實驗名稱:CMOS感測器影像資料擷取與傳送實習 3 --檔案名稱:br_gen_ezvision. vhd 4 --功 能:產生鮑率與SCLK 5 --日 期: 2003. 8. 8 6 ---------------------------------7 library ieee; 8 use ieee. std_logic_1164. all; 9 use ieee. std_logic_unsigned. all; 11 entity br_gen_ezvision is 12 generic(divisor: integer : = 3); 13 port( 14 sysclk : in std_logic; --system clock 15 sel : in std_logic_vector(2 downto 0); --baud rate select 16 bclkx 8 : buffer std_logic; --baud rate X 8 17 SCLK : out std_logic; --CMOS system clock 18 bclk : out std_logic --baud rate 19 ); 20 end br_gen_ezvision; 22 architecture arch of br_gen_ezvision is 23 signal cnt 2, clkdiv: std_logic; 24 signal ctr 1: std_logic_vector (7 downto 0): = "0000"; 25 signal ctr 2: std_logic_vector (3 downto 0): = "0000"; 26 begin 27 ----- clk divider ----28 process (sysclk) 29 variable cnt 1 : integer range 0 to divisor; 30 variable divisor 2 : integer range 0 to divisor; 31 begin 32 divisor 2 : = divisor/2; 陳慶逸、林柏辰編著---文魁資訊 33 if (sysclk'event and sysclk='1') then 34 if cnt 1=divisor then 35 cnt 1 : = 1; 36 else 37 cnt 1 : = cnt 1 + 1; 38 end if; 39 end if; 40 if (sysclk'event and sysclk='1') then 41 if (( cnt 1=divisor 2) or (cnt 1=divisor)) then 42 cnt 2 <= not cnt 2; 43 end if; 44 end if; 45 end process; 46 clkdiv<= cnt 2 ; 47 ----- 8 bits counter ----48 process (clkdiv) 49 begin 50 if(rising_edge(clkdiv)) then 51 ctr 1 <= ctr 1+1; 52 end if; 53 end process; 54 ----- MUX ----55 bclkx 8<=ctr 1(CONV_INTEGER(sel)); 56 ----- clkdiv 8 ----57 process (bclkx 8) 58 begin 59 if(rising_edge(bclkx 8)) then 60 ctr 2 <= ctr 2+1; 61 end if; 62 end process; 63 bclk <= ctr 2(2); -- baud rate 64 SCLK <= ctr 2(3); -- CMOS system clock 65 end arch; VHDL數位電路實習與專題設計 63

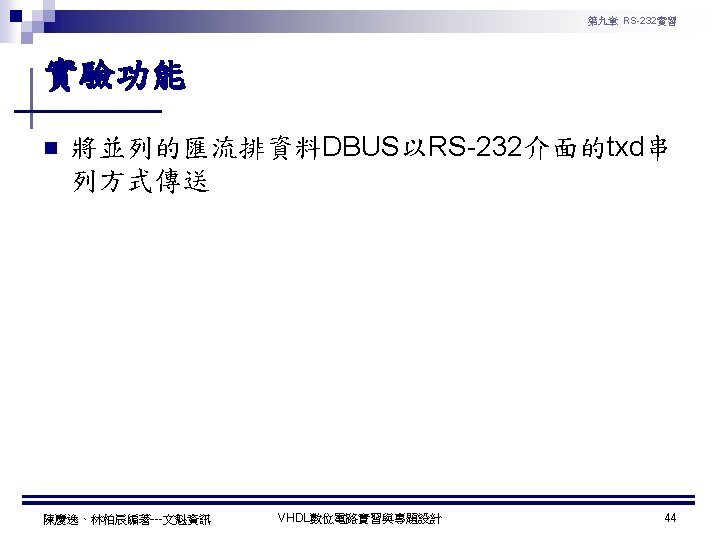

第九章 RS-232實習 串列傳輸傳送器程式碼 1 ---------------------------------2 --實驗名稱:RS-232實習 3 --檔案名稱:uart_transmitter. vhd 4 --功 能:串列傳輸; 1 start bit, 8 data bits, 1 stop bit 5 --日 期: 2003. 8. 8 6 ---------------------------------7 library ieee; 8 use ieee. std_logic_1164. all; 10 entity uart_transmitter is 11 port( 12 sysclk : in std_logic; 13 rst_n : in std_logic; 14 bclk : in std_logic; 15 txd_start. H : in std_logic; 16 DBUS : in std_logic_vector(7 downto 0); 17 txd_done. H : out std_logic; 18 txd : out std_logic 19 ); 20 end uart_transmitter; 22 architecture arch of uart_transmitter is 23 type statetype is (idle, synch, tdata); 24 signal state, nextstate : statetype; 25 signal tsr: std_logic_vector (8 downto 0); 26 signal bct: integer range 0 to 9; 陳慶逸、林柏辰編著---文魁資訊 27 signal inc, clr, load. TSR, shft. TSR, start: std_logic; 28 signal bclk_rising, bclk_dlayed, txd_done: std_logic; 29 begin 30 txd <= tsr(0); 31 txd_done. H <= txd_done; 32 bclk_rising <= bclk and (not bclk_dlayed); 33 process(state, txd_start. H, bct, bclk_rising) 34 begin 35 inc <= '0'; 36 clr <= '0'; 37 load. TSR <= '0'; 38 shft. TSR <= '0'; 39 start <= '0'; 40 txd_done <= '0'; 41 case state is 42 ----- idle state; wait until txd_start. H = '1' ----43 when idle => 44 if (txd_start. H = '1' ) then 45 load. TSR <= '1'; 46 nextstate <= synch; 47 else 48 nextstate <= idle; 49 end if; VHDL數位電路實習與專題設計 64

第九章 RS-232實習 串列傳輸傳送器程式碼 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 ----- synch state ----when synch => if (bclk_rising = '1') then start <= '1'; nextstate <= tdata; else nextstate <= synch; end if; ----- transmit data state ----when tdata => if (bclk_rising = '0') then nextstate <= tdata; elsif (bct /= 9) then shfttsr <= '1'; inc <= '1'; nextstate <= tdata; else clr <= '1'; txd_done <= '1'; nextstate <= idle; end if; end case; end process; ----- update data ----process (sysclk, rst_n) begin 陳慶逸、林柏辰編著---文魁資訊 76 if (rst_n = '0') then 77 tsr <= "11111"; 78 state <= idle; 79 bct <= 0; 80 bclk_dlayed <= '0'; 81 elsif (sysclk'event and sysclk = '1') then 82 state <= nextstate; 83 --counter of transmit bit 84 if (clr = '1') then 85 bct <= 0; 86 elsif (inc = '1') then 87 bct <= bct + 1; 88 end if; 89 --TSR assignment 90 if (loadtsr = '1') then 91 TSR <= DBUS & '1'; 92 elsif (start = '1') then 93 TSR(0) <= '0'; 94 elsif (shft. TSR = '1') then 95 TSR <= '1' & TSR(8 downto 1); 96 end if; 97 -- Bclk delayed by 1 sysclk 98 bclk_dlayed <= bclk; 99 end if; 100 end process; 101 end arch; VHDL數位電路實習與專題設計 65

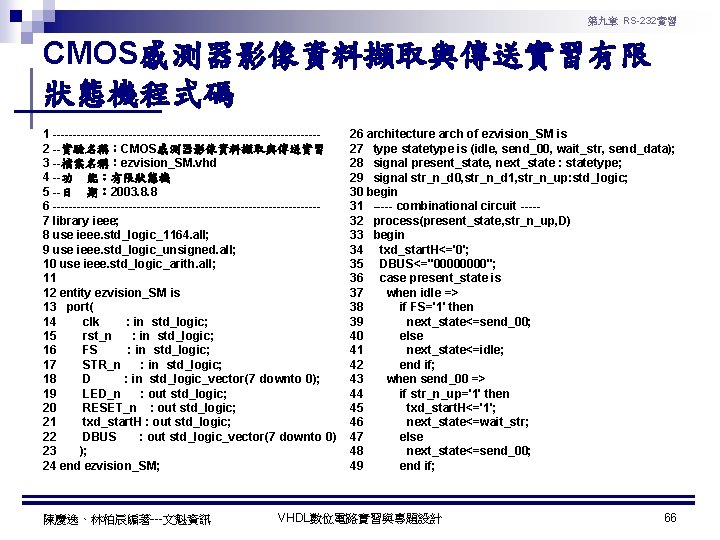

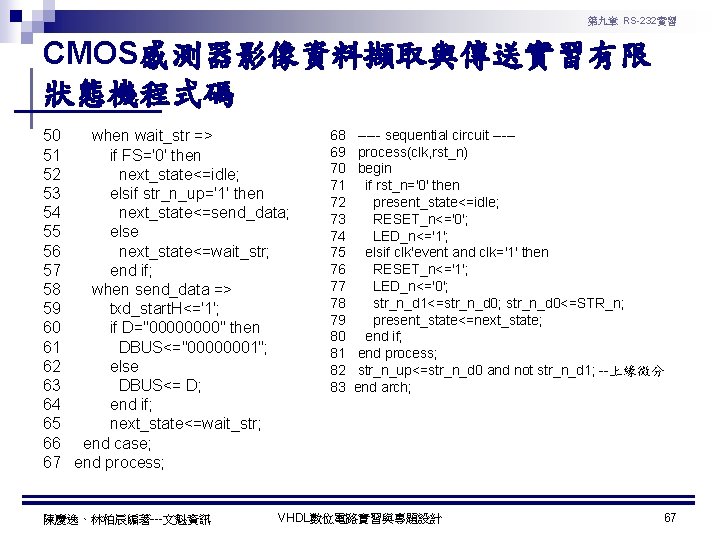

第九章 RS-232實習 CMOS感測器影像資料擷取與傳送實習有限 狀態機程式碼 1 ---------------------------------2 --實驗名稱:CMOS感測器影像資料擷取與傳送實習 3 --檔案名稱:ezvision_SM. vhd 4 --功 能:有限狀態機 5 --日 期: 2003. 8. 8 6 ---------------------------------7 library ieee; 8 use ieee. std_logic_1164. all; 9 use ieee. std_logic_unsigned. all; 10 use ieee. std_logic_arith. all; 11 12 entity ezvision_SM is 13 port( 14 clk : in std_logic; 15 rst_n : in std_logic; 16 FS : in std_logic; 17 STR_n : in std_logic; 18 D : in std_logic_vector(7 downto 0); 19 LED_n : out std_logic; 20 RESET_n : out std_logic; 21 txd_start. H : out std_logic; 22 DBUS : out std_logic_vector(7 downto 0) 23 ); 24 end ezvision_SM; 陳慶逸、林柏辰編著---文魁資訊 26 architecture arch of ezvision_SM is 27 type statetype is (idle, send_00, wait_str, send_data); 28 signal present_state, next_state : statetype; 29 signal str_n_d 0, str_n_d 1, str_n_up: std_logic; 30 begin 31 ----- combinational circuit ----32 process(present_state, str_n_up, D) 33 begin 34 txd_start. H<='0'; 35 DBUS<="0000"; 36 case present_state is 37 when idle => 38 if FS='1' then 39 next_state<=send_00; 40 else 41 next_state<=idle; 42 end if; 43 when send_00 => 44 if str_n_up='1' then 45 txd_start. H<='1'; 46 next_state<=wait_str; 47 else 48 next_state<=send_00; 49 end if; VHDL數位電路實習與專題設計 66

第九章 RS-232實習 CMOS感測器影像資料擷取與傳送實習有限 狀態機程式碼 50 when wait_str => 51 if FS='0' then 52 next_state<=idle; 53 elsif str_n_up='1' then 54 next_state<=send_data; 55 else 56 next_state<=wait_str; 57 end if; 58 when send_data => 59 txd_start. H<='1'; 60 if D="0000" then 61 DBUS<="00000001"; 62 else 63 DBUS<= D; 64 end if; 65 next_state<=wait_str; 66 end case; 67 end process; 陳慶逸、林柏辰編著---文魁資訊 68 69 70 71 72 73 74 75 76 77 78 79 80 81 82 83 ----- sequential circuit ----process(clk, rst_n) begin if rst_n='0' then present_state<=idle; RESET_n<='0'; LED_n<='1'; elsif clk'event and clk='1' then RESET_n<='1'; LED_n<='0'; str_n_d 1<=str_n_d 0; str_n_d 0<=STR_n; present_state<=next_state; end if; end process; str_n_up<=str_n_d 0 and not str_n_d 1; --上緣微分 end arch; VHDL數位電路實習與專題設計 67

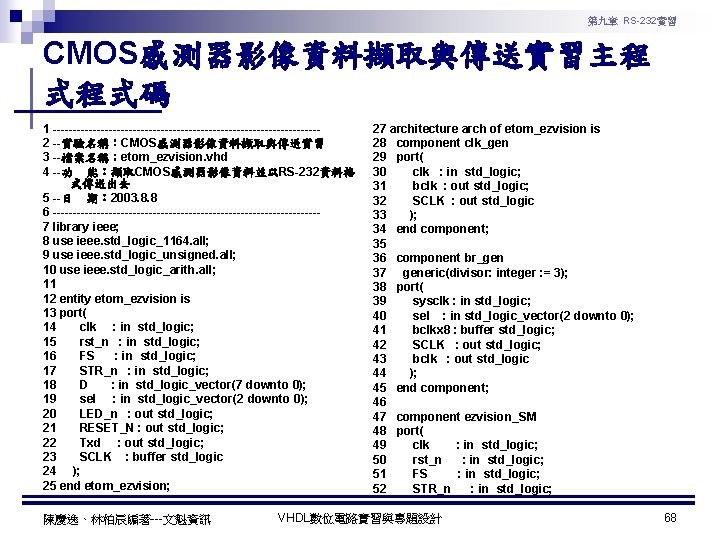

第九章 RS-232實習 CMOS感測器影像資料擷取與傳送實習主程 式程式碼 1 ---------------------------------2 --實驗名稱:CMOS感測器影像資料擷取與傳送實習 3 --檔案名稱:etom_ezvision. vhd 4 --功 能:擷取CMOS感測器影像資料並以RS-232資料格 式傳送出去 5 --日 期: 2003. 8. 8 6 ---------------------------------7 library ieee; 8 use ieee. std_logic_1164. all; 9 use ieee. std_logic_unsigned. all; 10 use ieee. std_logic_arith. all; 11 12 entity etom_ezvision is 13 port( 14 clk : in std_logic; 15 rst_n : in std_logic; 16 FS : in std_logic; 17 STR_n : in std_logic; 18 D : in std_logic_vector(7 downto 0); 19 sel : in std_logic_vector(2 downto 0); 20 LED_n : out std_logic; 21 RESET_N : out std_logic; 22 Txd : out std_logic; 23 SCLK : buffer std_logic 24 ); 25 end etom_ezvision; 陳慶逸、林柏辰編著---文魁資訊 27 architecture arch of etom_ezvision is 28 component clk_gen 29 port( 30 clk : in std_logic; 31 bclk : out std_logic; 32 SCLK : out std_logic 33 ); 34 end component; 35 36 component br_gen 37 generic(divisor: integer : = 3); 38 port( 39 sysclk : in std_logic; 40 sel : in std_logic_vector(2 downto 0); 41 bclkx 8 : buffer std_logic; 42 SCLK : out std_logic; 43 bclk : out std_logic 44 ); 45 end component; 46 47 component ezvision_SM 48 port( 49 clk : in std_logic; 50 rst_n : in std_logic; 51 FS : in std_logic; 52 STR_n : in std_logic; VHDL數位電路實習與專題設計 68

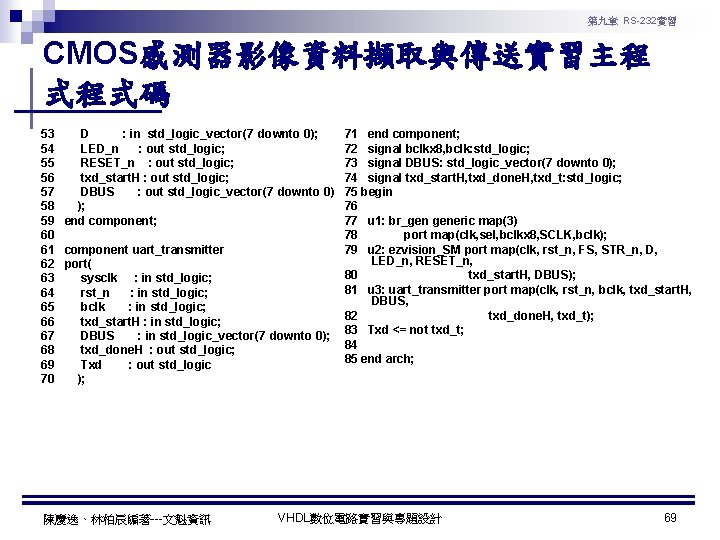

第九章 RS-232實習 CMOS感測器影像資料擷取與傳送實習主程 式程式碼 53 D : in std_logic_vector(7 downto 0); 54 LED_n : out std_logic; 55 RESET_n : out std_logic; 56 txd_start. H : out std_logic; 57 DBUS : out std_logic_vector(7 downto 0) 58 ); 59 end component; 60 61 component uart_transmitter 62 port( 63 sysclk : in std_logic; 64 rst_n : in std_logic; 65 bclk : in std_logic; 66 txd_start. H : in std_logic; 67 DBUS : in std_logic_vector(7 downto 0); 68 txd_done. H : out std_logic; 69 Txd : out std_logic 70 ); 陳慶逸、林柏辰編著---文魁資訊 71 end component; 72 signal bclkx 8, bclk: std_logic; 73 signal DBUS: std_logic_vector(7 downto 0); 74 signal txd_start. H, txd_done. H, txd_t: std_logic; 75 begin 76 77 u 1: br_gen generic map(3) 78 port map(clk, sel, bclkx 8, SCLK, bclk); 79 u 2: ezvision_SM port map(clk, rst_n, FS, STR_n, D, LED_n, RESET_n, 80 txd_start. H, DBUS); 81 u 3: uart_transmitter port map(clk, rst_n, bclk, txd_start. H, DBUS, 82 txd_done. H, txd_t); 83 Txd <= not txd_t; 84 85 end arch; VHDL數位電路實習與專題設計 69

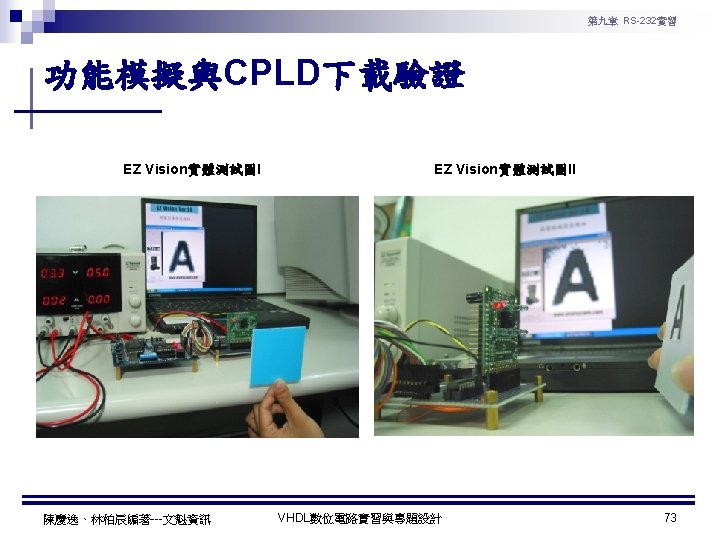

第九章 RS-232實習 功能模擬與CPLD下載驗證 腳位配置表 輸入 CLK RST_n FS STR_n D(0) D(1) D(2) D(3) D(4) D(5) D(6) D(7) Sel(0) Sel(1) Sel(2) 陳慶逸、林柏辰編著---文魁資訊 �位 43(CLK) 37(SW 1) 4(IO 8) 5(IO 9) 16(IO 0) 17(IO 1) 18(IO 2) 19(IO 3) 20(IO 4) 21(IO 5) 24(IO 6) 25(IO 7) 2(DIP 6) 44(DIP 7) 1(DIP 6) 輸出 LED_n RESET_n Txd SCLK VHDL數位電路實習與專題設計 �位 6(IO 10) 8(IO 11) 11(IO 13) 12(IO 14) 72

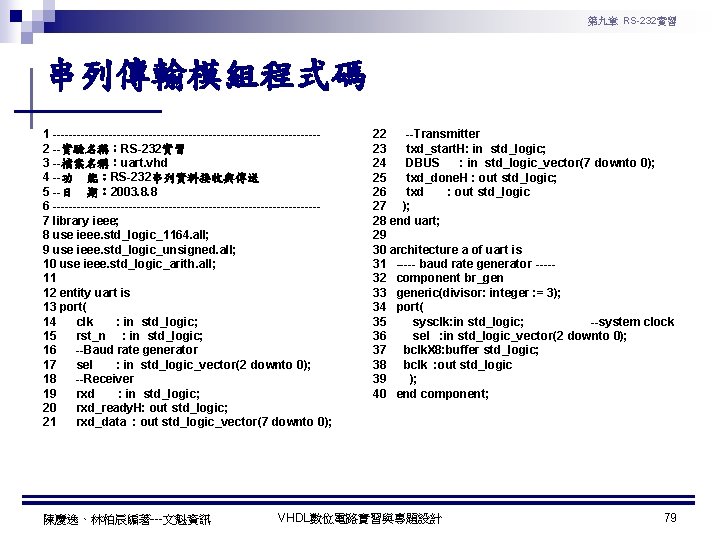

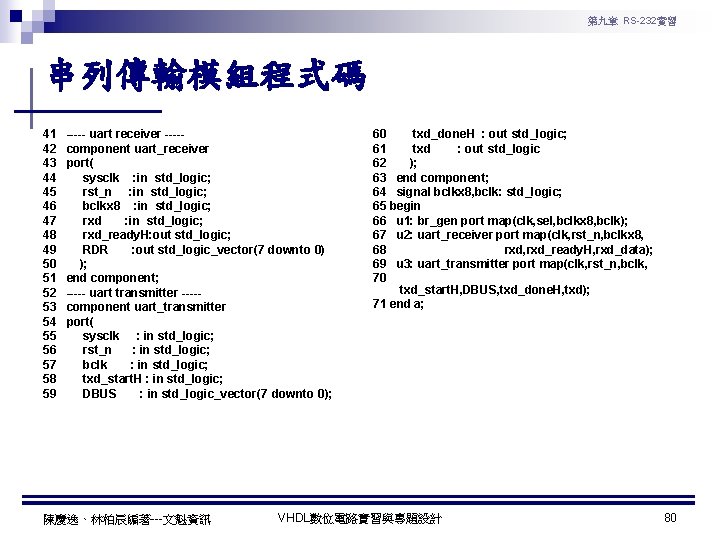

第九章 RS-232實習 串列傳輸模組程式碼 1 ---------------------------------2 --實驗名稱:RS-232實習 3 --檔案名稱:uart. vhd 4 --功 能:RS-232串列資料接收與傳送 5 --日 期: 2003. 8. 8 6 ---------------------------------7 library ieee; 8 use ieee. std_logic_1164. all; 9 use ieee. std_logic_unsigned. all; 10 use ieee. std_logic_arith. all; 11 12 entity uart is 13 port( 14 clk : in std_logic; 15 rst_n : in std_logic; 16 --Baud rate generator 17 sel : in std_logic_vector(2 downto 0); 18 --Receiver 19 rxd : in std_logic; 20 rxd_ready. H: out std_logic; 21 rxd_data : out std_logic_vector(7 downto 0); 陳慶逸、林柏辰編著---文魁資訊 22 --Transmitter 23 txd_start. H: in std_logic; 24 DBUS : in std_logic_vector(7 downto 0); 25 txd_done. H : out std_logic; 26 txd : out std_logic 27 ); 28 end uart; 29 30 architecture a of uart is 31 ----- baud rate generator ----32 component br_gen 33 generic(divisor: integer : = 3); 34 port( 35 sysclk: in std_logic; --system clock 36 sel : in std_logic_vector(2 downto 0); 37 bclk. X 8: buffer std_logic; 38 bclk : out std_logic 39 ); 40 end component; VHDL數位電路實習與專題設計 79

第九章 RS-232實習 串列傳輸模組程式碼 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 ----- uart receiver ----component uart_receiver port( sysclk : in std_logic; rst_n : in std_logic; bclkx 8 : in std_logic; rxd_ready. H: out std_logic; RDR : out std_logic_vector(7 downto 0) ); end component; ----- uart transmitter ----component uart_transmitter port( sysclk : in std_logic; rst_n : in std_logic; bclk : in std_logic; txd_start. H : in std_logic; DBUS : in std_logic_vector(7 downto 0); 陳慶逸、林柏辰編著---文魁資訊 60 txd_done. H : out std_logic; 61 txd : out std_logic 62 ); 63 end component; 64 signal bclkx 8, bclk: std_logic; 65 begin 66 u 1: br_gen port map(clk, sel, bclkx 8, bclk); 67 u 2: uart_receiver port map(clk, rst_n, bclkx 8, 68 rxd, rxd_ready. H, rxd_data); 69 u 3: uart_transmitter port map(clk, rst_n, bclk, 70 txd_start. H, DBUS, txd_done. H, txd); 71 end a; VHDL數位電路實習與專題設計 80

第九章 RS-232實習 串列傳輸腳位配置表(LP-2900) 輸入 clk rst_n sel(0) sel(1) sel(2) txd_start. H DBUS(0) DBUS(1) DBUS(2) DBUS(3) DBUS(4) DBUS(5) DBUS(6) DBUS(7) 陳慶逸、林柏辰編著---文魁資訊 �位 55 54(P 1) 67(SW 11) 65(SW 10) 64(SW 9) 124(P 3) 47(SW 1) 48(SW 2) 49(SW 3) 51(SW 4) 59(SW 5) 60(SW 6) 62(SW 7) 63(SW 8) 輸出 txd_done rxd_ready. H rxd_data(0) rxd_data(1) rxd_data(2) rxd_data(3) rxd_data(4) rxd_data(5) rxd_data(6) rxd_data(7) VHDL數位電路實習與專題設計 �位 19(L 11) 20(L 12) 7(L 1) 8(L 2) 9(L 3) 10(L 4) 11(L 5) 12(L 6) 13(L 7) 14(L 8) 83

- Slides: 85