RLL Relay Ladder Logic CONTENTS 1 PLC operation

![Ladder logic: basic notations n Simple “always on” load: [Always_On = 1] note: sometimes Ladder logic: basic notations n Simple “always on” load: [Always_On = 1] note: sometimes](https://slidetodoc.com/presentation_image_h2/4fdd577a7378b3ef4f493126975f8af5/image-9.jpg)

- Slides: 20

RLL: Relay Ladder Logic CONTENTS 1. PLC operation 2. PLC programming 3. Ladder logic 4. Memory and gates 1

PLC operation A PLC has 2 modes of operation Programming mode: translate engineering language (control logic) to machine language (binary code) Running (or scanning) mode: Relating the program to inputs and outputs 2

Programming through standard computer n Most PLC manufacturers offer software packages that allow a standard computer to be used as a programming terminal 3

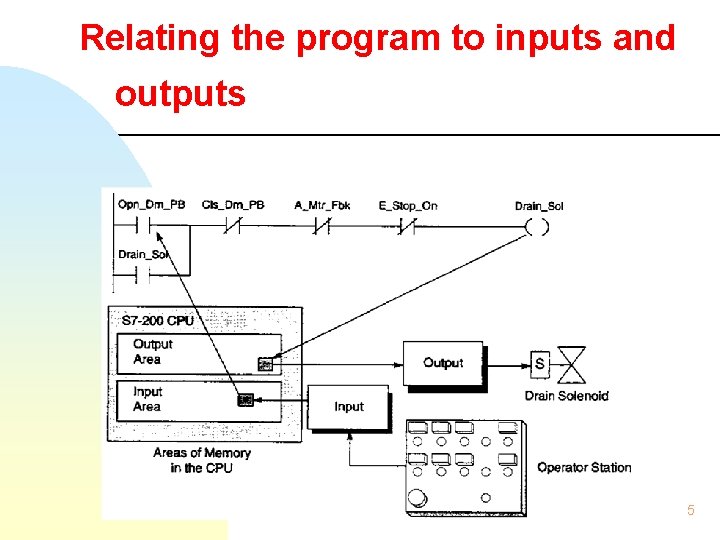

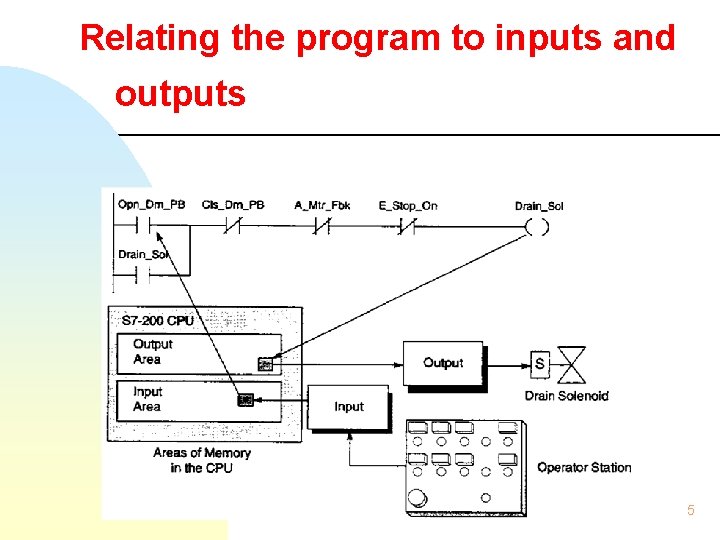

PLC running or scanning mode Relating the program to inputs and outputs n The CPU reads the data from the inputs n The program in the CPU uses the inputs to evaluate the control logic. As the program runs, the CPU updates the data n The CPU writes the data to the output 4

Relating the program to inputs and outputs 5

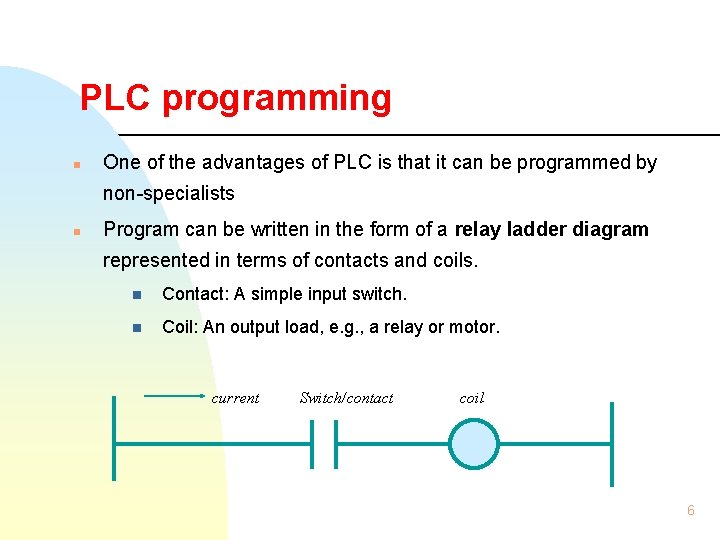

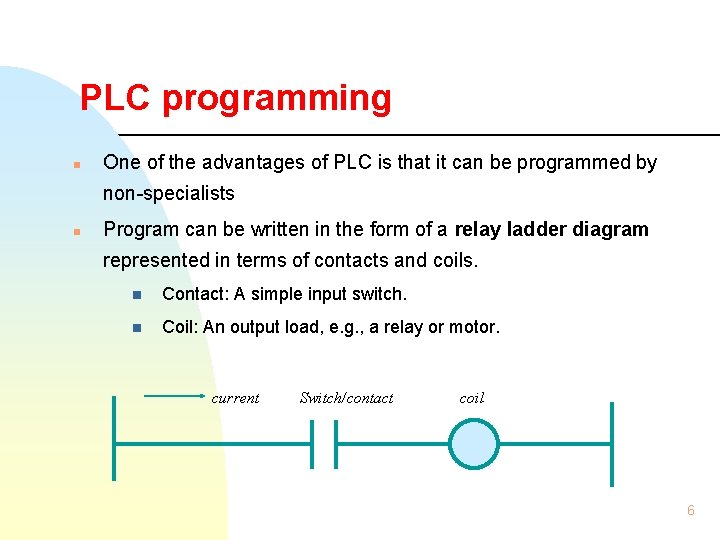

PLC programming n One of the advantages of PLC is that it can be programmed by non-specialists n Program can be written in the form of a relay ladder diagram represented in terms of contacts and coils. n Contact: A simple input switch. n Coil: An output load, e. g. , a relay or motor. current Switch/contact coil 6

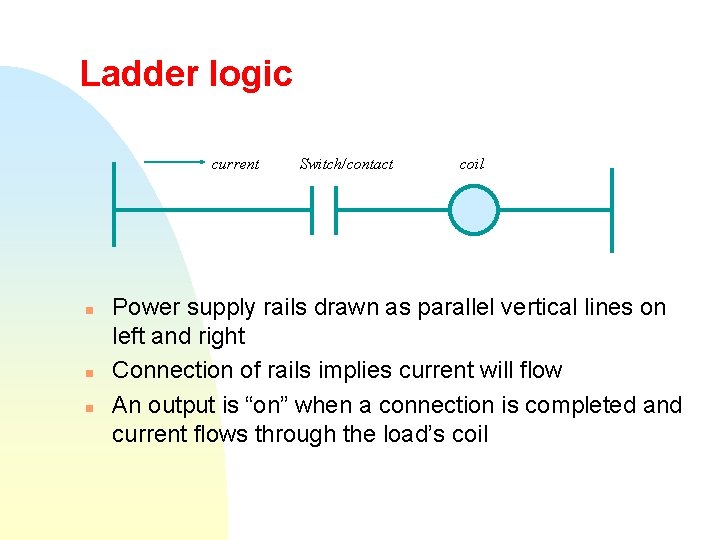

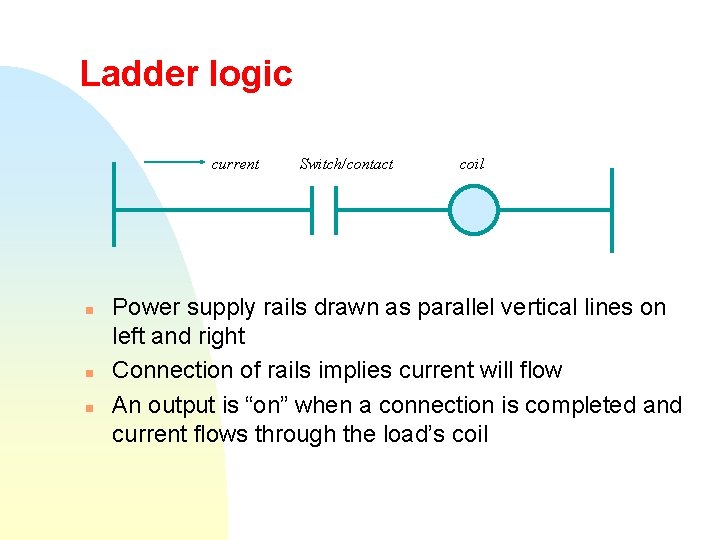

Ladder logic current n n n Switch/contact coil Power supply rails drawn as parallel vertical lines on left and right Connection of rails implies current will flow An output is “on” when a connection is completed and current flows through the load’s coil

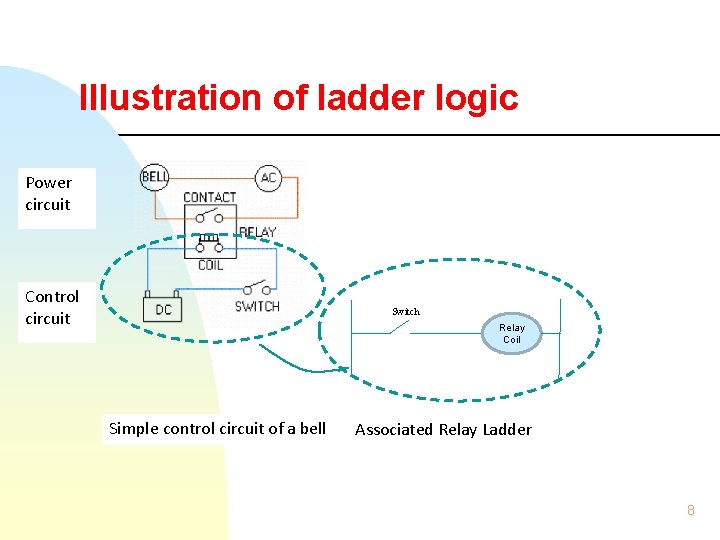

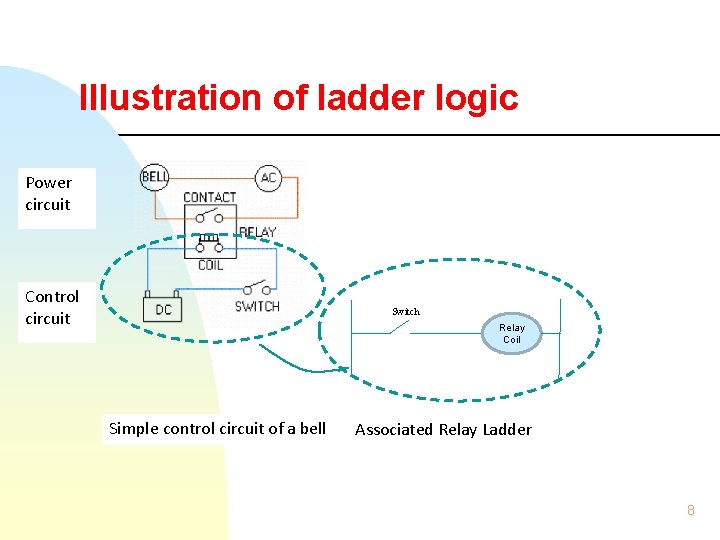

Illustration of ladder logic Power circuit Control circuit Switch Relay Coil Simple control circuit of a bell Associated Relay Ladder 8

![Ladder logic basic notations n Simple always on load AlwaysOn 1 note sometimes Ladder logic: basic notations n Simple “always on” load: [Always_On = 1] note: sometimes](https://slidetodoc.com/presentation_image_h2/4fdd577a7378b3ef4f493126975f8af5/image-9.jpg)

Ladder logic: basic notations n Simple “always on” load: [Always_On = 1] note: sometimes illegal n Load controlled by a single contact: [Switch_Con = Switch]

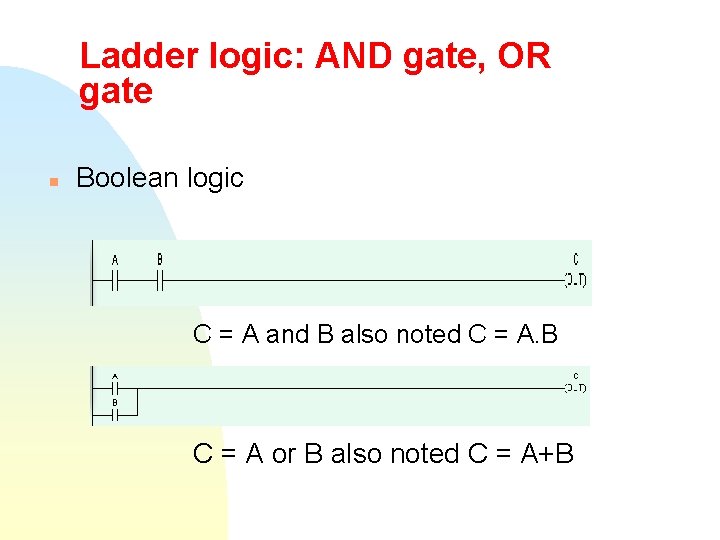

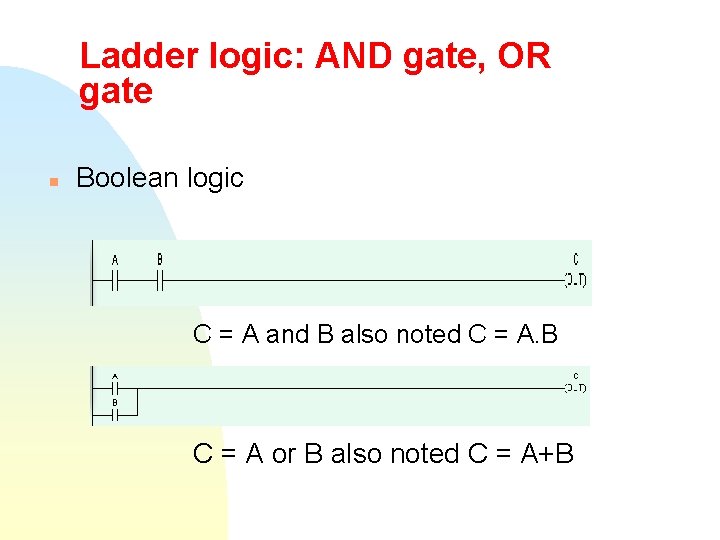

Ladder logic: AND gate, OR gate n Boolean logic C = A and B also noted C = A. B C = A or B also noted C = A+B

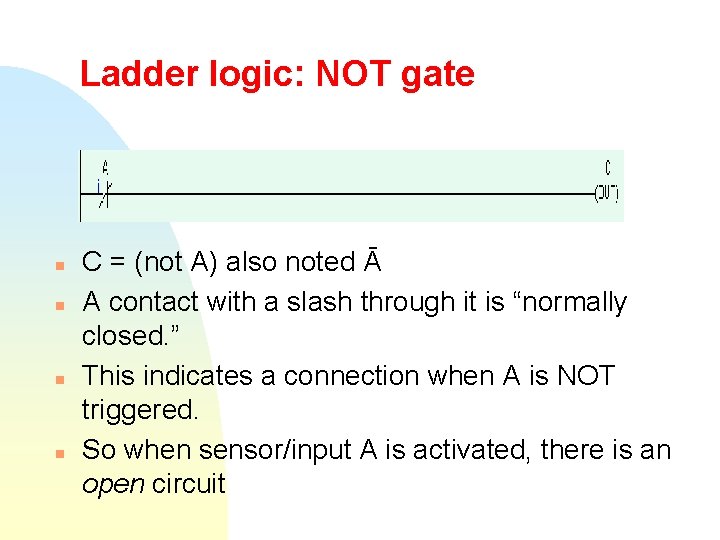

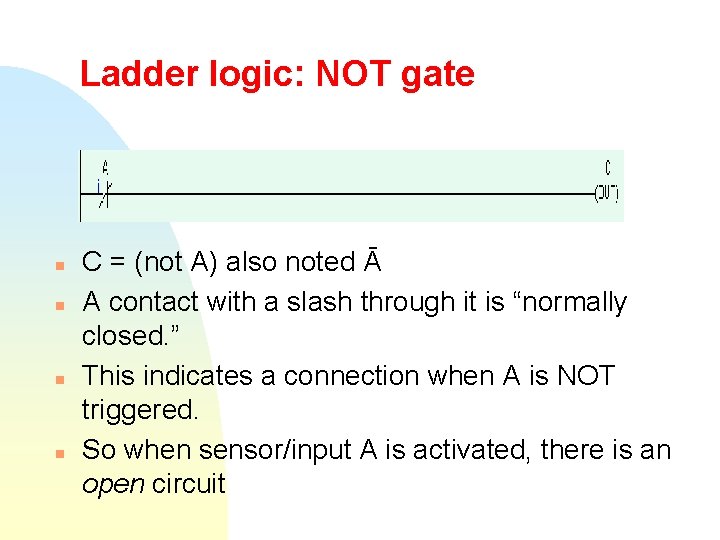

Ladder logic: NOT gate n n C = (not A) also noted Ā A contact with a slash through it is “normally closed. ” This indicates a connection when A is NOT triggered. So when sensor/input A is activated, there is an open circuit

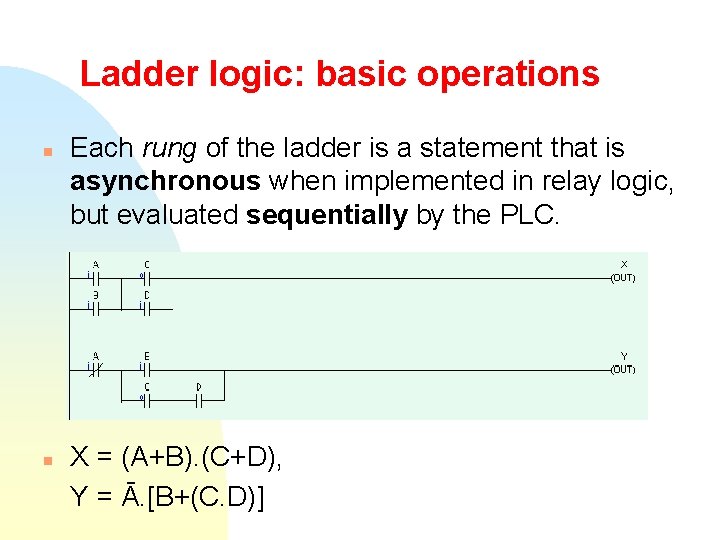

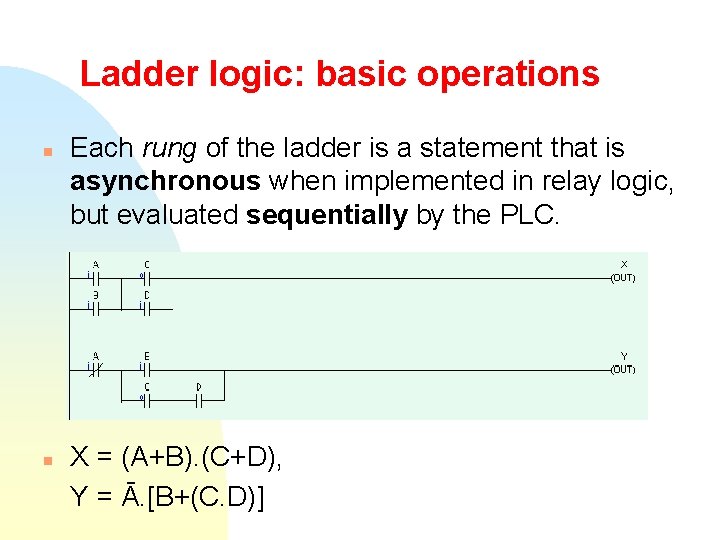

Ladder logic: basic operations n n Each rung of the ladder is a statement that is asynchronous when implemented in relay logic, but evaluated sequentially by the PLC. X = (A+B). (C+D), Y = Ā. [B+(C. D)]

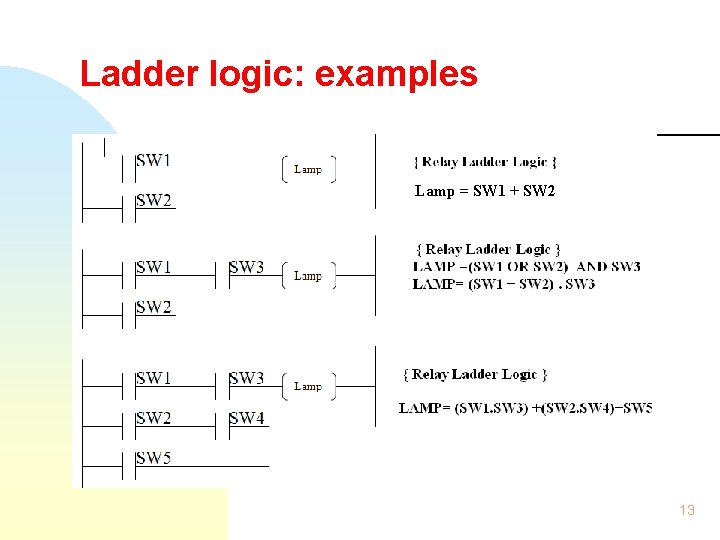

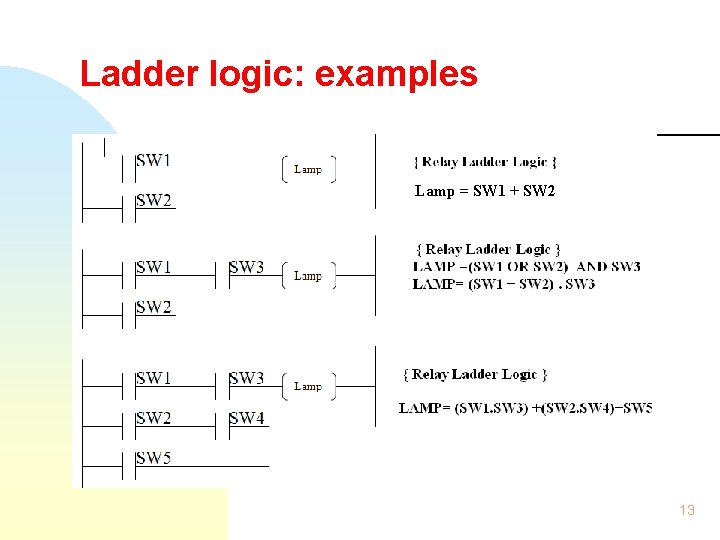

Ladder logic: examples Lamp = SW 1 + SW 2 13

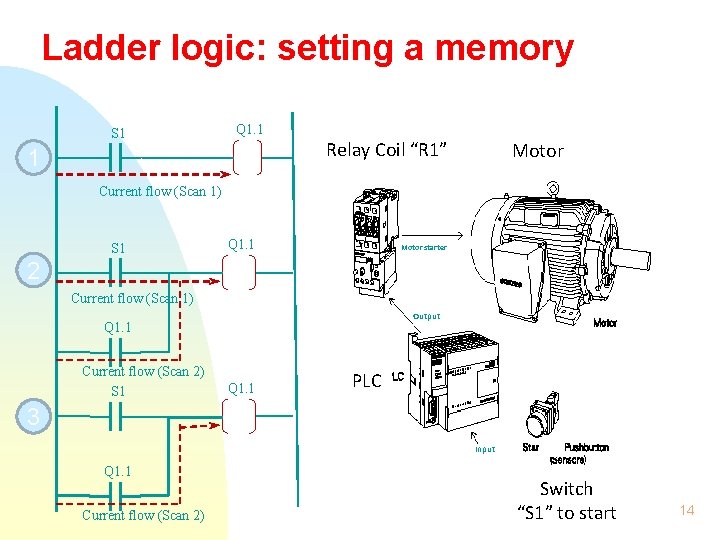

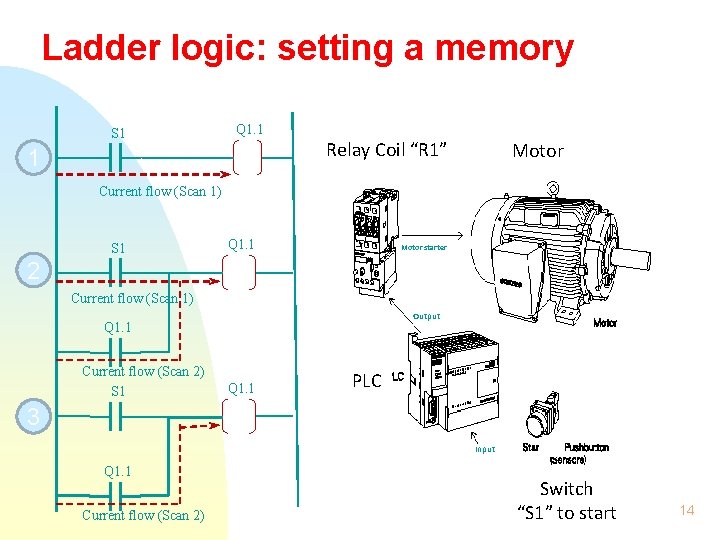

Ladder logic: setting a memory S 1 Q 1. 1 1 Relay Coil “R 1” Motor Current flow (Scan 1) S 1 Q 1. 1 Motor starter 2 Current flow (Scan 1) Output Q 1. 1 Current flow (Scan 2) S 1 Q 1. 1 PLC 3 Input Q 1. 1 Current flow (Scan 2) Switch “S 1” to start 14

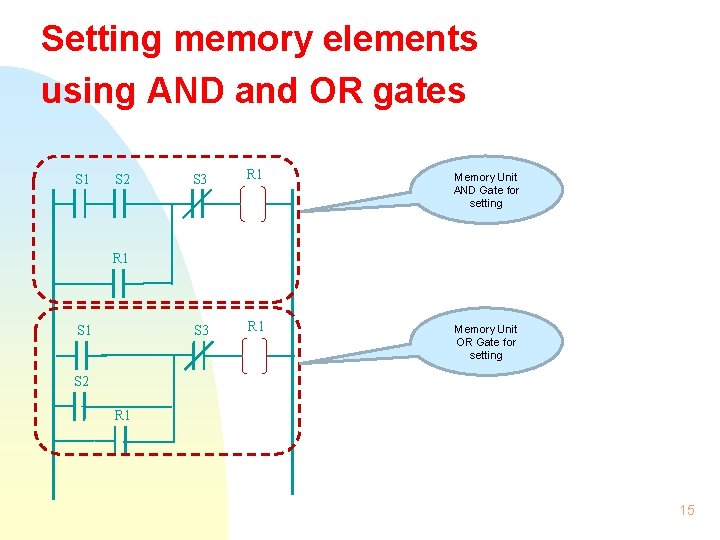

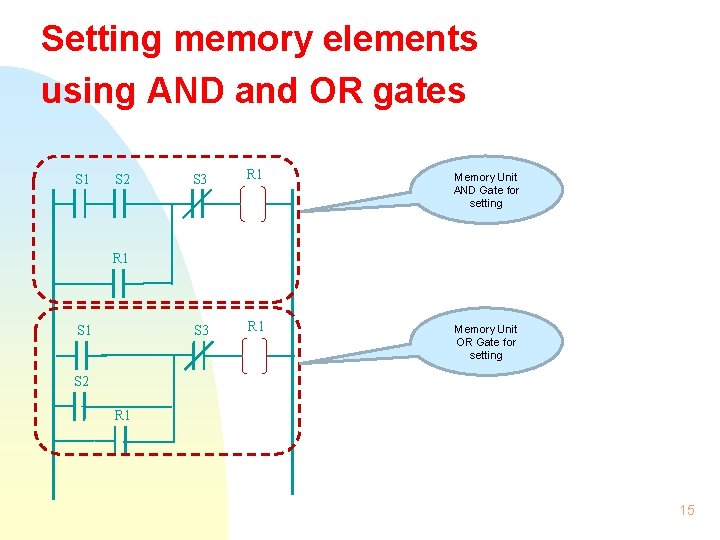

Setting memory elements using AND and OR gates S 1 S 2 S 3 R 1 Memory Unit AND Gate for setting S 3 R 1 Memory Unit OR Gate for setting R 1 S 2 R 1 15

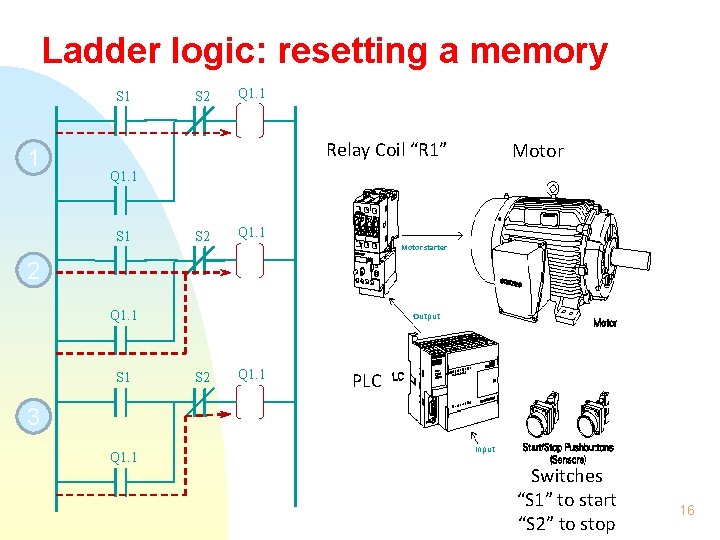

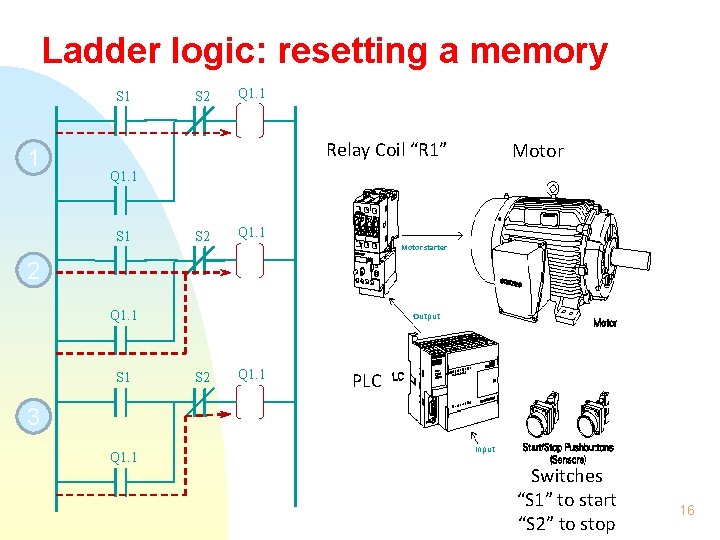

Ladder logic: resetting a memory S 1 1 S 2 Q 1. 1 Relay Coil “R 1” Motor Q 1. 1 S 2 Q 1. 1 Motor starter 2 Q 1. 1 S 1 Output S 2 Q 1. 1 PLC 3 Q 1. 1 Input Switches “S 1” to start “S 2” to stop 16

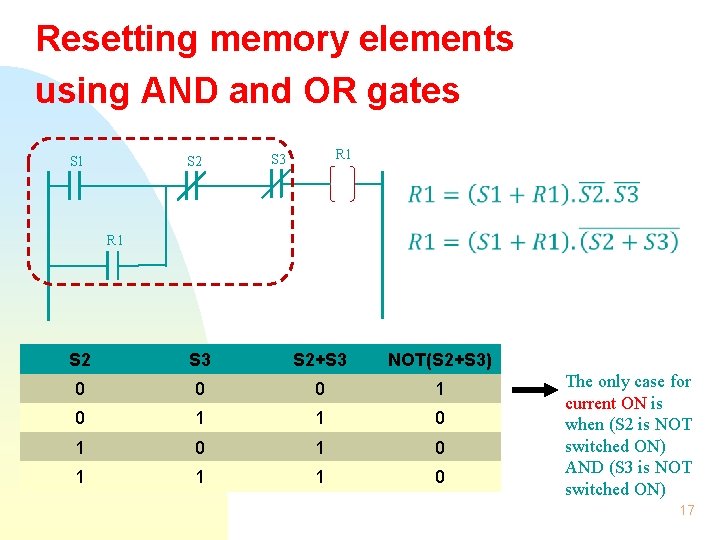

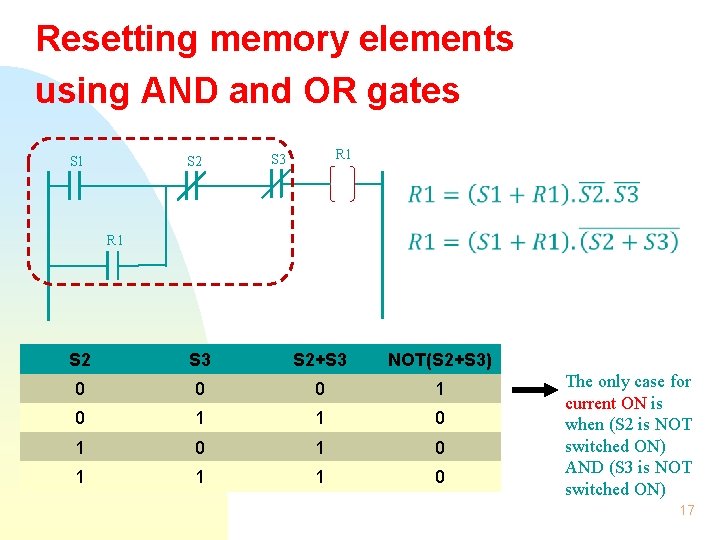

Resetting memory elements using AND and OR gates S 2 S 1 R 1 S 3 R 1 S 2 S 3 S 2+S 3 NOT(S 2+S 3) 0 0 0 1 1 0 1 0 1 1 1 0 The only case for current ON is when (S 2 is NOT switched ON) AND (S 3 is NOT switched ON) 17

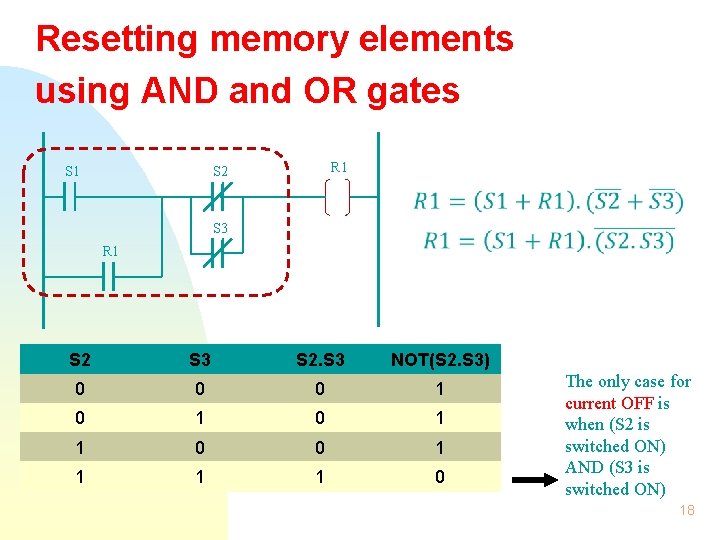

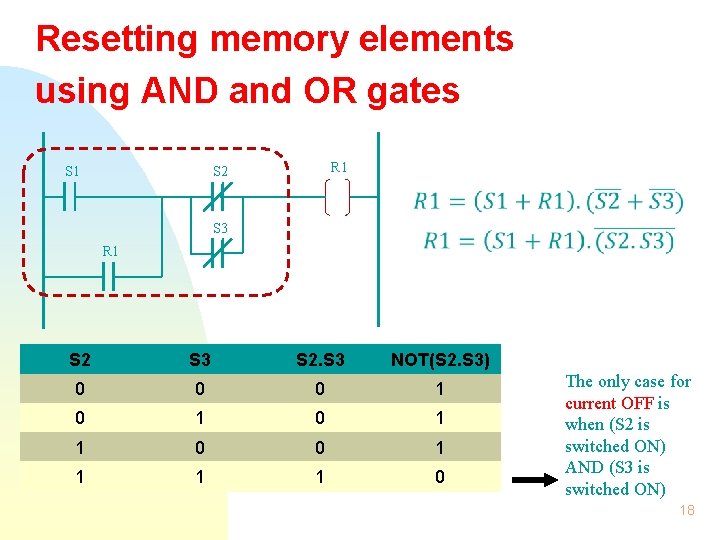

Resetting memory elements using AND and OR gates R 1 S 2 S 1 S 3 R 1 S 2 S 3 S 2. S 3 NOT(S 2. S 3) 0 0 0 1 0 1 1 0 The only case for current OFF is when (S 2 is switched ON) AND (S 3 is switched ON) 18

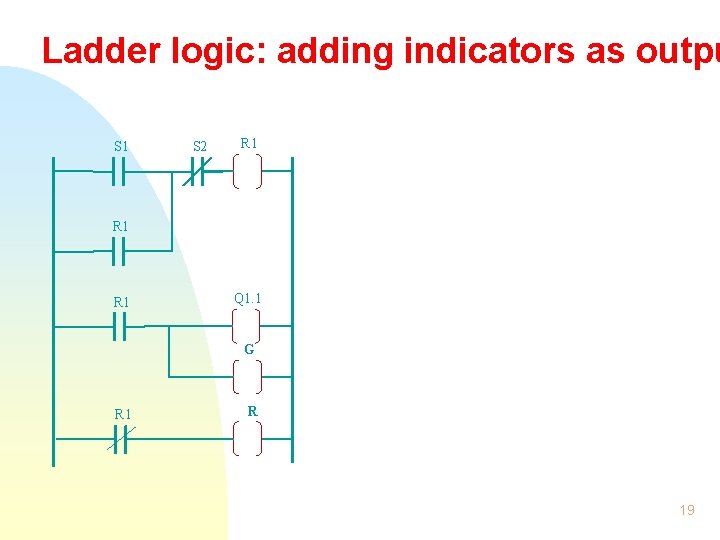

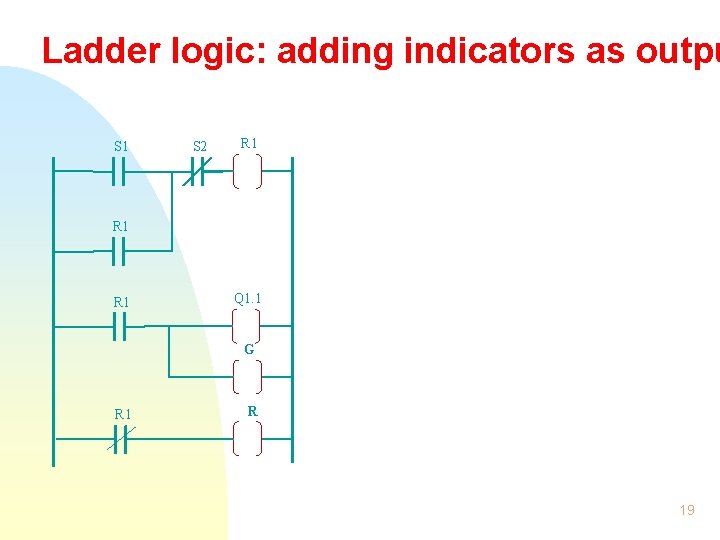

Ladder logic: adding indicators as outpu S 1 S 2 R 1 R 1 Q 1. 1 G R 19

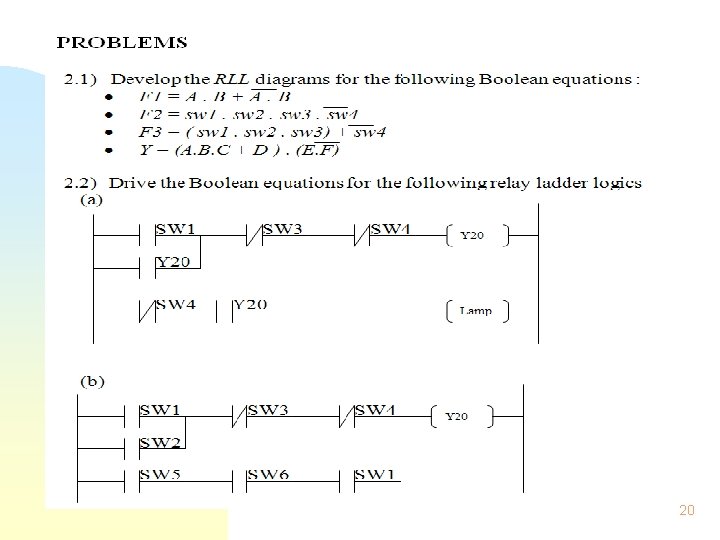

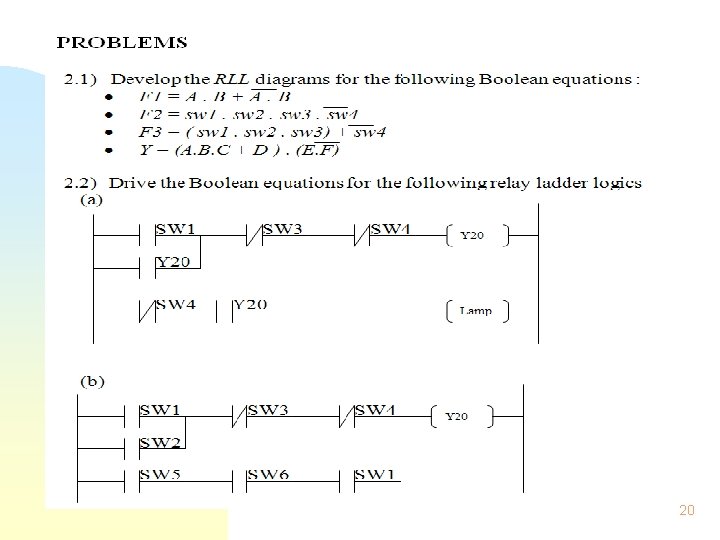

20