Reprogrammable Prototyping for Actel RTAX and RTSX space

Re-programmable Prototyping for Actel™ RTAX and RTSX space -flight systems designs MAPLD 2009 Presentation Poster Session

Today’s Prototyping Solution Socket + AX/SX-A Approach Good solution, but several design iterations could require several of the OTP (One Time Programmable) or Actel AX/SX-A commercial chips to complete the design. Weak Point The potential risk for using several of these OTP or AX/SX-A devices could add to the overall project cost and impact the budget. MAPLD 2009 – Poster Session 2

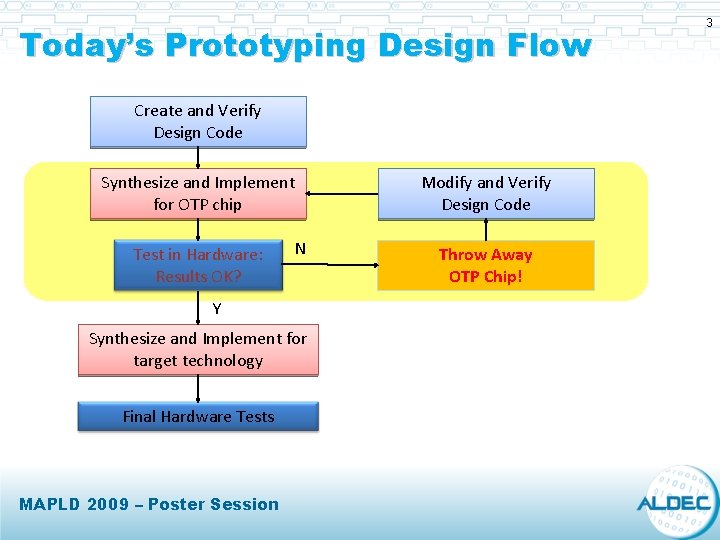

Today’s Prototyping Design Flow Create and Verify Design Code Synthesize and Implement for OTP chip Test in Hardware: Results OK? N Y Synthesize and Implement for target technology Final Hardware Tests MAPLD 2009 – Poster Session Modify and Verify Design Code Throw Away OTP Chip! 3

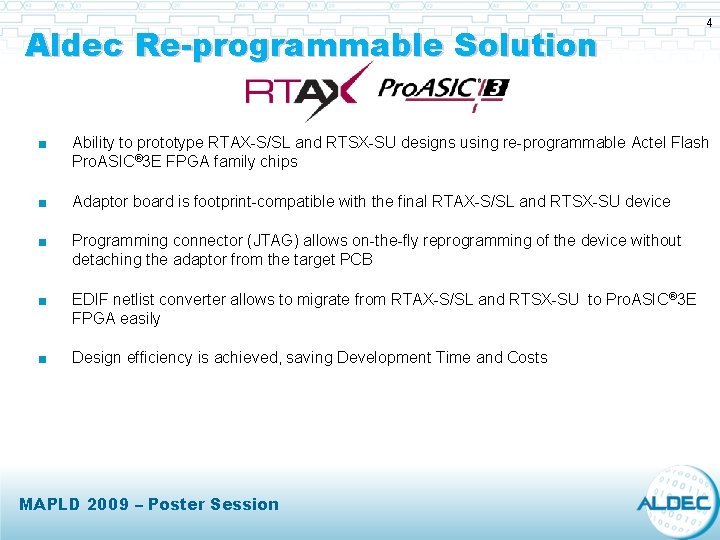

Aldec Re-programmable Solution 4 < Ability to prototype RTAX-S/SL and RTSX-SU designs using re-programmable Actel Flash Pro. ASIC® 3 E FPGA family chips < Adaptor board is footprint-compatible with the final RTAX-S/SL and RTSX-SU device < Programming connector (JTAG) allows on-the-fly reprogramming of the device without detaching the adaptor from the target PCB < EDIF netlist converter allows to migrate from RTAX-S/SL and RTSX-SU to Pro. ASIC ® 3 E FPGA easily < Design efficiency is achieved, saving Development Time and Costs MAPLD 2009 – Poster Session

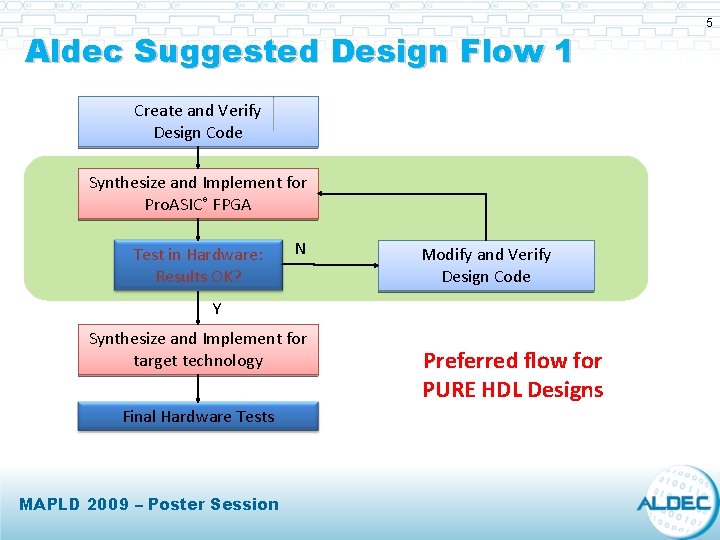

Aldec Suggested Design Flow 1 Create and Verify Design Code Synthesize and Implement for Pro. ASIC® FPGA Test in Hardware: Results OK? N Modify and Verify Design Code Y Synthesize and Implement for target technology Final Hardware Tests MAPLD 2009 – Poster Session Preferred flow for PURE HDL Designs 5

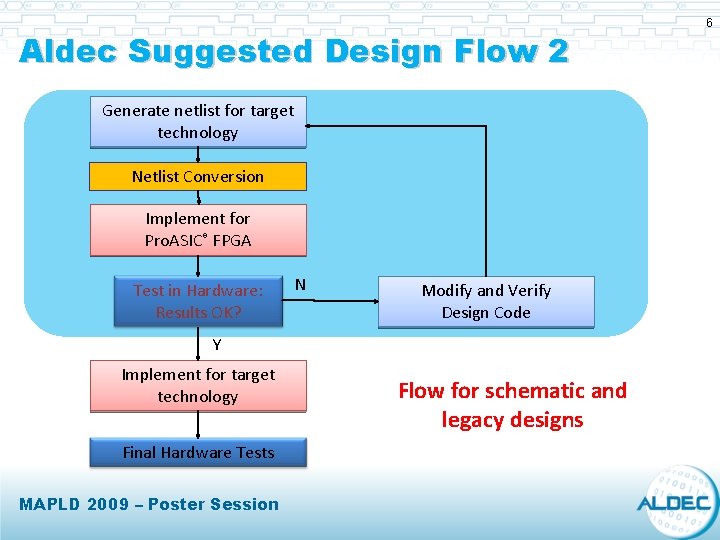

Aldec Suggested Design Flow 2 Generate netlist for target technology Netlist Conversion Implement for Pro. ASIC® FPGA Test in Hardware: Results OK? N Modify and Verify Design Code Y Implement for target technology Final Hardware Tests MAPLD 2009 – Poster Session Flow for schematic and legacy designs 6

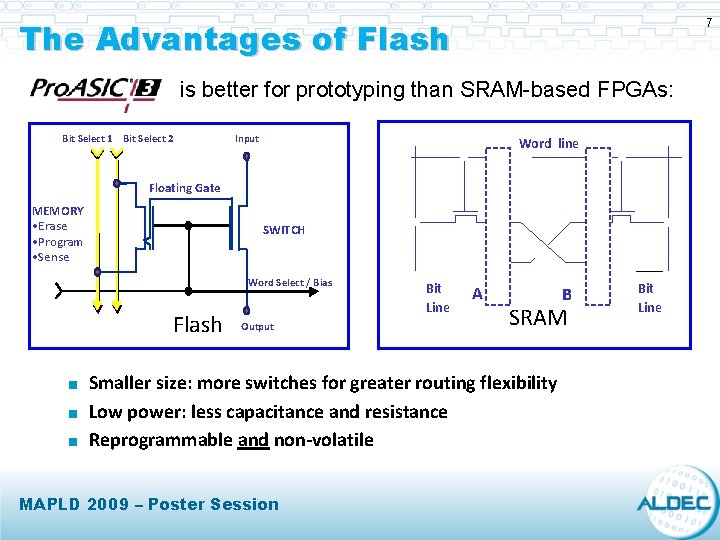

The Advantages of Flash 7 is better for prototyping than SRAM-based FPGAs: Bit Select 1 Bit Select 2 Input Word line VCC Floating Gate MEMORY • Erase • Program • Sense SWITCH Word Select / Bias Flash < < < Output Bit Line A SRAM Smaller size: more switches for greater routing flexibility Low power: less capacitance and resistance Reprogrammable and non-volatile MAPLD 2009 – Poster Session B Bit Line

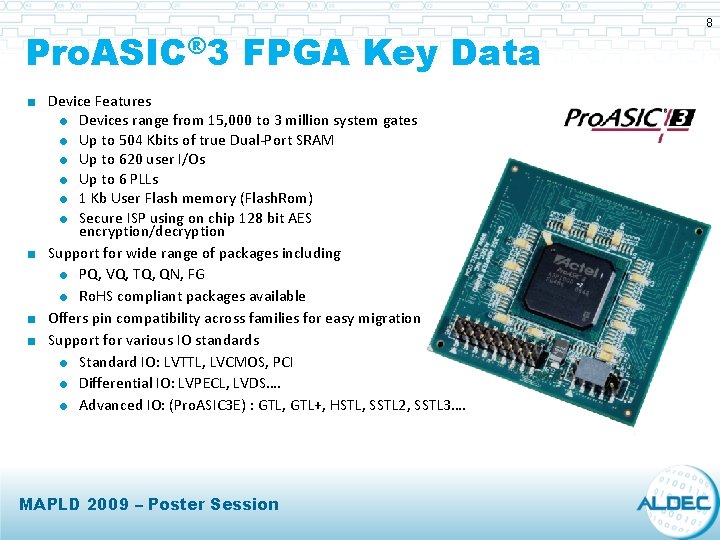

Pro. ASIC® 3 FPGA Key Data < < Device Features Devices range from 15, 000 to 3 million system gates Up to 504 Kbits of true Dual-Port SRAM Up to 620 user I/Os Up to 6 PLLs 1 Kb User Flash memory (Flash. Rom) Secure ISP using on chip 128 bit AES encryption/decryption Support for wide range of packages including PQ, VQ, TQ, QN, FG Ro. HS compliant packages available Offers pin compatibility across families for easy migration Support for various IO standards Standard IO: LVTTL, LVCMOS, PCI Differential IO: LVPECL, LVDS…. Advanced IO: (Pro. ASIC 3 E) : GTL, GTL+, HSTL, SSTL 2, SSTL 3…. MAPLD 2009 – Poster Session 8

9 Prototyping Adaptors and Converter • ALDEC Prototyping Solution consists of two parts: s Selection of Prototyping Adaptors s (designers picks adaptor according to the desired package of RTAX/RTSX chip and design size) EDIF Netlist Converter (allows conversion of RTAS/RTSX netlist to Pro. ASIC 3 format, skipping synthesis stage and proceeding directly to implementation) • Converter use is optional, but allows faster workflow in many design cases MAPLD 2009 – Poster Session

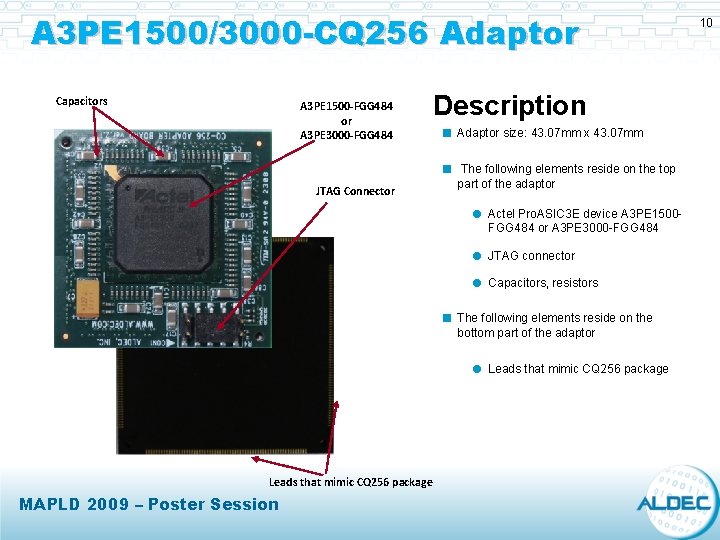

A 3 PE 1500/3000 -CQ 256 Adaptor Capacitors A 3 PE 1500 -FGG 484 or A 3 PE 3000 -FGG 484 Description < Adaptor size: 43. 07 mm x 43. 07 mm < The following elements reside on the top JTAG Connector part of the adaptor Actel Pro. ASIC 3 E device A 3 PE 1500 FGG 484 or A 3 PE 3000 -FGG 484 JTAG connector Capacitors, resistors < The following elements reside on the bottom part of the adaptor Leads that mimic CQ 256 package MAPLD 2009 – Poster Session 10

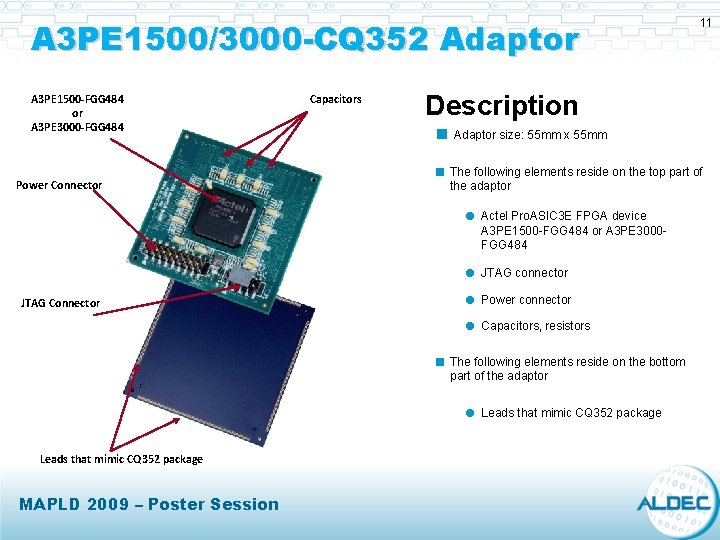

A 3 PE 1500/3000 -CQ 352 Adaptor A 3 PE 1500 -FGG 484 or A 3 PE 3000 -FGG 484 Power Connector Capacitors Description < Adaptor size: 55 mm x 55 mm < The following elements reside on the top part of the adaptor Actel Pro. ASIC 3 E FPGA device A 3 PE 1500 -FGG 484 or A 3 PE 3000 FGG 484 JTAG connector JTAG Connector Power connector Capacitors, resistors < The following elements reside on the bottom part of the adaptor Leads that mimic CQ 352 package MAPLD 2009 – Poster Session 11

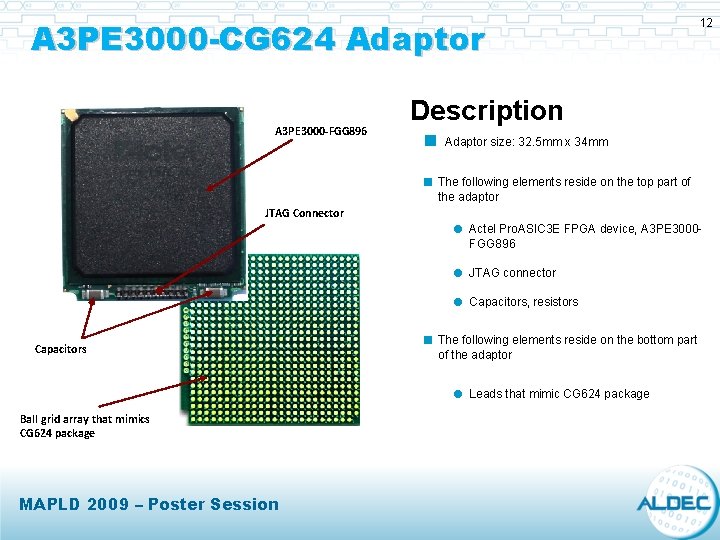

A 3 PE 3000 -CG 624 Adaptor A 3 PE 3000 -FGG 896 12 Description < Adaptor size: 32. 5 mm x 34 mm < The following elements reside on the top part of the adaptor JTAG Connector Actel Pro. ASIC 3 E FPGA device, A 3 PE 3000 FGG 896 JTAG connector Capacitors, resistors Capacitors < The following elements reside on the bottom part of the adaptor Leads that mimic CG 624 package Ball grid array that mimics CG 624 package MAPLD 2009 – Poster Session

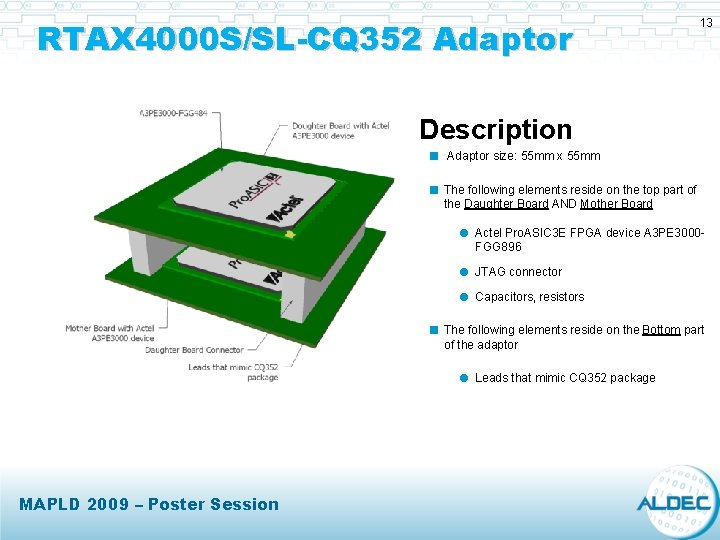

RTAX 4000 S/SL-CQ 352 Adaptor 13 Description < Adaptor size: 55 mm x 55 mm < The following elements reside on the top part of the Daughter Board AND Mother Board Actel Pro. ASIC 3 E FPGA device A 3 PE 3000 FGG 896 JTAG connector Capacitors, resistors < The following elements reside on the Bottom part of the adaptor Leads that mimic CQ 352 package MAPLD 2009 – Poster Session

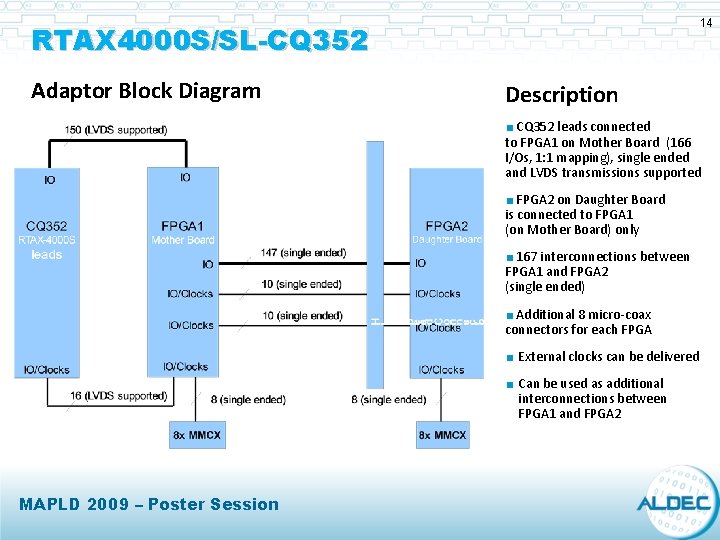

14 RTAX 4000 S/SL-CQ 352 Adaptor Block Diagram Description <CQ 352 leads connected to FPGA 1 on Mother Board (166 I/Os, 1: 1 mapping), single ended and LVDS transmissions supported <FPGA 2 on Daughter Board is connected to FPGA 1 (on Mother Board) only <167 interconnections between FPGA 1 and FPGA 2 (single ended) <Additional 8 micro-coax connectors for each FPGA < External clocks can be delivered < Can be used as additional interconnections between FPGA 1 and FPGA 2 MAPLD 2009 – Poster Session

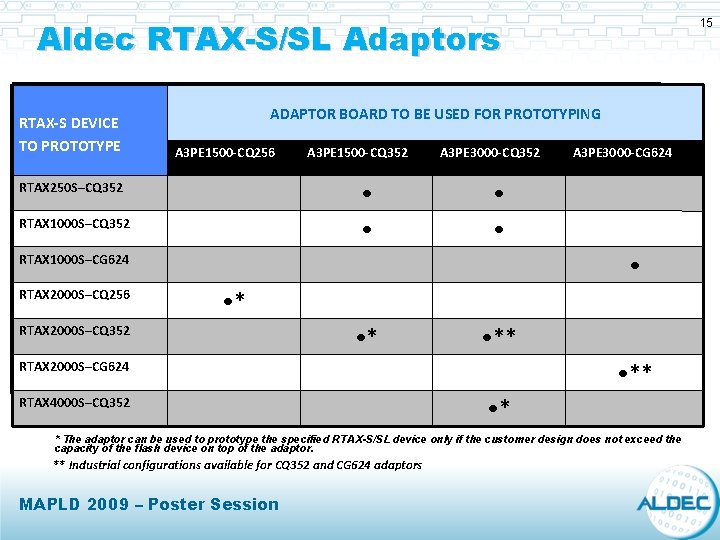

Aldec RTAX-S/SL Adaptors RTAX-S DEVICE TO PROTOTYPE ADAPTOR BOARD TO BE USED FOR PROTOTYPING A 3 PE 1500 -CQ 256 A 3 PE 1500 -CQ 352 • • RTAX 250 S–CQ 352 RTAX 1000 S–CQ 352 A 3 PE 3000 -CG 624 • • • RTAX 1000 S–CG 624 RTAX 2000 S–CQ 256 15 • * RTAX 2000 S–CQ 352 • ** RTAX 2000 S–CG 624 RTAX 4000 S–CQ 352 • * * The adaptor can be used to prototype the specified RTAX-S/SL device only if the customer design does not exceed the capacity of the flash device on top of the adaptor. ** Industrial configurations available for CQ 352 and CG 624 adaptors MAPLD 2009 – Poster Session

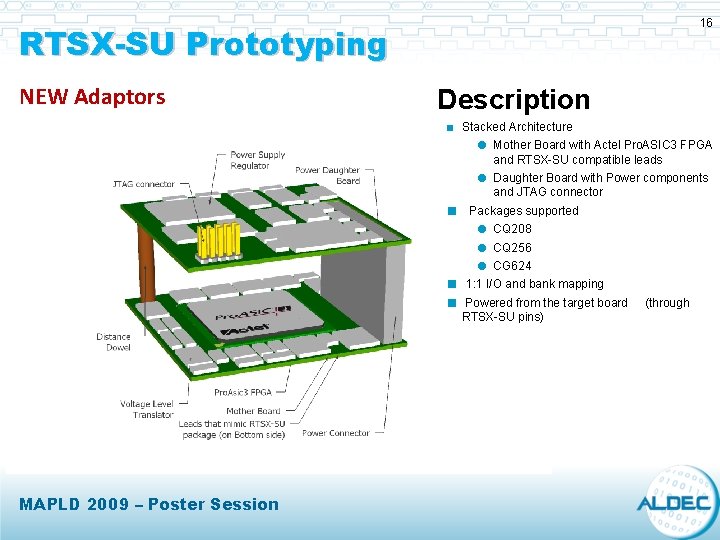

16 RTSX-SU Prototyping NEW Adaptors Description < Stacked Architecture Mother Board with Actel Pro. ASIC 3 FPGA and RTSX-SU compatible leads Daughter Board with Power components and JTAG connector < Packages supported CQ 208 CQ 256 CG 624 < 1: 1 I/O and bank mapping < Powered from the target board RTSX-SU pins) MAPLD 2009 – Poster Session (through

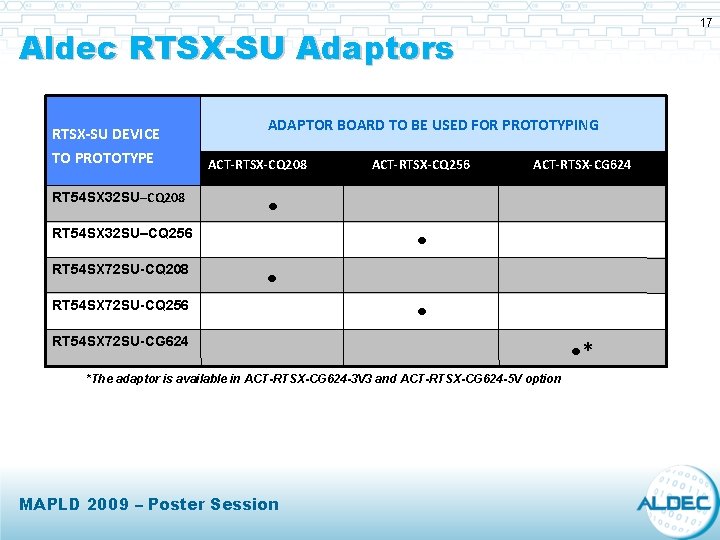

17 Aldec RTSX-SU Adaptors RTSX-SU DEVICE TO PROTOTYPE RT 54 SX 32 SU–CQ 208 ADAPTOR BOARD TO BE USED FOR PROTOTYPING ACT-RTSX-CQ 208 ACT-RTSX-CG 624 • • RT 54 SX 32 SU–CQ 256 RT 54 SX 72 SU-CQ 208 ACT-RTSX-CQ 256 • RT 54 SX 72 SU-CG 624 *The adaptor is available in ACT-RTSX-CG 624 -3 V 3 and ACT-RTSX-CG 624 -5 V option MAPLD 2009 – Poster Session • *

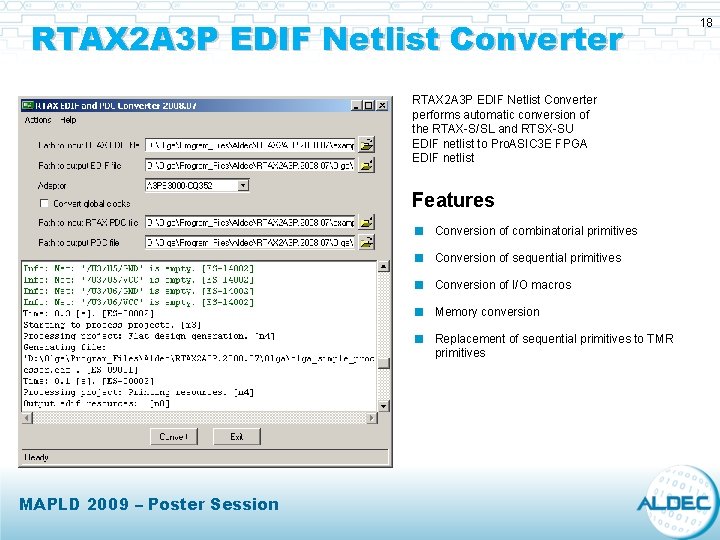

RTAX 2 A 3 P EDIF Netlist Converter performs automatic conversion of the RTAX-S/SL and RTSX-SU EDIF netlist to Pro. ASIC 3 E FPGA EDIF netlist Features < Conversion of combinatorial primitives < Conversion of sequential primitives < Conversion of I/O macros < Memory conversion < Replacement of sequential primitives to TMR primitives MAPLD 2009 – Poster Session 18

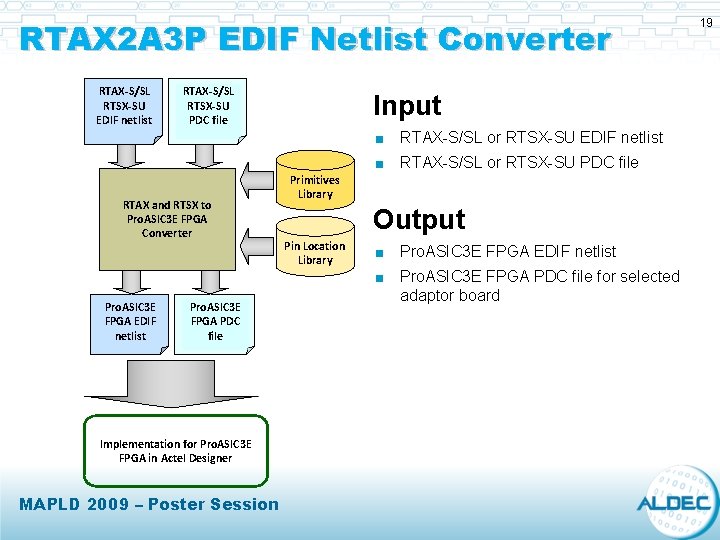

RTAX 2 A 3 P EDIF Netlist Converter RTAX-S/SL RTSX-SU EDIF netlist RTAX-S/SL RTSX-SU PDC file RTAX and RTSX to Pro. ASIC 3 E FPGA Converter Pro. ASIC 3 E FPGA EDIF netlist Pro. ASIC 3 E FPGA PDC file Implementation for Pro. ASIC 3 E FPGA in Actel Designer MAPLD 2009 – Poster Session Input < RTAX-S/SL or RTSX-SU EDIF netlist < RTAX-S/SL or RTSX-SU PDC file Primitives Library Output Pin Location Library < Pro. ASIC 3 E FPGA EDIF netlist < Pro. ASIC 3 E FPGA PDC file for selected adaptor board 19

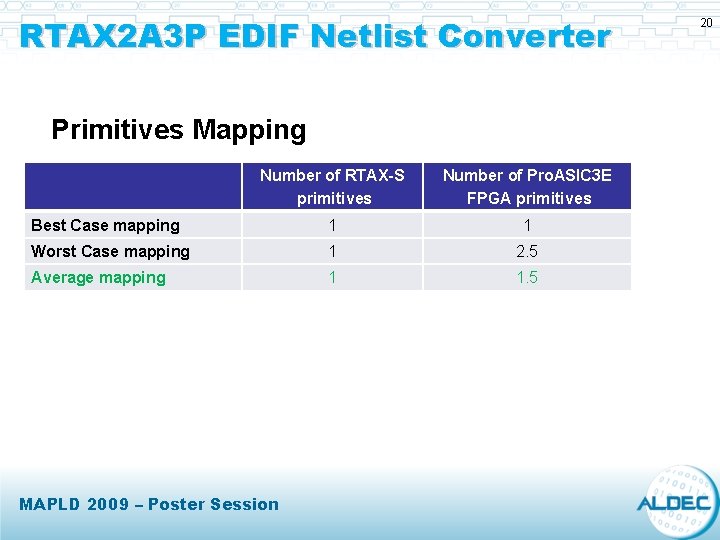

RTAX 2 A 3 P EDIF Netlist Converter Primitives Mapping Number of RTAX-S primitives Number of Pro. ASIC 3 E FPGA primitives Best Case mapping 1 1 Worst Case mapping 1 2. 5 Average mapping 1 1. 5 MAPLD 2009 – Poster Session 20

Summary < < < < Reduce chip costs Save Development Time – “Re-Programmability” Pro. ASIC® 3 FPGA “flash-based” technology Wide Device & Package Support: CQ 208, CQ 256, CQ 352 & CG 624 packages Footprint compatible adaptors Automatic translation of netlist, memories and constraints Customer proven with over 100 units shipped worldwide MAPLD 2009 – Poster Session 21

- Slides: 21