REDUCING REFRESH POWER IN MOBILE DEVICES WITH MORPHABLE

REDUCING REFRESH POWER IN MOBILE DEVICES WITH MORPHABLE ECC DSN-45 06/24/2015 Rio de Janeiro, Brazil Chiachen Chou, Georgia Tech Prashant Nair, Georgia Tech Moinuddin K. Qureshi, Georgia Tech Computer Architecture and Emerging Technologies Lab, Georgia Tech

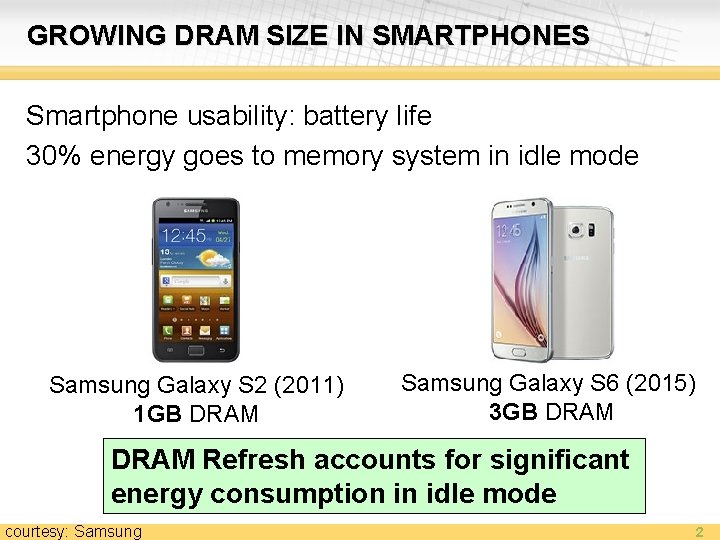

GROWING DRAM SIZE IN SMARTPHONES Smartphone usability: battery life 30% energy goes to memory system in idle mode Samsung Galaxy S 2 (2011) 1 GB DRAM Samsung Galaxy S 6 (2015) 3 GB DRAM Refresh accounts for significant energy consumption in idle mode courtesy: Samsung 2

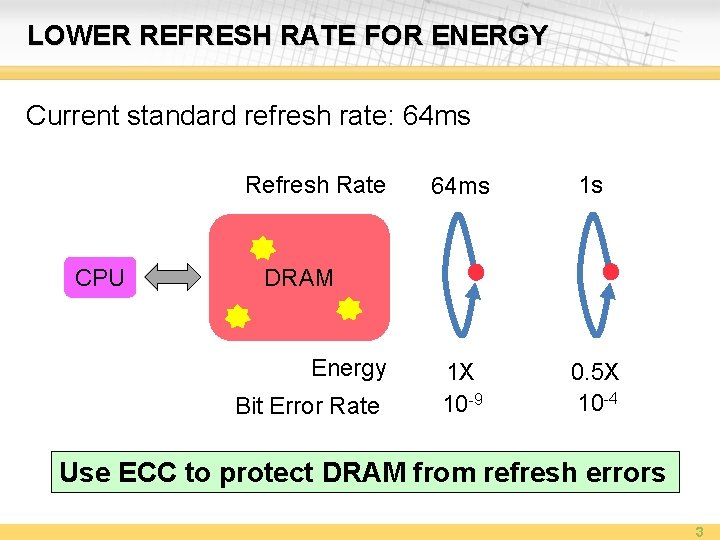

LOWER REFRESH RATE FOR ENERGY Current standard refresh rate: 64 ms Refresh Rate CPU 64 ms 1 s 1 X 10 -9 0. 5 X 10 -4 DRAM Energy Bit Error Rate Use ECC to protect DRAM from refresh errors 3

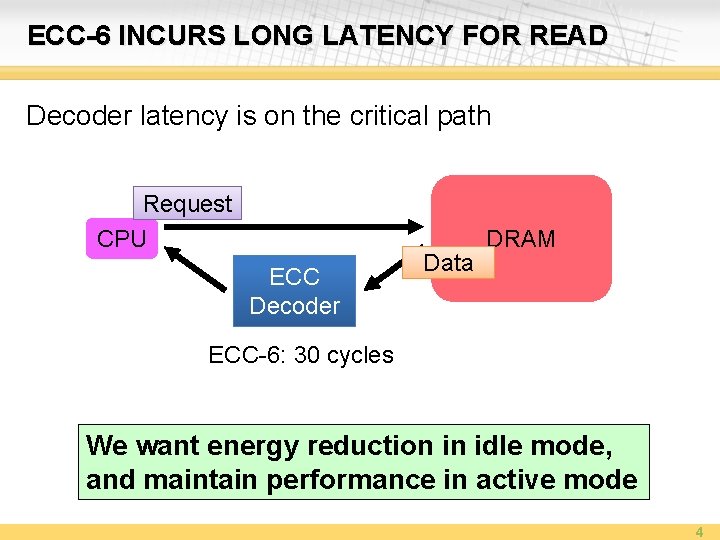

ECC-6 INCURS LONG LATENCY FOR READ Decoder latency is on the critical path Request CPU ECC Decoder Data DRAM ECC-6: 30 cycles We want energy reduction in idle mode, and maintain performance in active mode 4

AGENDA • Introduction • Background – DRAM 101 – Refresh and Errors – Error Correction Codes (ECC) • Morphable ECC • Results • Summary 5

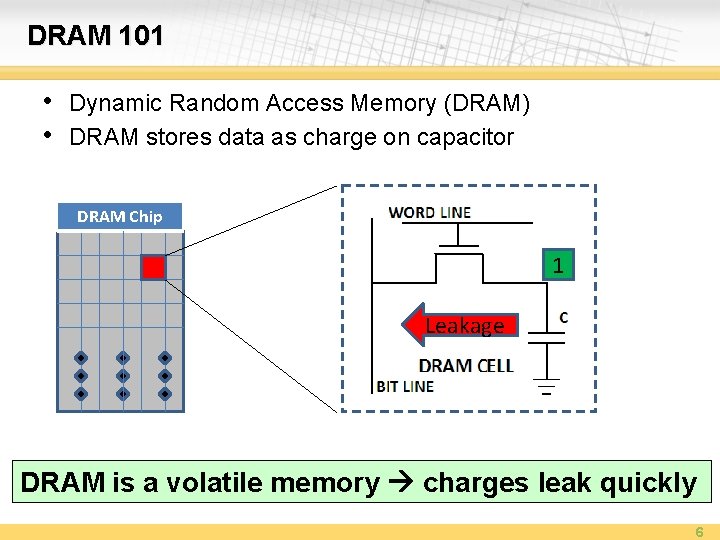

DRAM 101 • Dynamic Random Access Memory (DRAM) • DRAM stores data as charge on capacitor DRAM Chip 1 Leakage DRAM is a volatile memory charges leak quickly 6

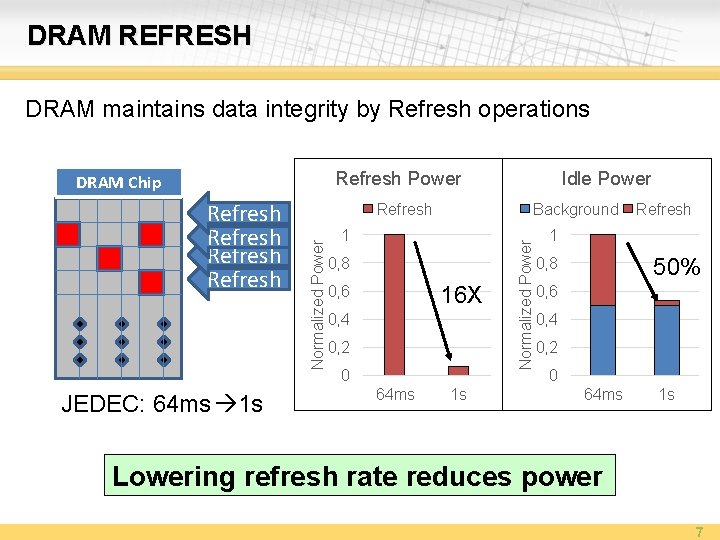

DRAM REFRESH DRAM maintains data integrity by Refresh operations Refresh Power JEDEC: 64 ms 1 s Refresh Normalized Power Refresh Background 1 0, 8 16 X 0, 6 0, 4 0, 2 0 64 ms Idle Power 1 s Normalized Power DRAM Chip Refresh 1 50% 0, 8 0, 6 0, 4 0, 2 0 64 ms 1 s Lowering refresh rate reduces power 7

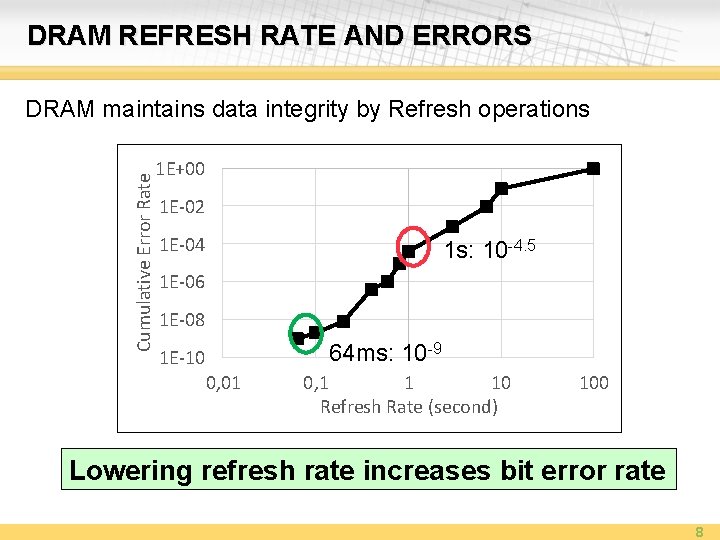

DRAM REFRESH RATE AND ERRORS Cumulative Error Rate DRAM maintains data integrity by Refresh operations 1 E+00 1 E-02 1 E-04 1 s: 10 -4. 5 1 E-06 1 E-08 64 ms: 10 -9 1 E-10 0, 01 0, 1 1 10 Refresh Rate (second) 100 Lowering refresh rate increases bit error rate 8

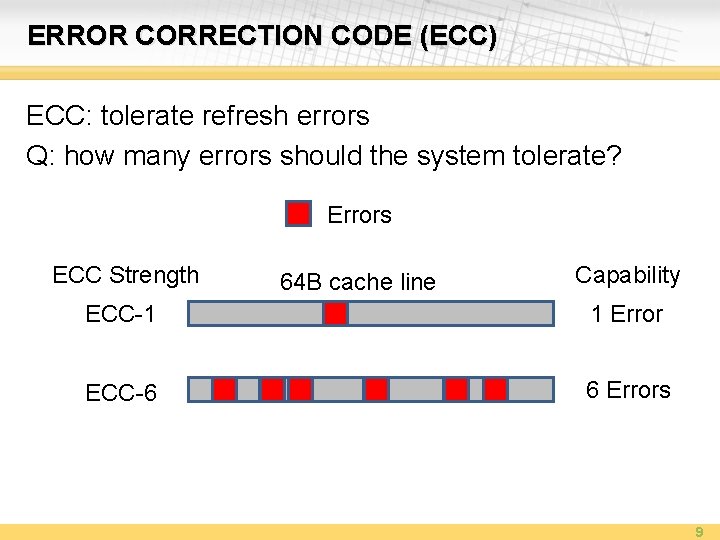

ERROR CORRECTION CODE (ECC) ECC: tolerate refresh errors Q: how many errors should the system tolerate? Errors ECC Strength 64 B cache line Capability ECC-1 1 Error ECC-6 6 Errors 9

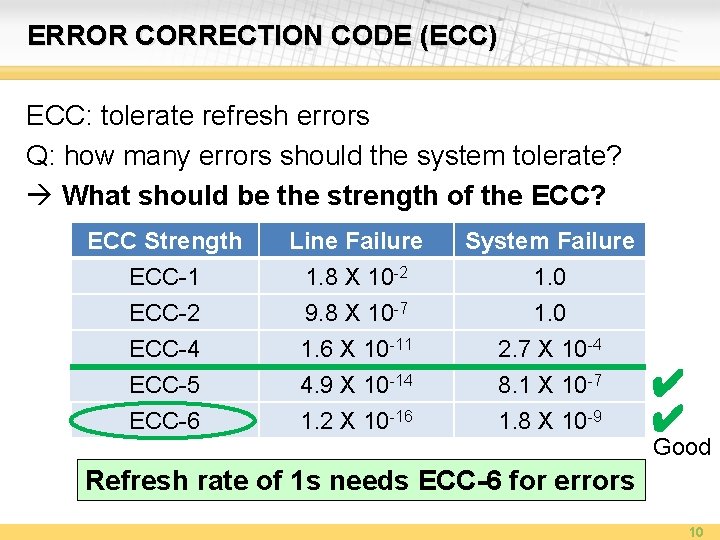

ERROR CORRECTION CODE (ECC) ECC: tolerate refresh errors Q: how many errors should the system tolerate? What should be the strength of the ECC? ECC Strength ECC-1 ECC-2 ECC-4 Line Failure 1. 8 X 10 -2 9. 8 X 10 -7 1. 6 X 10 -11 System Failure 1. 0 2. 7 X 10 -4 ECC-5 ECC-6 4. 9 X 10 -14 1. 2 X 10 -16 8. 1 X 10 -7 1. 8 X 10 -9 ✔ ✔ Good Refresh rate of 1 s needs ECC-6 for errors 10

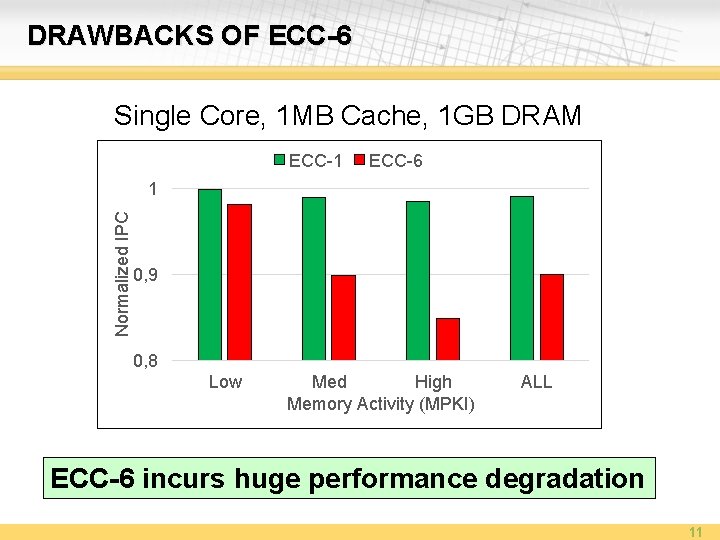

DRAWBACKS OF ECC-6 Single Core, 1 MB Cache, 1 GB DRAM ECC-1 ECC-6 Normalized IPC 1 0, 9 0, 8 Low Med High Memory Activity (MPKI) ALL ECC-6 incurs huge performance degradation 11

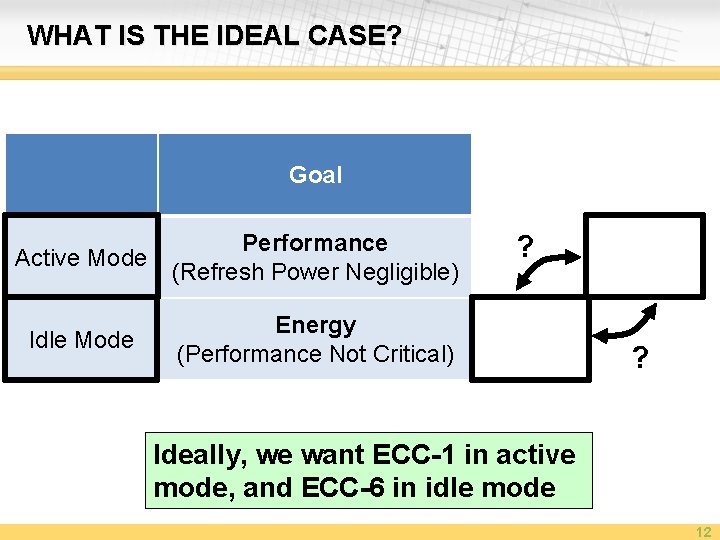

WHAT IS THE IDEAL CASE? Goal Active Mode Performance (Refresh Power Negligible) Idle Mode Energy (Performance Not Critical) Strong ECC ✘? Bad Weak ECC ✔Good ✘Bad ? Ideally, we want ECC-1 in active mode, and ECC-6 in idle mode 12

AGENDA • Introduction • Background • Morphable ECC (MECC) – Overview – Design – ECC Support and Storage • Results • Summary 13

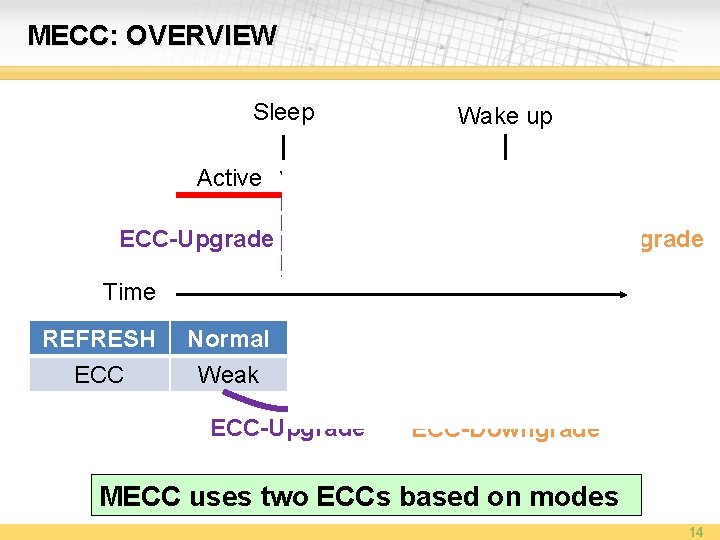

MECC: OVERVIEW Sleep Wake up Active ECC-Upgrade Idle ECC-Downgrade Time REFRESH ECC Normal Weak Slow Strong ECC-Upgrade Normal Weak ECC-Downgrade MECC uses two ECCs based on modes 14

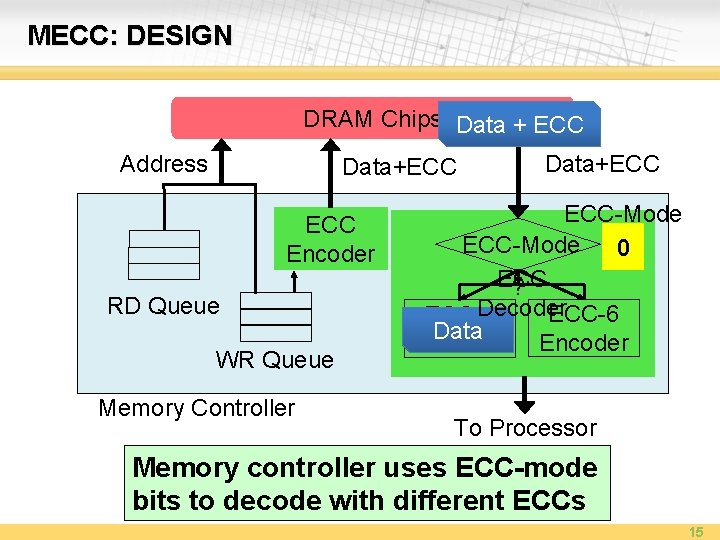

MECC: DESIGN DRAM Chips Data + ECC Address Data+ECC Encoder RD Queue WR Queue Memory Controller Data+ECC ECC-Mode M 0 ECC ? Decoder ECC-6 ECC-1 Data Encoder To Processor Memory controller uses ECC-mode bits to decode with different ECCs 15

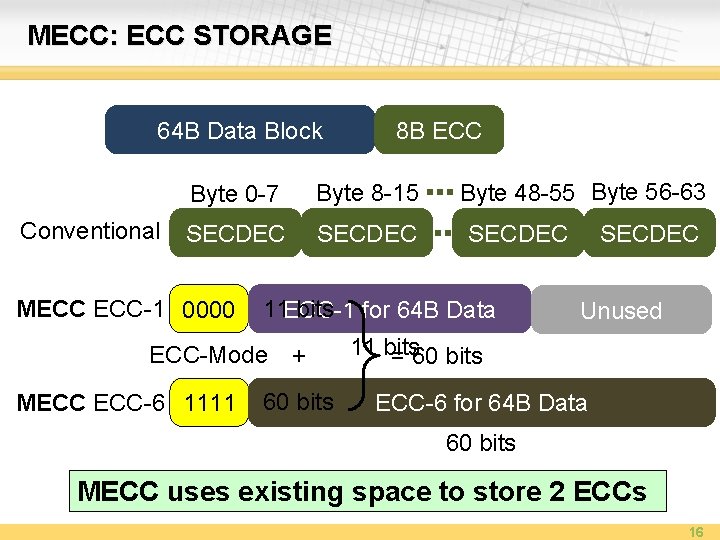

MECC: ECC STORAGE 64 B Data Block Conventional 8 B ECC Byte 0 -7 Byte 8 -15 SECDEC MECC ECC-1 0000 60 bits SECDEC 11 ECC-1 bits for 64 B Data ECC-Mode + MECC ECC-6 1111 Byte 48 -55 Byte 56 -63 Unused 11 bits = 60 bits ECC-6 for 64 B Data 60 bits MECC uses existing space to store 2 ECCs 16

AGENDA • • • Introduction Background Morphable ECC Results Summary 17

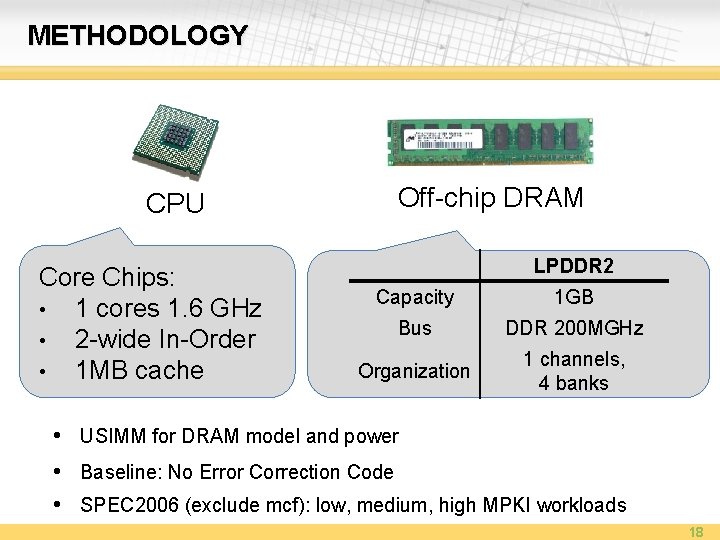

METHODOLOGY CPU Core Chips: • 1 cores 1. 6 GHz • 2 -wide In-Order • 1 MB cache Off-chip DRAM LPDDR 2 Capacity 1 GB Bus DDR 200 MGHz Organization 1 channels, 4 banks • USIMM for DRAM model and power • Baseline: No Error Correction Code • SPEC 2006 (exclude mcf): low, medium, high MPKI workloads 18

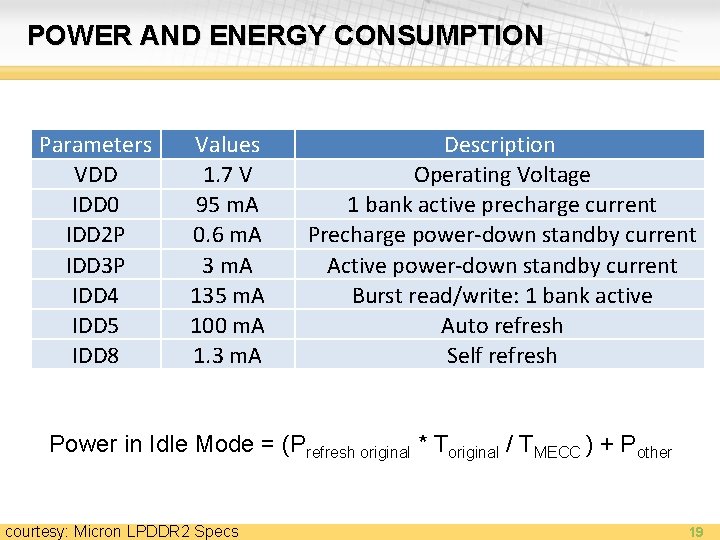

POWER AND ENERGY CONSUMPTION Parameters VDD IDD 0 IDD 2 P IDD 3 P IDD 4 IDD 5 IDD 8 Values 1. 7 V 95 m. A 0. 6 m. A 3 m. A 135 m. A 100 m. A 1. 3 m. A Description Operating Voltage 1 bank active precharge current Precharge power-down standby current Active power-down standby current Burst read/write: 1 bank active Auto refresh Self refresh Power in Idle Mode = (Prefresh original * Toriginal / TMECC ) + Pother courtesy: Micron LPDDR 2 Specs 19

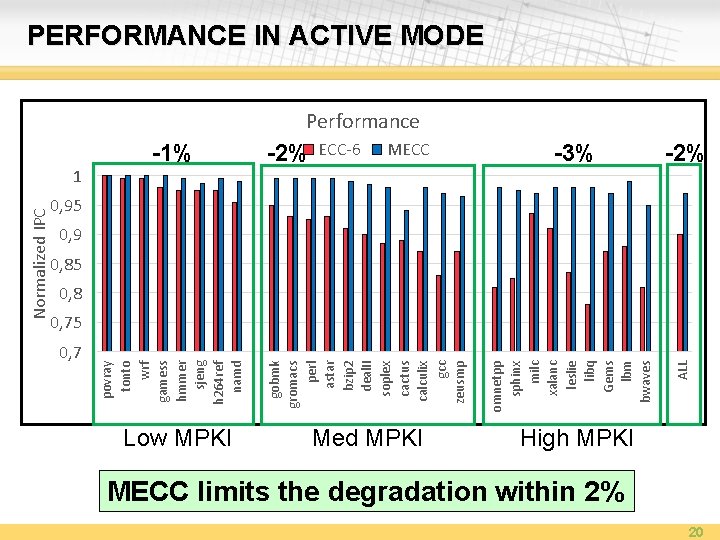

0, 7 -1% Low MPKI -2% ECC-6 0, 95 0, 9 0, 85 0, 8 0, 75 Med MPKI -3% -2% ALL MECC omnetpp sphinx milc xalanc leslie libq Gems lbm bwaves gobmk gromacs perl astar bzip 2 deal. II soplex cactus calculix gcc zeusmp 1 povray tonto wrf gamess hmmer sjeng h 264 ref namd Normalized IPC PERFORMANCE IN ACTIVE MODE Performance High MPKI MECC limits the degradation within 2% 20

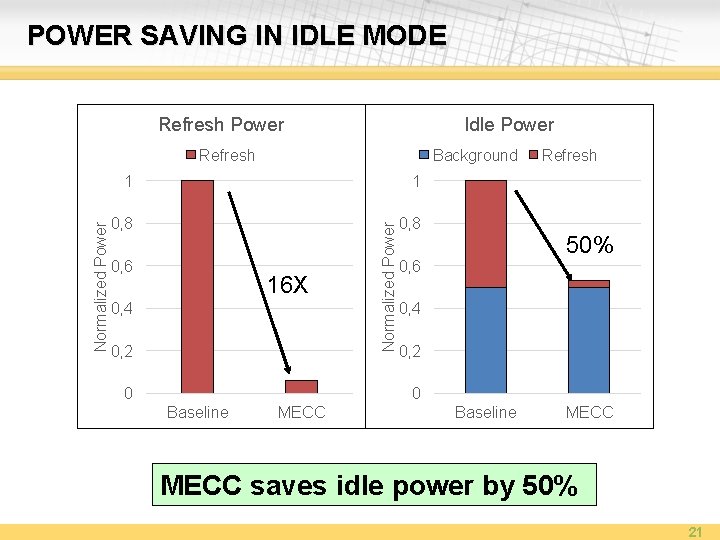

POWER SAVING IN IDLE MODE Refresh Power Idle Power Background 1 1 0, 8 0, 6 16 X 0, 4 0, 2 0 Normalized Power Refresh 50% 0, 6 0, 4 0, 2 0 Baseline MECC saves idle power by 50% 21

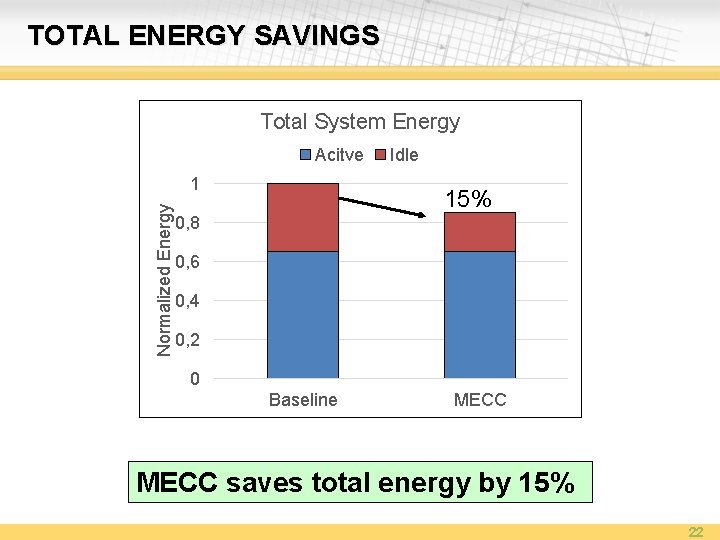

TOTAL ENERGY SAVINGS Total System Energy Acitve Normalized Energy 1 Idle 15% 0, 8 0, 6 0, 4 0, 2 0 Baseline MECC saves total energy by 15% 22

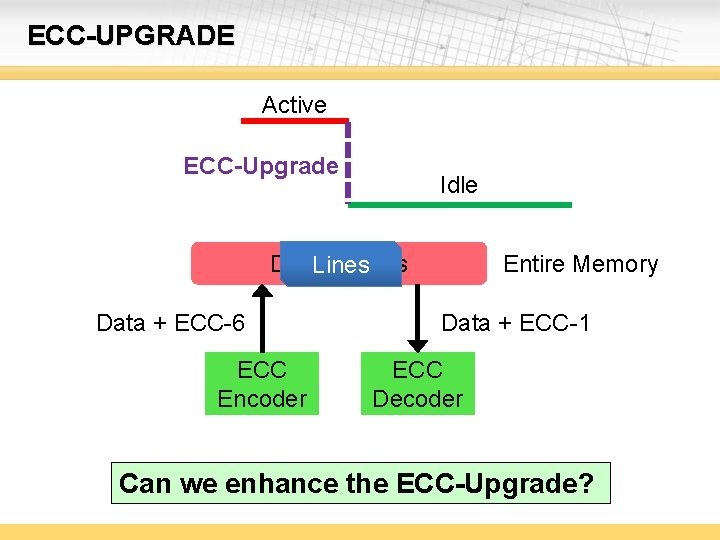

ECC-UPGRADE Active ECC-Upgrade Idle Entire Memory DRAM Chips Lines Data + ECC-6 ECC Encoder Data + ECC-1 ECC Decoder Can we enhance the ECC-Upgrade?

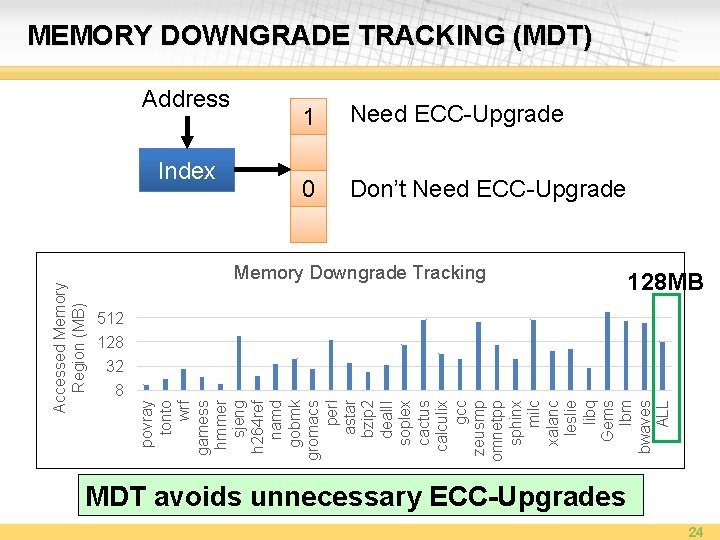

povray tonto wrf gamess hmmer sjeng h 264 ref namd gobmk gromacs perl astar bzip 2 deal. II soplex cactus calculix gcc zeusmp omnetpp sphinx milc xalanc leslie libq Gems lbm bwaves ALL Accessed Memory Region (MB) MEMORY DOWNGRADE TRACKING (MDT) Address Index 1 Need ECC-Upgrade 0 Don’t Need ECC-Upgrade Memory Downgrade Tracking 128 MB 512 128 32 8 MDT avoids unnecessary ECC-Upgrades 24

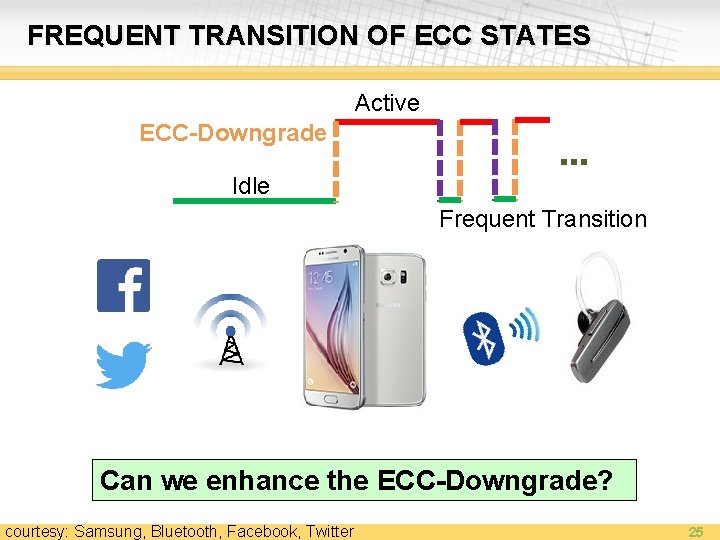

FREQUENT TRANSITION OF ECC STATES Active ECC-Downgrade Idle Frequent Transition Can we enhance the ECC-Downgrade? courtesy: Samsung, Bluetooth, Facebook, Twitter 25

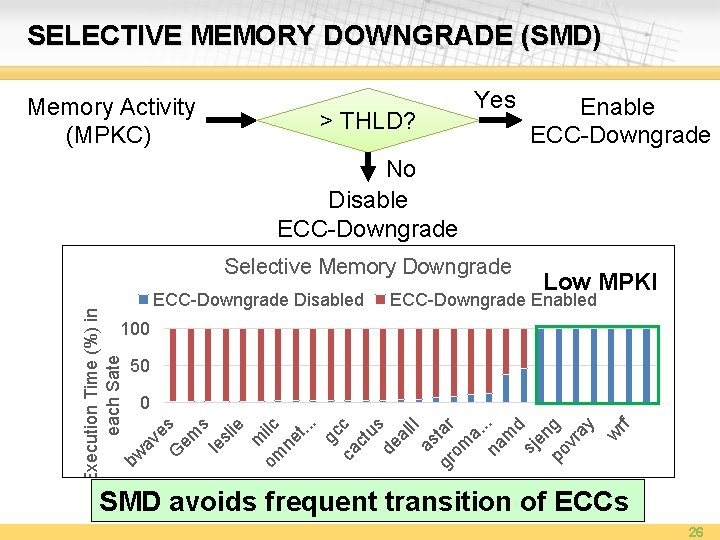

SELECTIVE MEMORY DOWNGRADE (SMD) Memory Activity (MPKC) > THLD? Yes Enable ECC-Downgrade No Disable ECC-Downgrade Selective Memory Downgrade ECC-Downgrade Enabled Execution Time (%) in each Sate bw av es G em s le sl ie m om ilc ne t. . . gc ca c ct us de al II as gr tar om a. na. . m d sj en po g vr ay w rf ECC-Downgrade Disabled Low MPKI 100 50 0 SMD avoids frequent transition of ECCs 26

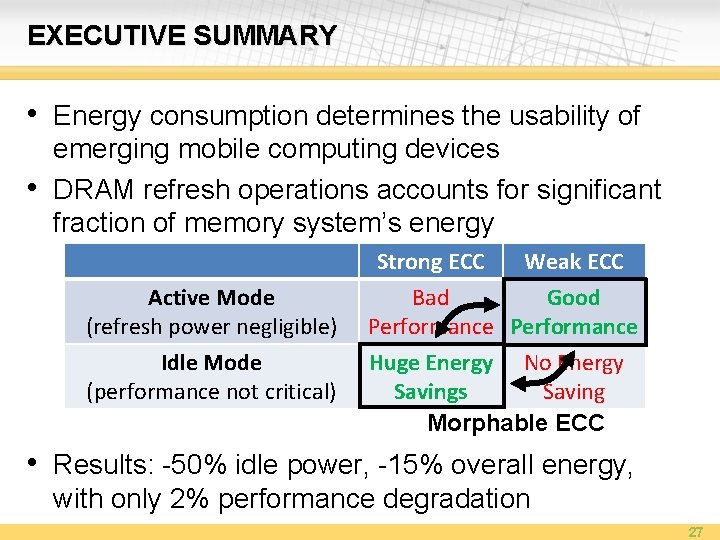

EXECUTIVE SUMMARY • Energy consumption determines the usability of • emerging mobile computing devices DRAM refresh operations accounts for significant fraction of memory system’s energy Active Mode (refresh power negligible) Idle Mode (performance not critical) Strong ECC Weak ECC Bad Good Performance Huge Energy No Energy Savings Saving Morphable ECC • Results: -50% idle power, -15% overall energy, with only 2% performance degradation 27

REDUCING REFRESH POWER IN MOBILE DEVICES WITH MORPHABLE ECC DSN-45 06/24/2015 Rio de Janeiro, Brazil Chiachen Chou, Georgia Tech Prashant Nair, Georgia Tech Moinuddin K. Qureshi, Georgia Tech Computer Architecture and Emerging Technologies Lab, Georgia Tech

- Slides: 28