PRELUCRAREA VOLUMELOR MARI DE DATE CURS 2 ARHITECTURI

- Slides: 43

PRELUCRAREA VOLUMELOR MARI DE DATE CURS 2: ARHITECTURI ȘI SISTEME PENTRU CALCULUL PARALEL ȘI DISTRIBUIT Conf. Univ. Dr. Habil. Marc FRÎNCU marc. frincu@e-uvt. ro

CE ESTE O ARHITECTURĂ PARALELĂ? ”A collection of processing elements that cooperate to solve large problems fast” – Almasi and Gottlieb, 1989 ARM 11 (2002 -2005) � 90% din piața dispozitiviler embedded se bazează pe procesoare ARM � � Pipeline în 8 pași 8 instrucțiuni in-flight (out-of-order) Intel Pentium 4 (2000 -2008) � � � 32. 000 Intel Xeon CPU-uri cu 12 core-uri 48. 000 Intel Xeon Phi CPU-uri cu 57 core-uri 34 petaflopi Sunway Taihulight � � � Quad core 2 thread-uri per core GPU Tianhe-2 (2013) � � � 124 instrucțiuni in-flight Pipeline în 31 de pași Superscalar: paralelism la nivel de instrucțiuni în procesor Intel Skylake (august 2015) � � � Rasberry Pi Locul 1 în lume în noiembrie 2017 40. 960 SW 26010 CPU-uri cu 256 core-uri 125 petaflopi Google Cloud � � Ferme de clustere interconectate 10 Tbps bandwidth (SUA-Japonia)

MOTIVAȚIE Performanța sistemelor secvențiale este limitată Calcul/transfer de date prin porți logice, dispozitive de memorie � Latență <> 0 � Presupunând un mediu ideal rămân limitările datorate vitezei luminii Numeroase aplicații importante necesită performanță Simulări de reactoare nucleare � Predicții climatice � Big Data � Google: 40. 000 căutări per minut Facebook: 1 miliard de utilizatori online zilnic Progrese tehnologice � Ce facem cu atâția tranzistori?

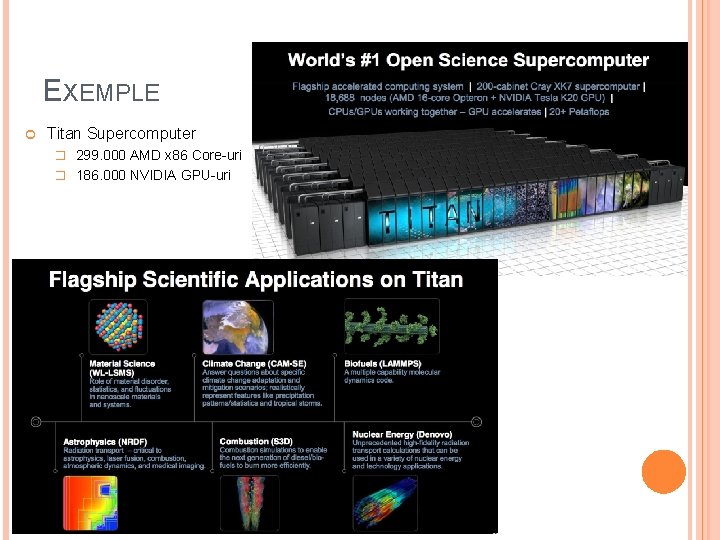

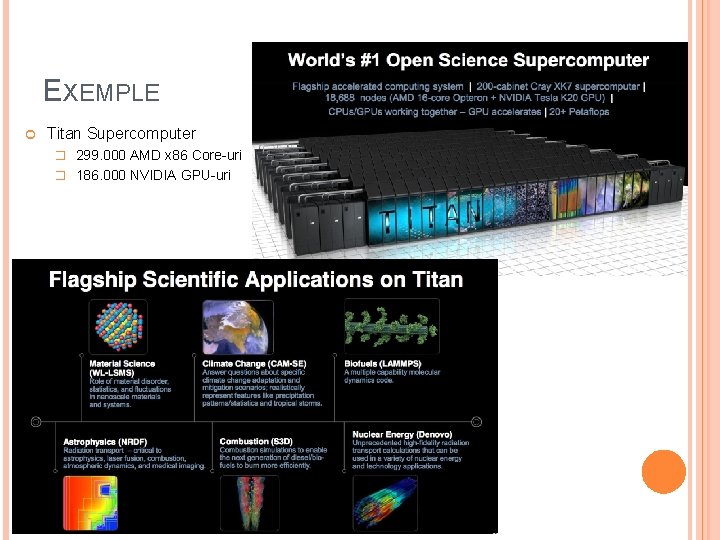

EXEMPLE Titan Supercomputer � 299. 000 AMD x 86 Core-uri � 186. 000 NVIDIA GPU-uri

TRANZISTORI VS. VITEZĂ Mai mulți tranzistori pe chip mai multă viteză � Dispozitive electronice ce au rol de întrerupătoare pentru a construi porți logice � Viteza operațiilor este dată de timpul necesar tranzistorilor pentru a se opri fără a cauza erori Un tranzistor mic se va opri/porni mai repede Exemplu: 3 Ghz = 3 miliarde de operații per secundă � Creșterea densității tranzistorilor pentru a mări viteza Intel P 4: 170 milioane tranzistori Intel 15 -core Xeon IVY Bridge: 4, 3 miliarde În medie în fiecare an puterea de calcul crește cu 60% față de anul trecut

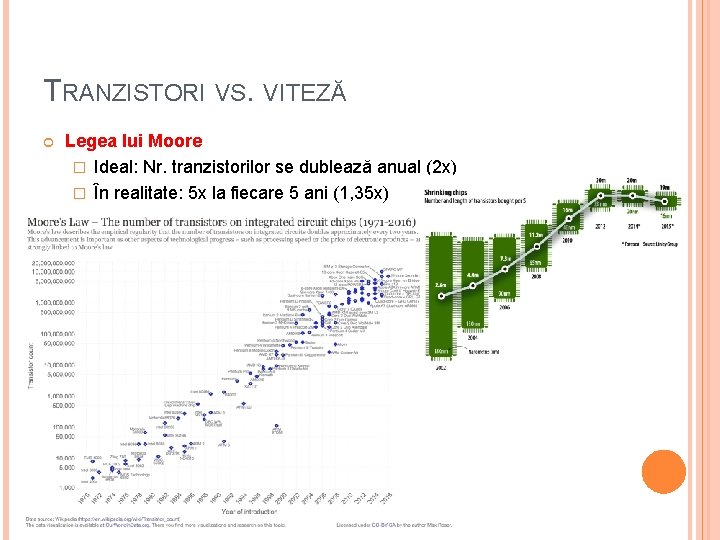

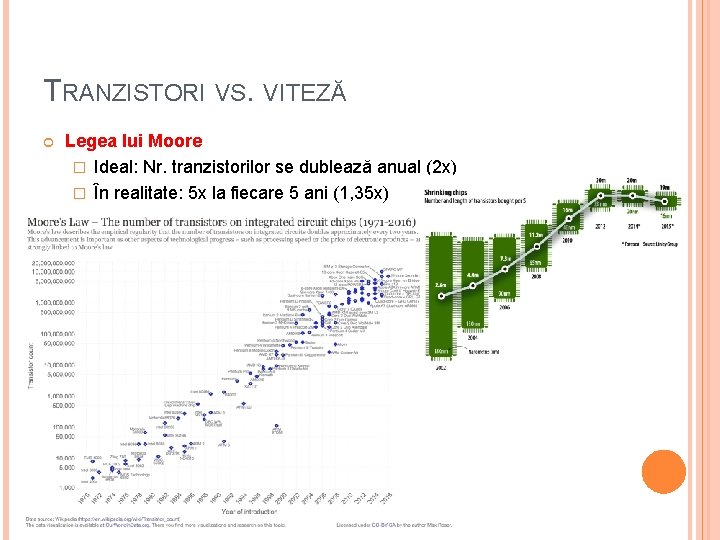

TRANZISTORI VS. VITEZĂ Legea lui Moore � Ideal: Nr. tranzistorilor se dublează anual (2 x) � În realitate: 5 x la fiecare 5 ani (1, 35 x)

TRANZISTORI VS. VITEZĂ De ce nu putem mări viteza la infinit? � Dimensiunea chip-lui = constantă � Dar, crește densitatea tranzistorilor 2018: 10 nm Intel Cannonlake � Scalabilitatea lui Dennard Puterea (V) necesară operării tranzistorilor = constantă chiar dacă crește numărul de tranzistori de pe chip Totuși acest lucru nu mai e valabil (din 2006)! Tranzistorii devin atât de mici încât le scade integritatea structurală și scapă curent Cu cât oprim/pornim tranzistor mai des (repede ) căldură mai mare � Viteze de 8, 5 -9 GHz necesită răcire cu azot lichid

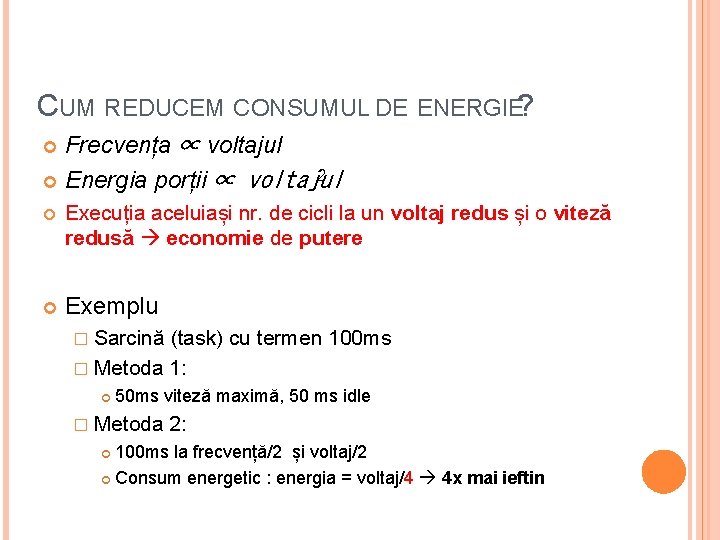

CUM REDUCEM CONSUMUL DE ENERGIE? Frecvența ∝ voltajul 2 Energia porții ∝ voltajul Execuția aceluiași nr. de cicli la un voltaj redus și o viteză redusă economie de putere Exemplu � Sarcină (task) cu termen 100 ms � Metoda 1: 50 ms viteză maximă, 50 ms idle � Metoda 2: 100 ms la frecvență/2 și voltaj/2 Consum energetic : energia = voltaj/4 4 x mai ieftin

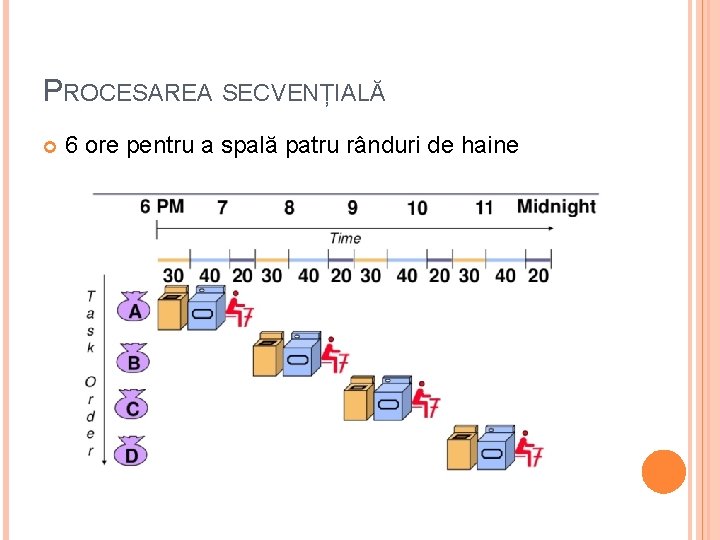

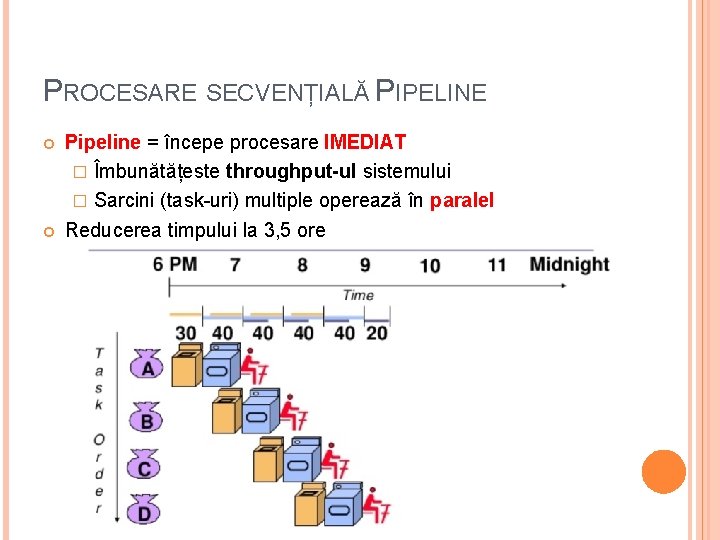

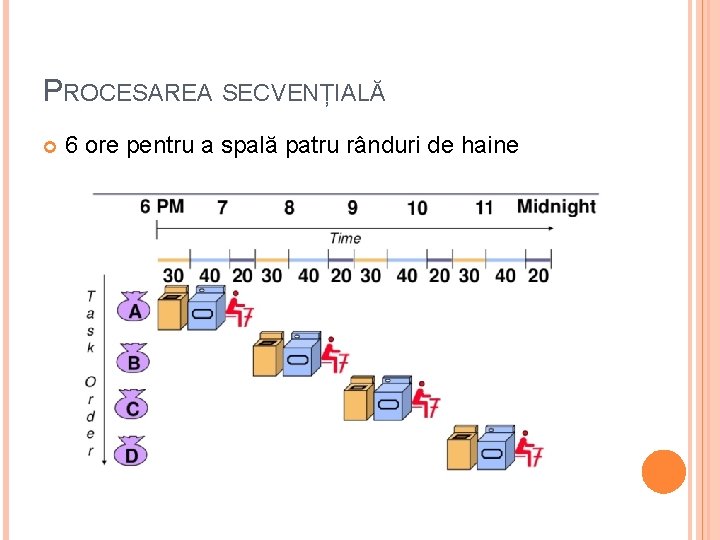

PROCESAREA SECVENȚIALĂ 6 ore pentru a spală patru rânduri de haine

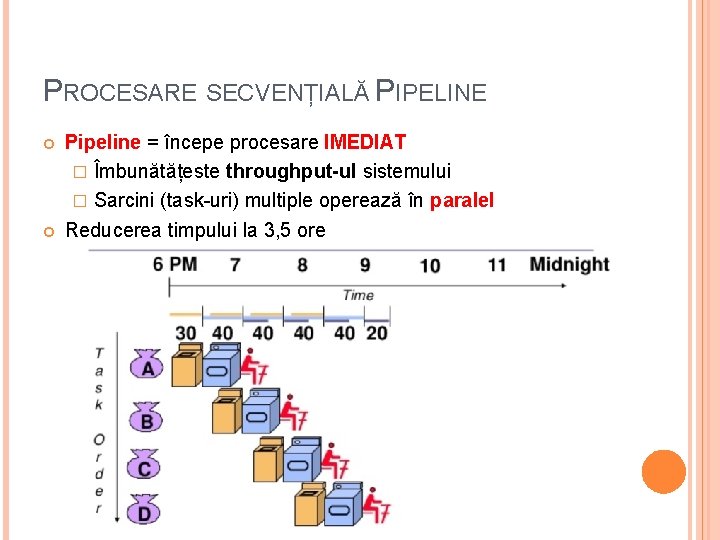

PROCESARE SECVENȚIALĂ PIPELINE Pipeline = începe procesare IMEDIAT � Îmbunătățeste throughput-ul sistemului � Sarcini (task-uri) multiple operează în paralel Reducerea timpului la 3, 5 ore

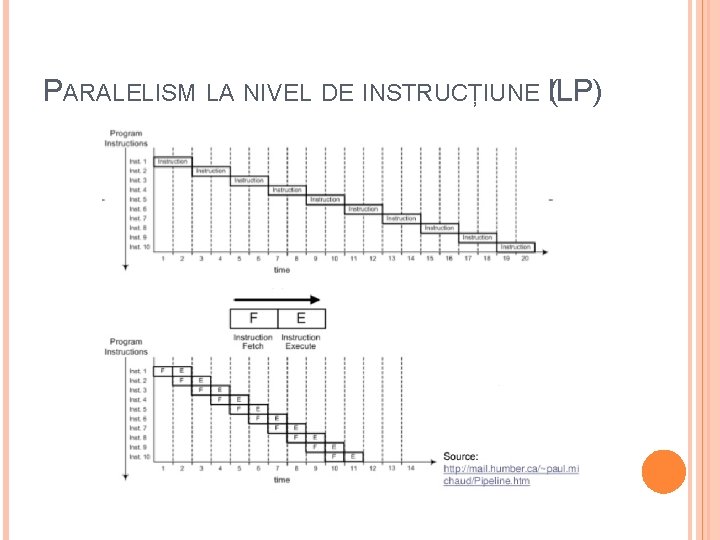

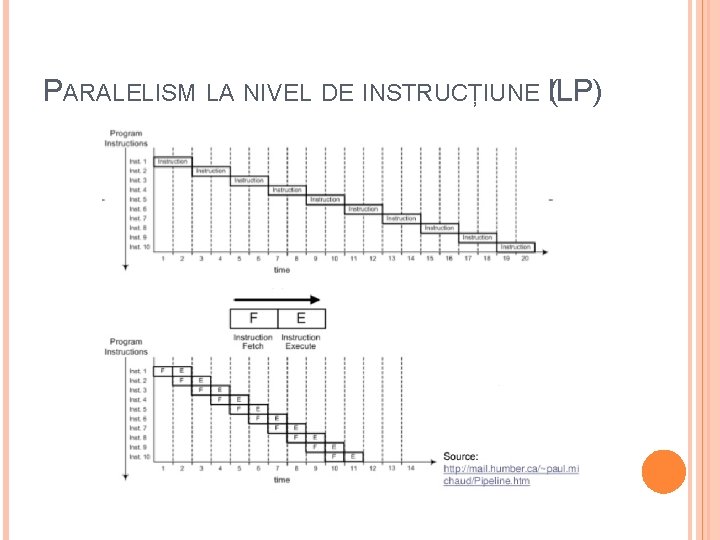

PARALELISM LA NIVEL DE INSTRUCȚIUNE (ILP)

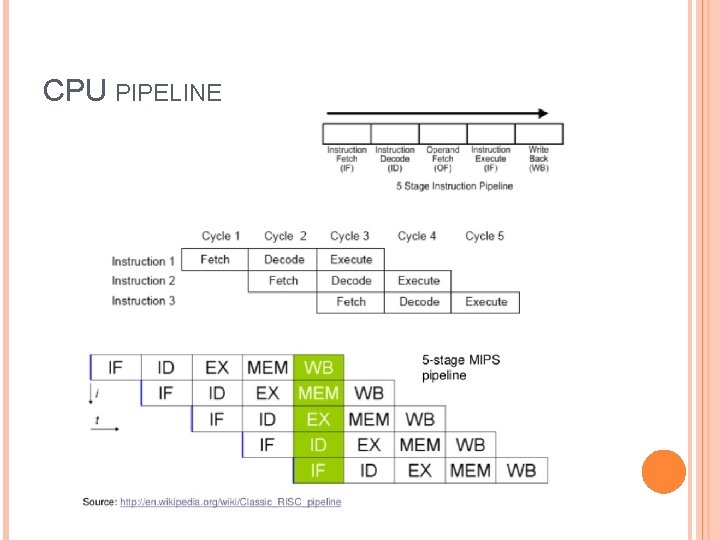

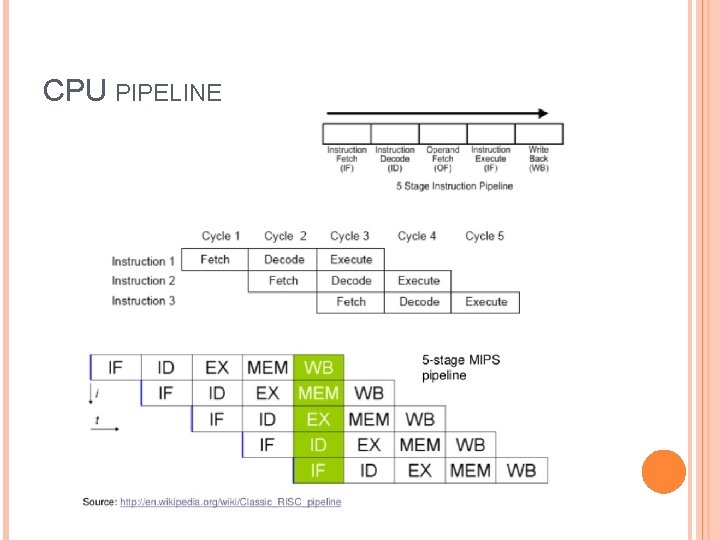

CPU PIPELINE

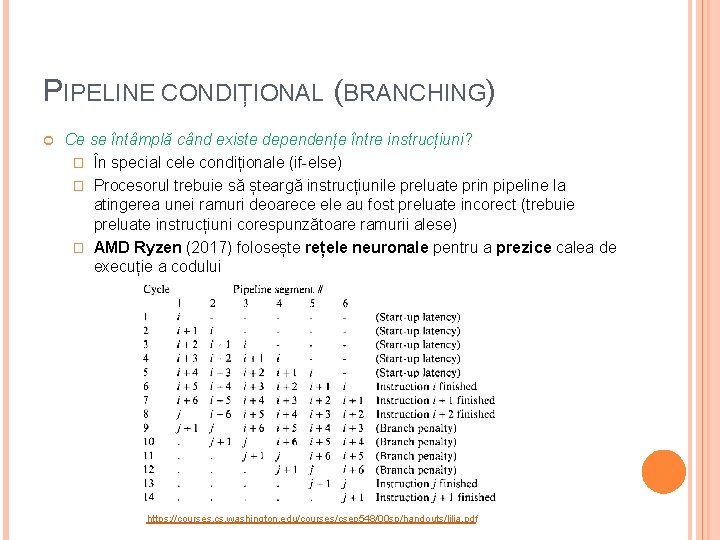

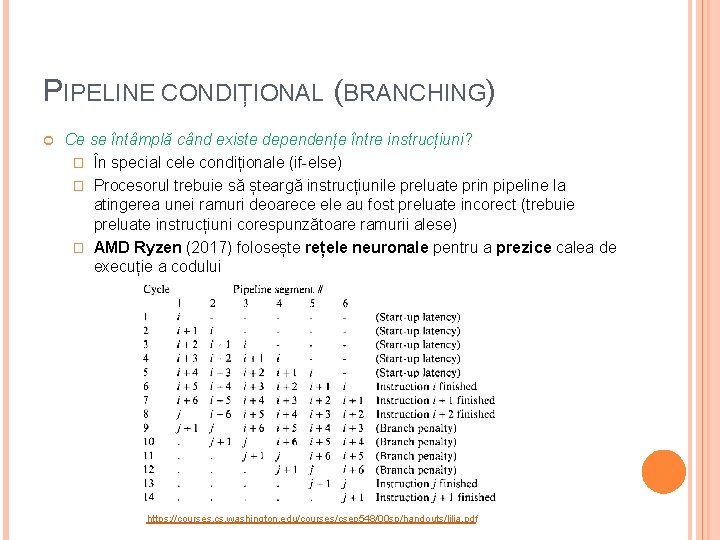

PIPELINE CONDIȚIONAL (BRANCHING) Ce se întâmplă când existe dependențe între instrucțiuni? � În special cele condiționale (if-else) � Procesorul trebuie să șteargă instrucțiunile preluate prin pipeline la atingerea unei ramuri deoarece ele au fost preluate incorect (trebuie preluate instrucțiuni corespunzătoare ramurii alese) � AMD Ryzen (2017) folosește rețele neuronale pentru a prezice calea de execuție a codului https: //courses. cs. washington. edu/courses/csep 548/00 sp/handouts/lilja. pdf

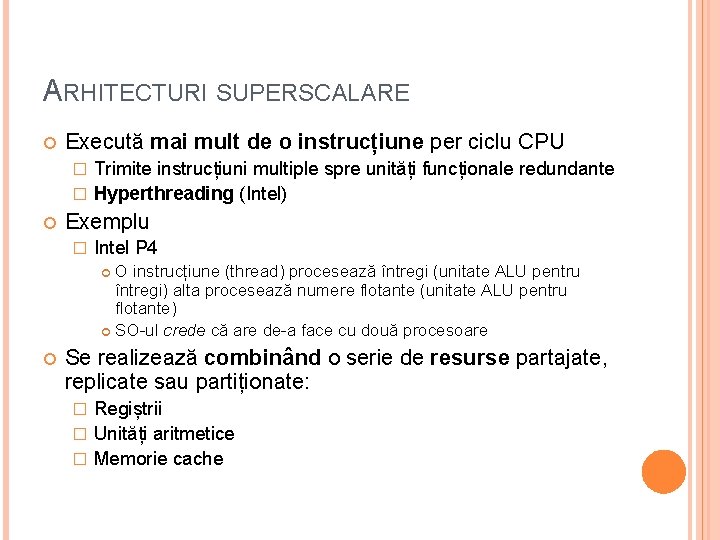

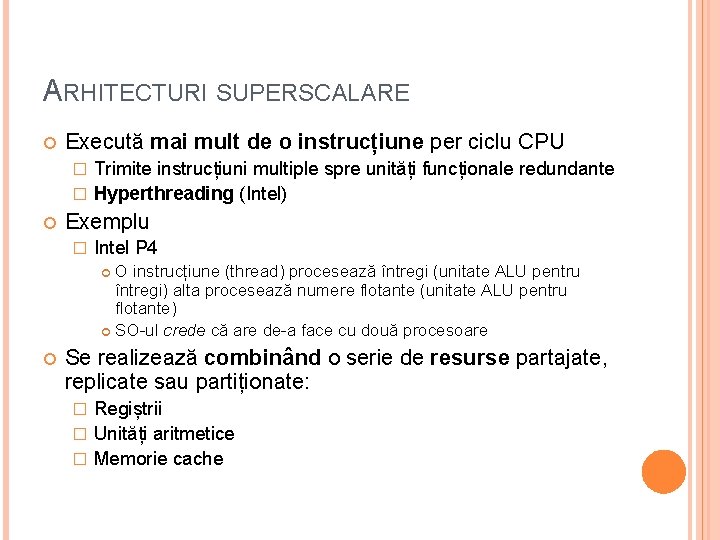

ARHITECTURI SUPERSCALARE Execută mai mult de o instrucțiune per ciclu CPU Trimite instrucțiuni multiple spre unități funcționale redundante � Hyperthreading (Intel) � Exemplu � Intel P 4 O instrucțiune (thread) procesează întregi (unitate ALU pentru întregi) alta procesează numere flotante (unitate ALU pentru flotante) SO-ul crede că are de-a face cu două procesoare Se realizează combinând o serie de resurse partajate, replicate sau partiționate: Regiștrii � Unități aritmetice � Memorie cache �

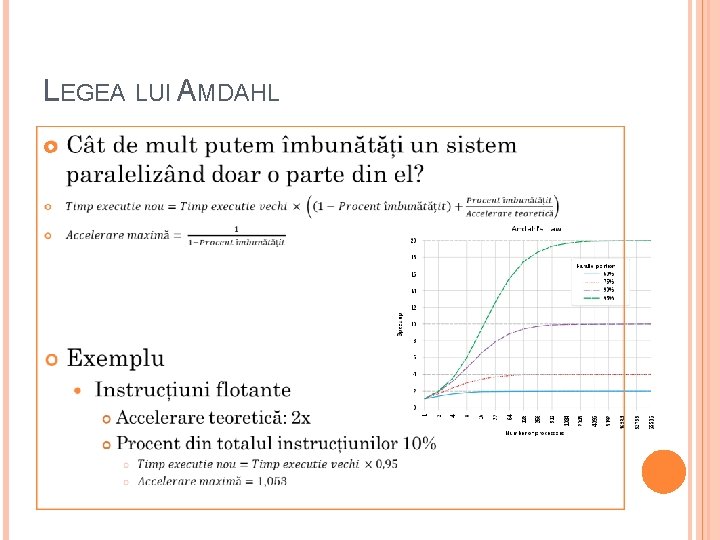

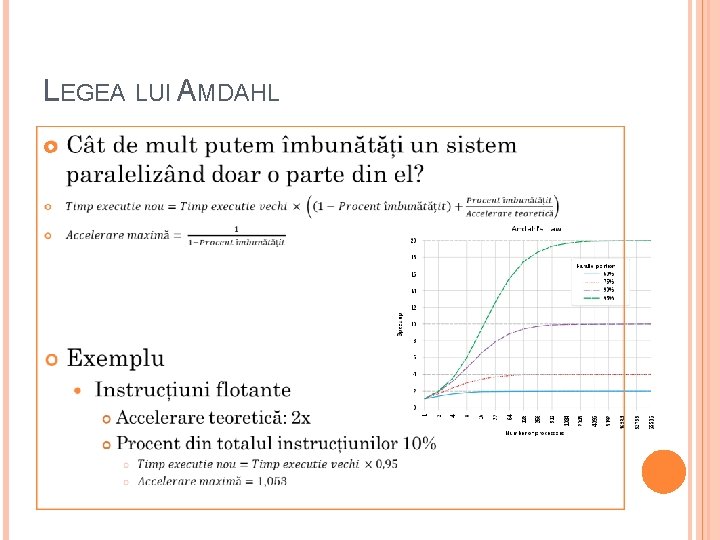

LEGEA LUI AMDAHL

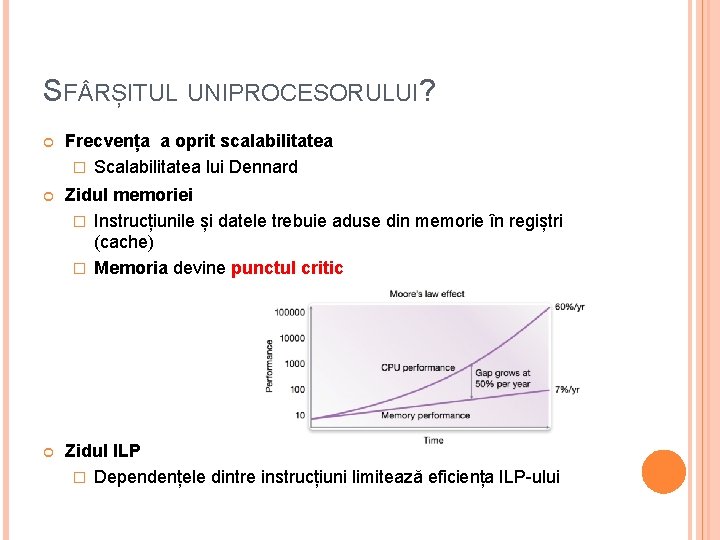

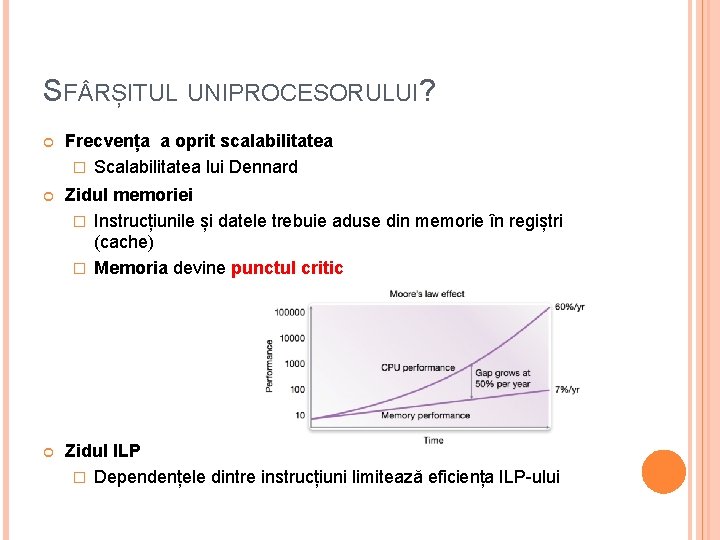

SF RȘITUL UNIPROCESORULUI? Frecvența a oprit scalabilitatea � Scalabilitatea lui Dennard Zidul memoriei � Instrucțiunile și datele trebuie aduse din memorie în regiștri (cache) � Memoria devine punctul critic Zidul ILP � Dependențele dintre instrucțiuni limitează eficiența ILP-ului

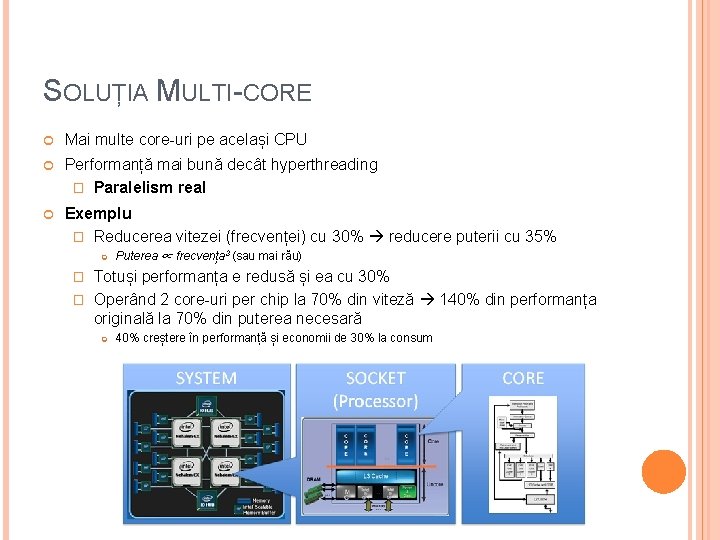

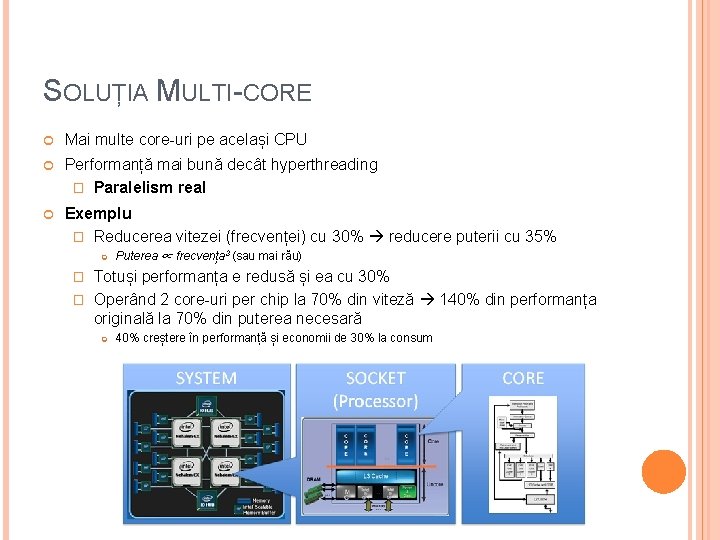

SOLUȚIA MULTI-CORE Mai multe core-uri pe același CPU Performanță mai bună decât hyperthreading � Paralelism real Exemplu � Reducerea vitezei (frecvenței) cu 30% reducere puterii cu 35% Puterea ∝ frecvența 3 (sau mai rău) Totuși performanța e redusă și ea cu 30% � Operând 2 core-uri per chip la 70% din viteză 140% din performanța originală la 70% din puterea necesară � 40% creștere în performanță și economii de 30% la consum

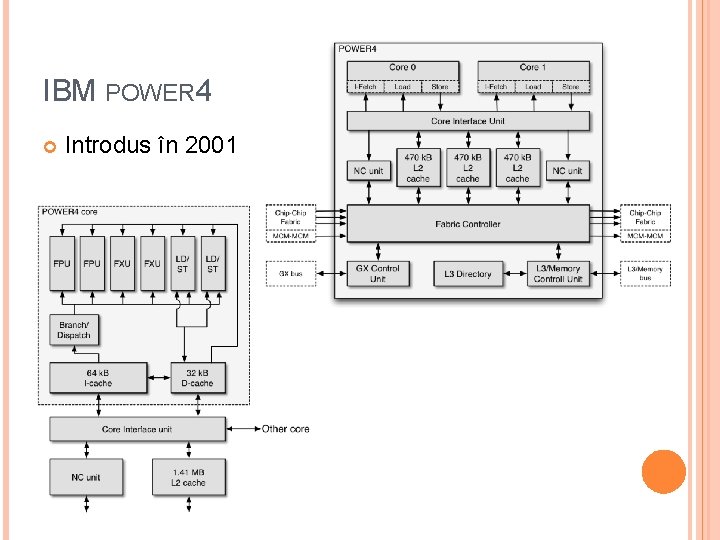

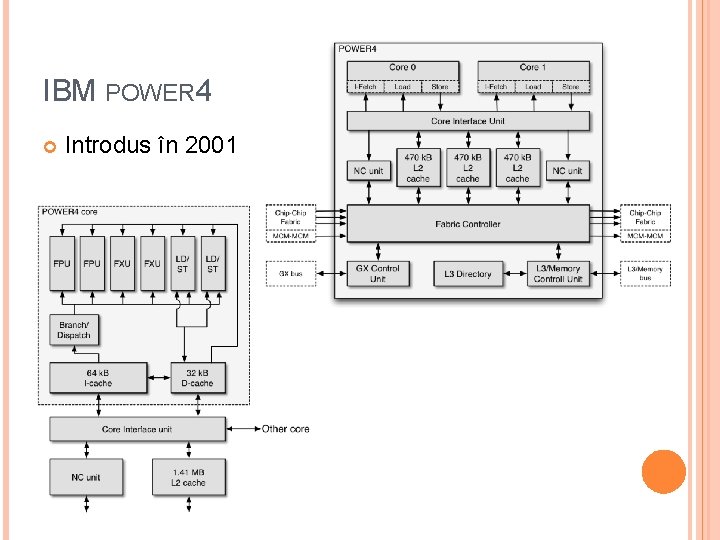

IBM POWER 4 Introdus în 2001

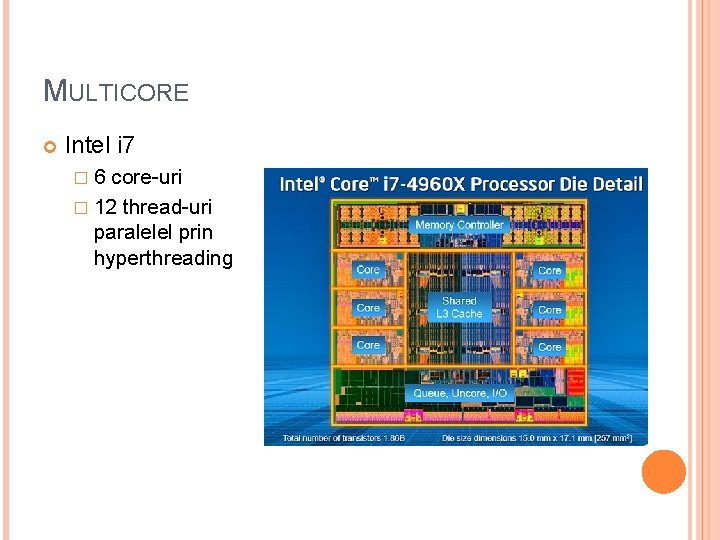

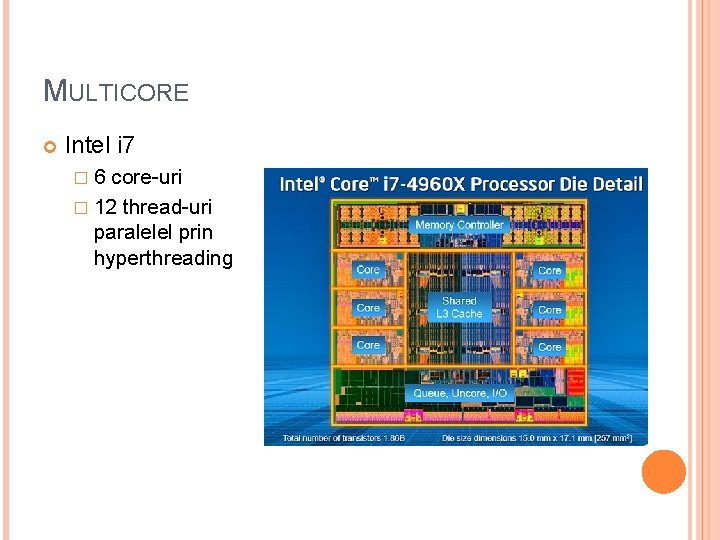

MULTICORE Intel i 7 � 6 core-uri � 12 thread-uri paralelel prin hyperthreading

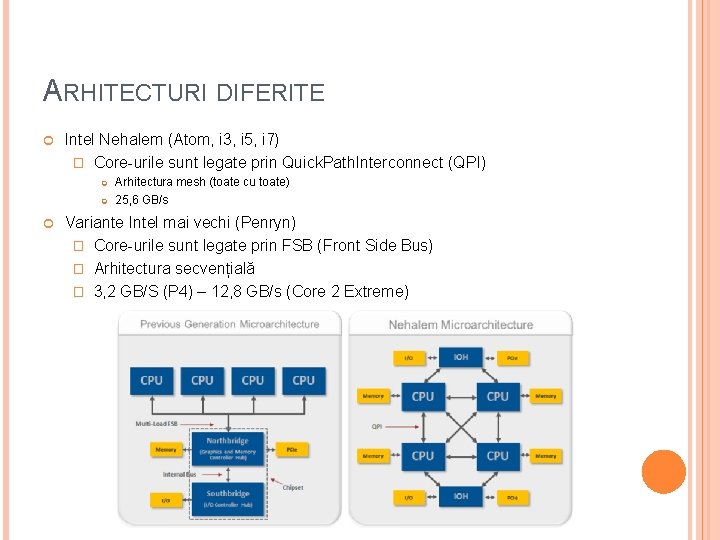

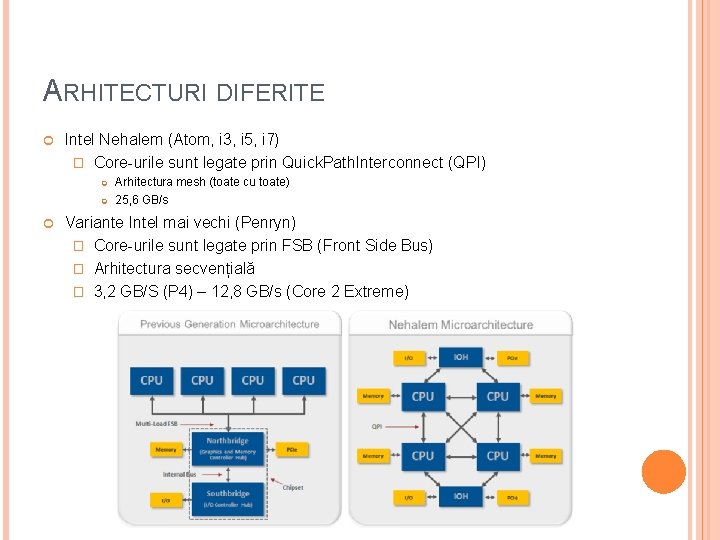

ARHITECTURI DIFERITE Intel Nehalem (Atom, i 3, i 5, i 7) � Core-urile sunt legate prin Quick. Path. Interconnect (QPI) Arhitectura mesh (toate cu toate) 25, 6 GB/s Variante Intel mai vechi (Penryn) � Core-urile sunt legate prin FSB (Front Side Bus) � Arhitectura secvențială � 3, 2 GB/S (P 4) – 12, 8 GB/s (Core 2 Extreme)

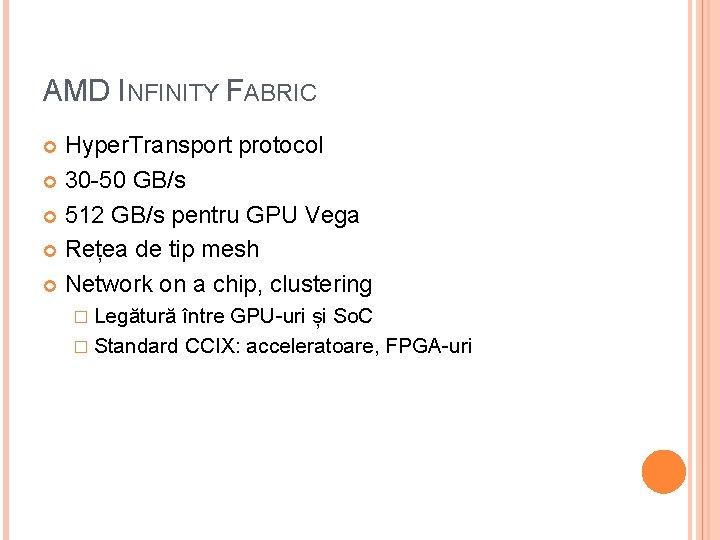

AMD INFINITY FABRIC Hyper. Transport protocol 30 -50 GB/s 512 GB/s pentru GPU Vega Rețea de tip mesh Network on a chip, clustering � Legătură între GPU-uri și So. C � Standard CCIX: acceleratoare, FPGA-uri

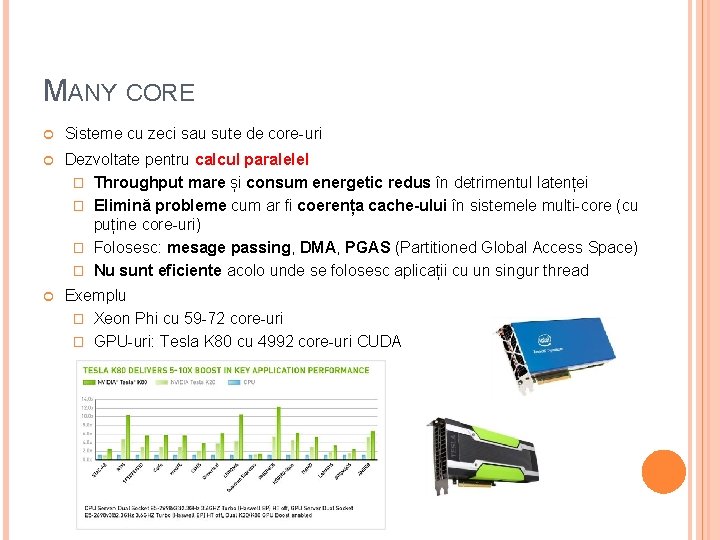

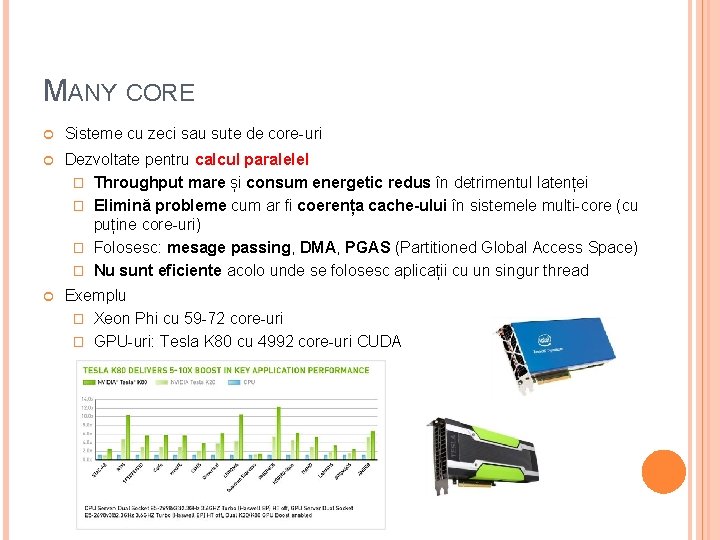

MANY CORE Sisteme cu zeci sau sute de core-uri Dezvoltate pentru calcul paralelel � Throughput mare și consum energetic redus în detrimentul latenței � Elimină probleme cum ar fi coerența cache-ului în sistemele multi-core (cu puține core-uri) � Folosesc: mesage passing, DMA, PGAS (Partitioned Global Access Space) � Nu sunt eficiente acolo unde se folosesc aplicații cu un singur thread Exemplu � Xeon Phi cu 59 -72 core-uri � GPU-uri: Tesla K 80 cu 4992 core-uri CUDA

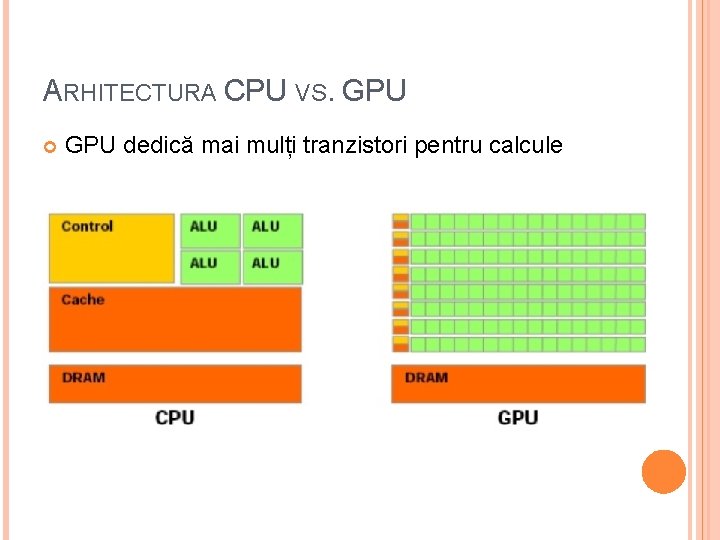

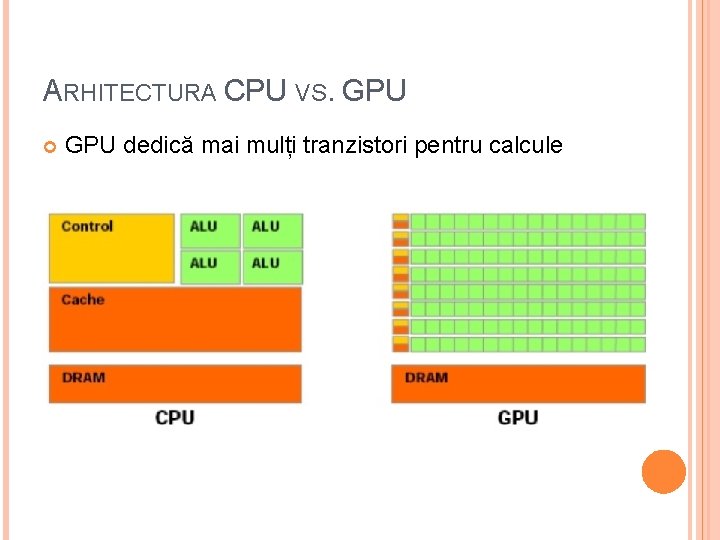

ARHITECTURA CPU VS. GPU dedică mai mulți tranzistori pentru calcule

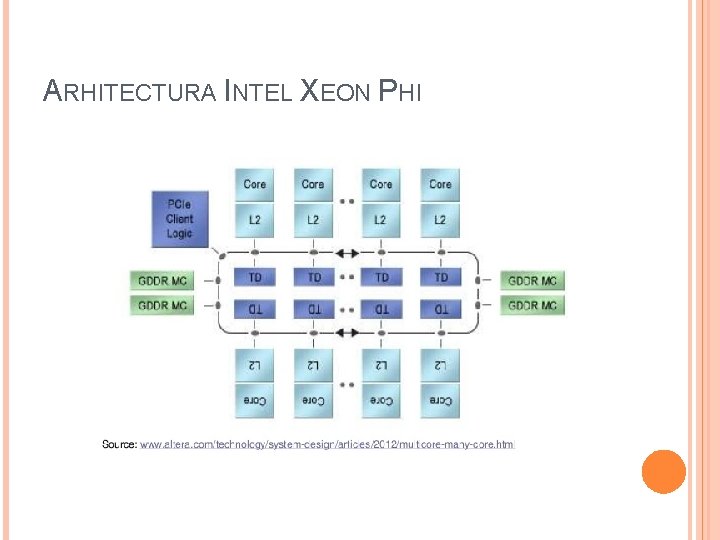

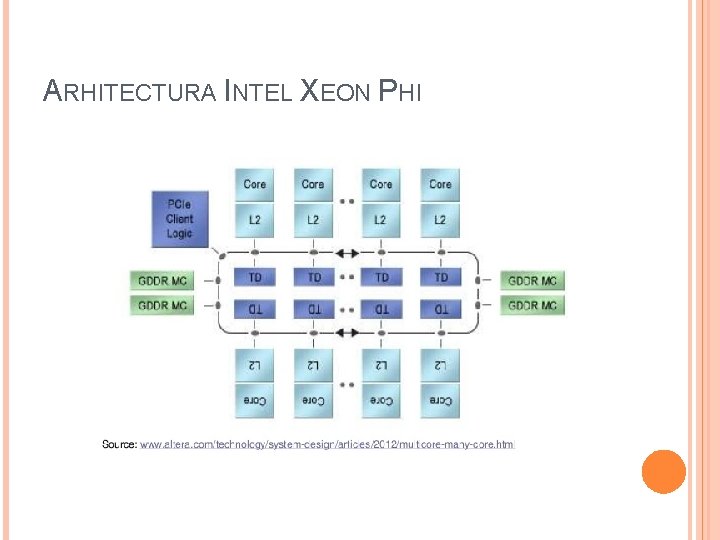

ARHITECTURA INTEL XEON PHI

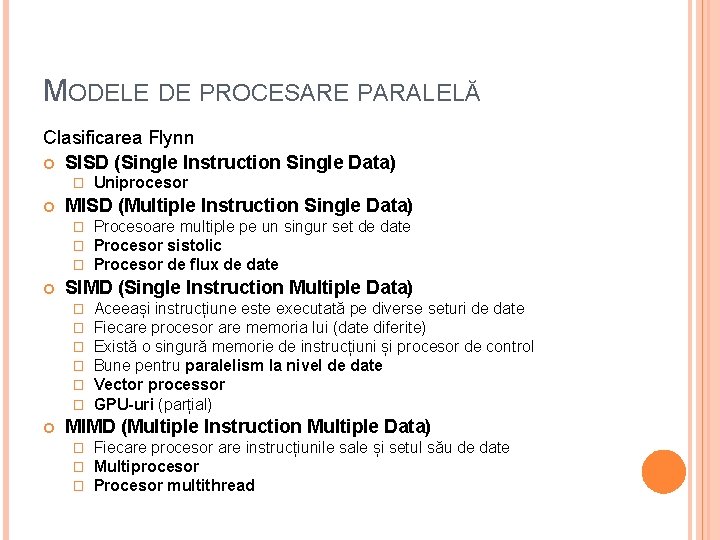

MODELE DE PROCESARE PARALELĂ Clasificarea Flynn SISD (Single Instruction Single Data) � MISD (Multiple Instruction Single Data) � � � Procesoare multiple pe un singur set de date Procesor sistolic Procesor de flux de date SIMD (Single Instruction Multiple Data) � � � Uniprocesor Aceeași instrucțiune este executată pe diverse seturi de date Fiecare procesor are memoria lui (date diferite) Există o singură memorie de instrucțiuni și procesor de control Bune pentru paralelism la nivel de date Vector processor GPU-uri (parțial) MIMD (Multiple Instruction Multiple Data) � � � Fiecare procesor are instrucțiunile sale și setul său de date Multiprocesor Procesor multithread

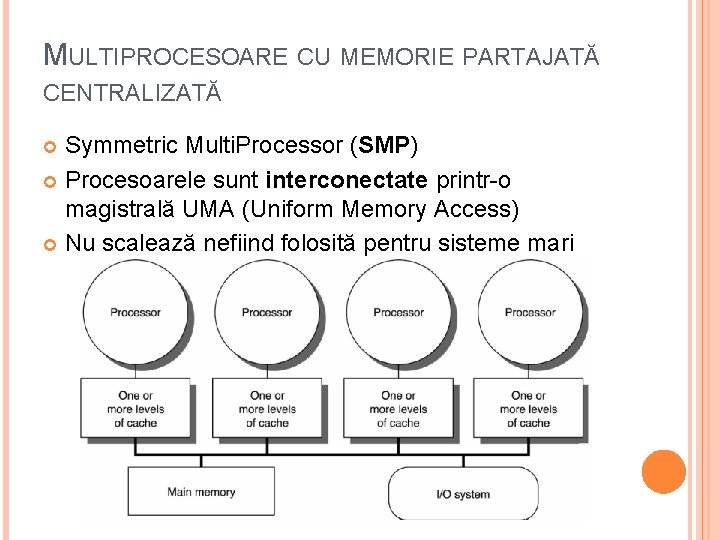

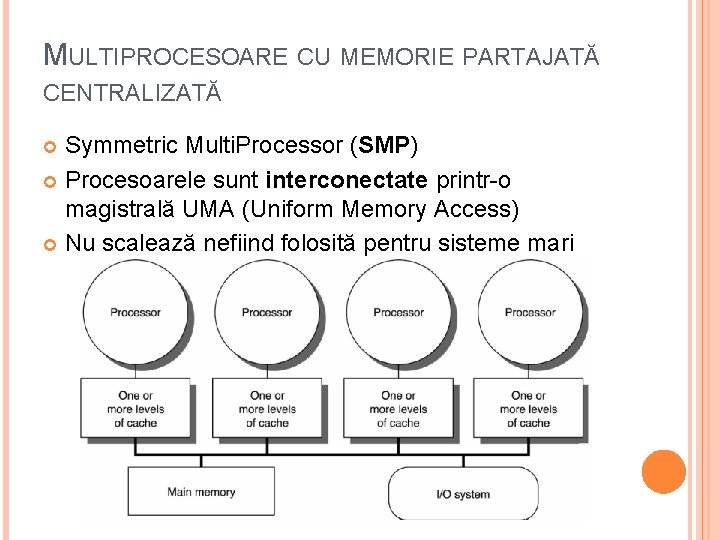

MULTIPROCESOARE CU MEMORIE PARTAJATĂ CENTRALIZATĂ Symmetric Multi. Processor (SMP) Procesoarele sunt interconectate printr-o magistrală UMA (Uniform Memory Access) Nu scalează nefiind folosită pentru sisteme mari

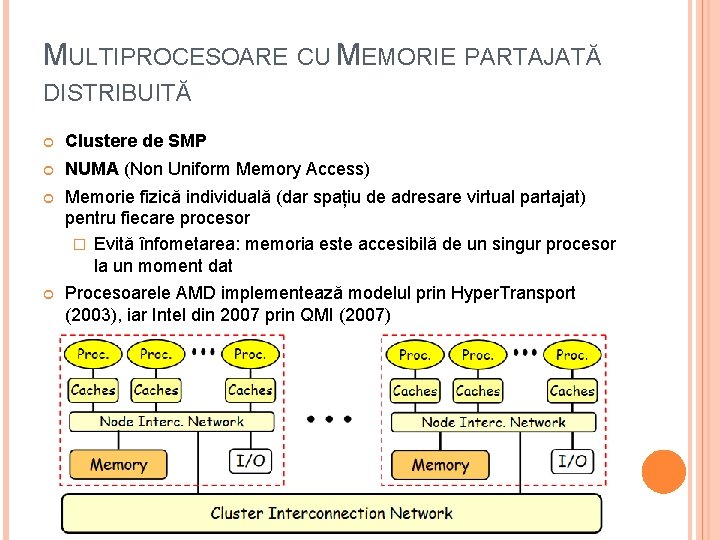

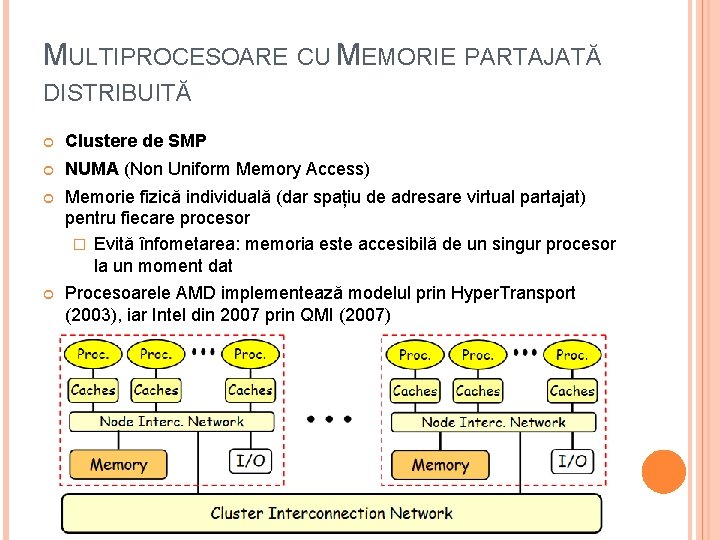

MULTIPROCESOARE CU MEMORIE PARTAJATĂ DISTRIBUITĂ Clustere de SMP NUMA (Non Uniform Memory Access) Memorie fizică individuală (dar spațiu de adresare virtual partajat) pentru fiecare procesor � Evită înfometarea: memoria este accesibilă de un singur procesor la un moment dat Procesoarele AMD implementează modelul prin Hyper. Transport (2003), iar Intel din 2007 prin QMI (2007)

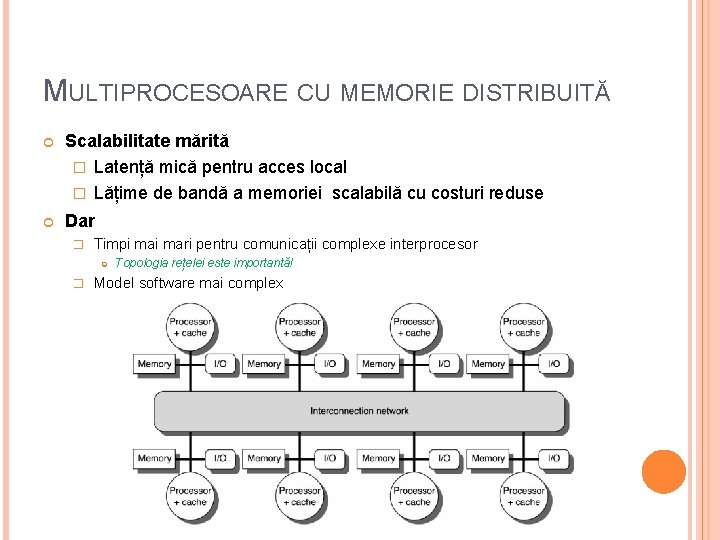

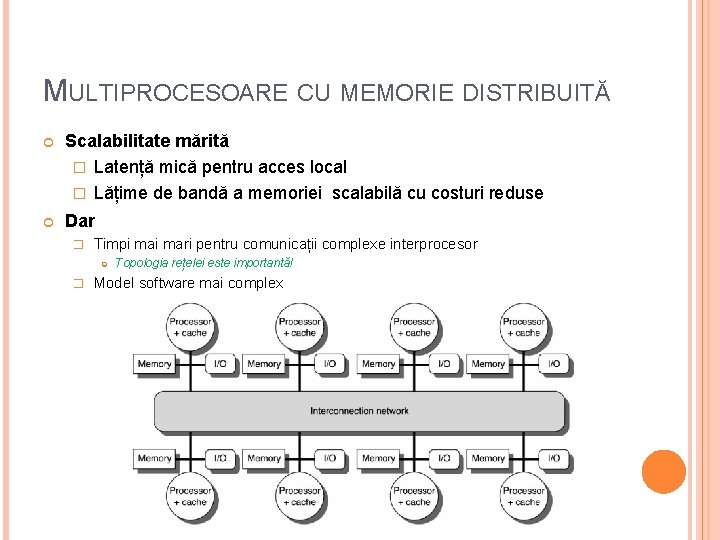

MULTIPROCESOARE CU MEMORIE DISTRIBUITĂ Scalabilitate mărită � Latență mică pentru acces local � Lățime de bandă a memoriei scalabilă cu costuri reduse Dar � Timpi mari pentru comunicații complexe interprocesor � Topologia rețelei este importantă! Model software mai complex

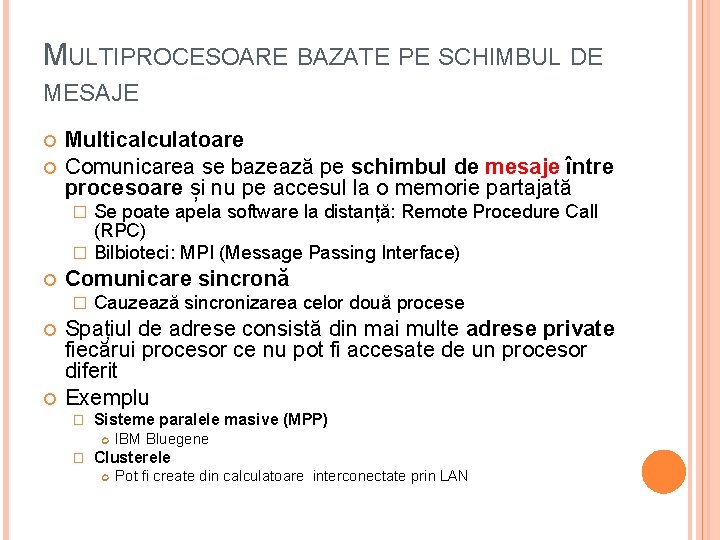

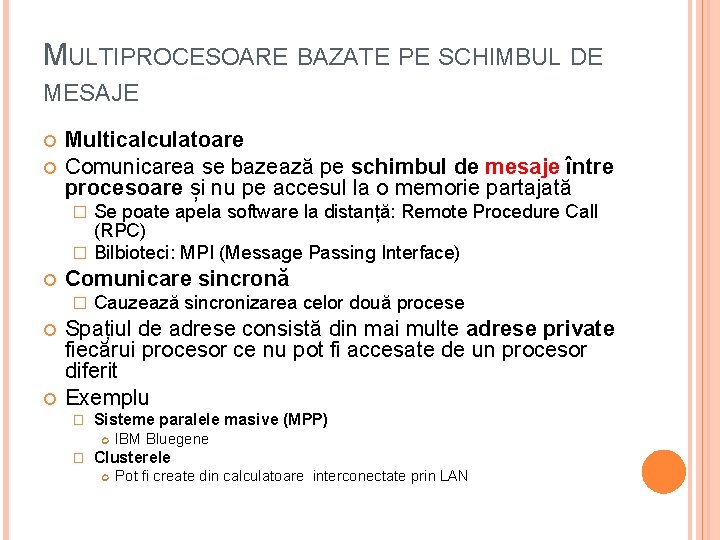

MULTIPROCESOARE BAZATE PE SCHIMBUL DE MESAJE Multicalculatoare Comunicarea se bazează pe schimbul de mesaje între procesoare și nu pe accesul la o memorie partajată Se poate apela software la distanță: Remote Procedure Call (RPC) � Bilbioteci: MPI (Message Passing Interface) � Comunicare sincronă � Cauzează sincronizarea celor două procese Spațiul de adrese consistă din mai multe adrese private fiecărui procesor ce nu pot fi accesate de un procesor diferit Exemplu � Sisteme paralele masive (MPP) � IBM Bluegene Clusterele Pot fi create din calculatoare interconectate prin LAN

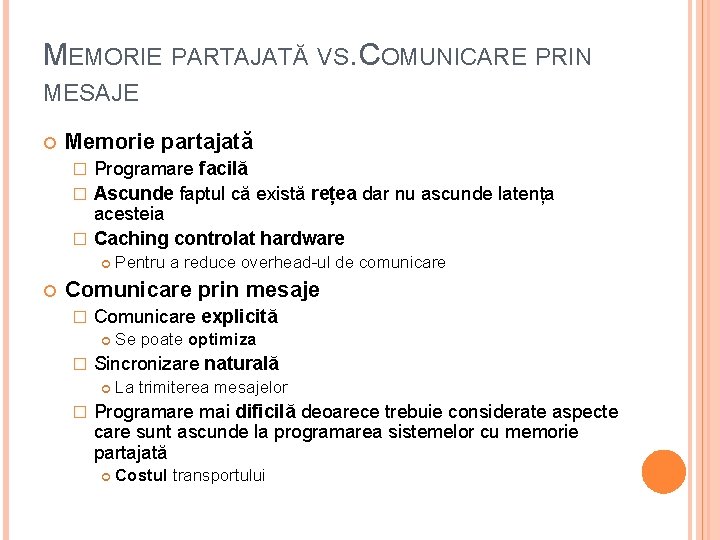

MEMORIE PARTAJATĂ VS. COMUNICARE PRIN MESAJE Memorie partajată Programare facilă � Ascunde faptul că există rețea dar nu ascunde latența acesteia � Caching controlat hardware � Pentru a reduce overhead-ul de comunicare Comunicare prin mesaje � Comunicare explicită � Sincronizare naturală � Se poate optimiza La trimiterea mesajelor Programare mai dificilă deoarece trebuie considerate aspecte care sunt ascunde la programarea sistemelor cu memorie partajată Costul transportului

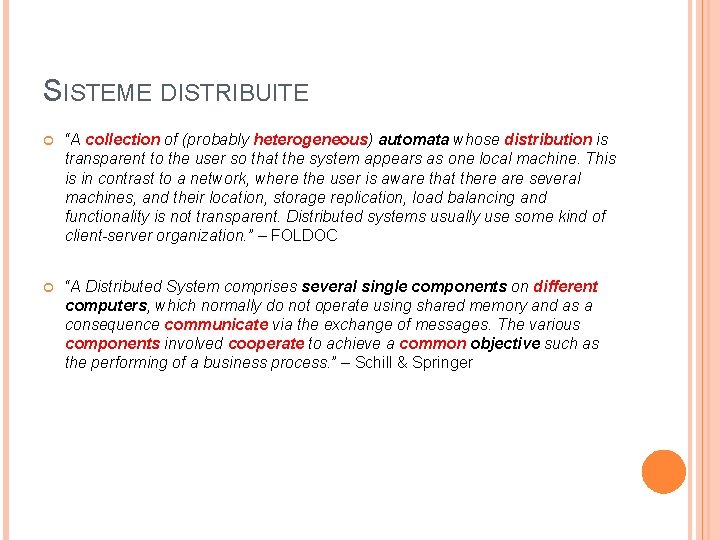

SISTEME DISTRIBUITE “A collection of (probably heterogeneous) automata whose distribution is transparent to the user so that the system appears as one local machine. This is in contrast to a network, where the user is aware that there are several machines, and their location, storage replication, load balancing and functionality is not transparent. Distributed systems usually use some kind of client-server organization. ” – FOLDOC “A Distributed System comprises several single components on different computers, which normally do not operate using shared memory and as a consequence communicate via the exchange of messages. The various components involved cooperate to achieve a common objective such as the performing of a business process. ” – Schill & Springer

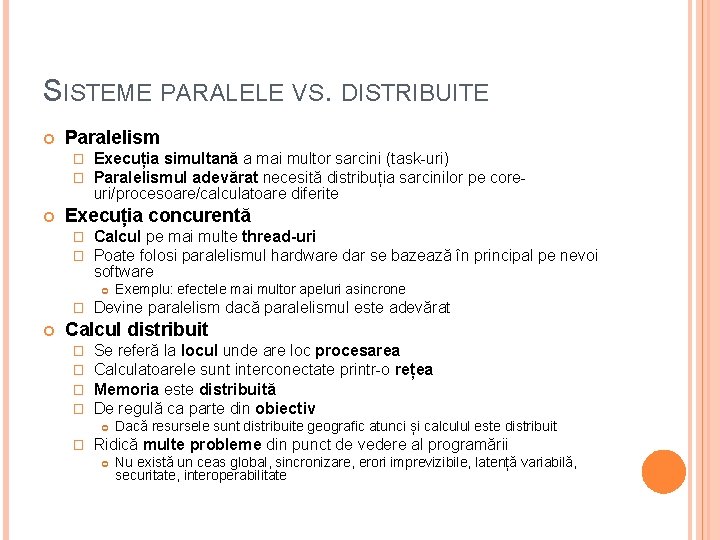

SISTEME PARALELE VS. DISTRIBUITE Paralelism � � Execuția simultană a mai multor sarcini (task-uri) Paralelismul adevărat necesită distribuția sarcinilor pe coreuri/procesoare/calculatoare diferite Execuția concurentă � � Calcul pe mai multe thread-uri Poate folosi paralelismul hardware dar se bazează în principal pe nevoi software � Exemplu: efectele mai multor apeluri asincrone Devine paralelism dacă paralelismul este adevărat Calcul distribuit � � Se referă la locul unde are loc procesarea Calculatoarele sunt interconectate printr-o rețea Memoria este distribuită De regulă ca parte din obiectiv � Dacă resursele sunt distribuite geografic atunci și calculul este distribuit Ridică multe probleme din punct de vedere al programării Nu există un ceas global, sincronizare, erori imprevizibile, latență variabilă, securitate, interoperabilitate

MODELE ALE SISTEMELOR DISTRIBUITE Minicalculator Stație de lucru – server Pool de procesoare Cluster Grid Cloud

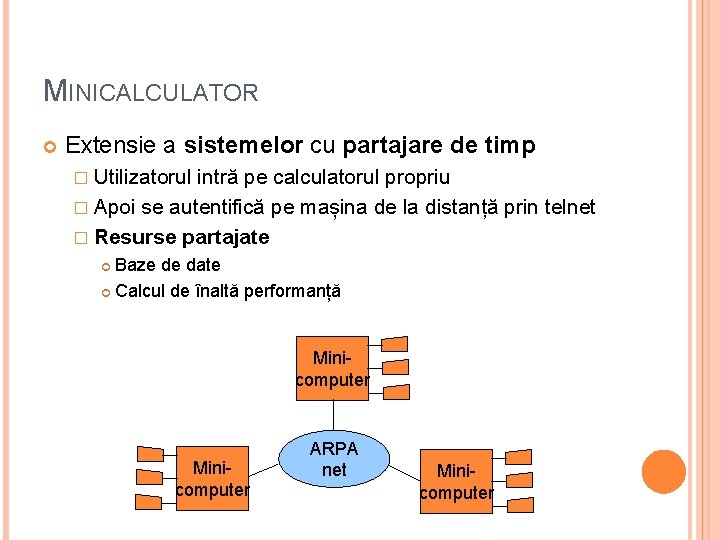

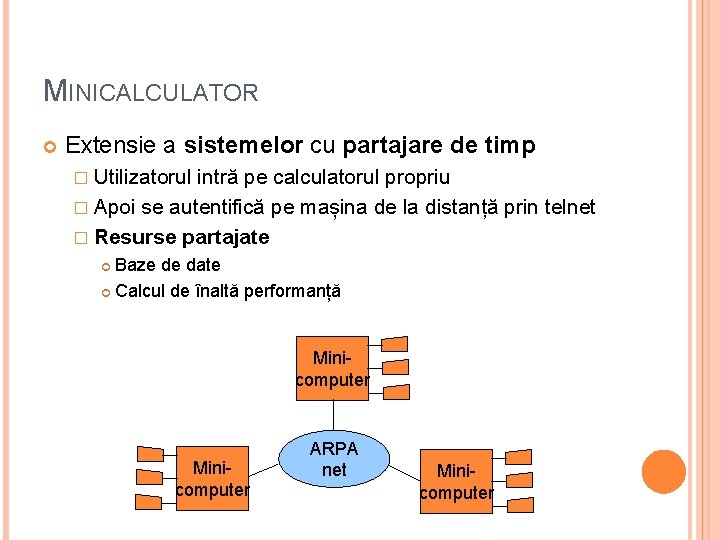

MINICALCULATOR Extensie a sistemelor cu partajare de timp � Utilizatorul intră pe calculatorul propriu � Apoi se autentifică pe mașina de la distanță prin telnet � Resurse partajate Baze de date Calcul de înaltă performanță Minicomputer ARPA net Minicomputer

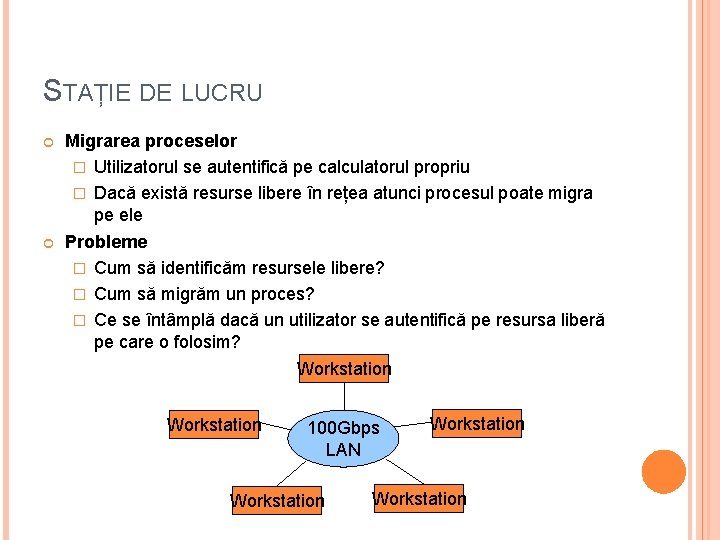

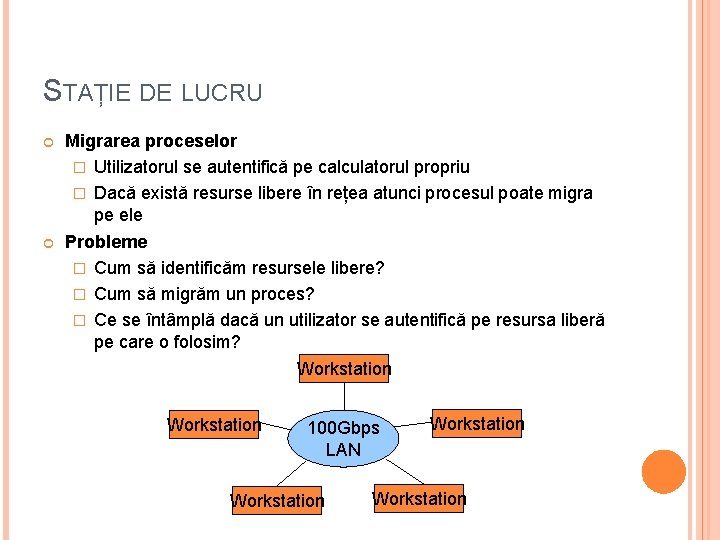

STAȚIE DE LUCRU Migrarea proceselor � Utilizatorul se autentifică pe calculatorul propriu � Dacă există resurse libere în rețea atunci procesul poate migra pe ele Probleme � Cum să identificăm resursele libere? � Cum să migrăm un proces? � Ce se întâmplă dacă un utilizator se autentifică pe resursa liberă pe care o folosim? Workstation 100 Gbps LAN Workstation

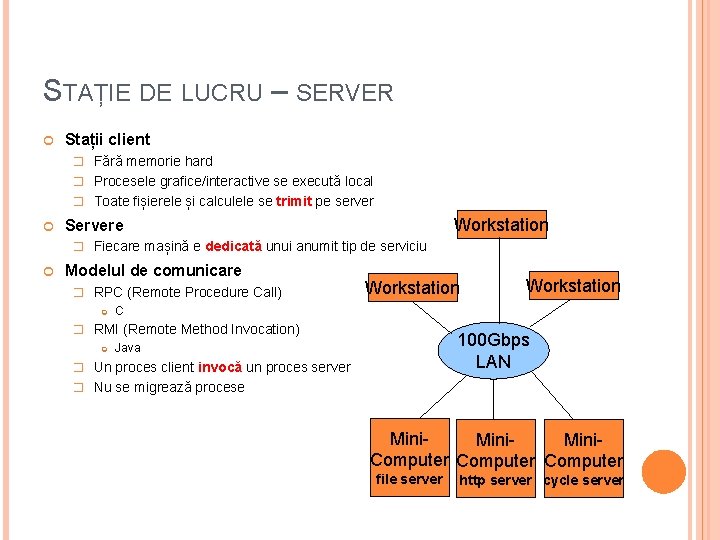

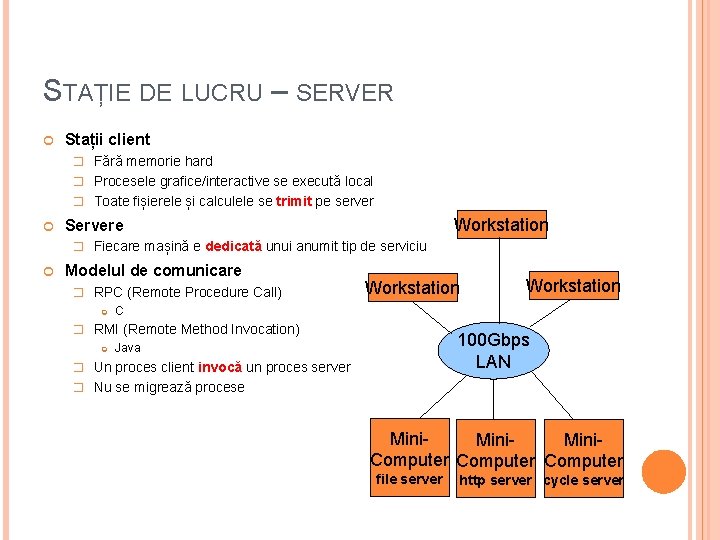

STAȚIE DE LUCRU – SERVER Stații client � Fără memorie hard � Procesele grafice/interactive se execută local � Toate fișierele și calculele se trimit pe server Workstation Servere � Fiecare mașină e dedicată unui anumit tip de serviciu Modelul de comunicare � RPC (Remote Procedure Call) Workstation C � RMI (Remote Method Invocation) Workstation 100 Gbps LAN Java � Un proces client invocă un proces server � Nu se migrează procese Mini. Computer file server http server cycle server

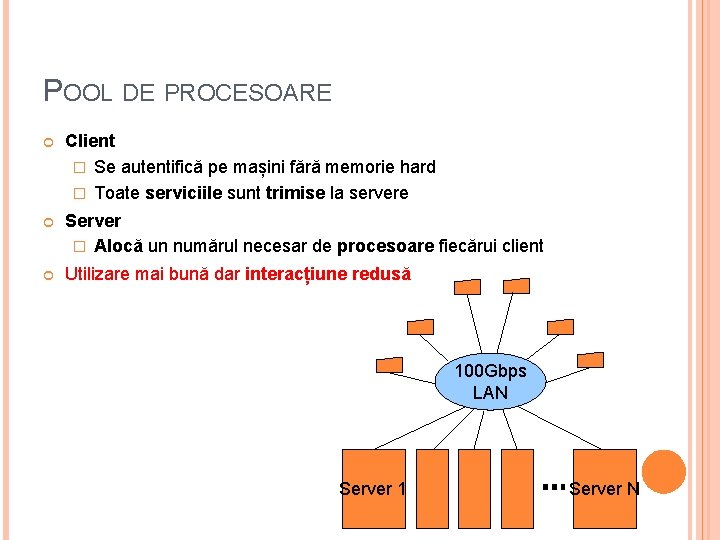

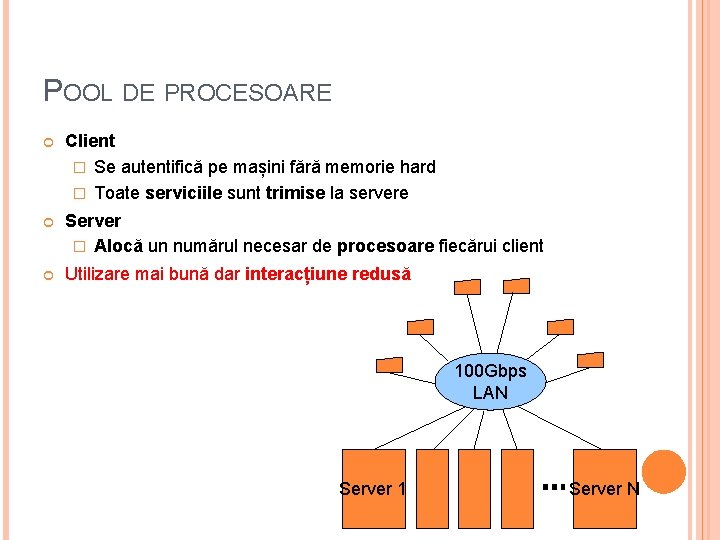

POOL DE PROCESOARE Client � Se autentifică pe mașini fără memorie hard � Toate serviciile sunt trimise la servere Server � Alocă un numărul necesar de procesoare fiecărui client Utilizare mai bună dar interacțiune redusă 100 Gbps LAN Server 1 Server N

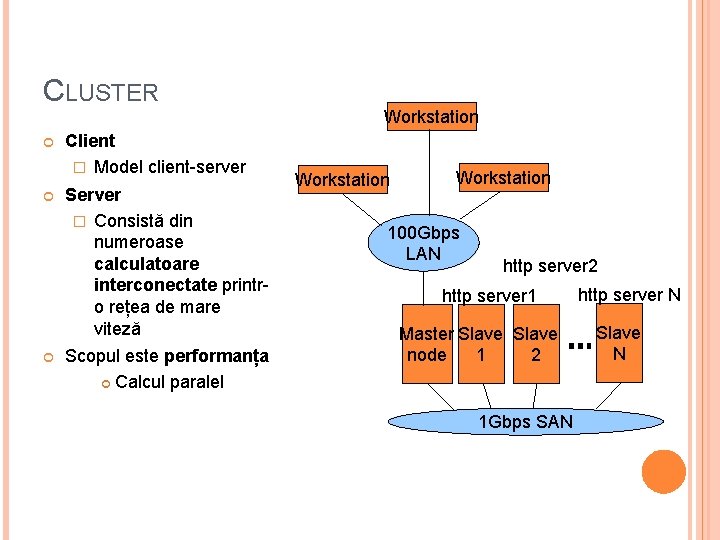

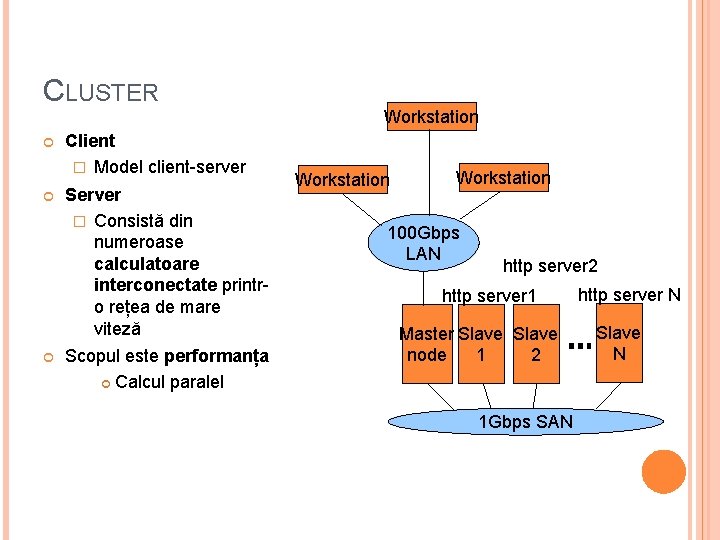

CLUSTER Client � Model client-server Server � Consistă din numeroase calculatoare interconectate printro rețea de mare viteză Scopul este performanța Calcul paralel Workstation 100 Gbps LAN http server 2 http server 1 Master Slave node 1 2 1 Gbps SAN http server N Slave N

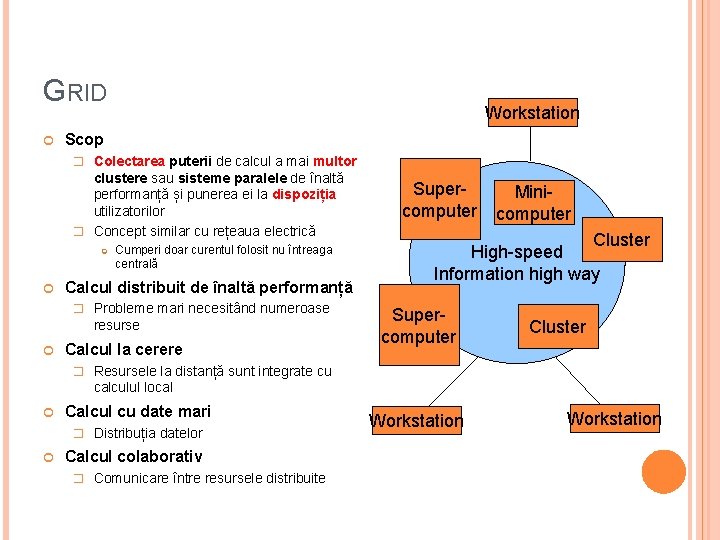

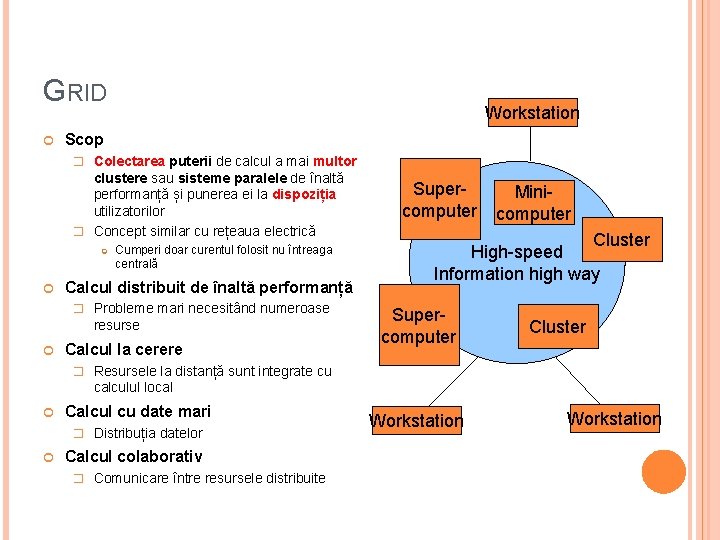

GRID Workstation Scop � Colectarea puterii de calcul a mai multor clustere sau sisteme paralele de înaltă performanță și punerea ei la dispoziția utilizatorilor � Concept similar cu rețeaua electrică Cumperi doar curentul folosit nu întreaga centrală Calcul distribuit de înaltă performanță � Probleme mari necesitând numeroase resurse Calcul la cerere Supercomputer Minicomputer Cluster High-speed Information high way Supercomputer Cluster � Resursele la distanță sunt integrate cu calculul local Calcul cu date mari � Distribuția datelor Calcul colaborativ � Comunicare între resursele distribuite Workstation

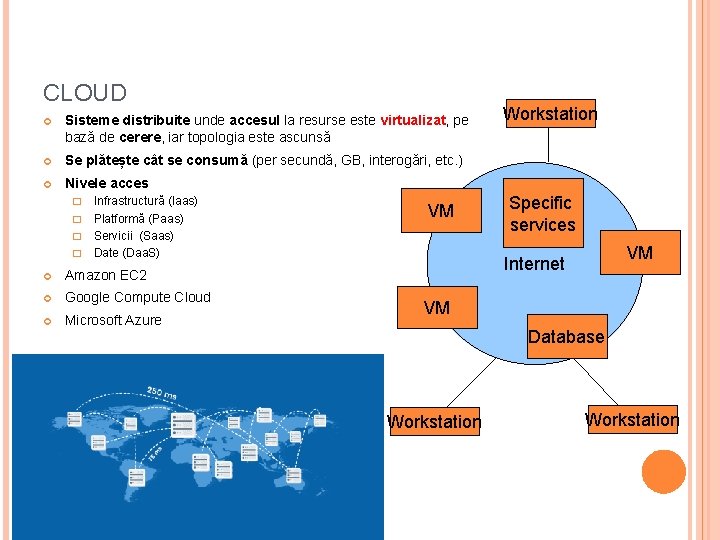

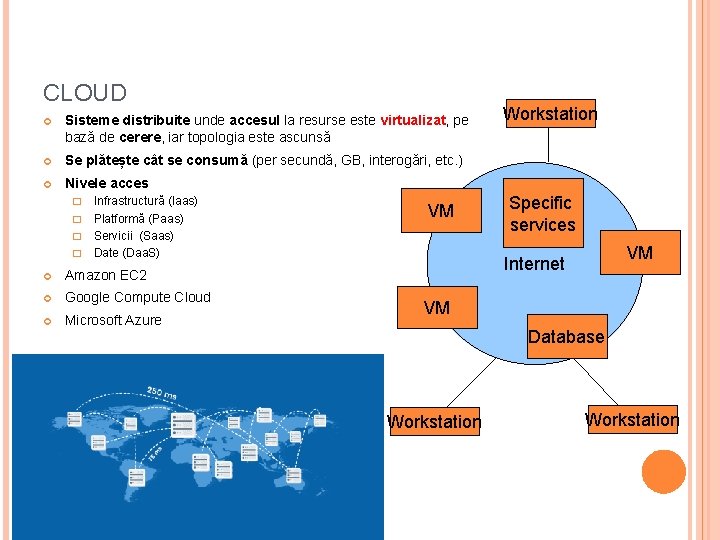

CLOUD Sisteme distribuite unde accesul la resurse este virtualizat, pe bază de cerere, iar topologia este ascunsă Se plătește cât se consumă (per secundă, GB, interogări, etc. ) Nivele acces Infrastructură (Iaas) � Platformă (Paas) � Servicii (Saas) � Date (Daa. S) � Amazon EC 2 Google Compute Cloud Microsoft Azure VM Workstation Specific services VM Internet VM Database Workstation

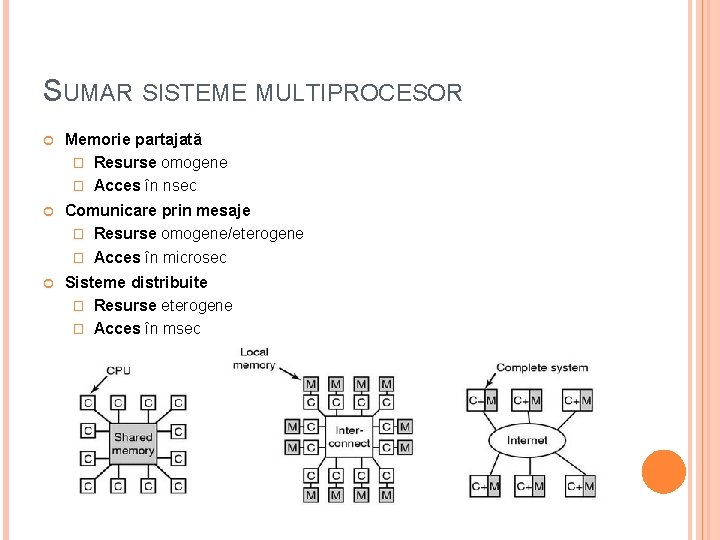

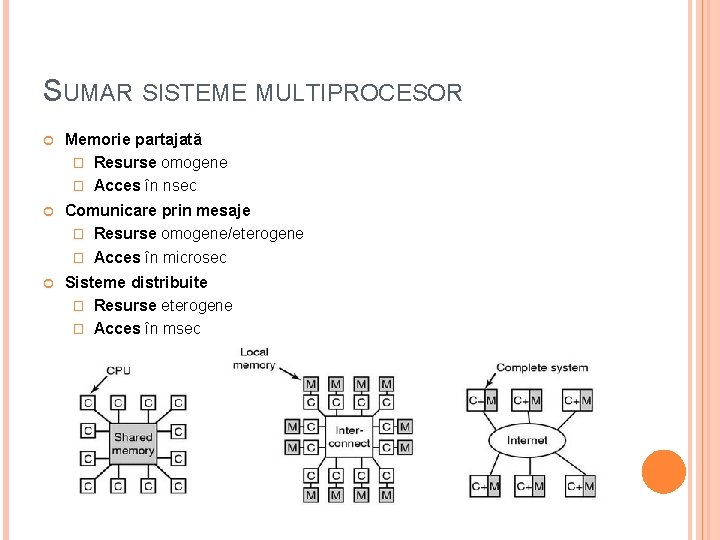

SUMAR SISTEME MULTIPROCESOR Memorie partajată � Resurse omogene � Acces în nsec Comunicare prin mesaje � Resurse omogene/eterogene � Acces în microsec Sisteme distribuite � Resurse eterogene � Acces în msec

SURSE CURS http: //slideplayer. com/slide/5704113/ https: //www. comsol. com/blogs/havent-cpu-clock-speedsincreased-last-years/ http: //www. inf. ed. ac. uk/teaching/courses/pa/Notes/lectur e 01 -intro. pdf https: //www. slideshare. net/Dilum. Bandara/11 performance-enhancements http: //wgropp. cs. illinois. edu/courses/cs 598 s 16/lectures/lecture 15. pdf http: //www. ni. com/white-paper/11266/en/ https: //www. cs. virginia. edu/~skadron/cs 433_s 09_proces sors/arm 11. pdf http: //www. csie. nuk. edu. tw/~wuch/course/eef 011/4 p/eef 011 -6. pdf

CURSUL VIITOR Tehnici de paralelizare a algoritmilor API-uri și platforme software pentru calculul paralel și distribuit � Open. MP � MPI � Uniform Parallel C � CUDA � Hadoop