Paul Scherrer Institute Stefan Ritt Limiting factors in

![-3 db Bandwidth [GHz] Influence of write switch • Write switch has a finite -3 db Bandwidth [GHz] Influence of write switch • Write switch has a finite](https://slidetodoc.com/presentation_image_h/b30de7dbb85e4a218973cd74b646de90/image-15.jpg)

- Slides: 34

Paul Scherrer Institute Stefan Ritt Limiting factors in Switched Capacitor Arrays Sampling speed, Timing accuracy, Readout speed Timing Workshop, Chicago April 28 th, 2011

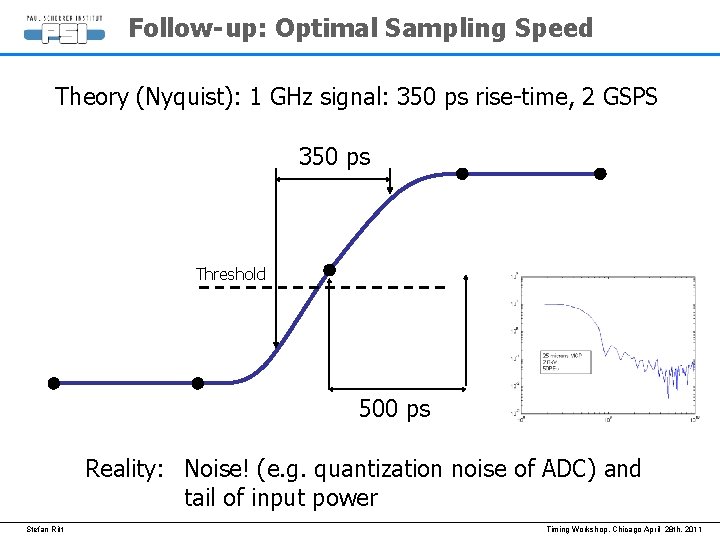

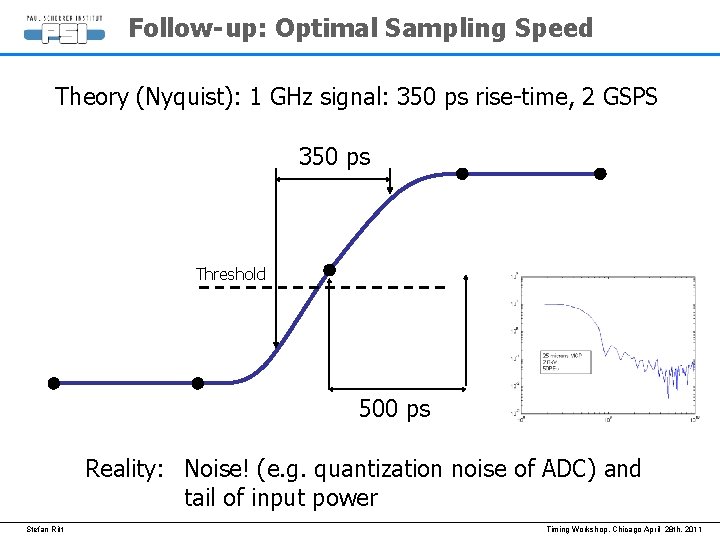

Follow-up: Optimal Sampling Speed Theory (Nyquist): 1 GHz signal: 350 ps rise-time, 2 GSPS 350 ps Threshold 500 ps Reality: Noise! (e. g. quantization noise of ADC) and tail of input power Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

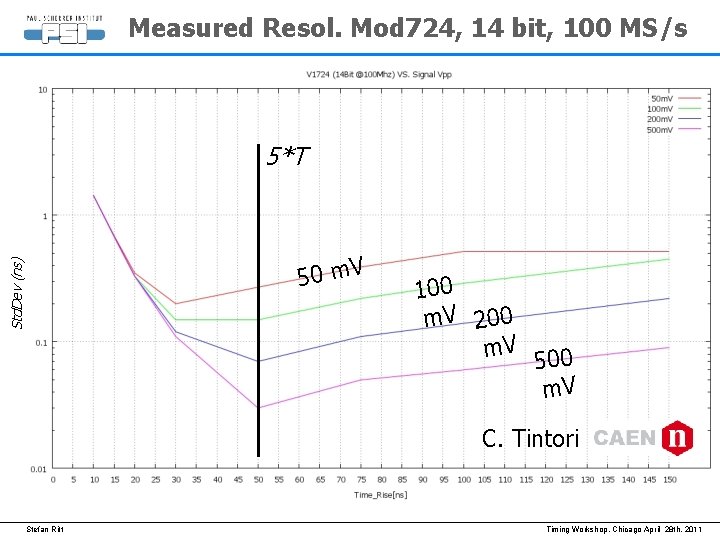

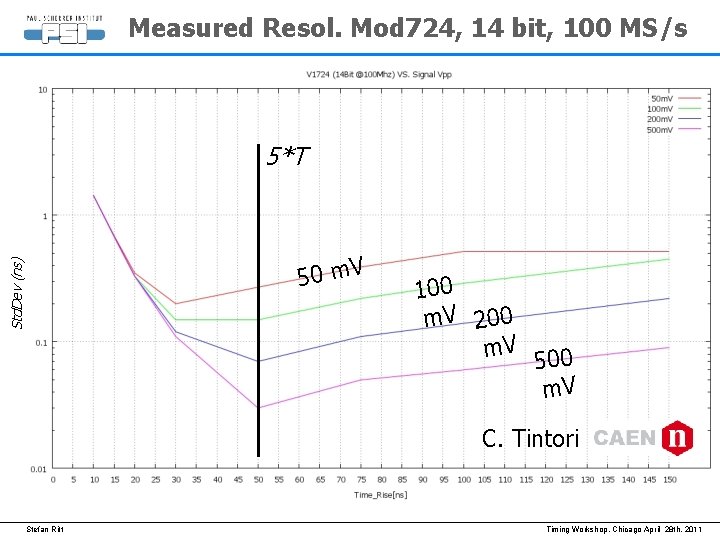

Measured Resol. Mod 724, 14 bit, 100 MS/s 5*T Std. Dev (ns) 50 m. V 100 m. V 200 m. V 500 m. V C. Tintori Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

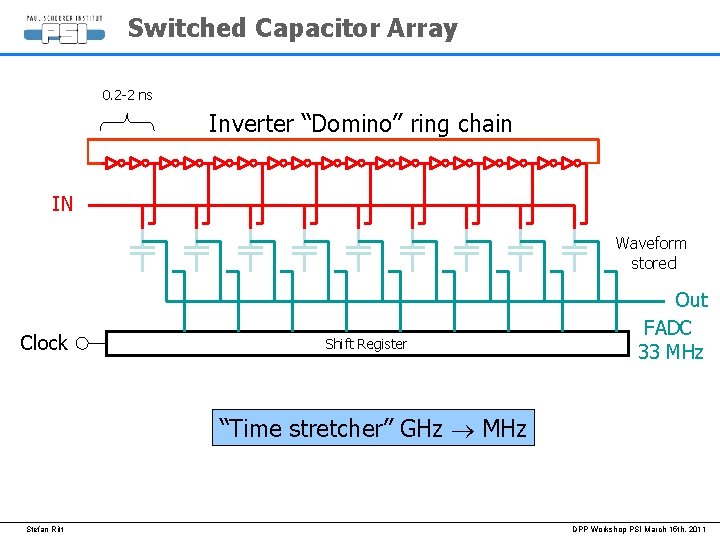

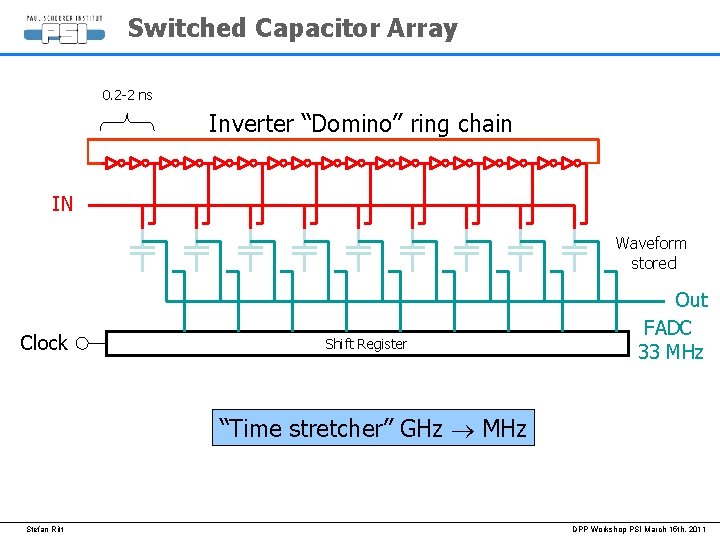

Switched Capacitor Array 0. 2 -2 ns Inverter “Domino” ring chain IN Waveform stored Clock Shift Register Out FADC 33 MHz “Time stretcher” GHz MHz Stefan Ritt DPP Workshop PSI March 15 th, 2011

Limits on sampling speed vs. technology Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

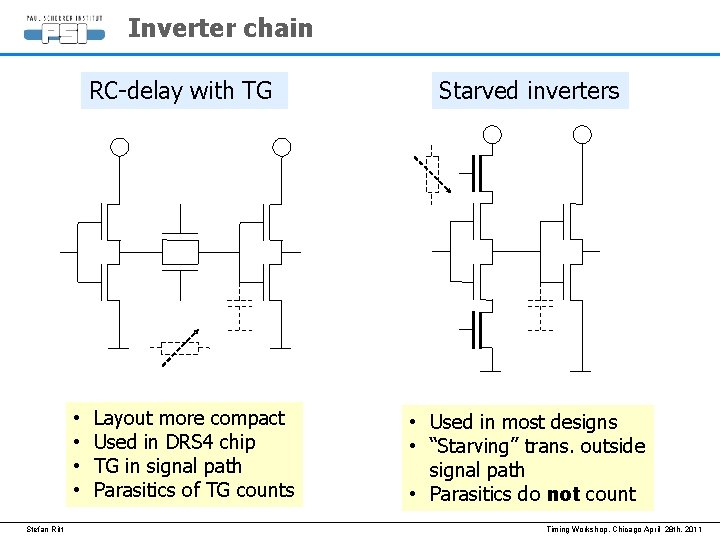

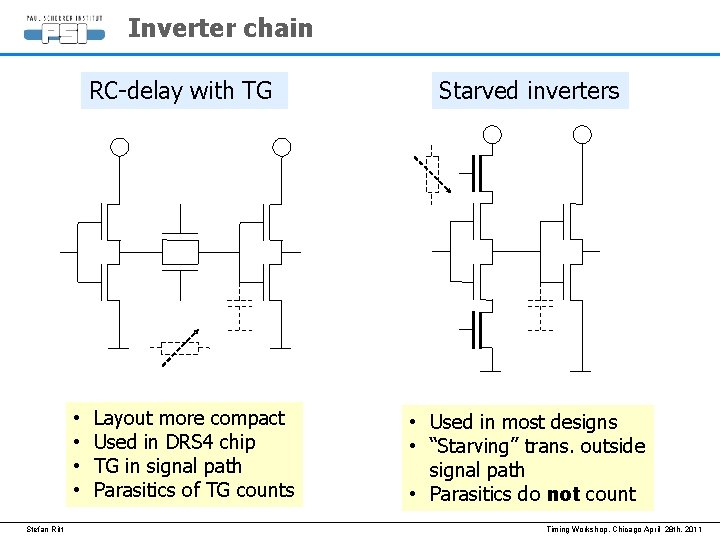

Inverter chain RC-delay with TG • • Stefan Ritt Layout more compact Used in DRS 4 chip TG in signal path Parasitics of TG counts Starved inverters • Used in most designs • “Starving” trans. outside signal path • Parasitics do not count Timing Workshop, Chicago April 28 th, 2011

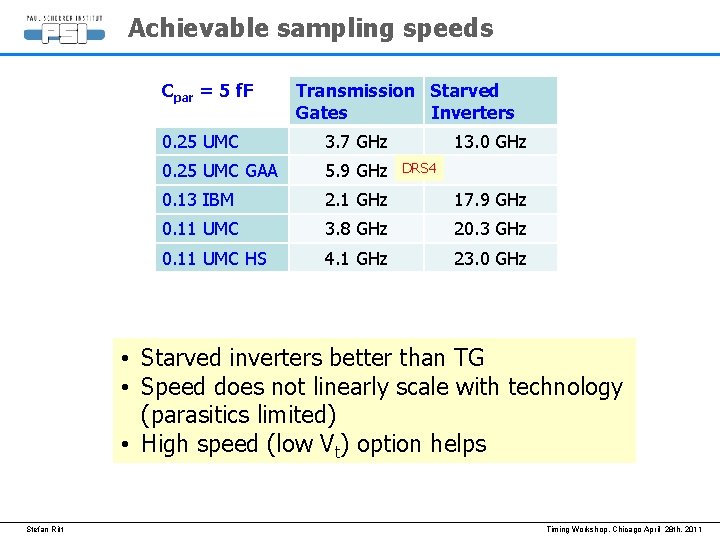

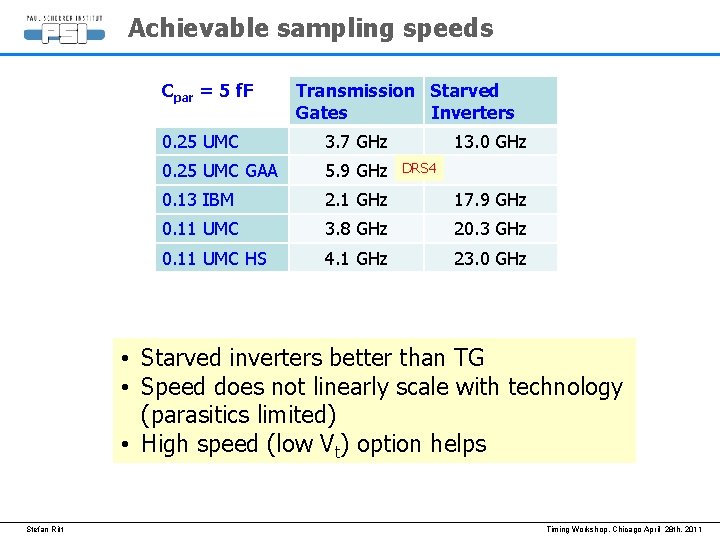

Achievable sampling speeds Cpar = 5 f. F Transmission Starved Gates Inverters 0. 25 UMC 3. 7 GHz 13. 0 GHz 0. 25 UMC GAA 5. 9 GHz 0. 13 IBM 2. 1 GHz 17. 9 GHz 0. 11 UMC 3. 8 GHz 20. 3 GHz 0. 11 UMC HS 4. 1 GHz 23. 0 GHz DRS 4 • Starved inverters better than TG • Speed does not linearly scale with technology (parasitics limited) • High speed (low Vt) option helps Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

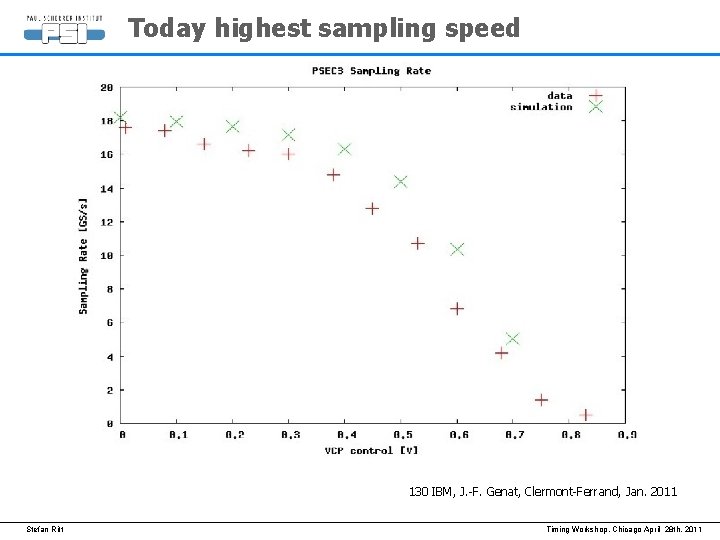

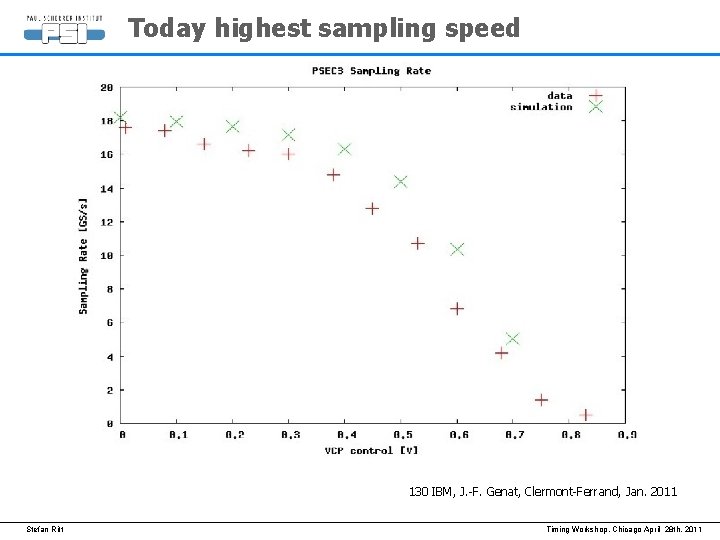

Today highest sampling speed 130 IBM, J. -F. Genat, Clermont-Ferrand, Jan. 2011 Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

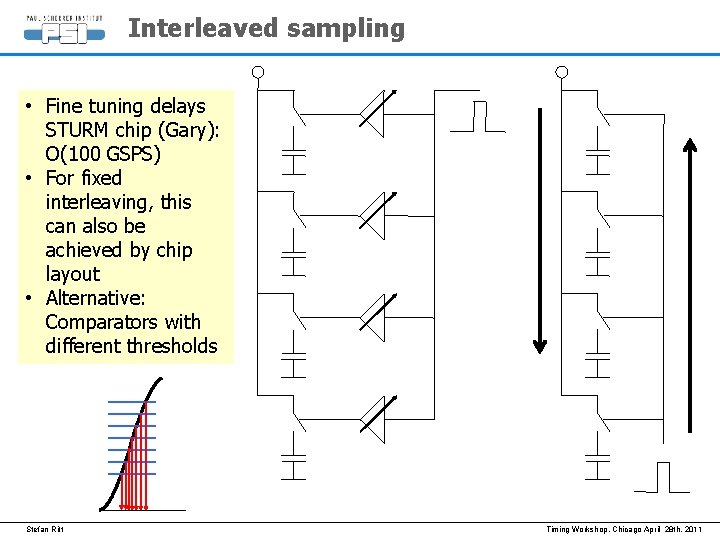

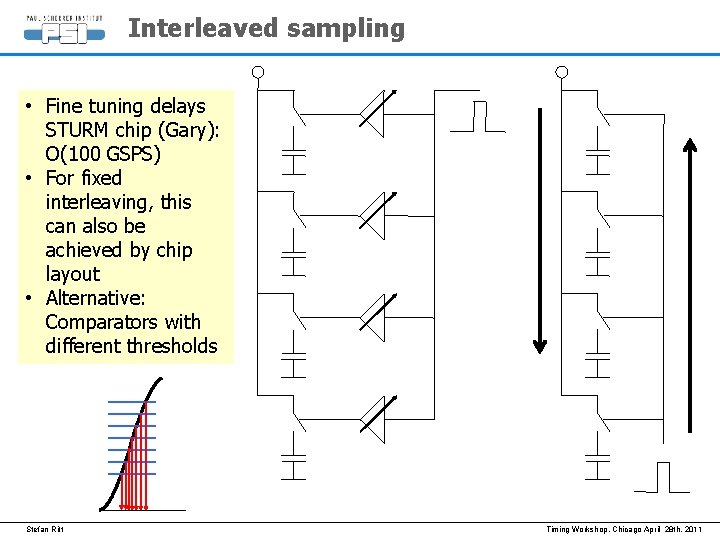

Interleaved sampling • Fine tuning delays STURM chip (Gary): O(100 GSPS) • For fixed interleaving, this can also be achieved by chip layout • Alternative: Comparators with different thresholds Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

Limits on analog bandwidth Parasitics, bond wires, Ron of sampling cell Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

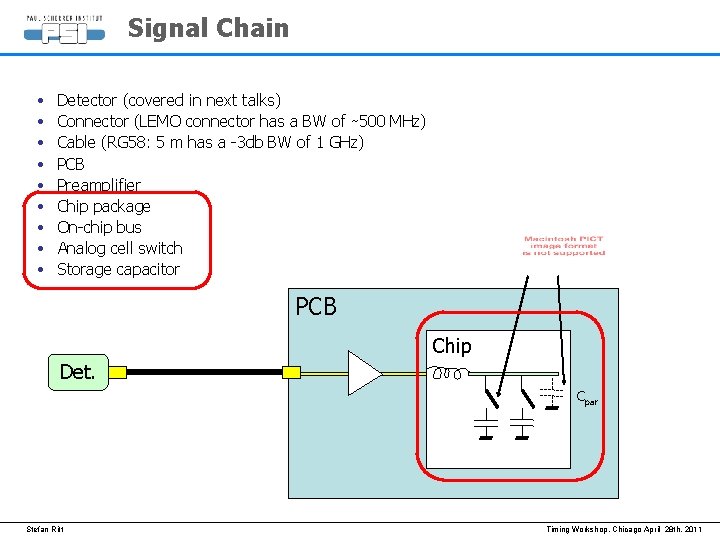

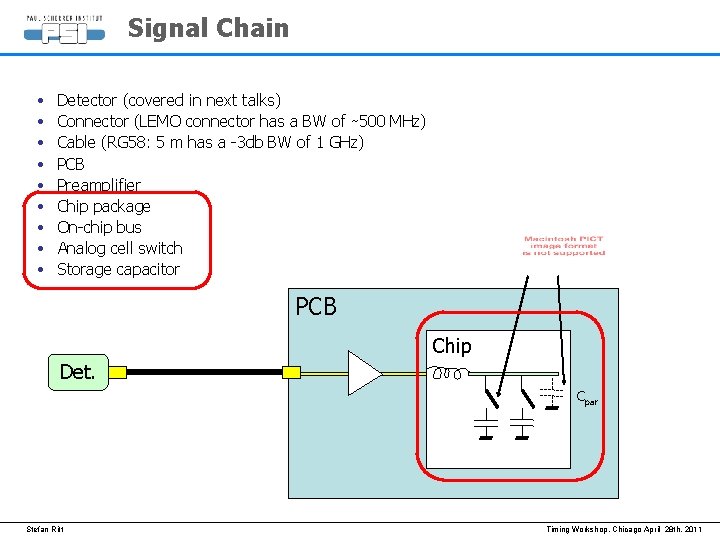

Signal Chain • • • Detector (covered in next talks) Connector (LEMO connector has a BW of ∼ 500 MHz) Cable (RG 58: 5 m has a -3 db BW of 1 GHz) PCB Preamplifier Chip package On-chip bus Analog cell switch Storage capacitor PCB Chip Det. Cpar Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

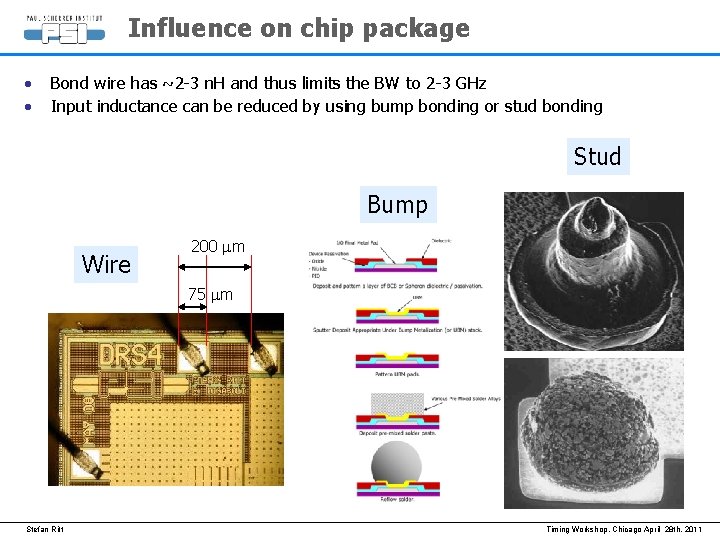

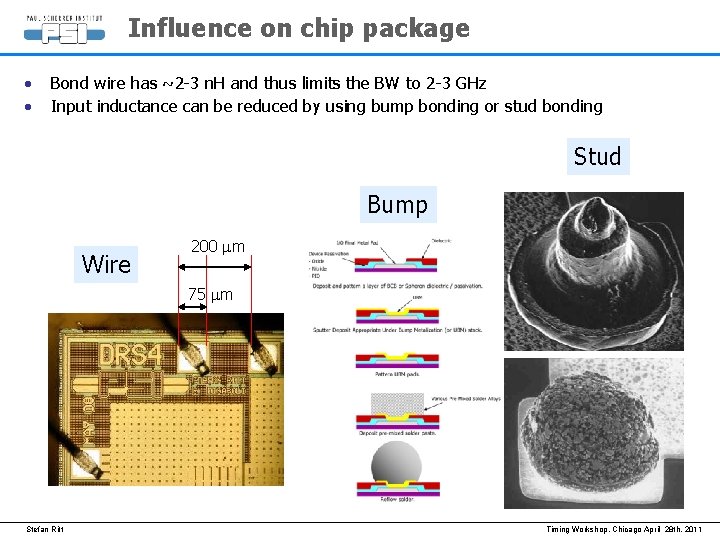

Influence on chip package • • Bond wire has ~2 -3 n. H and thus limits the BW to 2 -3 GHz Input inductance can be reduced by using bump bonding or stud bonding Stud Bump Wire 200 mm 75 mm Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

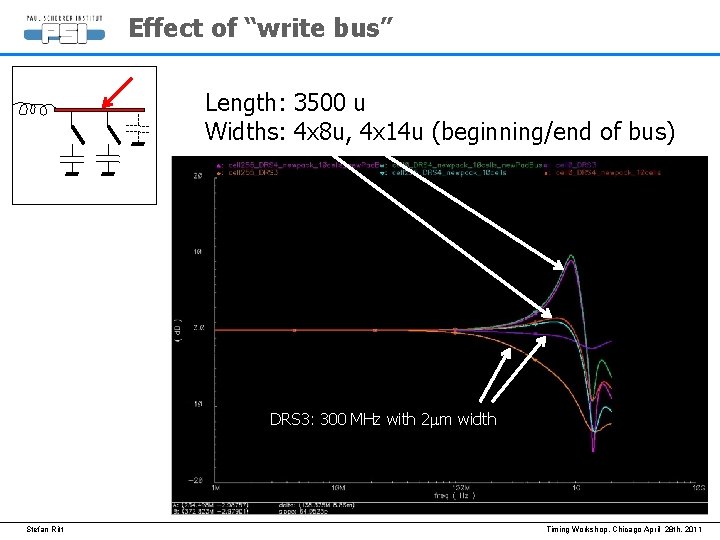

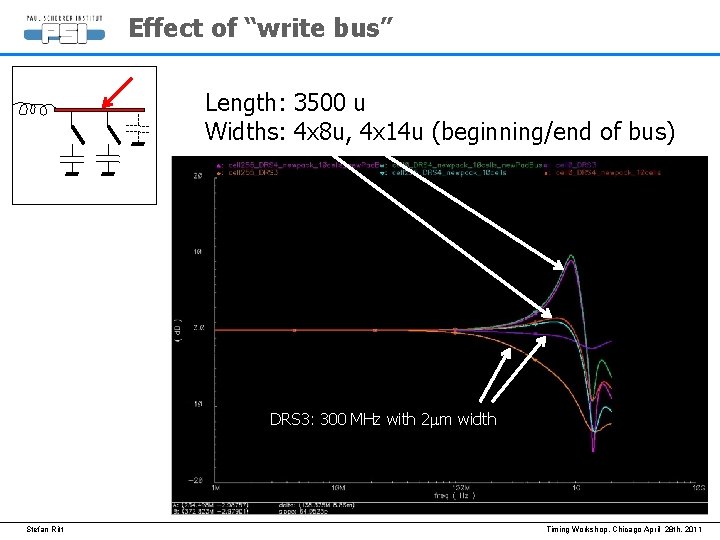

Effect of “write bus” Length: 3500 u Widths: 4 x 8 u, 4 x 14 u (beginning/end of bus) DRS 3: 300 MHz with 2 mm width Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

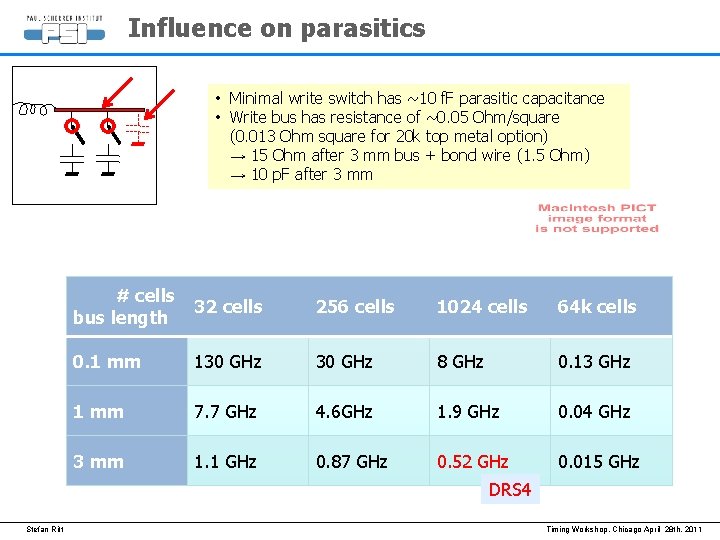

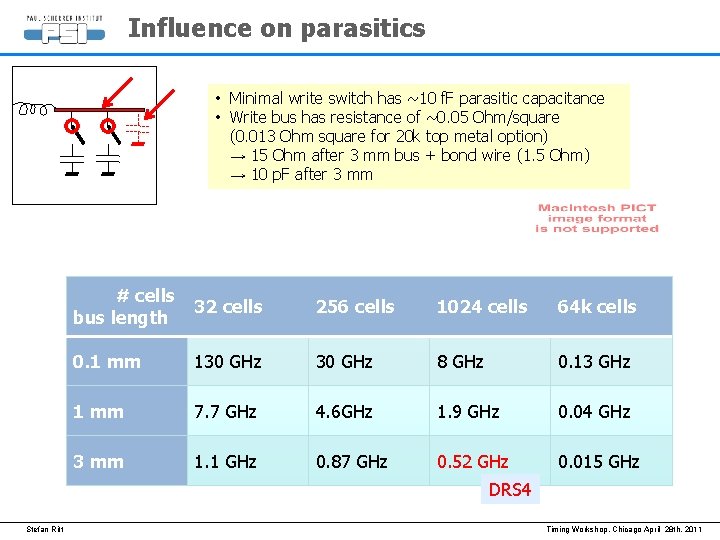

Influence on parasitics • Minimal write switch has ~10 f. F parasitic capacitance • Write bus has resistance of ~0. 05 Ohm/square (0. 013 Ohm square for 20 k top metal option) → 15 Ohm after 3 mm bus + bond wire (1. 5 Ohm) → 10 p. F after 3 mm # cells bus length 32 cells 256 cells 1024 cells 64 k cells 0. 1 mm 130 GHz 8 GHz 0. 13 GHz 1 mm 7. 7 GHz DRS 3: 4. 6 GHz 300 MHz with 2 u 1. 9 width 0. 04 GHz 3 mm 1. 1 GHz 0. 015 GHz 0. 87 GHz 0. 52 GHz DRS 4 Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

![3 db Bandwidth GHz Influence of write switch Write switch has a finite -3 db Bandwidth [GHz] Influence of write switch • Write switch has a finite](https://slidetodoc.com/presentation_image_h/b30de7dbb85e4a218973cd74b646de90/image-15.jpg)

-3 db Bandwidth [GHz] Influence of write switch • Write switch has a finite “on” resistance • Storage cap needs to be >10 f. F for reasonable k. TC noise • Leakage current requires even bigger C wopt. ~ 6 um • Simulation • Cstore = 50 f. F • UMC 0. 25 um technology • Vdd = 2. 5 V • Minimal l • W = 0. 25 um * N • Note: N>1 adds parasitic to write bus! Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

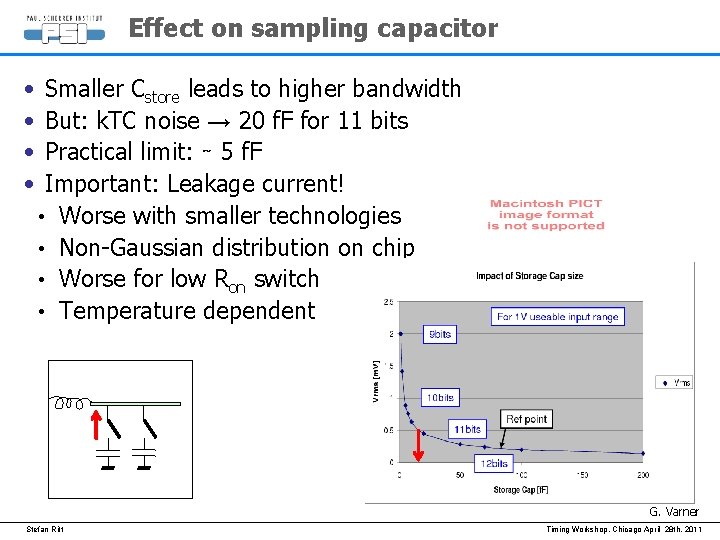

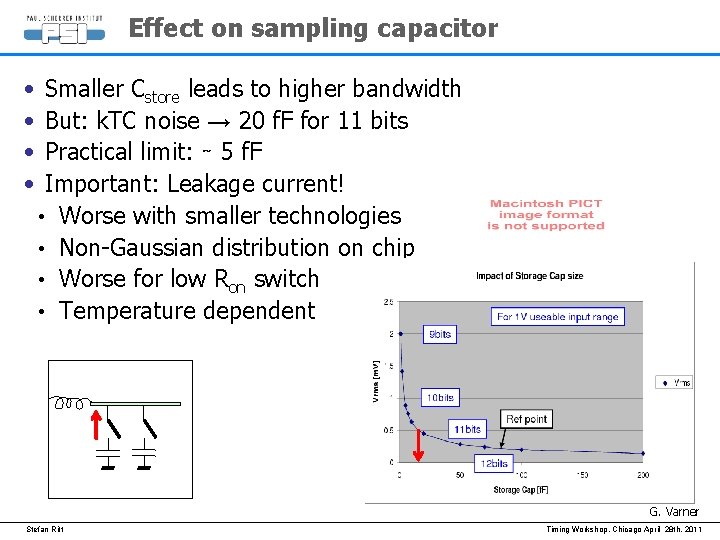

Effect on sampling capacitor • • Smaller Cstore leads to higher bandwidth But: k. TC noise → 20 f. F for 11 bits Practical limit: ∼ 5 f. F Important: Leakage current! • Worse with smaller technologies • Non-Gaussian distribution on chip • Worse for low Ron switch • Temperature dependent G. Varner Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

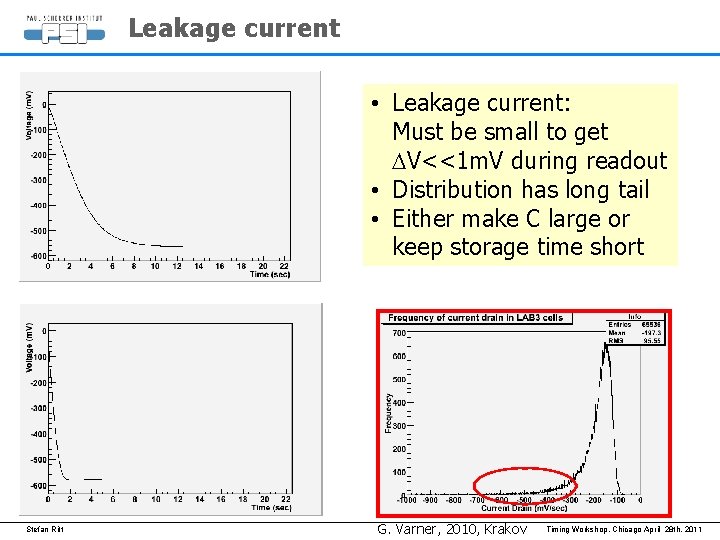

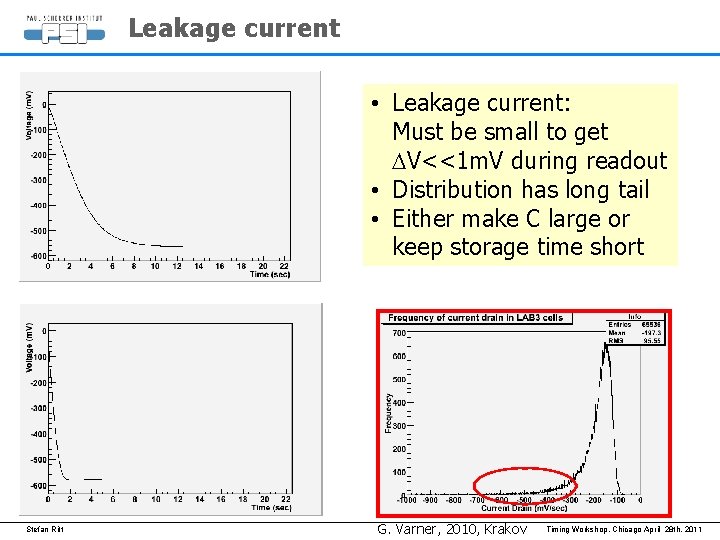

Leakage current • Leakage current: Must be small to get DV<<1 m. V during readout • Distribution has long tail • Either make C large or keep storage time short Stefan Ritt G. Varner, 2010, Krakov Timing Workshop, Chicago April 28 th, 2011

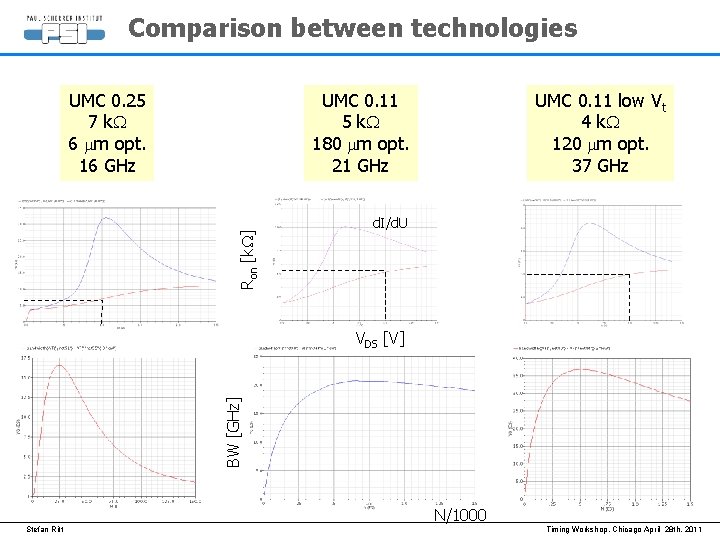

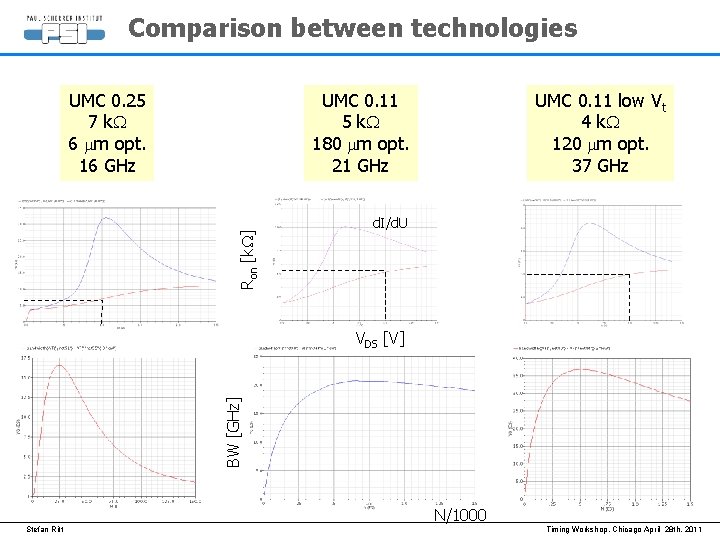

Comparison between technologies UMC 0. 11 5 k. W 180 mm opt. 21 GHz Ron [k. W] UMC 0. 25 7 k. W 6 mm opt. 16 GHz UMC 0. 11 low Vt 4 k. W 120 mm opt. 37 GHz d. I/d. U BW [GHz] VDS [V] N/1000 Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

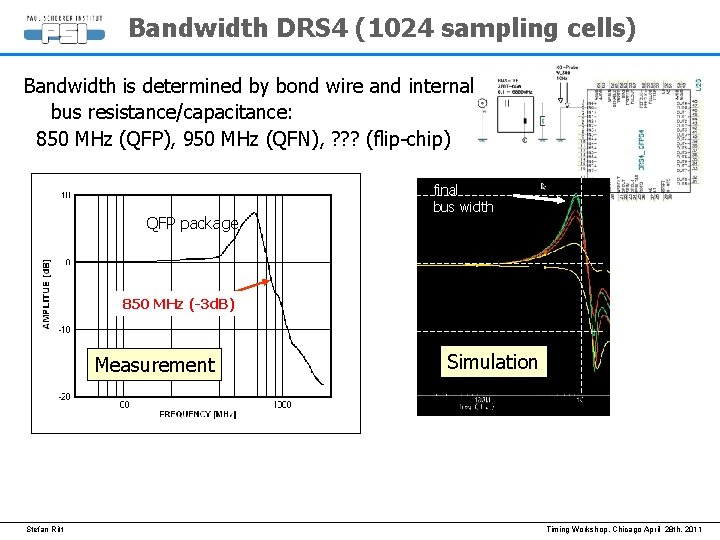

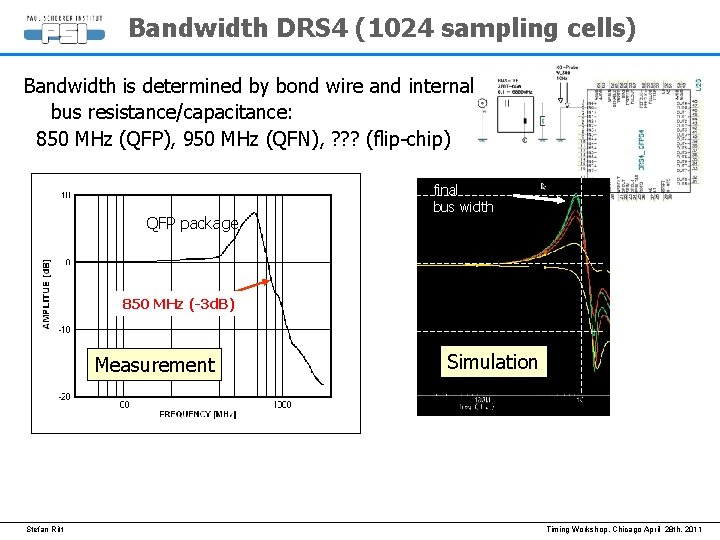

Bandwidth DRS 4 (1024 sampling cells) Bandwidth is determined by bond wire and internal bus resistance/capacitance: 850 MHz (QFP), 950 MHz (QFN), ? ? ? (flip-chip) QFP package final bus width 850 MHz (-3 d. B) Measurement Stefan Ritt Simulation Timing Workshop, Chicago April 28 th, 2011

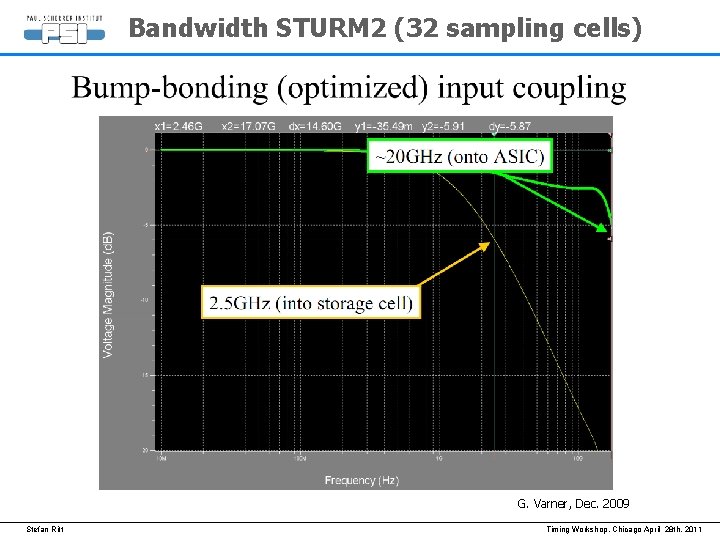

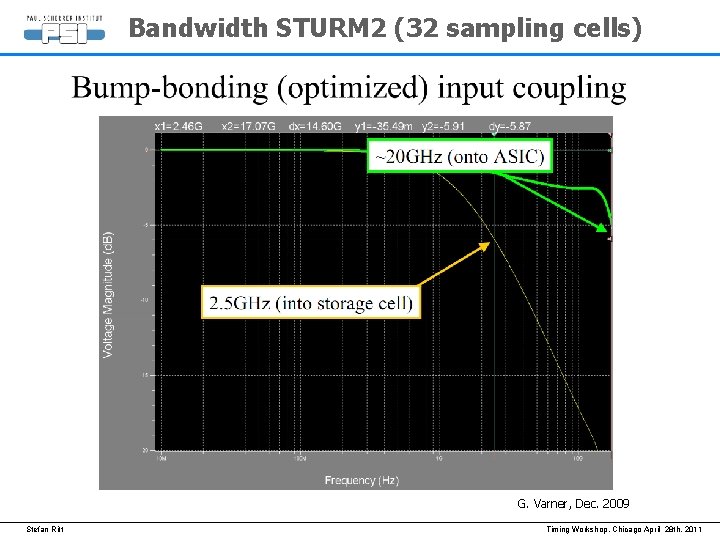

Bandwidth STURM 2 (32 sampling cells) G. Varner, Dec. 2009 Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

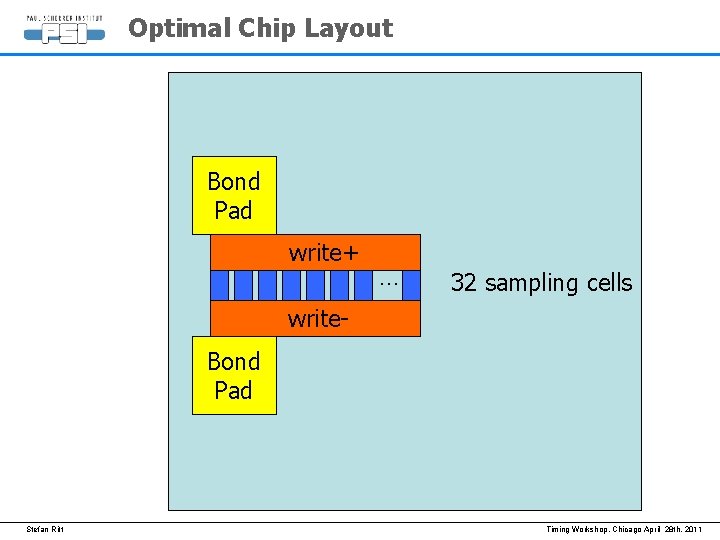

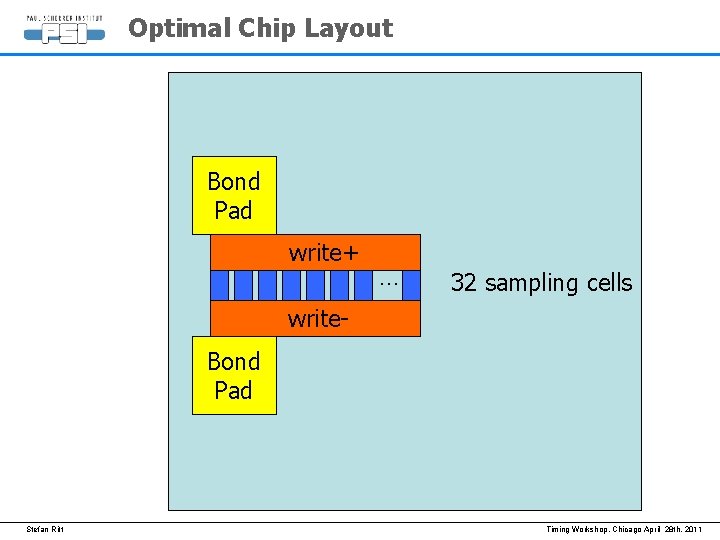

Optimal Chip Layout Bond Pad write+ … 32 sampling cells write. Bond Pad Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

Limits on timing resolution Matching – PLL phase jitter – Aperture Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

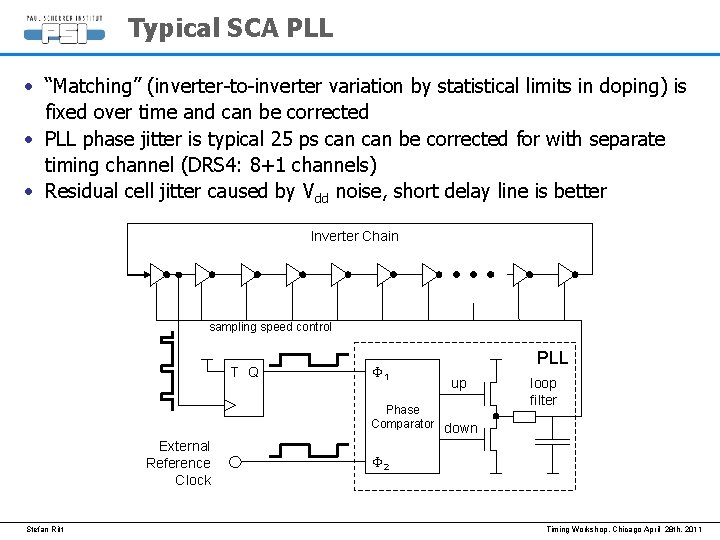

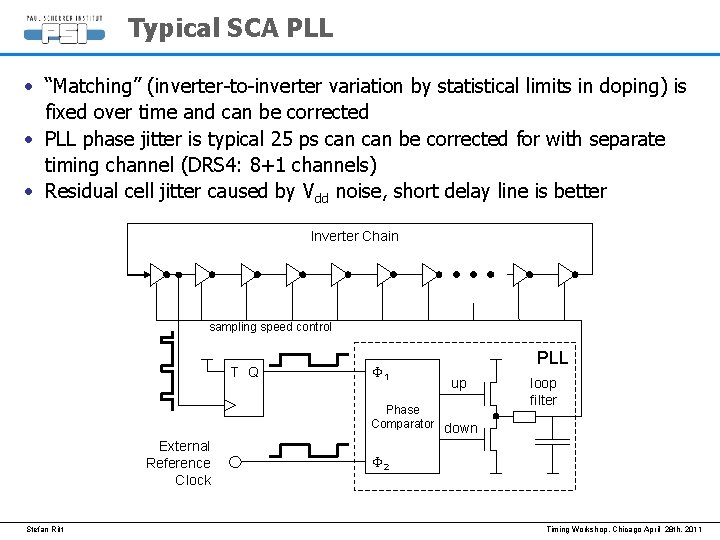

Typical SCA PLL • “Matching” (inverter-to-inverter variation by statistical limits in doping) is fixed over time and can be corrected • PLL phase jitter is typical 25 ps can be corrected for with separate timing channel (DRS 4: 8+1 channels) • Residual cell jitter caused by Vdd noise, short delay line is better Inverter Chain sampling speed control T Q F 1 PLL up Phase Comparator down External Reference Clock Stefan Ritt loop filter F 2 Timing Workshop, Chicago April 28 th, 2011

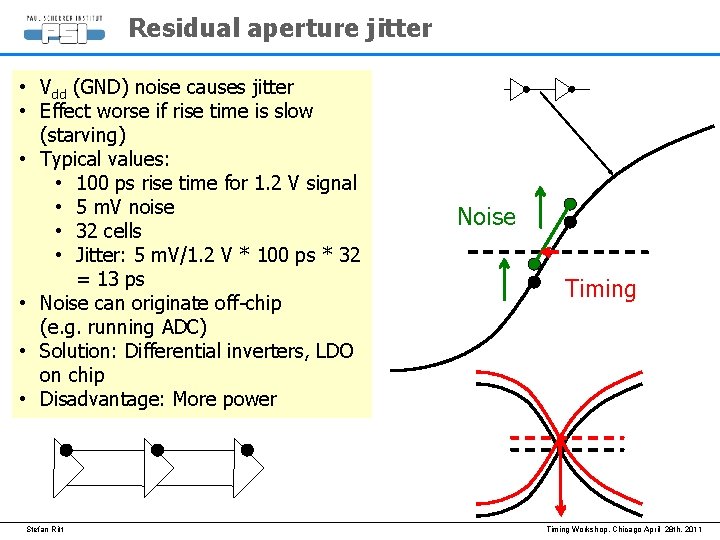

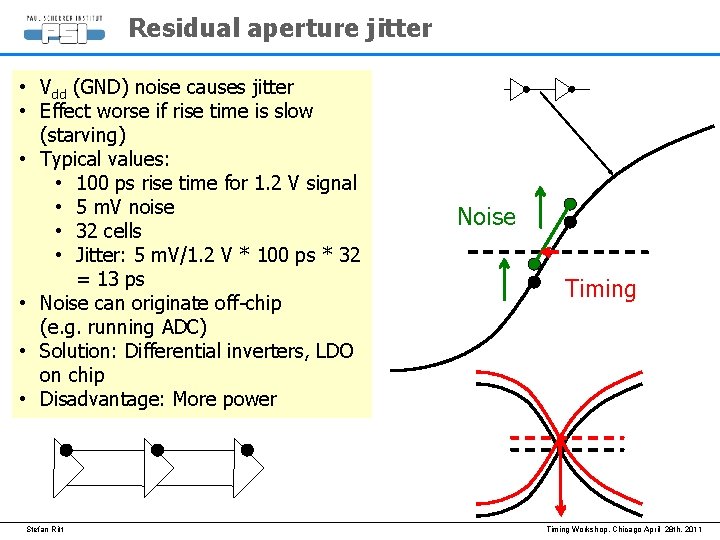

Residual aperture jitter • Vdd (GND) noise causes jitter • Effect worse if rise time is slow (starving) • Typical values: • 100 ps rise time for 1. 2 V signal • 5 m. V noise • 32 cells • Jitter: 5 m. V/1. 2 V * 100 ps * 32 = 13 ps • Noise can originate off-chip (e. g. running ADC) • Solution: Differential inverters, LDO on chip • Disadvantage: More power Stefan Ritt Noise Timing Workshop, Chicago April 28 th, 2011

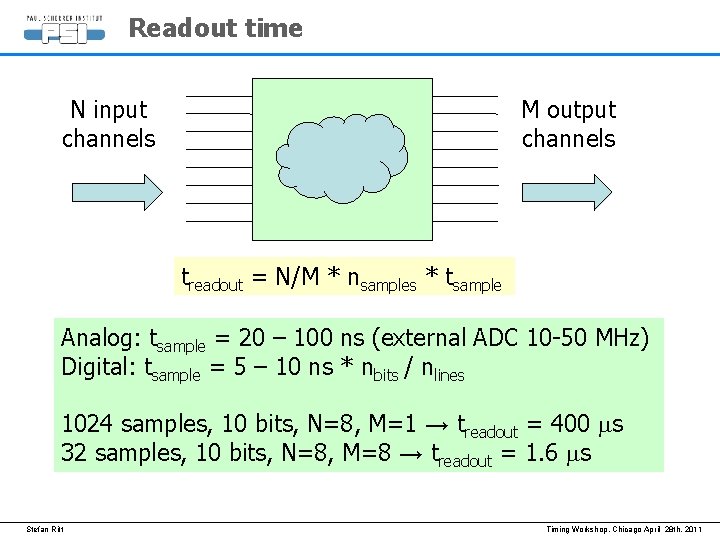

Limits on readout speed Analog-Digital readout, multi-buffer Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

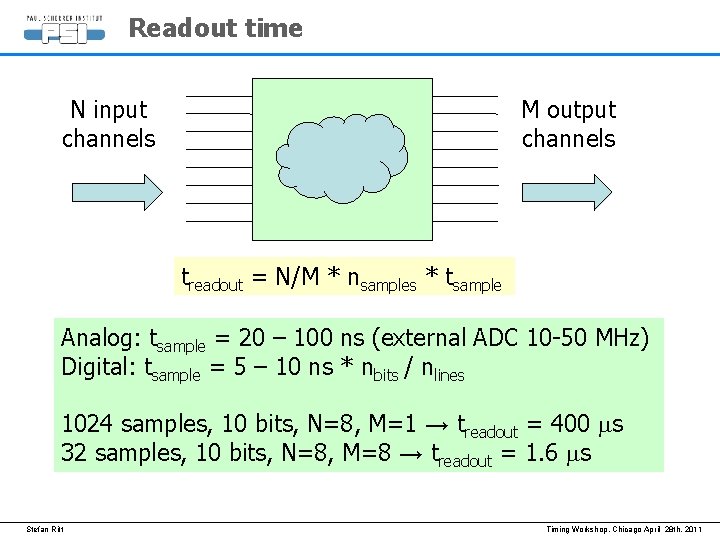

Readout time N input channels M output channels treadout = N/M * nsamples * tsample Analog: tsample = 20 – 100 ns (external ADC 10 -50 MHz) Digital: tsample = 5 – 10 ns * nbits / nlines 1024 samples, 10 bits, N=8, M=1 → treadout = 400 ms 32 samples, 10 bits, N=8, M=8 → treadout = 1. 6 ms Stefan Ritt Timing Workshop, Chicago April 28 th, 2011

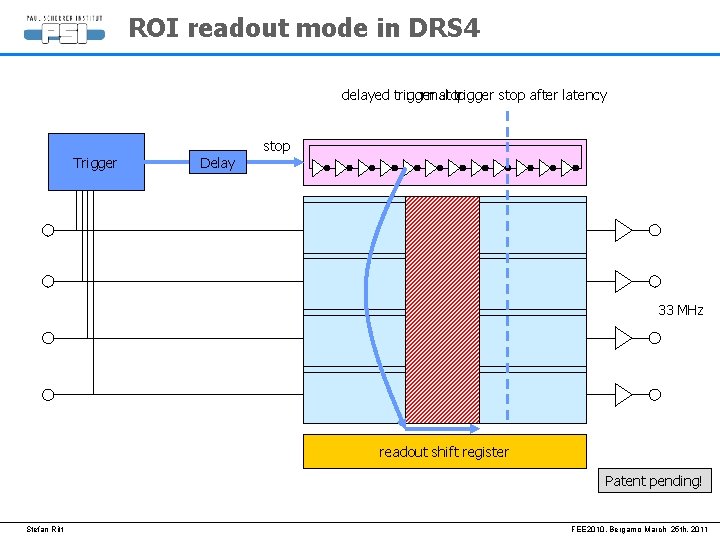

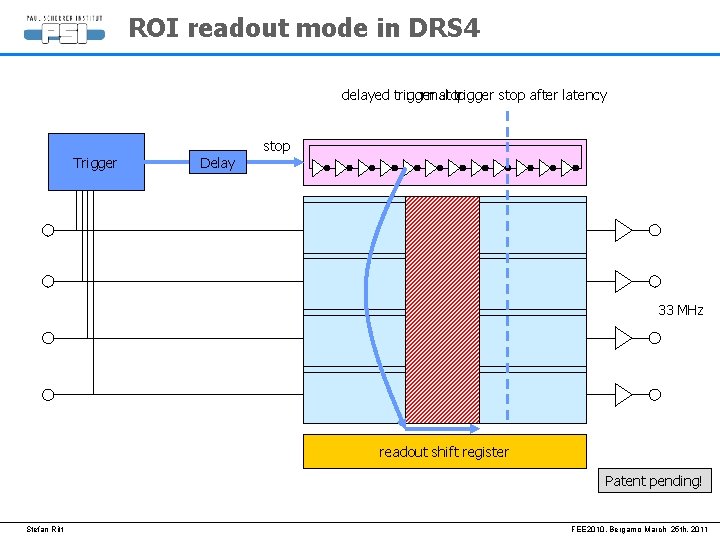

ROI readout mode in DRS 4 delayed trigger normal stop trigger stop after latency Trigger Delay stop 33 MHz readout shift register Patent pending! Stefan Ritt FEE 2010, Bergamo March 25 th, 2011

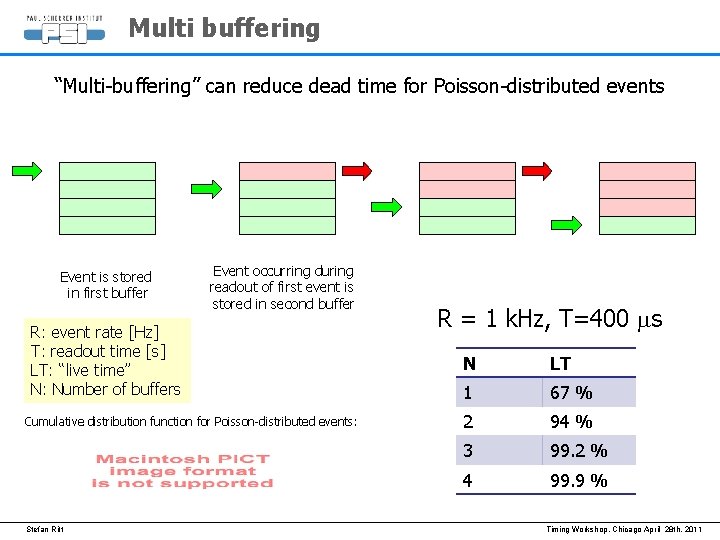

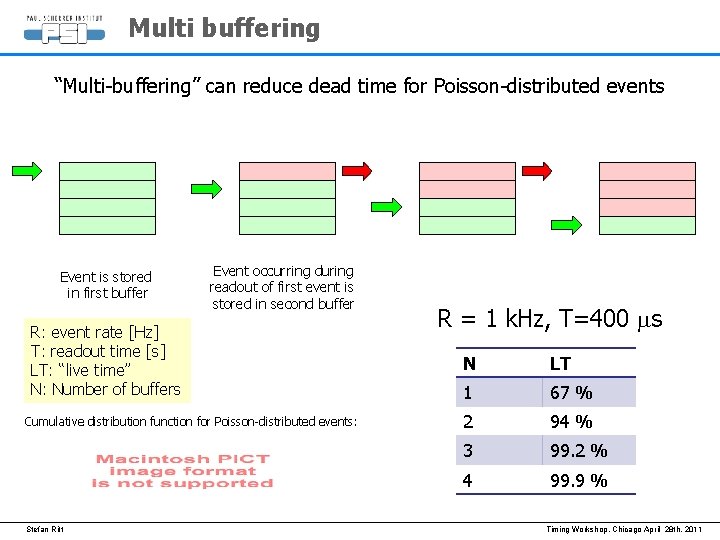

Multi buffering “Multi-buffering” can reduce dead time for Poisson-distributed events Event is stored in first buffer Event occurring during readout of first event is stored in second buffer R: event rate [Hz] T: readout time [s] LT: “live time” N: Number of buffers Cumulative distribution function for Poisson-distributed events: Stefan Ritt R = 1 k. Hz, T=400 ms N LT 1 67 % 2 94 % 3 99. 2 % 4 99. 9 % Timing Workshop, Chicago April 28 th, 2011

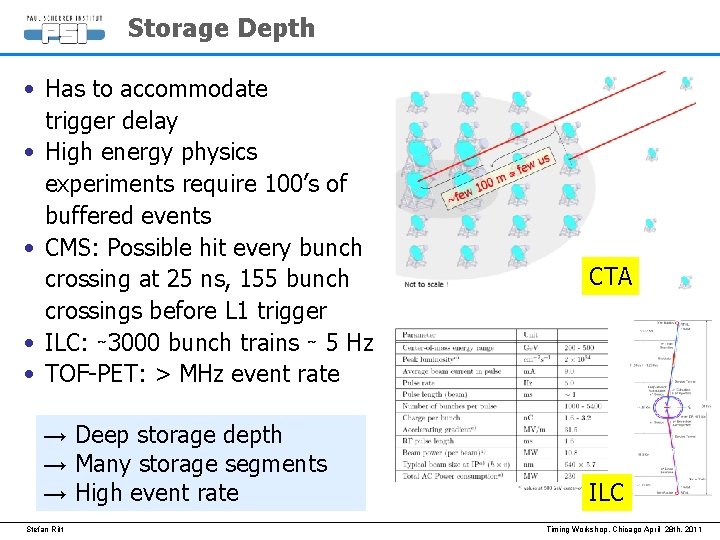

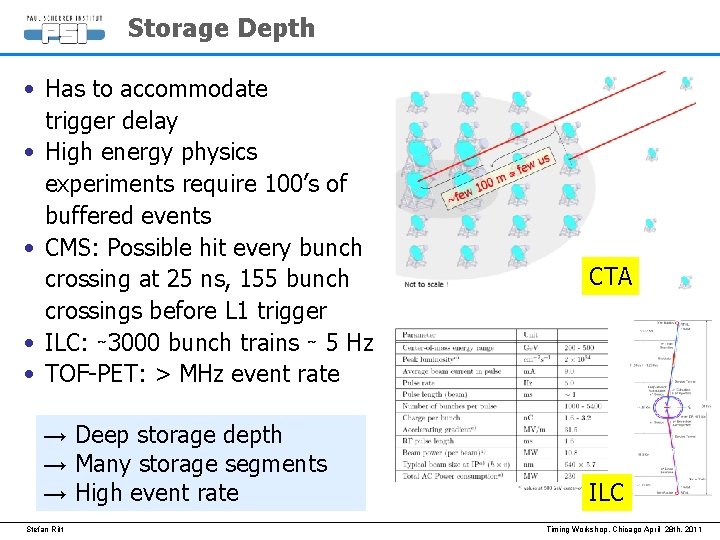

Storage Depth • Has to accommodate trigger delay • High energy physics experiments require 100’s of buffered events • CMS: Possible hit every bunch crossing at 25 ns, 155 bunch crossings before L 1 trigger • ILC: ∼ 3000 bunch trains ∼ 5 Hz • TOF-PET: > MHz event rate → Deep storage depth → Many storage segments → High event rate Stefan Ritt CTA ILC Timing Workshop, Chicago April 28 th, 2011

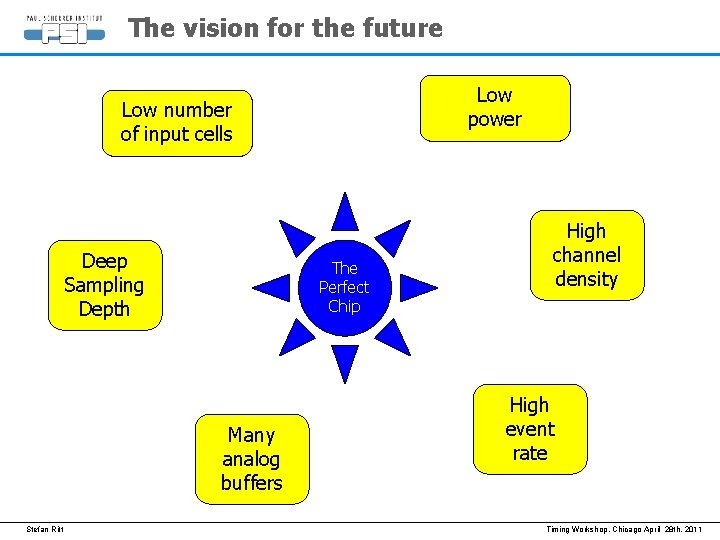

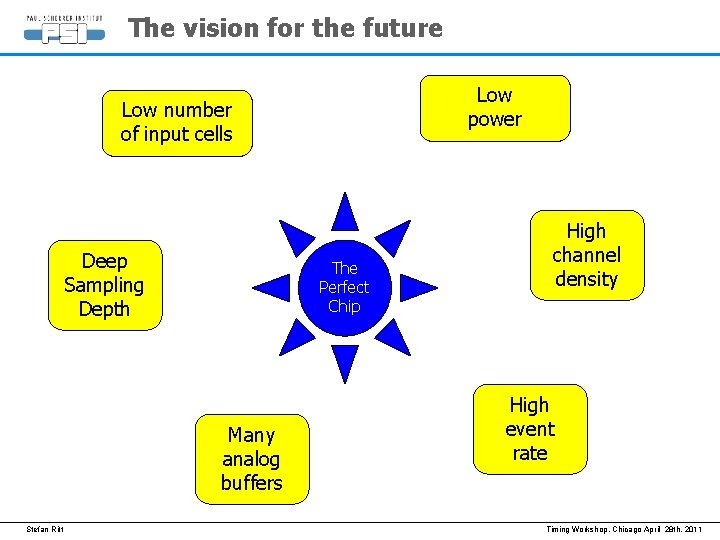

The vision for the future Low power Low number of input cells Deep Sampling Depth The Perfect Chip Many analog buffers Stefan Ritt High channel density High event rate Timing Workshop, Chicago April 28 th, 2011

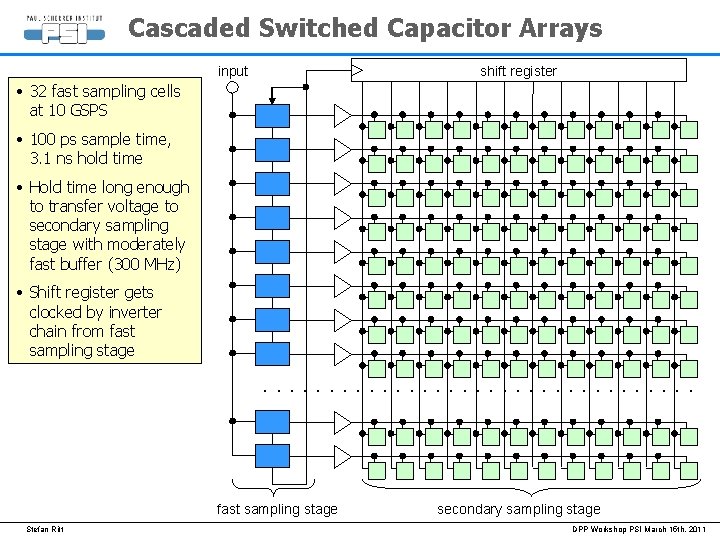

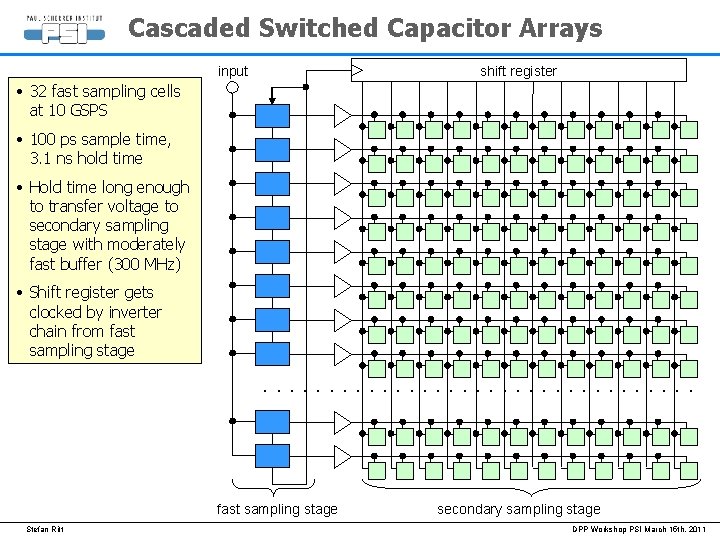

Cascaded Switched Capacitor Arrays shift register input • 32 fast sampling cells at 10 GSPS • 100 ps sample time, 3. 1 ns hold time • Hold time long enough to transfer voltage to secondary sampling stage with moderately fast buffer (300 MHz) • Shift register gets clocked by inverter chain from fast sampling stage . . . . fast sampling stage Stefan Ritt secondary sampling stage DPP Workshop PSI March 15 th, 2011

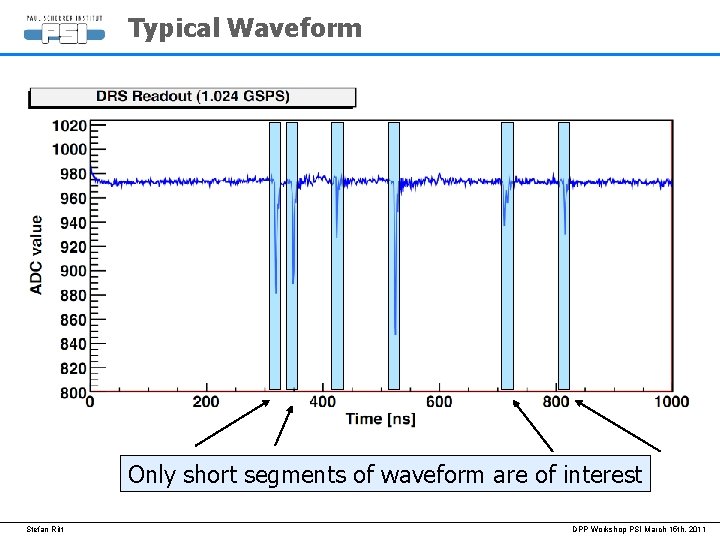

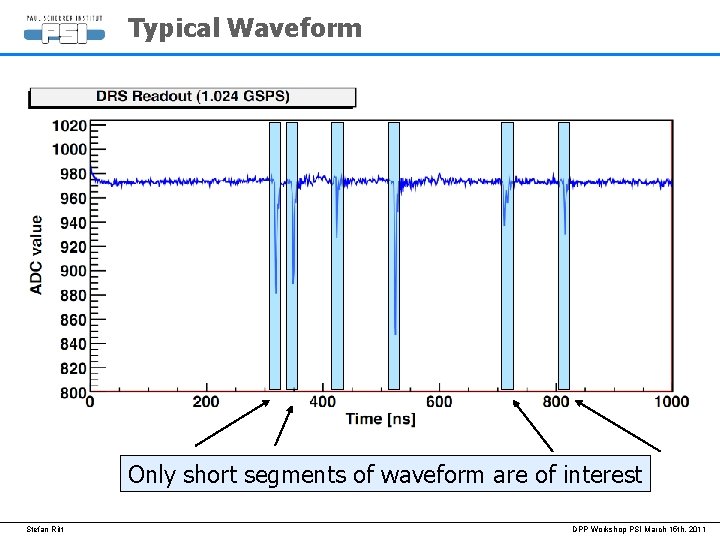

Typical Waveform Only short segments of waveform are of interest Stefan Ritt DPP Workshop PSI March 15 th, 2011

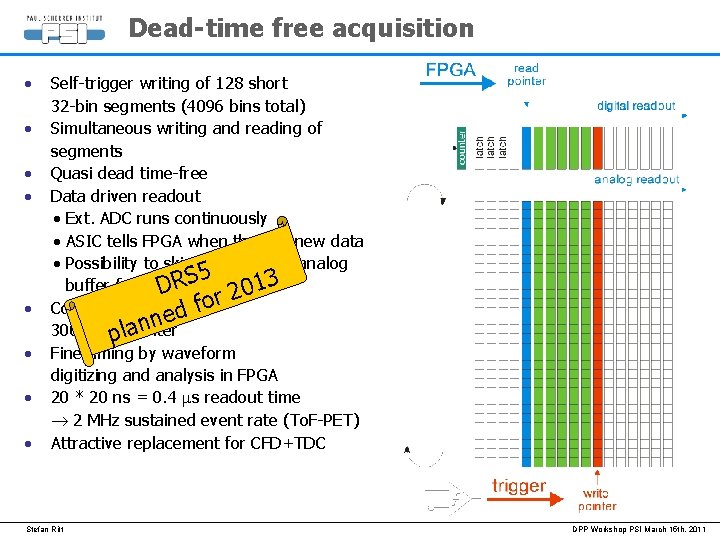

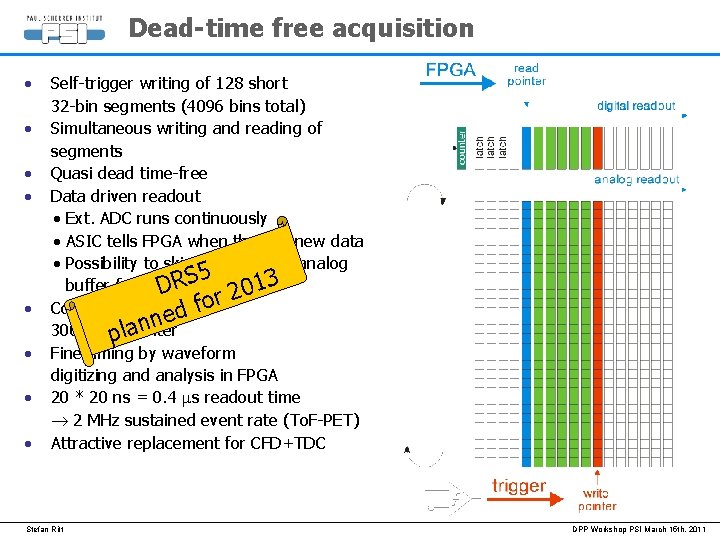

Dead-time free acquisition • • Self-trigger writing of 128 short 32 -bin segments (4096 bins total) Simultaneous writing and reading of segments Quasi dead time-free Data driven readout • Ext. ADC runs continuously • ASIC tells FPGA when there is new data • Possibility to skip segments → analog S 5 013 buffer for HEP DRexperiments r 2 o f Coarse timing from d e n 300 MHzpcounter lan Fine timing by waveform digitizing and analysis in FPGA 20 * 20 ns = 0. 4 ms readout time 2 MHz sustained event rate (To. F-PET) Attractive replacement for CFD+TDC Stefan Ritt DPP Workshop PSI March 15 th, 2011

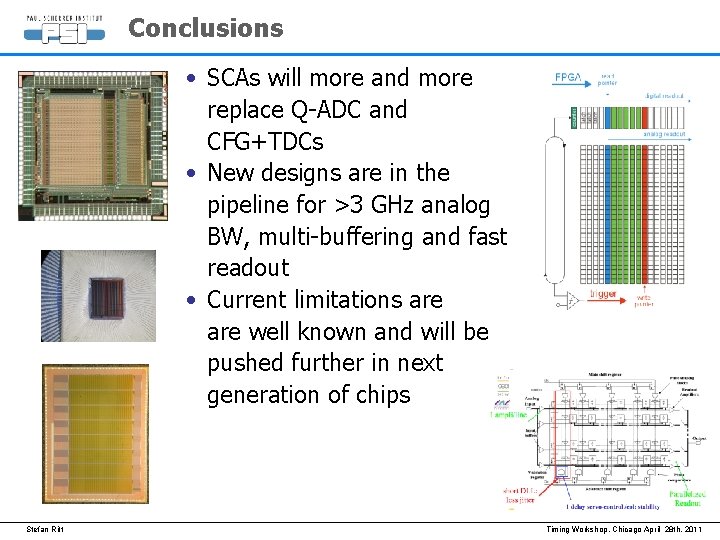

Conclusions • SCAs will more and more replace Q-ADC and CFG+TDCs • New designs are in the pipeline for >3 GHz analog BW, multi-buffering and fast readout • Current limitations are well known and will be pushed further in next generation of chips Stefan Ritt Timing Workshop, Chicago April 28 th, 2011