Organizao e Arquitetura de Computadores II Classificao de

- Slides: 35

Organização e Arquitetura de Computadores II Classificação de Máquinas Paralelas Capítulo 7. 1 do J. L. Baer Capítulos 17. 1, 18. 3 do Stallings Capítulos 8. 1, 8. 3 do Tanenbaum e Austin Capítulo 6 do Hennessy e Patterson Última alteração: 07/05/2018 Prof. Ney Laert Vilar Calazans Baseado em notas de aulas originais do Prof. Dr. César Marcon

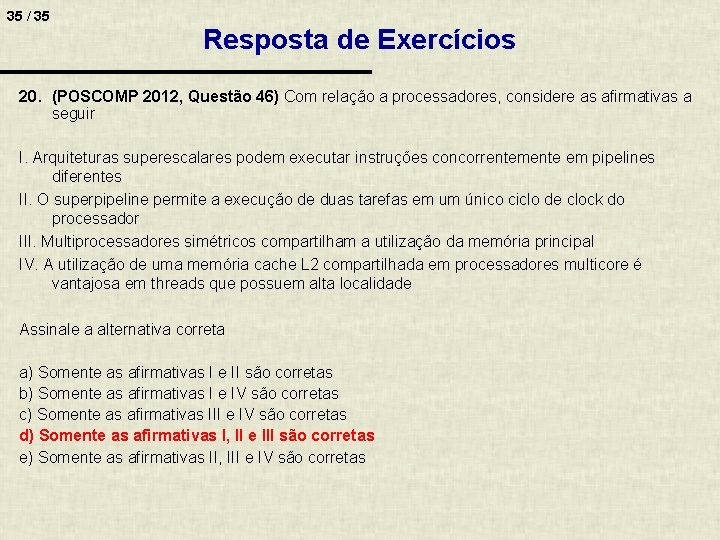

2 / 35 Índice Classificação de Flynn SISD – Single Instruction Single Data SIMD – Single Instruction Multiple Data MISD – Multiple Instruction Single Data MIMD – Multiple Instruction Multiple Data Classificação Segundo Modelos de Memória Compartilhada x Não Compartilhada Memória Centralizada x Distribuída

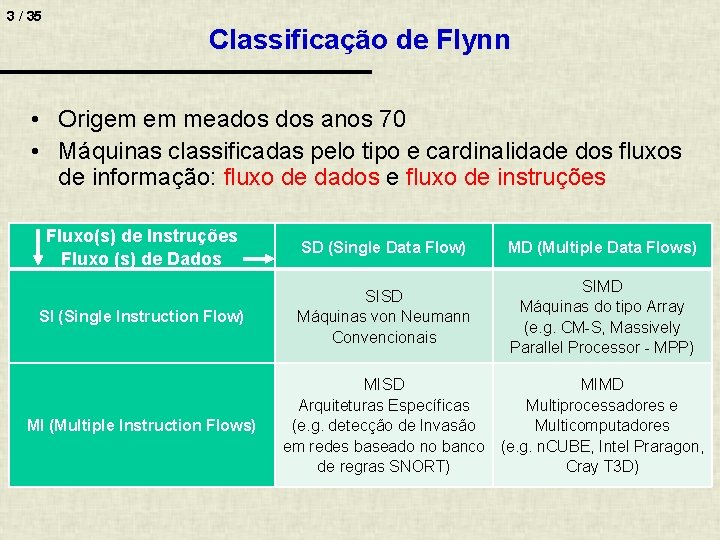

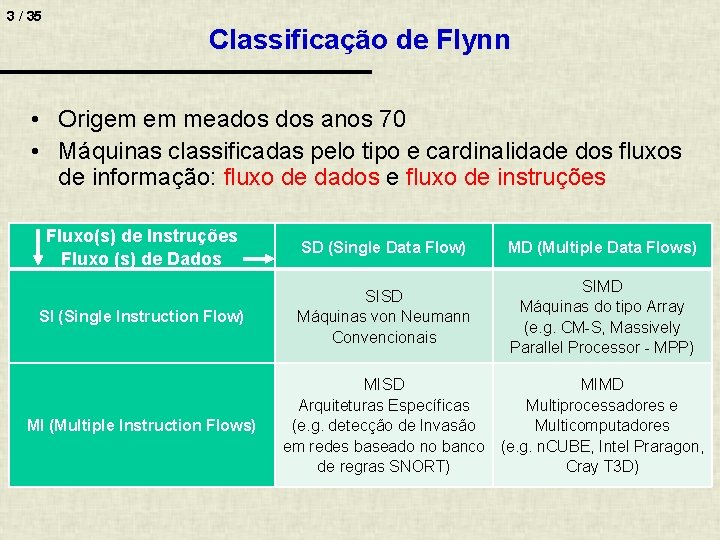

3 / 35 Classificação de Flynn • Origem em meados anos 70 • Máquinas classificadas pelo tipo e cardinalidade dos fluxos de informação: fluxo de dados e fluxo de instruções Fluxo(s) de Instruções Fluxo (s) de Dados SD (Single Data Flow) MD (Multiple Data Flows) SI (Single Instruction Flow) SISD Máquinas von Neumann Convencionais SIMD Máquinas do tipo Array (e. g. CM-S, Massively Parallel Processor - MPP) MI (Multiple Instruction Flows) MISD MIMD Arquiteturas Específicas Multiprocessadores e (e. g. detecção de Invasão Multicomputadores em redes baseado no banco (e. g. n. CUBE, Intel Praragon, de regras SNORT) Cray T 3 D)

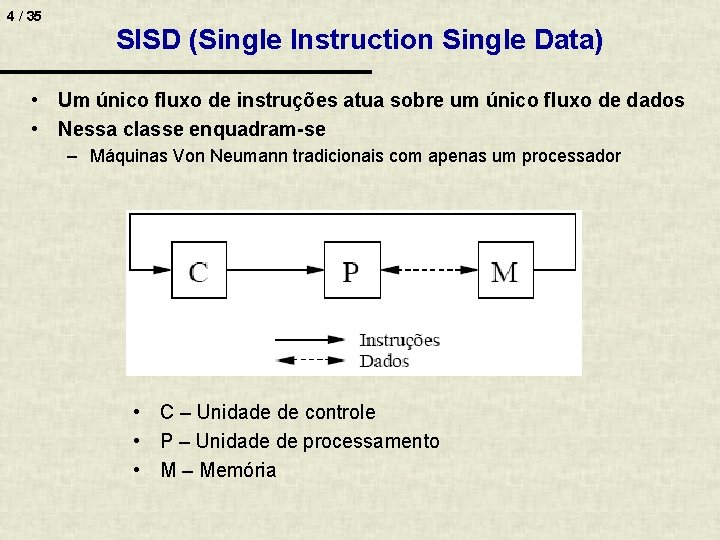

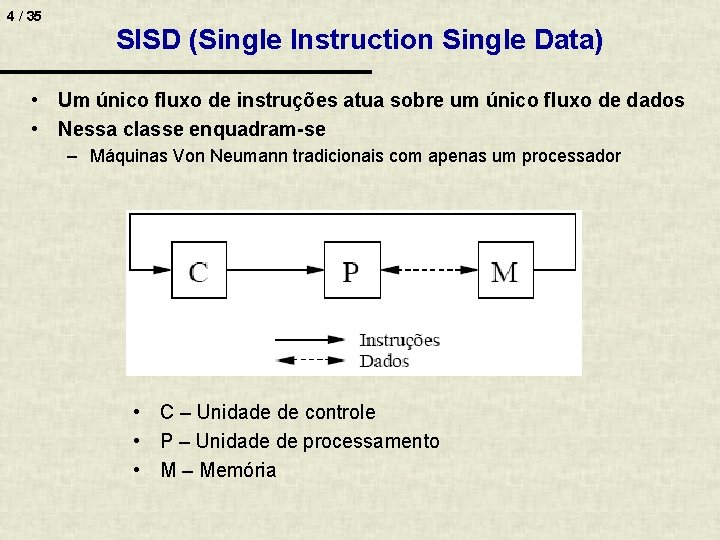

4 / 35 SISD (Single Instruction Single Data) • Um único fluxo de instruções atua sobre um único fluxo de dados • Nessa classe enquadram-se – Máquinas Von Neumann tradicionais com apenas um processador • C – Unidade de controle • P – Unidade de processamento • M – Memória

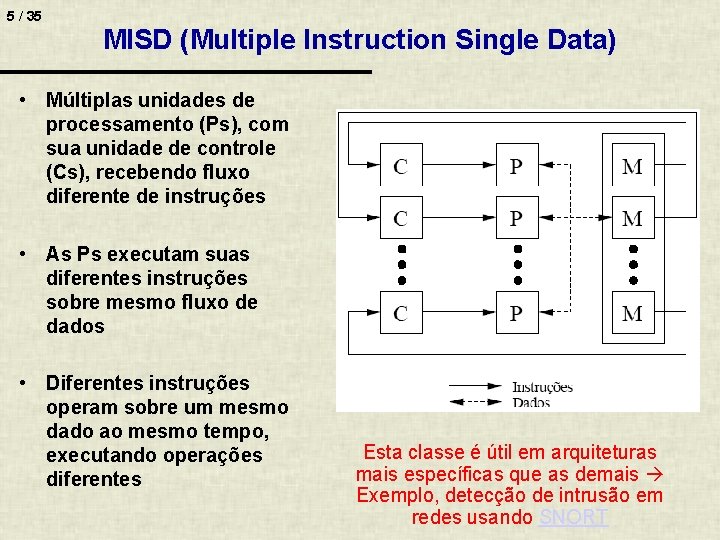

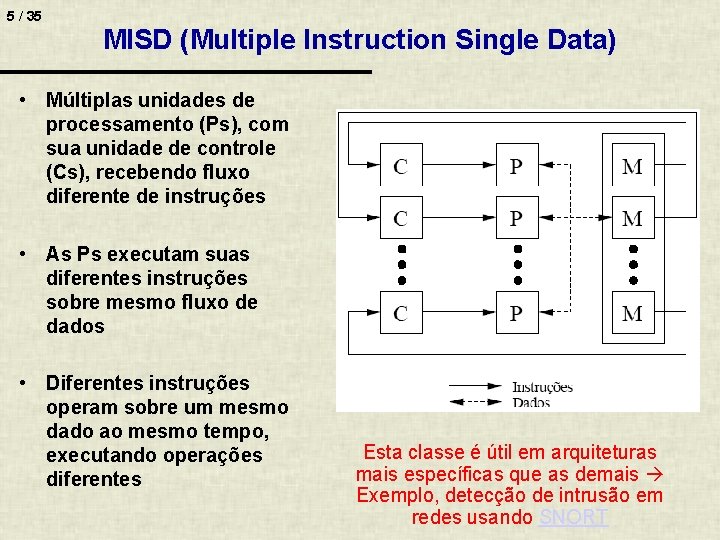

5 / 35 MISD (Multiple Instruction Single Data) • Múltiplas unidades de processamento (Ps), com sua unidade de controle (Cs), recebendo fluxo diferente de instruções • As Ps executam suas diferentes instruções sobre mesmo fluxo de dados • Diferentes instruções operam sobre um mesmo dado ao mesmo tempo, executando operações diferentes Esta classe é útil em arquiteturas mais específicas que as demais Exemplo, detecção de intrusão em redes usando SNORT

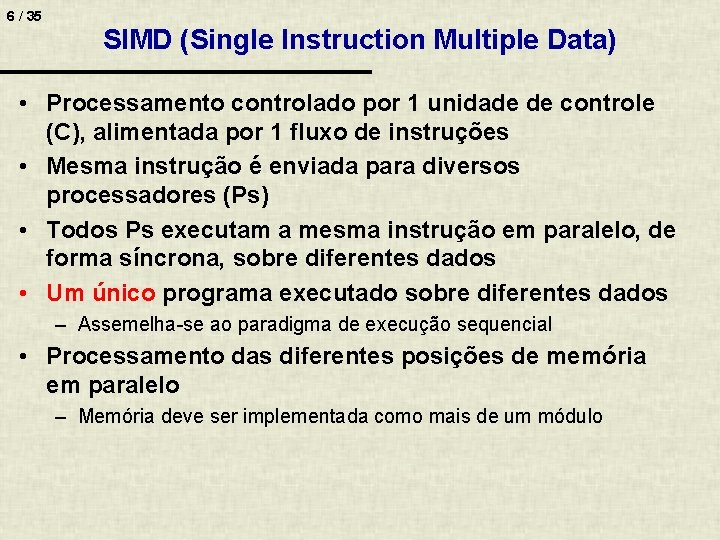

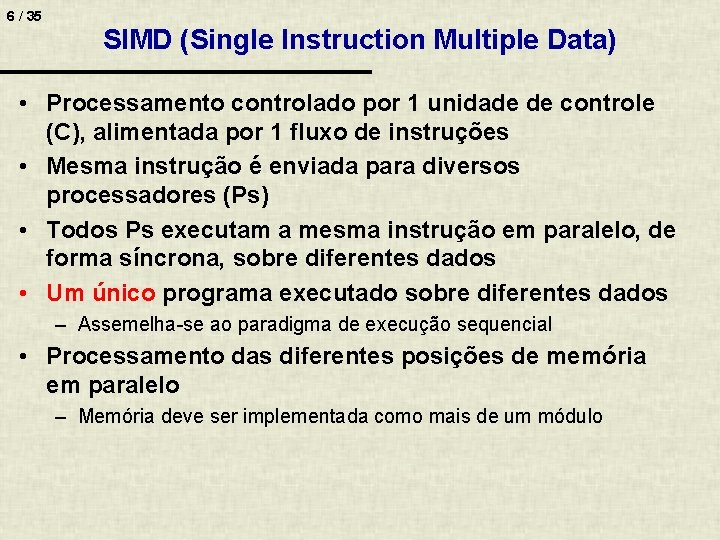

6 / 35 SIMD (Single Instruction Multiple Data) • Processamento controlado por 1 unidade de controle (C), alimentada por 1 fluxo de instruções • Mesma instrução é enviada para diversos processadores (Ps) • Todos Ps executam a mesma instrução em paralelo, de forma síncrona, sobre diferentes dados • Um único programa executado sobre diferentes dados – Assemelha-se ao paradigma de execução sequencial • Processamento das diferentes posições de memória em paralelo – Memória deve ser implementada como mais de um módulo

7 / 35 SIMD (Single Instruction Multiple Data) • Nessa classe enquadram-se as máquinas vetoriais – CM-2 – MPP – Etc.

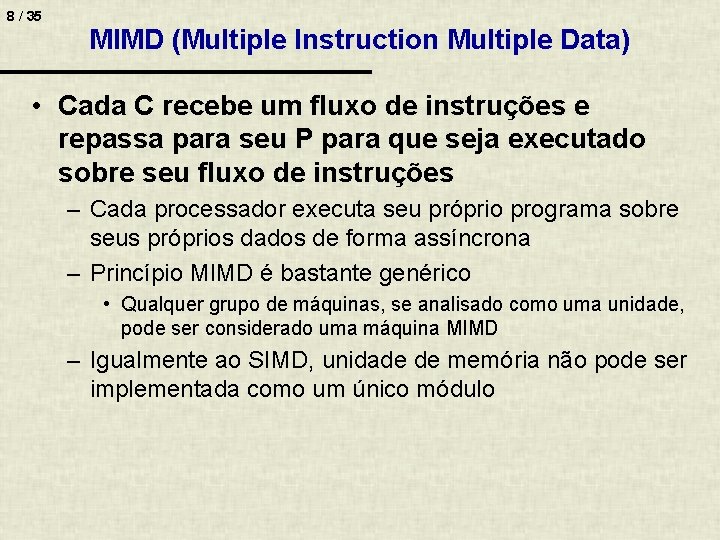

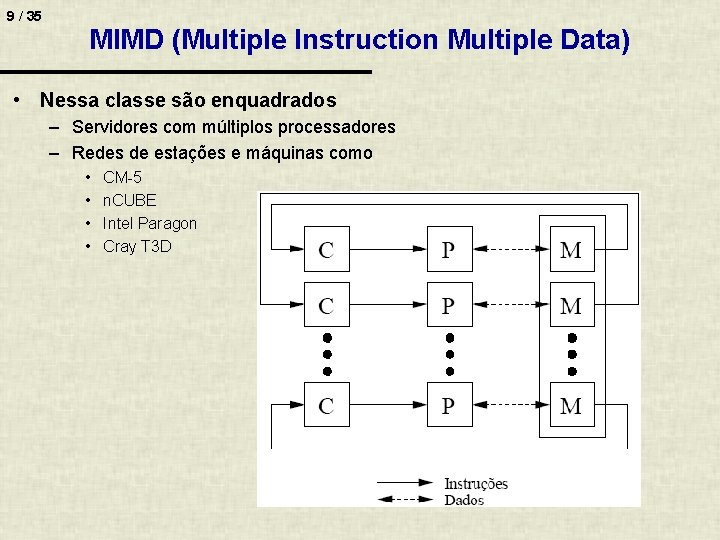

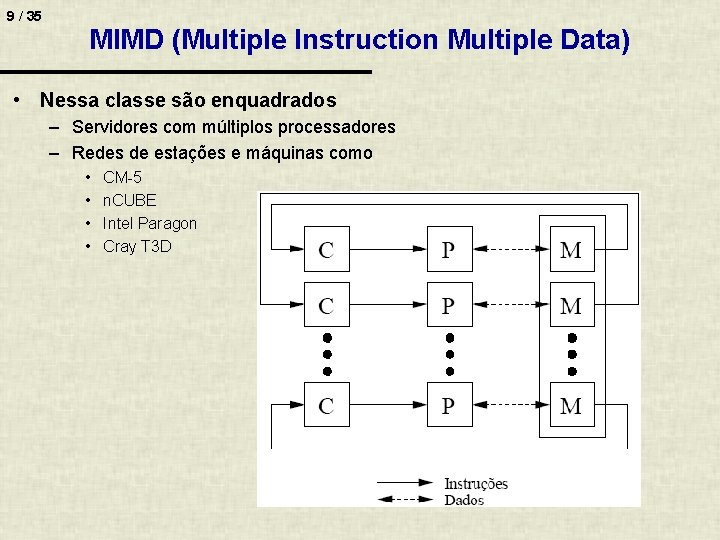

8 / 35 MIMD (Multiple Instruction Multiple Data) • Cada C recebe um fluxo de instruções e repassa para seu P para que seja executado sobre seu fluxo de instruções – Cada processador executa seu próprio programa sobre seus próprios dados de forma assíncrona – Princípio MIMD é bastante genérico • Qualquer grupo de máquinas, se analisado como uma unidade, pode ser considerado uma máquina MIMD – Igualmente ao SIMD, unidade de memória não pode ser implementada como um único módulo

9 / 35 MIMD (Multiple Instruction Multiple Data) • Nessa classe são enquadrados – Servidores com múltiplos processadores – Redes de estações e máquinas como • • CM-5 n. CUBE Intel Paragon Cray T 3 D

10 / 35 Exercícios 1. Dê um exemplo de máquina para a classe MISD de Flynn 2. Qual o princípio de funcionamento das arquiteturas SIMD? Comente para as arquiteturas SIMD o parâmetro "granularidade" dos processadores 3. Analise uma máquina vetorial com relação à classificação de Flynn. Utilize a figura apresentada em aula e mostre os elementos de uma arquitetura vetorial 4. Quais são as características do paralelismo em uma máquina SIMD e MIMD: ( ) paralelismo espacial assíncrono; ( ) paralelismo espacial síncrono. Explique. . .

11 / 35 Índice Classificação de Flynn SISD – Single Instruction Single Data SIMD – Single Instruction Multiple Data MISD – Multiple Instruction Single Data MIMD – Multiple Instruction Multiple Data Classificação Segundo Modelos de Memória Compartilhada x Não Compartilhada Memória Centralizada x Distribuída

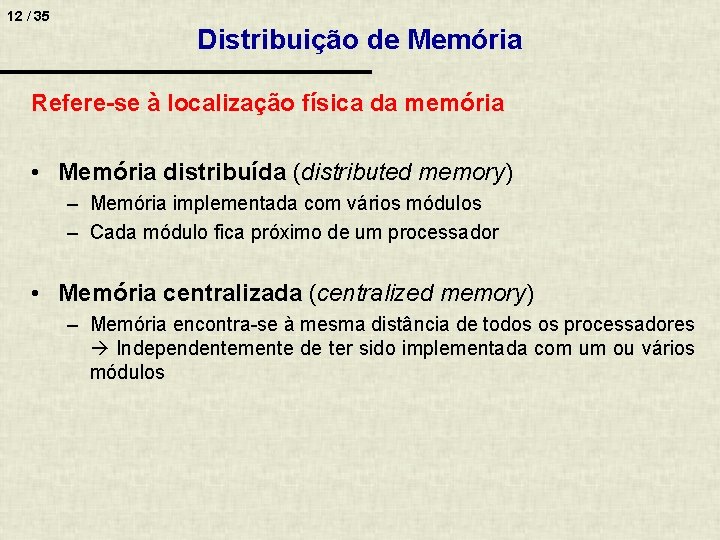

12 / 35 Distribuição de Memória Refere-se à localização física da memória • Memória distribuída (distributed memory) – Memória implementada com vários módulos – Cada módulo fica próximo de um processador • Memória centralizada (centralized memory) – Memória encontra-se à mesma distância de todos os processadores Independentemente de ter sido implementada com um ou vários módulos

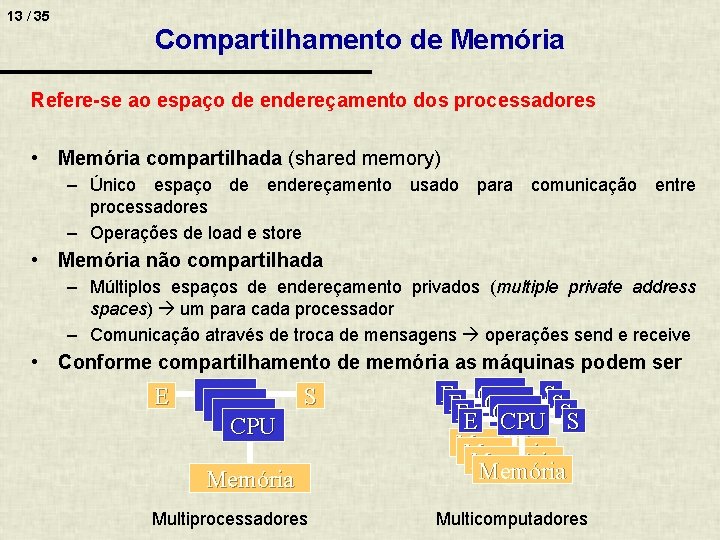

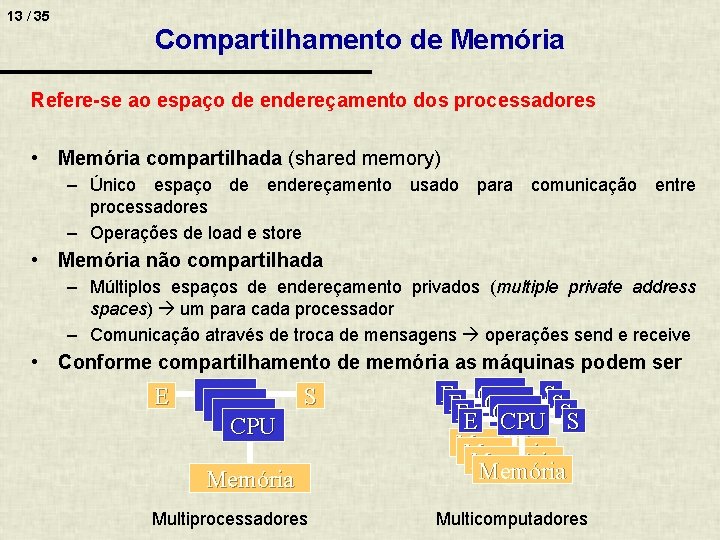

13 / 35 Compartilhamento de Memória Refere-se ao espaço de endereçamento dos processadores • Memória compartilhada (shared memory) – Único espaço de endereçamento usado para comunicação entre processadores – Operações de load e store • Memória não compartilhada – Múltiplos espaços de endereçamento privados (multiple private address spaces) um para cada processador – Comunicação através de troca de mensagens operações send e receive • Conforme compartilhamento de memória as máquinas podem ser E CPU CPU S Memória Multiprocessadores EE CPU SS CPU EE CPU SS Memória Multicomputadores

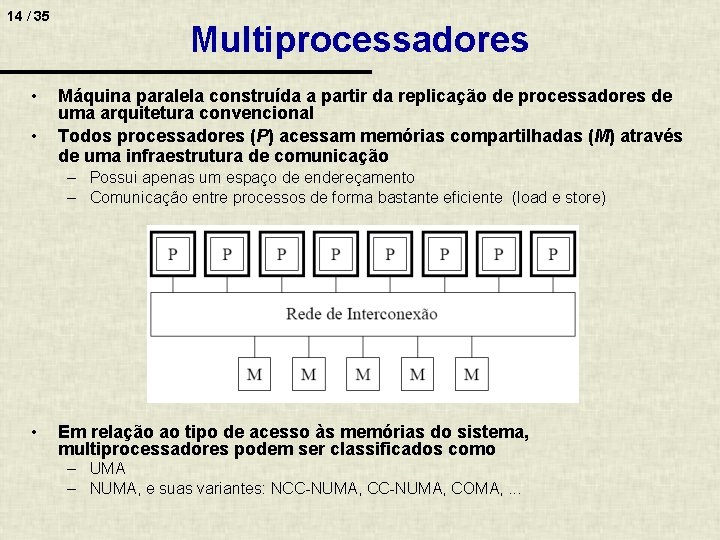

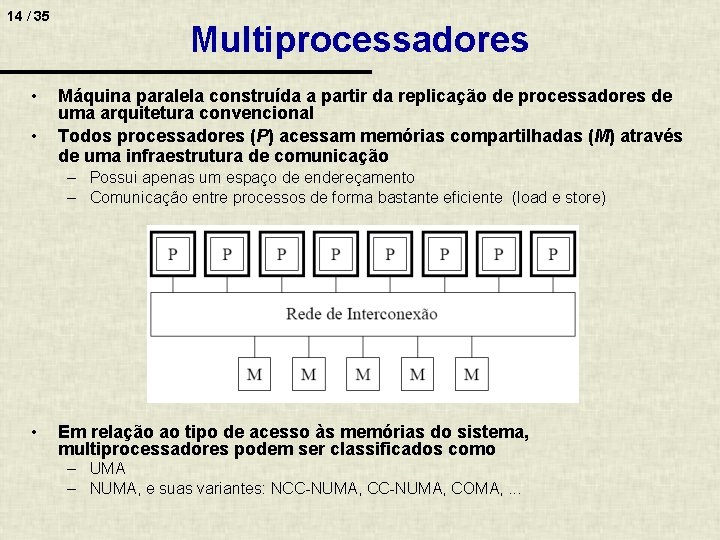

14 / 35 • • Multiprocessadores Máquina paralela construída a partir da replicação de processadores de uma arquitetura convencional Todos processadores (P) acessam memórias compartilhadas (M) através de uma infraestrutura de comunicação – Possui apenas um espaço de endereçamento – Comunicação entre processos de forma bastante eficiente (load e store) • Em relação ao tipo de acesso às memórias do sistema, multiprocessadores podem ser classificados como – UMA – NUMA, e suas variantes: NCC-NUMA, COMA, . . .

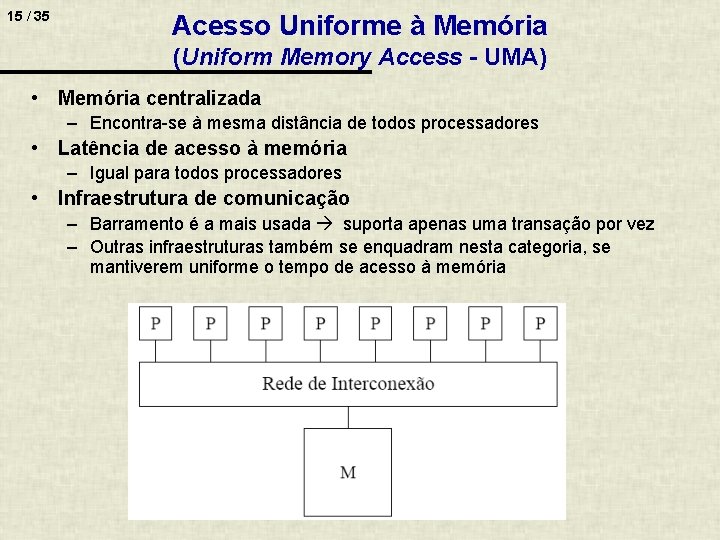

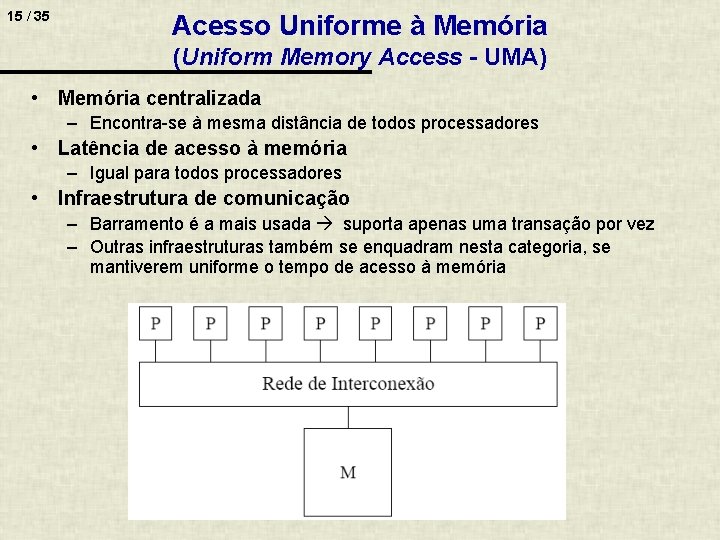

15 / 35 Acesso Uniforme à Memória (Uniform Memory Access - UMA) • Memória centralizada – Encontra-se à mesma distância de todos processadores • Latência de acesso à memória – Igual para todos processadores • Infraestrutura de comunicação – Barramento é a mais usada suporta apenas uma transação por vez – Outras infraestruturas também se enquadram nesta categoria, se mantiverem uniforme o tempo de acesso à memória

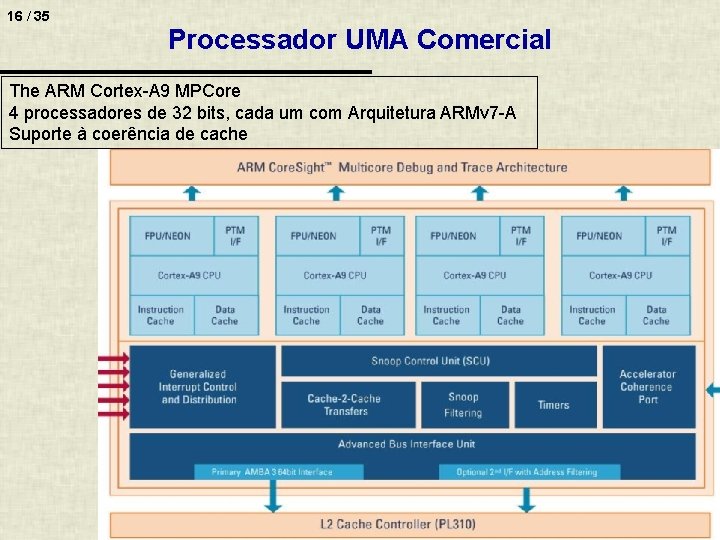

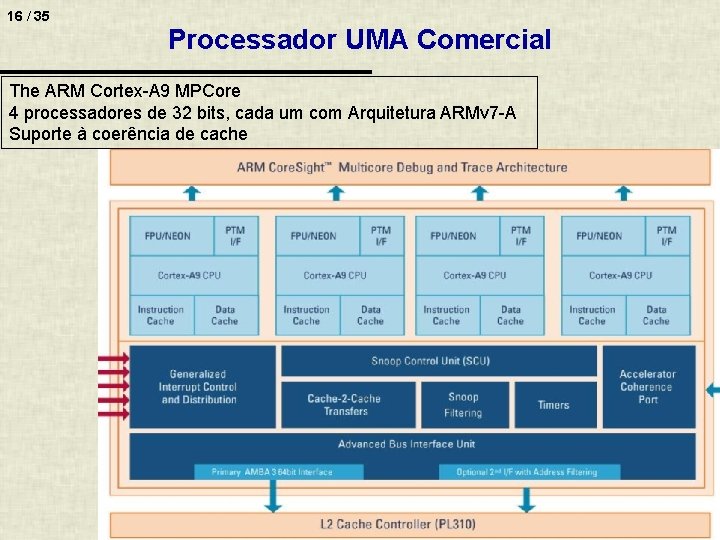

16 / 35 Processador UMA Comercial The ARM Cortex-A 9 MPCore 4 processadores de 32 bits, cada um com Arquitetura ARMv 7 -A Suporte à coerência de cache

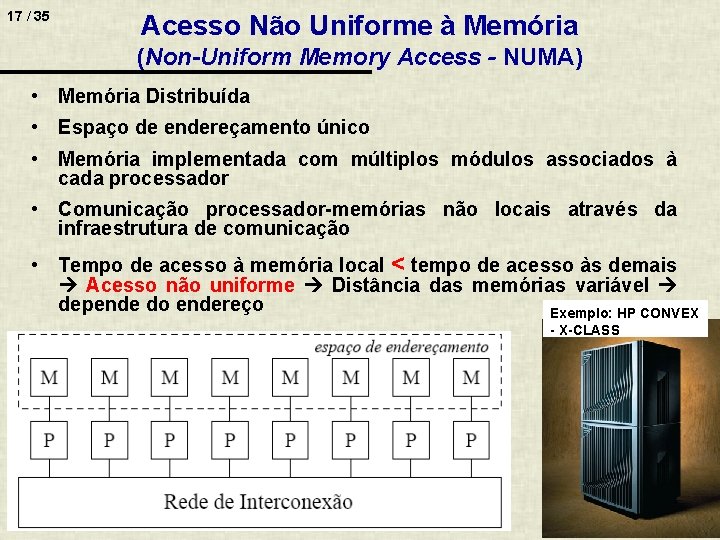

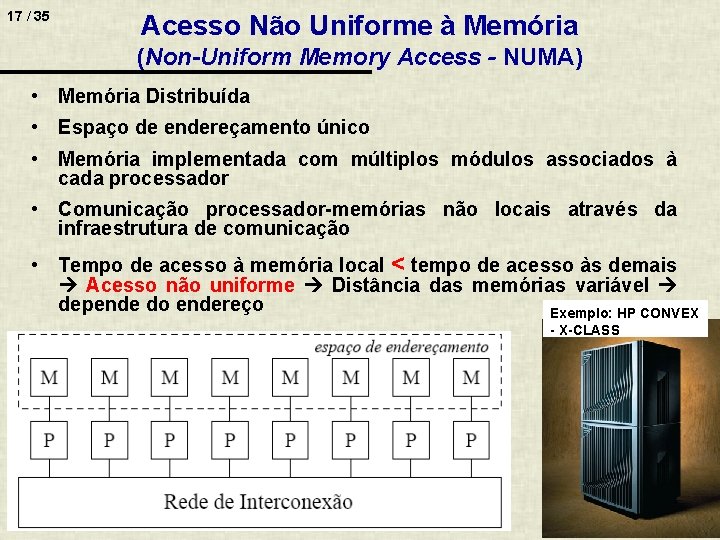

17 / 35 Acesso Não Uniforme à Memória (Non-Uniform Memory Access - NUMA) • Memória Distribuída • Espaço de endereçamento único • Memória implementada com múltiplos módulos associados à cada processador • Comunicação processador-memórias não locais através da infraestrutura de comunicação • Tempo de acesso à memória local < tempo de acesso às demais Acesso não uniforme Distância das memórias variável depende do endereço Exemplo: HP CONVEX - X-CLASS

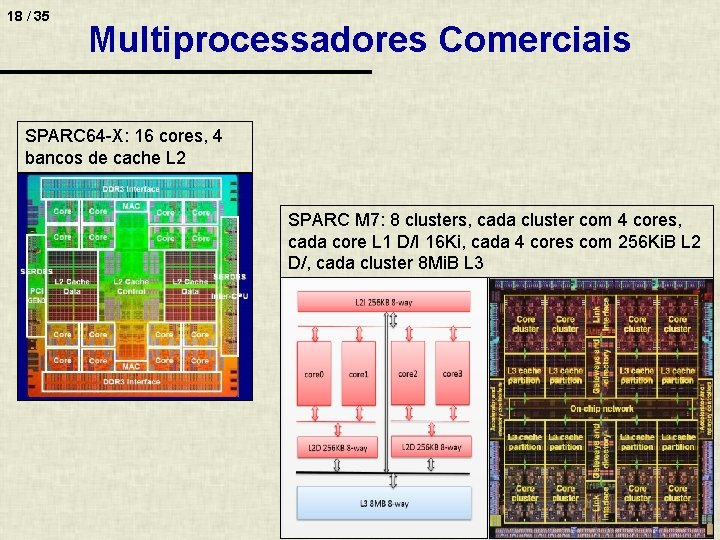

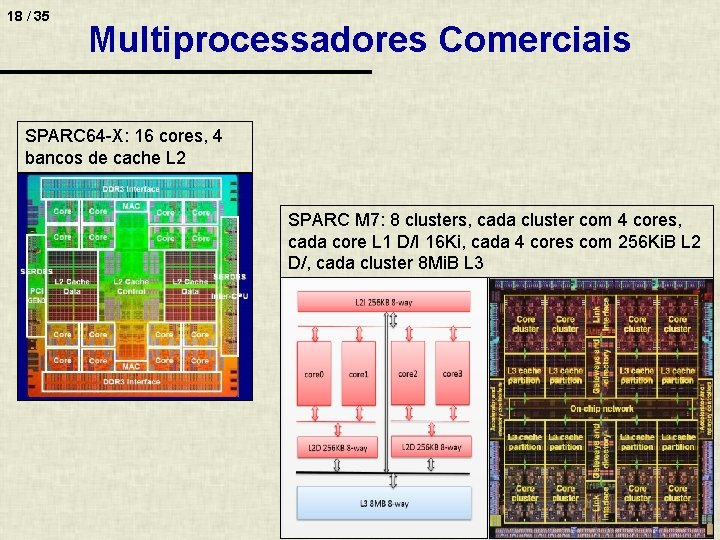

18 / 35 Multiprocessadores Comerciais SPARC 64 -X: 16 cores, 4 bancos de cache L 2 SPARC M 7: 8 clusters, cada cluster com 4 cores, cada core L 1 D/I 16 Ki, cada 4 cores com 256 Ki. B L 2 D/, cada cluster 8 Mi. B L 3

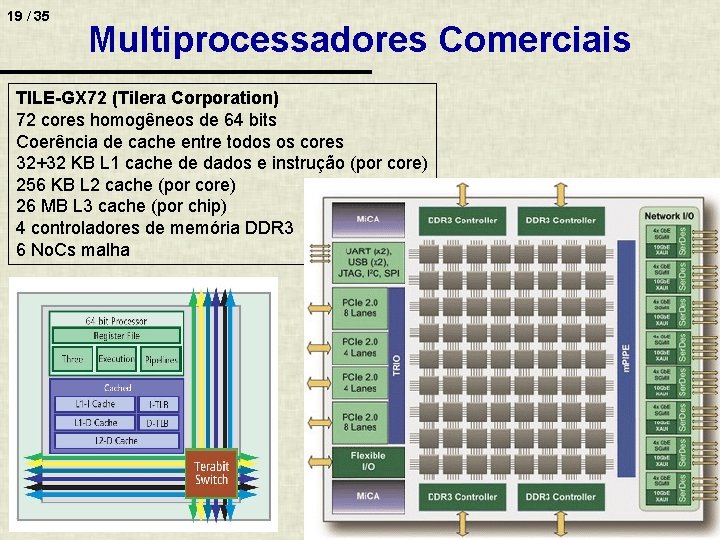

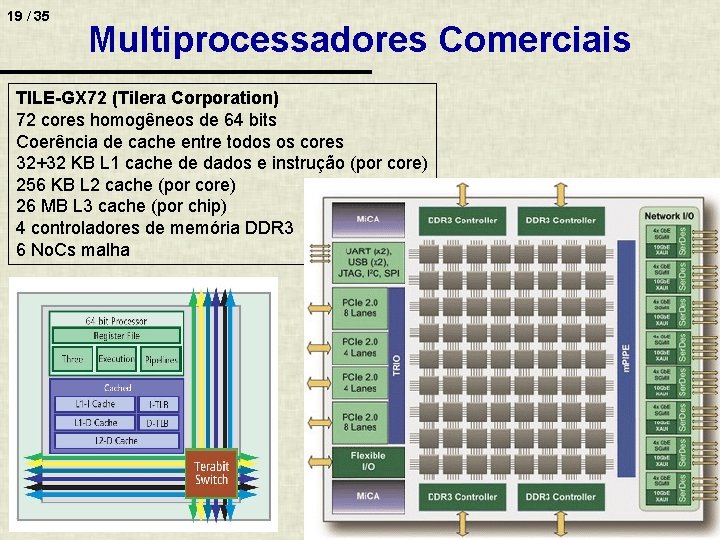

19 / 35 Multiprocessadores Comerciais TILE-GX 72 (Tilera Corporation) 72 cores homogêneos de 64 bits Coerência de cache entre todos os cores 32+32 KB L 1 cache de dados e instrução (por core) 256 KB L 2 cache (por core) 26 MB L 3 cache (por chip) 4 controladores de memória DDR 3 6 No. Cs malha

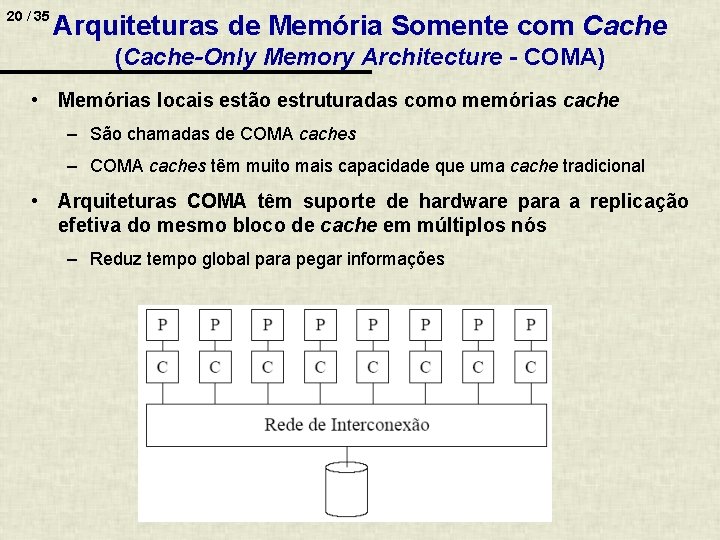

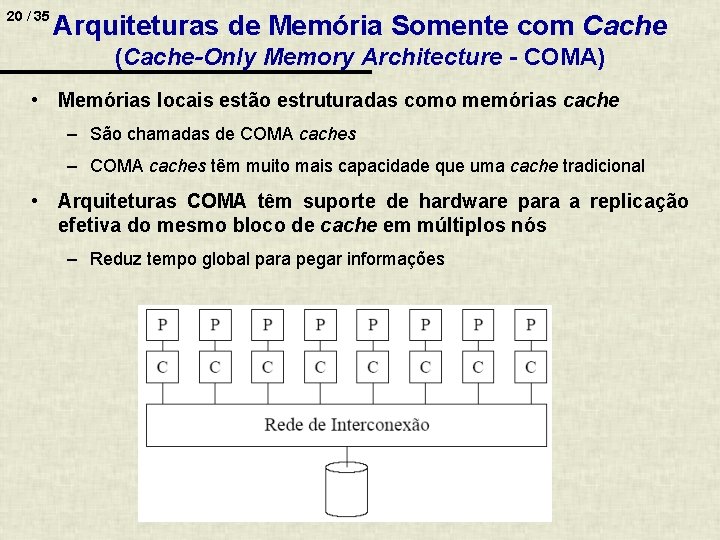

20 / 35 Arquiteturas de Memória Somente com Cache (Cache-Only Memory Architecture - COMA) • Memórias locais estão estruturadas como memórias cache – São chamadas de COMA caches – COMA caches têm muito mais capacidade que uma cache tradicional • Arquiteturas COMA têm suporte de hardware para a replicação efetiva do mesmo bloco de cache em múltiplos nós – Reduz tempo global para pegar informações

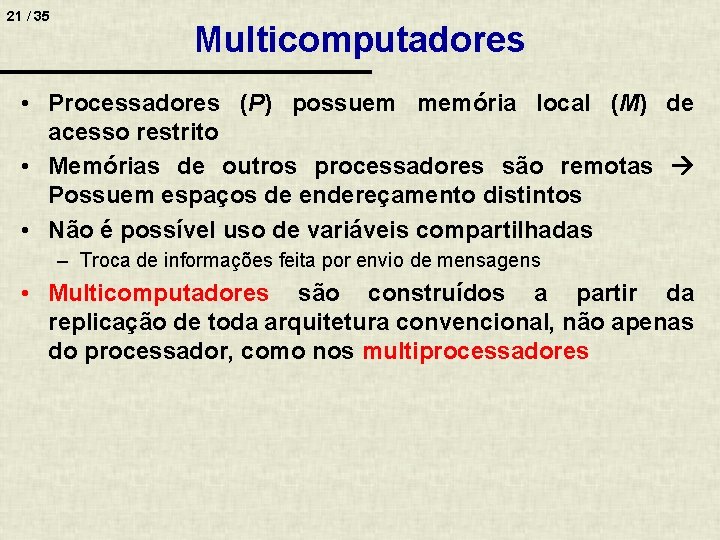

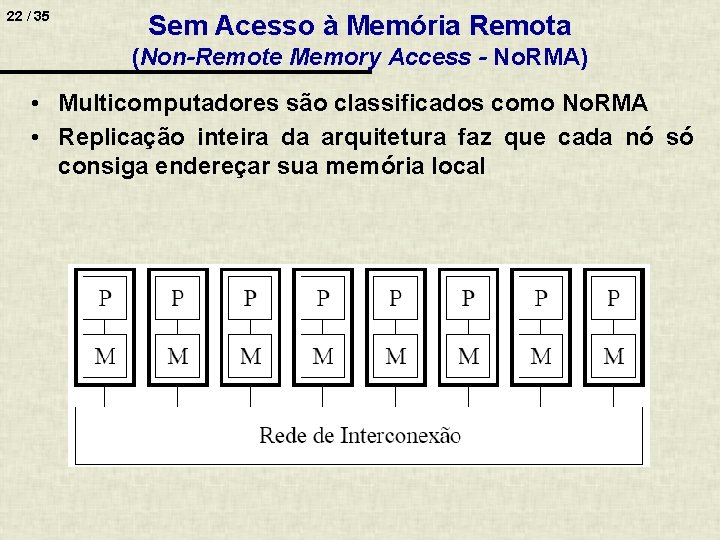

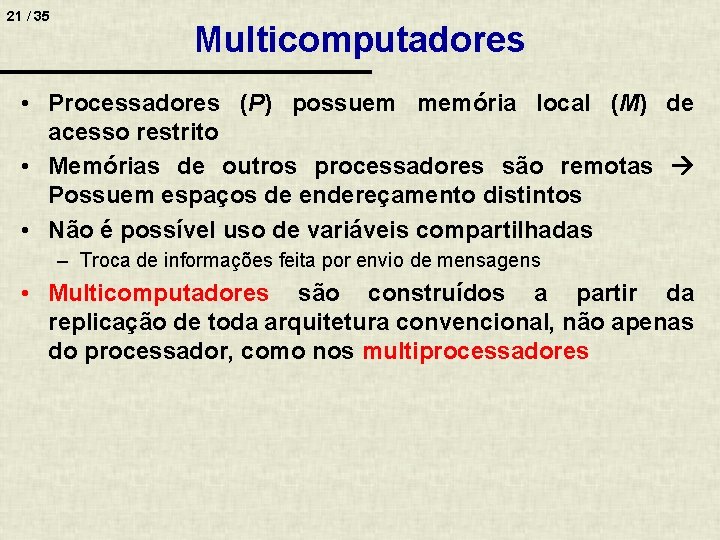

21 / 35 Multicomputadores • Processadores (P) possuem memória local (M) de acesso restrito • Memórias de outros processadores são remotas Possuem espaços de endereçamento distintos • Não é possível uso de variáveis compartilhadas – Troca de informações feita por envio de mensagens • Multicomputadores são construídos a partir da replicação de toda arquitetura convencional, não apenas do processador, como nos multiprocessadores

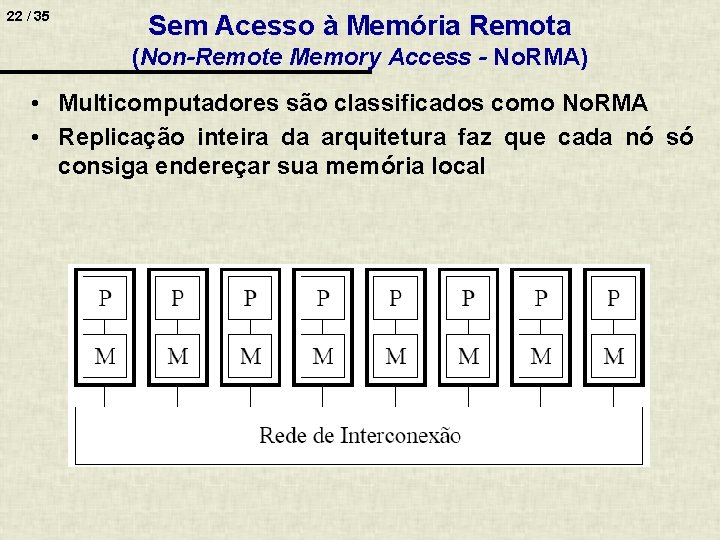

22 / 35 Sem Acesso à Memória Remota (Non-Remote Memory Access - No. RMA) • Multicomputadores são classificados como No. RMA • Replicação inteira da arquitetura faz que cada nó só consiga endereçar sua memória local

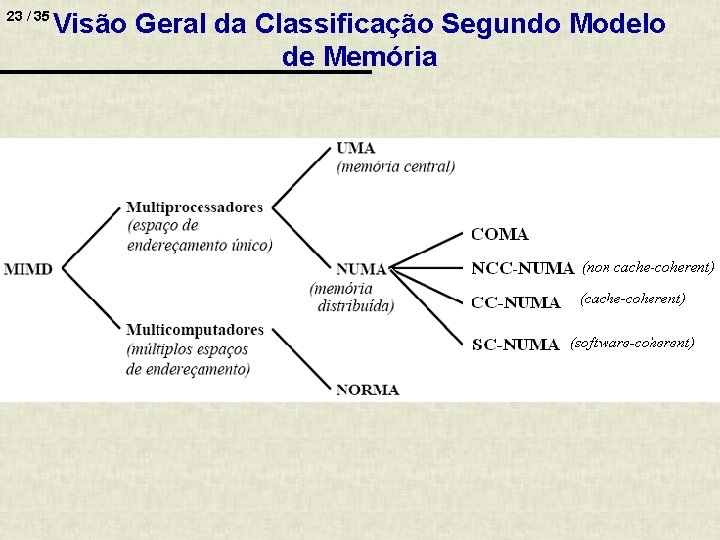

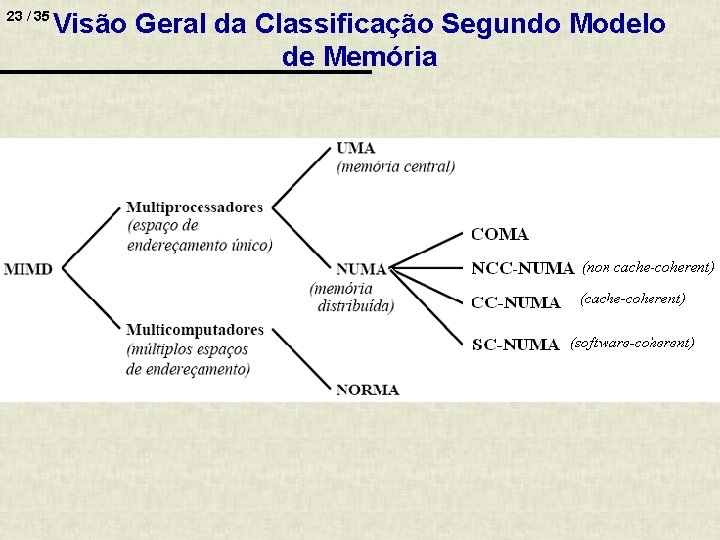

23 / 35 Visão Geral da Classificação Segundo Modelo de Memória

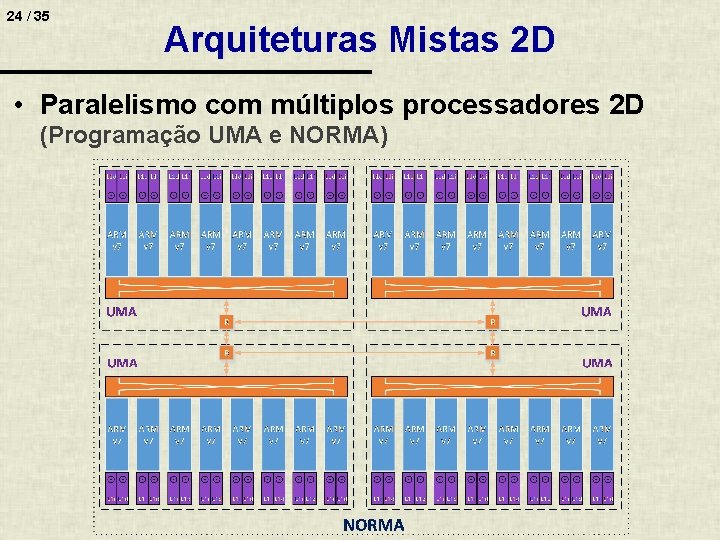

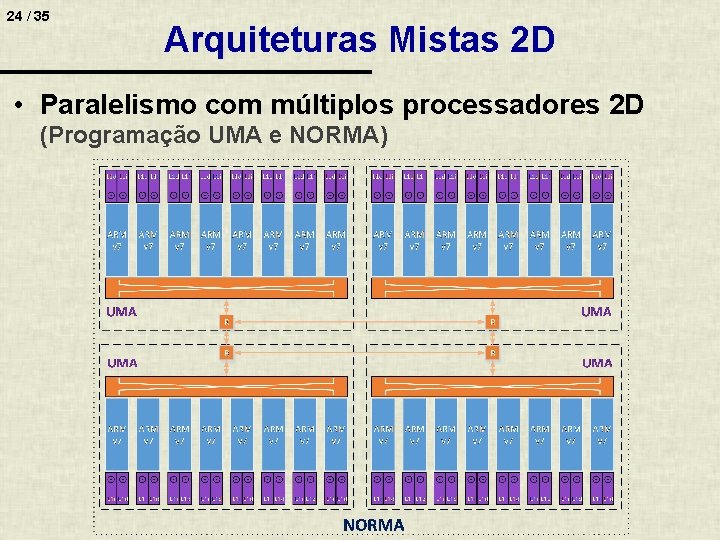

24 / 35 Arquiteturas Mistas 2 D • Paralelismo com múltiplos processadores 2 D (Programação UMA e NORMA)

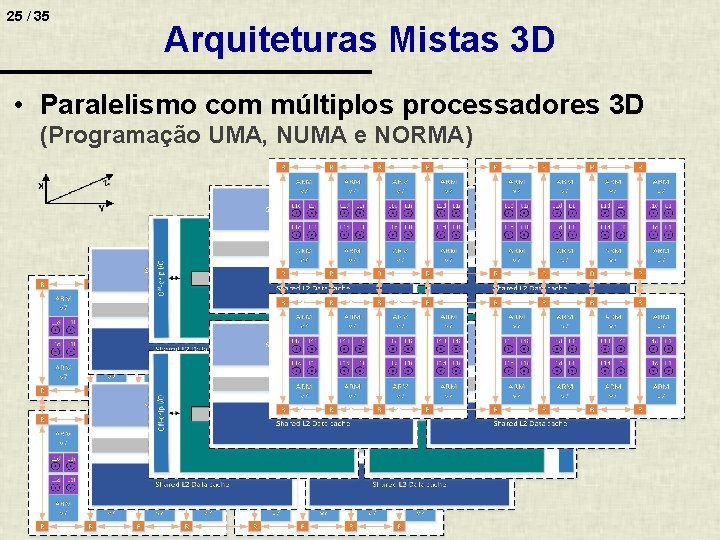

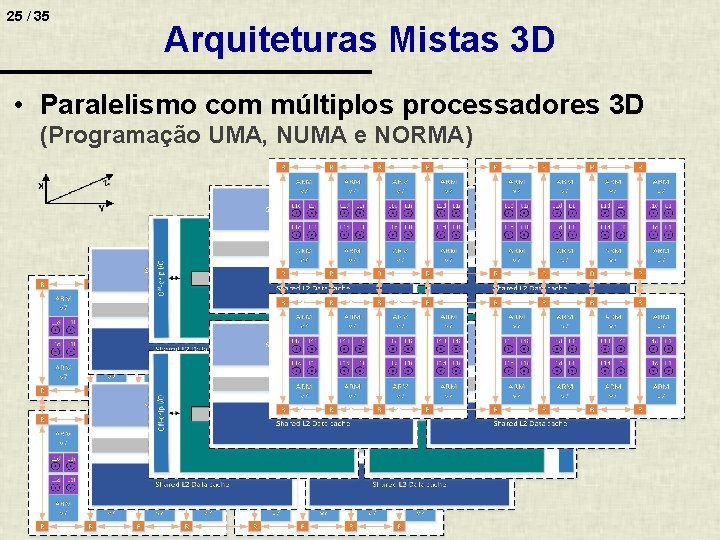

25 / 35 Arquiteturas Mistas 3 D • Paralelismo com múltiplos processadores 3 D (Programação UMA, NUMA e NORMA)

26 / 35 Exercícios 1. Segundo o modelo de compartilhamento de memória, quais são as duas possibilidades para se construir máquinas com vários processadores? Que nome é dado a cada uma delas? 2. Qual o efeito prático de ter um espaço de endereçamento único? E um espaço de endereçamento distinto? 3. Discuta a classificação de máquinas paralelas segundo a memória (compartilhamento/distribuição) 4. Qual a principal diferença entre memórias centralizadas e memórias distribuídas? O que caracteriza esta classificação? 5. Discuta a afirmação: - “A programação paralela com memória de endereçamento compartilhado é mais simples que a programação com endereçamento distribuído” 6. Compare o desempenho de multicomputadores com multiprocessadores 7. Quais as vantagens das máquinas UMA/NUMA sobre as máquinas NORMA, sob o ponto de vista do programador? Por quê? 8. Diferencie as arquiteturas com organização de memória tipo UMA/NUMA das arquiteturas tipo NORMA

27 / 35 Exercícios 9. Por que alguns autores consideram uma arquitetura COMA como subclassificação de arquiteturas UMA? 10. Qual classe de máquinas possui uma memória distribuída e compartilhada? 11. Discuta a afirmação: - “Uma máquina COMA tem maior desempenho que uma máquina NORMA”. Diga se verdadeira ou não e quando? 12. Quais são as necessidades de projeto ou de um sistema operacional para trabalhar em máquinas NUMA, se comparados com máquinas UMA? 13. Desenhe um esquema básico de arquiteturas NORMA e NUMA. Os desenhos são muito parecidos. Onde esta a diferença significativa entre eles? 14. Como a máquina UMA, com barramento para ligar os processadores à memória principal, se beneficiaria de múltiplos canais de uma memória entrelaçada? 15. Qual a grande vantagem de uma máquina COMA frente a uma máquina NUMA? 16. Quais são as características das arquiteturas UMA e NUMA quanto: (a) número de processadores, (b) rede de interconexão, (c) tempo de acesso à memória? Faça um esquema em blocos das arquiteturas UMA e NUMA

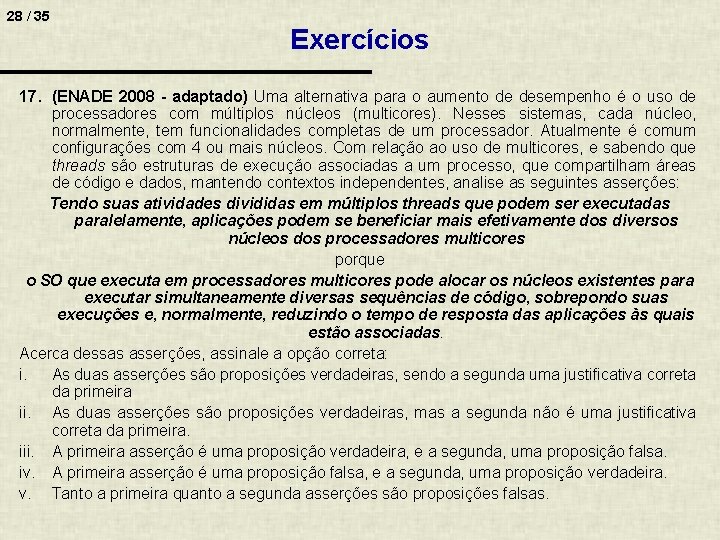

28 / 35 Exercícios 17. (ENADE 2008 - adaptado) Uma alternativa para o aumento de desempenho é o uso de processadores com múltiplos núcleos (multicores). Nesses sistemas, cada núcleo, normalmente, tem funcionalidades completas de um processador. Atualmente é comum configurações com 4 ou mais núcleos. Com relação ao uso de multicores, e sabendo que threads são estruturas de execução associadas a um processo, que compartilham áreas de código e dados, mantendo contextos independentes, analise as seguintes asserções: Tendo suas atividades divididas em múltiplos threads que podem ser executadas paralelamente, aplicações podem se beneficiar mais efetivamente dos diversos núcleos dos processadores multicores porque o SO que executa em processadores multicores pode alocar os núcleos existentes para executar simultaneamente diversas sequências de código, sobrepondo suas execuções e, normalmente, reduzindo o tempo de resposta das aplicações às quais estão associadas. Acerca dessas asserções, assinale a opção correta: i. As duas asserções são proposições verdadeiras, sendo a segunda uma justificativa correta da primeira ii. As duas asserções são proposições verdadeiras, mas a segunda não é uma justificativa correta da primeira. iii. A primeira asserção é uma proposição verdadeira, e a segunda, uma proposição falsa. iv. A primeira asserção é uma proposição falsa, e a segunda, uma proposição verdadeira. v. Tanto a primeira quanto a segunda asserções são proposições falsas.

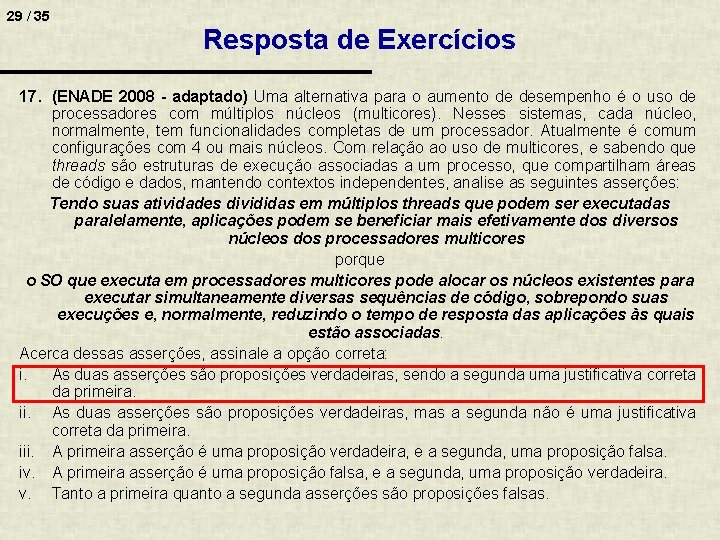

29 / 35 Resposta de Exercícios 17. (ENADE 2008 - adaptado) Uma alternativa para o aumento de desempenho é o uso de processadores com múltiplos núcleos (multicores). Nesses sistemas, cada núcleo, normalmente, tem funcionalidades completas de um processador. Atualmente é comum configurações com 4 ou mais núcleos. Com relação ao uso de multicores, e sabendo que threads são estruturas de execução associadas a um processo, que compartilham áreas de código e dados, mantendo contextos independentes, analise as seguintes asserções: Tendo suas atividades divididas em múltiplos threads que podem ser executadas paralelamente, aplicações podem se beneficiar mais efetivamente dos diversos núcleos dos processadores multicores porque o SO que executa em processadores multicores pode alocar os núcleos existentes para executar simultaneamente diversas sequências de código, sobrepondo suas execuções e, normalmente, reduzindo o tempo de resposta das aplicações às quais estão associadas. Acerca dessas asserções, assinale a opção correta: i. As duas asserções são proposições verdadeiras, sendo a segunda uma justificativa correta da primeira. ii. As duas asserções são proposições verdadeiras, mas a segunda não é uma justificativa correta da primeira. iii. A primeira asserção é uma proposição verdadeira, e a segunda, uma proposição falsa. iv. A primeira asserção é uma proposição falsa, e a segunda, uma proposição verdadeira. v. Tanto a primeira quanto a segunda asserções são proposições falsas.

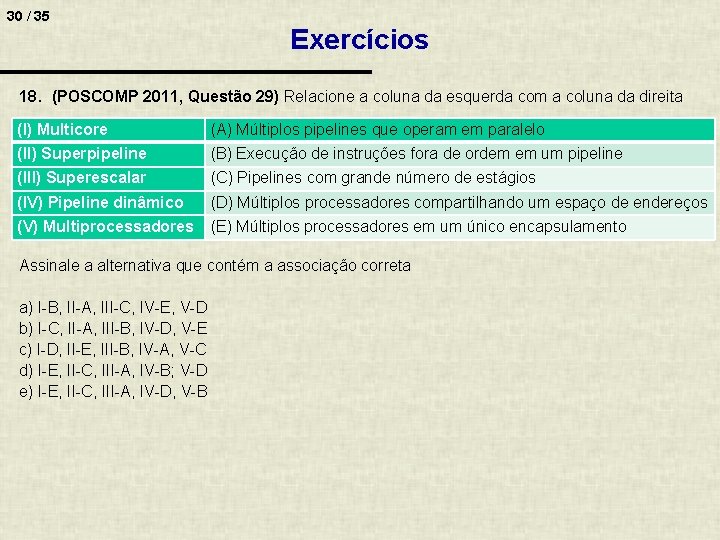

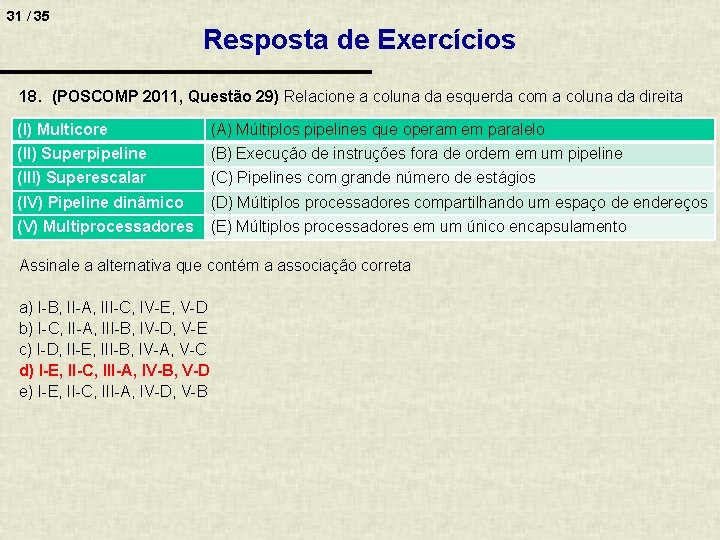

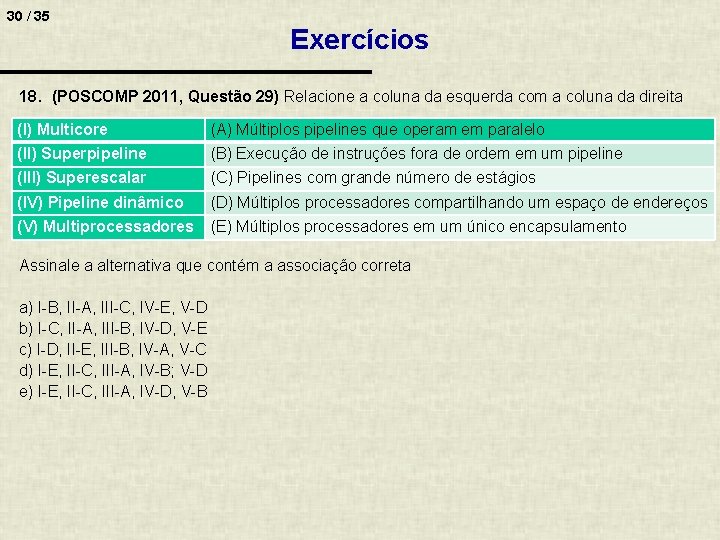

30 / 35 Exercícios 18. (POSCOMP 2011, Questão 29) Relacione a coluna da esquerda com a coluna da direita (I) Multicore (A) Múltiplos pipelines que operam em paralelo (II) Superpipeline (B) Execução de instruções fora de ordem em um pipeline (III) Superescalar (C) Pipelines com grande número de estágios (IV) Pipeline dinâmico (D) Múltiplos processadores compartilhando um espaço de endereços (V) Multiprocessadores (E) Múltiplos processadores em um único encapsulamento Assinale a alternativa que contém a associação correta a) I-B, II-A, III-C, IV-E, V-D b) I-C, II-A, III-B, IV-D, V-E c) I-D, II-E, III-B, IV-A, V-C d) I-E, II-C, III-A, IV-B; V-D e) I-E, II-C, III-A, IV-D, V-B

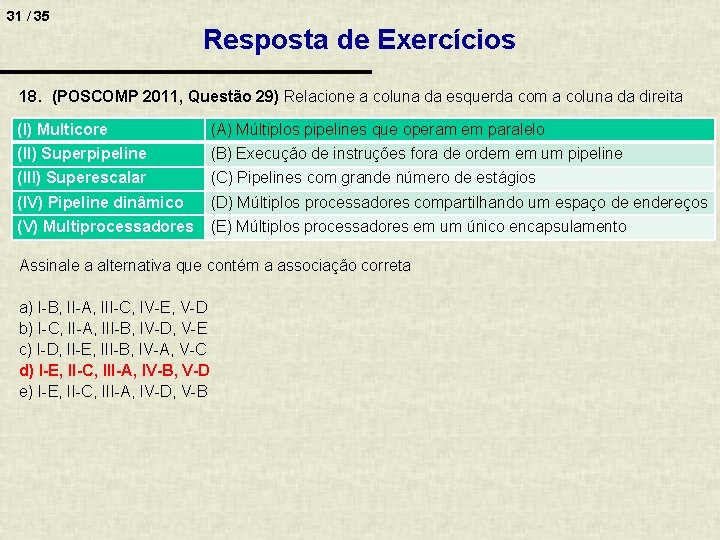

31 / 35 Resposta de Exercícios 18. (POSCOMP 2011, Questão 29) Relacione a coluna da esquerda com a coluna da direita (I) Multicore (A) Múltiplos pipelines que operam em paralelo (II) Superpipeline (B) Execução de instruções fora de ordem em um pipeline (III) Superescalar (C) Pipelines com grande número de estágios (IV) Pipeline dinâmico (D) Múltiplos processadores compartilhando um espaço de endereços (V) Multiprocessadores (E) Múltiplos processadores em um único encapsulamento Assinale a alternativa que contém a associação correta a) I-B, II-A, III-C, IV-E, V-D b) I-C, II-A, III-B, IV-D, V-E c) I-D, II-E, III-B, IV-A, V-C d) I-E, II-C, III-A, IV-B, V-D e) I-E, II-C, III-A, IV-D, V-B

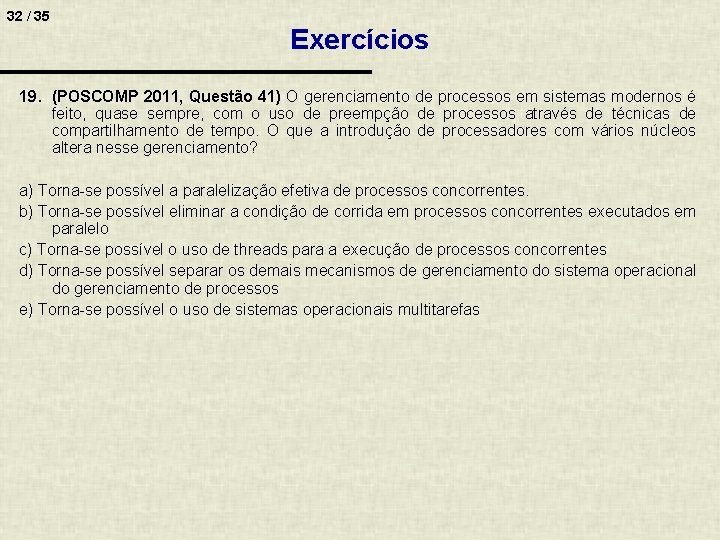

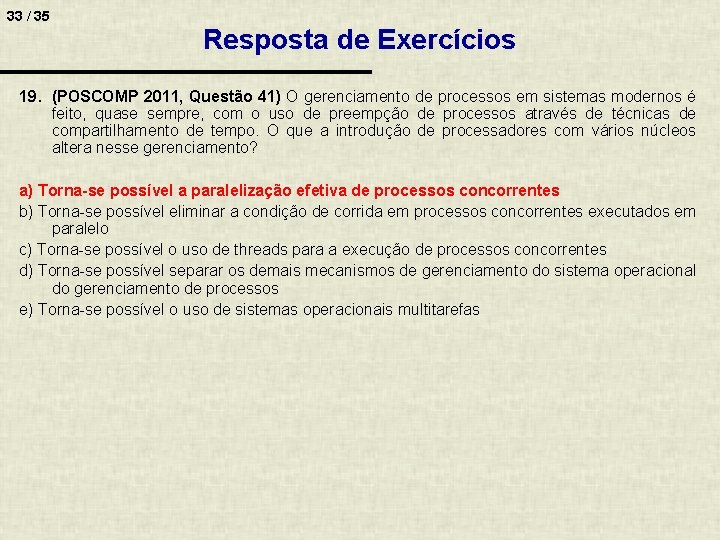

32 / 35 Exercícios 19. (POSCOMP 2011, Questão 41) O gerenciamento de processos em sistemas modernos é feito, quase sempre, com o uso de preempção de processos através de técnicas de compartilhamento de tempo. O que a introdução de processadores com vários núcleos altera nesse gerenciamento? a) Torna-se possível a paralelização efetiva de processos concorrentes. b) Torna-se possível eliminar a condição de corrida em processos concorrentes executados em paralelo c) Torna-se possível o uso de threads para a execução de processos concorrentes d) Torna-se possível separar os demais mecanismos de gerenciamento do sistema operacional do gerenciamento de processos e) Torna-se possível o uso de sistemas operacionais multitarefas

33 / 35 Resposta de Exercícios 19. (POSCOMP 2011, Questão 41) O gerenciamento de processos em sistemas modernos é feito, quase sempre, com o uso de preempção de processos através de técnicas de compartilhamento de tempo. O que a introdução de processadores com vários núcleos altera nesse gerenciamento? a) Torna-se possível a paralelização efetiva de processos concorrentes b) Torna-se possível eliminar a condição de corrida em processos concorrentes executados em paralelo c) Torna-se possível o uso de threads para a execução de processos concorrentes d) Torna-se possível separar os demais mecanismos de gerenciamento do sistema operacional do gerenciamento de processos e) Torna-se possível o uso de sistemas operacionais multitarefas

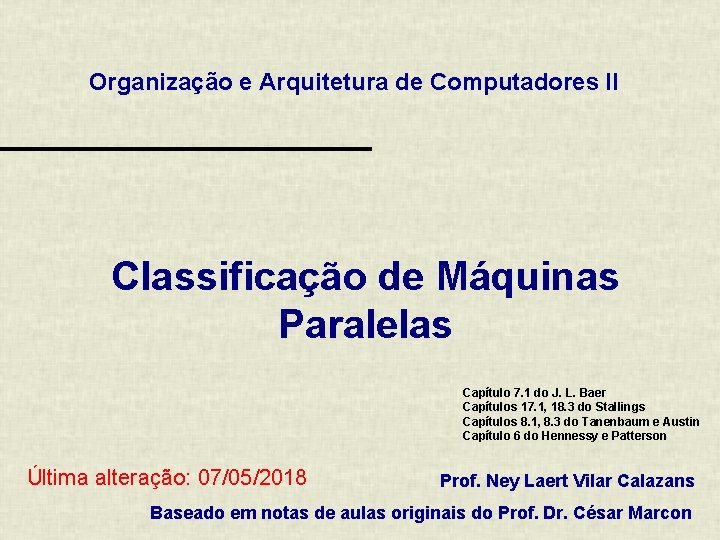

34 / 35 Exercícios 20. (POSCOMP 2012, Questão 46) Com relação a processadores, considere as afirmativas a seguir I. Arquiteturas Superescalares podem executar instruções concorrentemente em pipelines diferentes II. O Superpipeline permite a execução de duas tarefas em um único ciclo de clock do processador III. Multiprocessadores simétricos compartilham a utilização da memória principal IV. A utilização de uma memória cache L 2 compartilhada em processadores multicore é vantajosa em threads que possuem alta localidade Assinale a alternativa correta a) Somente as afirmativas I e II são corretas b) Somente as afirmativas I e IV são corretas c) Somente as afirmativas III e IV são corretas d) Somente as afirmativas I, II e III são corretas e) Somente as afirmativas II, III e IV são corretas

35 / 35 Resposta de Exercícios 20. (POSCOMP 2012, Questão 46) Com relação a processadores, considere as afirmativas a seguir I. Arquiteturas superescalares podem executar instruções concorrentemente em pipelines diferentes II. O superpipeline permite a execução de duas tarefas em um único ciclo de clock do processador III. Multiprocessadores simétricos compartilham a utilização da memória principal IV. A utilização de uma memória cache L 2 compartilhada em processadores multicore é vantajosa em threads que possuem alta localidade Assinale a alternativa correta a) Somente as afirmativas I e II são corretas b) Somente as afirmativas I e IV são corretas c) Somente as afirmativas III e IV são corretas d) Somente as afirmativas I, II e III são corretas e) Somente as afirmativas II, III e IV são corretas