Organizao e Arquitetura de Computadores Captulo 11 Estrutura

- Slides: 54

Organização e Arquitetura de Computadores Capítulo 11 Estrutura e Funções da CPU

Parte I Funcionalidades da CPU Registradores Ciclo de Instruções

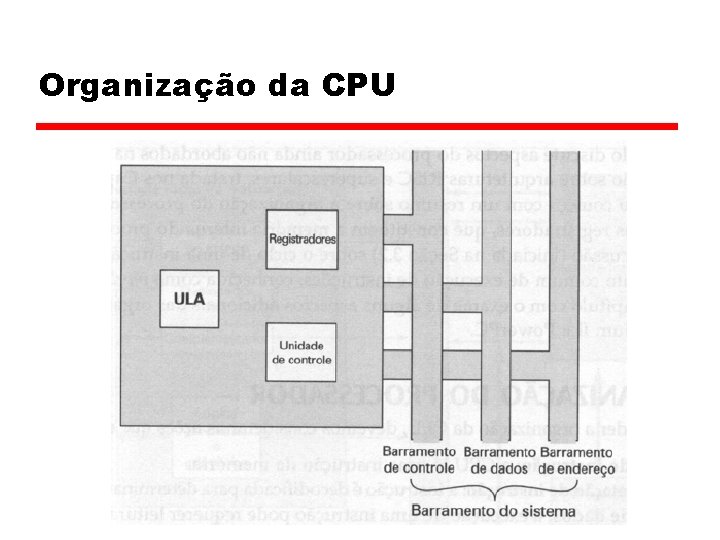

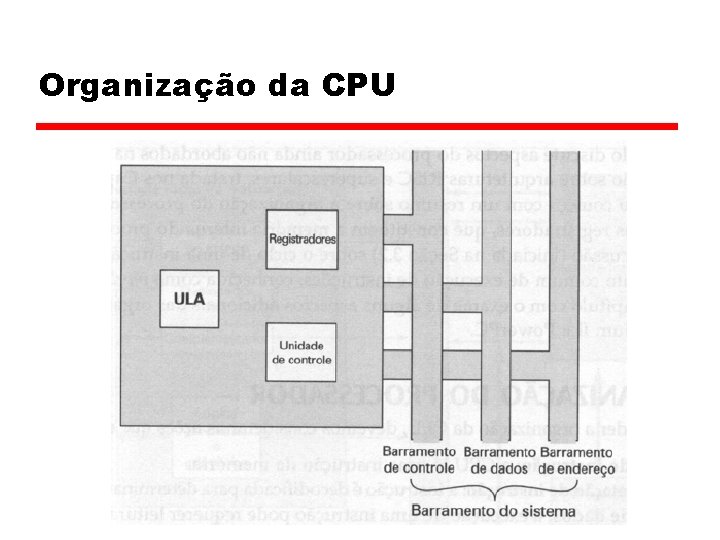

Organização da CPU

Funcionalidades da CPU q Em um ciclo de instruções, envolve-se: • Buscar instruções § CPU lê uma instrução da memória • Interpretar instruções § Instrução é decodificada para determinar a ação requerida • Buscar dados § Busca dados na memória ou dispositivos de E/S • Processar dados § Execução de uma instrução sobre os dados • Escrever dados § Escrever dados na memória ou dispositivos

Registradores q A CPU deve ter algum espaço para trabalho • armazenamento temporário q Registradores • Número e funções dos registradores variam entre os projetos dos processadores • Uma das mais importantes decisões de projeto q Duas funções: • Registradores visíveis ao usuário • Registradores de controle e de estado

Registradores visíveis ao usuário q q Podem ser referenciados pela linguagem de máquina que a CPU executa Categorias: • • De propósito geral Dados Endereços Códigos de condição

Registradores de propósito geral q q q Podem ser usados para uma variedade de funções Qualquer registrador pode conter um operando para uma instrução qualquer Excessões: • Números em ponto flutuante • Operações com a pilha q Podem ainda ser utilizados para endereçamento

Registradores de Dados q q Usados apenas para dados Não podem ser utilizados no cálculo de endereço de operandos

Registradores de Endereço q Utilizados para endereçamento • Podem ser utilizados como registradores de propósito geral q Exemplos: • Registrador de segmento • Registradores de Índices • Apontador para o topo da pilha

Registradores de propósito geral: prós e contras q Qual o limite entre definir registradores de propósito geral ou específicos? • Propósito geral: maximiza a flexibilidade das instruções • Propósito específico: a execução de operação busca o registrador específico, sendo necessário somente definir qual o registrador específico • Não existe a melhor solução

Quantos registradores são suficientes? q Mais registradores • permite mais operandos serem tratados na CPU • causam um aumento no tamanho do campo necessário para especificar o registrador na instrução q Menos registradores • mais referências a memória q Ideal • Entre 8 e 32 • RISC (centenas)

Qual o tamanho do registrador? q q Devem ser capazes de armazenar o maior endereço usado no sistema Registradores de dados devem ser capazes de conter valores da maioria dos tipos de dados • Por exemplo, não é necessário ter registradores de 64 bits se a maioria dos operações com dados utilizam operandos com 32 ou 16 bits

Registradores de Código de Condição q q Flags Conjunto de bits individuais • e. x. resultado da última operação é zero q Pode ser implicitamente lido por programas • e. x. Jump se zero q Não pode ser (normalmente) configurado por programas

Registradores de Controle e Status q Registradores utilizados durante as fases de busca, decodificação e execução das instruções • Muitos não são visíveis ao usuário • Alguns são visíveis mas não podem ser alterados § § Modo de controle Sistema Operacional

Registradores de Controle e Status q Contador de Programa • Program Counter - PC • Contém o endereço da instrução a ser buscada q Registrador de Instrução • Instruction Register – IR • Contém a última instrução buscada

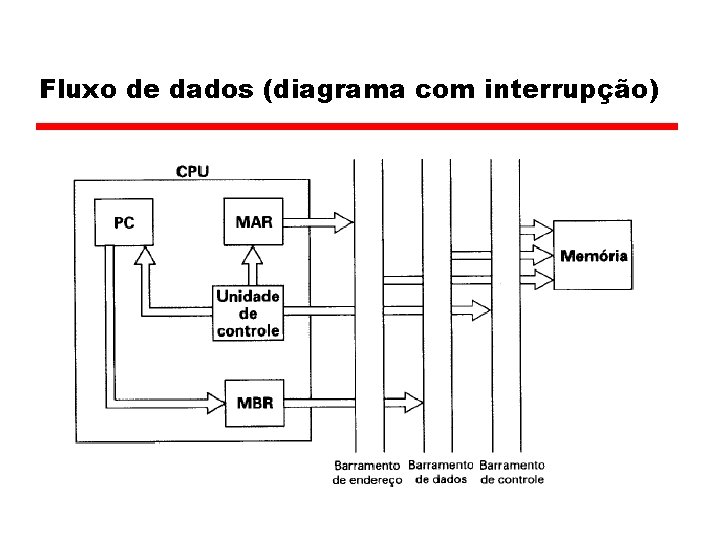

Registradores de Controle e Status q Registrador de endereçamento à memória • Memory address register - MAR • Contém o endereço de uma posição de memória q Registrador de armazenamento temporário de dados • Memory Data/Buffer Register – MBR • Contém uma palavra de dados a ser escrita na memória ou a palavra lida mais recentemente

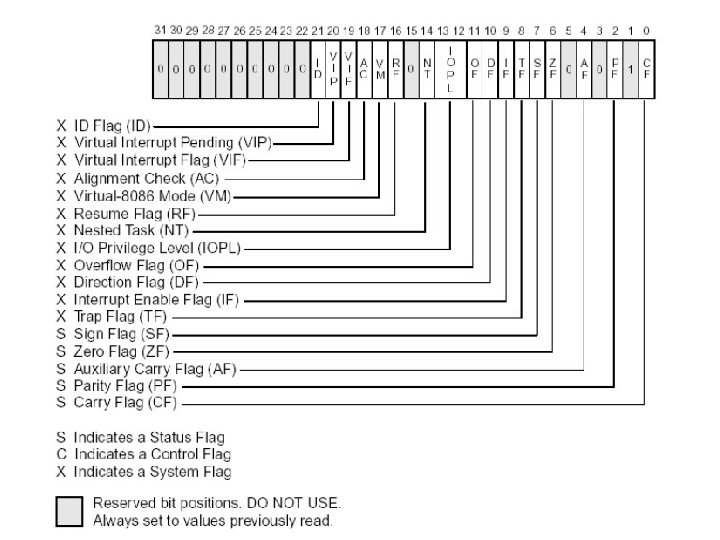

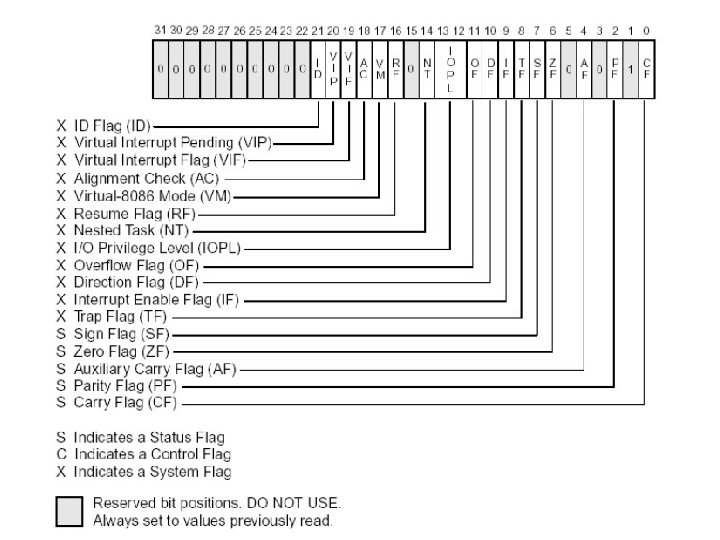

Registradores de Controle e Status q Palavra de estado de programa • Program Status Word – PSW • Contém informações de estado: § § § § Sinal: contém o bit de sinal da última operação Zero: indica se o resultado da última operação é zero “Vai-um” Igual: indica se uma comparação lógica resulta em igualdade Overflow: overflow aritmético Habilitar/Desabilitar interrupção Supervisor: indica se a CPU está executando em modo supervisor ou usuário

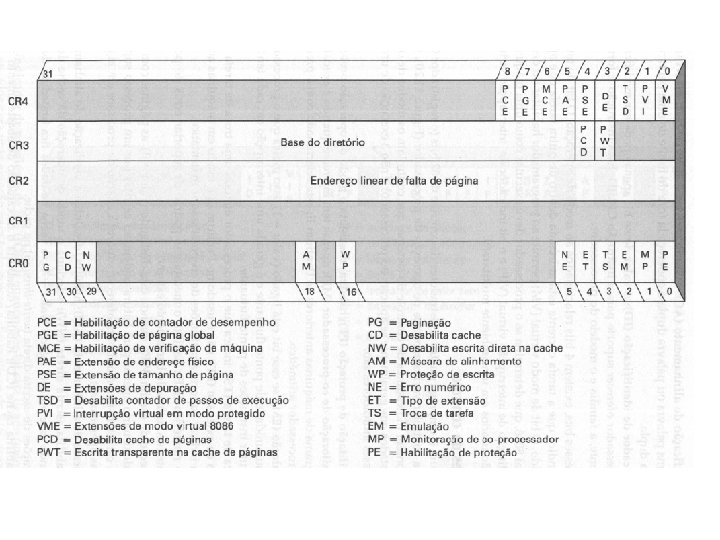

Outros registradores q Outros registradores relacionados ao estado e controle • Registrador para apontar para um bloco de memória que contém informação de estado adicional (ex. , blocos de controle de processos) • Vetor de interrupções • Registrador indicador de topo de pilha • Registrador para indicar tabela de páginas (no caso de memória virtual)

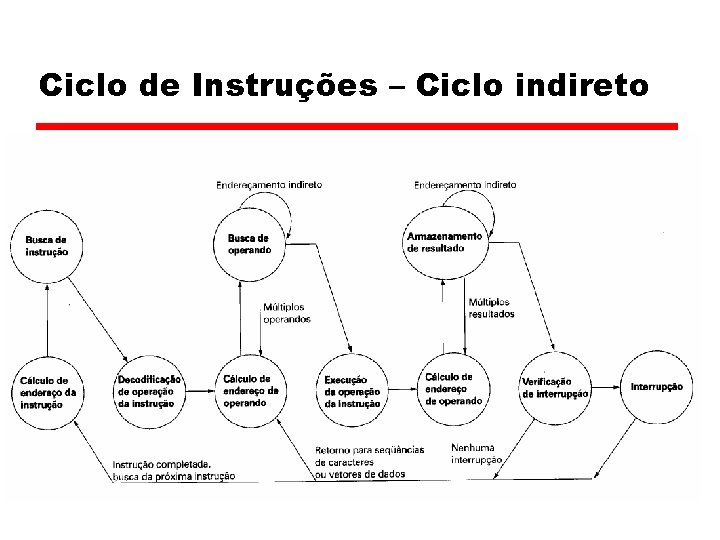

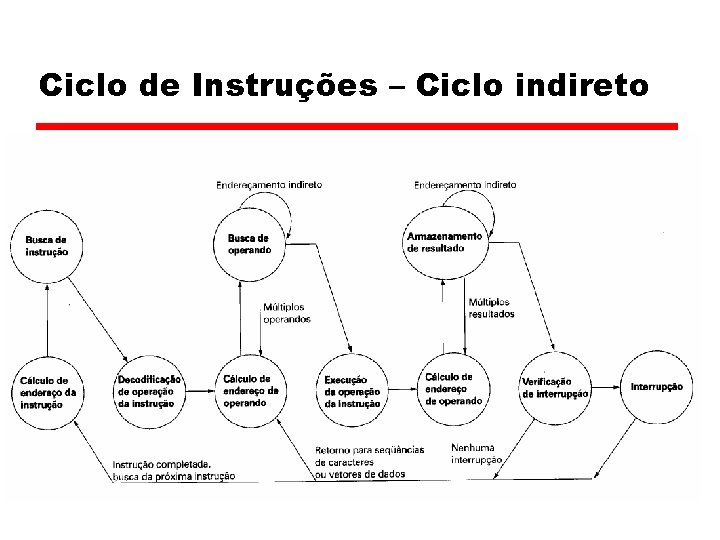

Ciclo de Instruções – Ciclo indireto

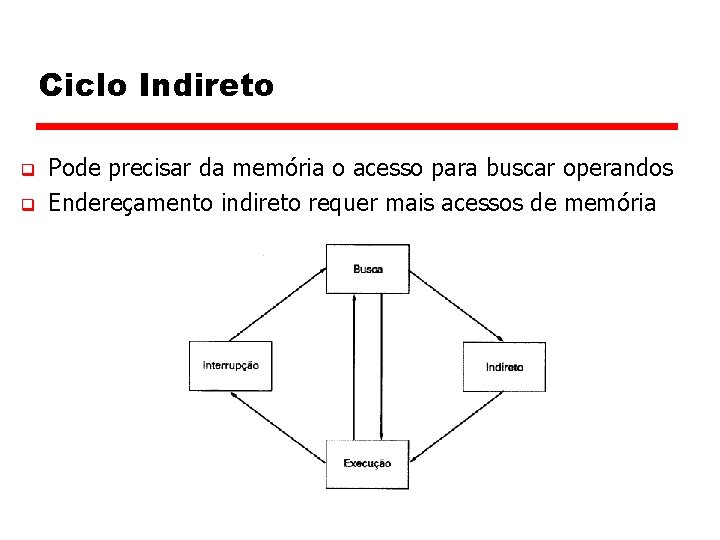

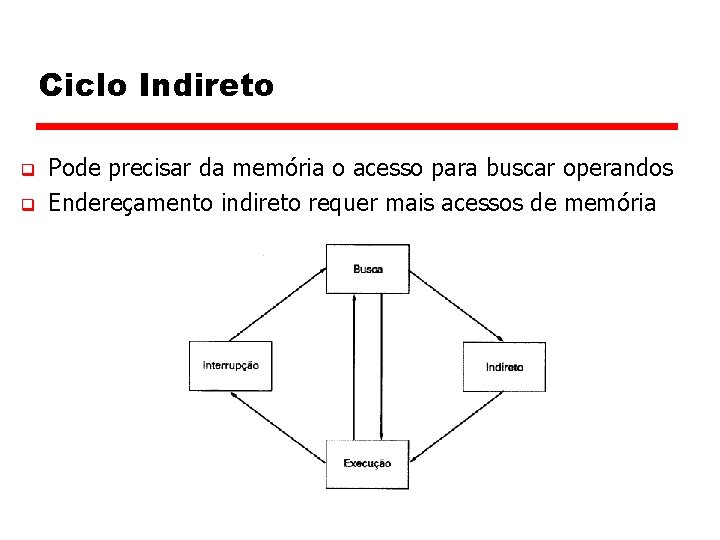

Ciclo Indireto q q Pode precisar da memória o acesso para buscar operandos Endereçamento indireto requer mais acessos de memória

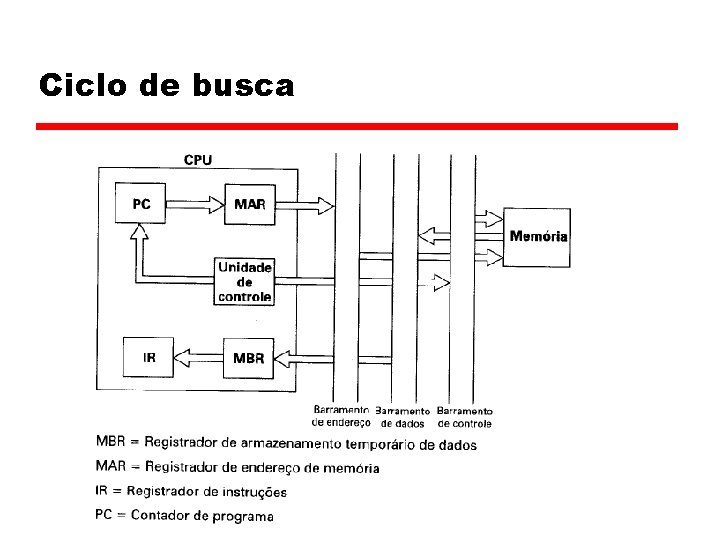

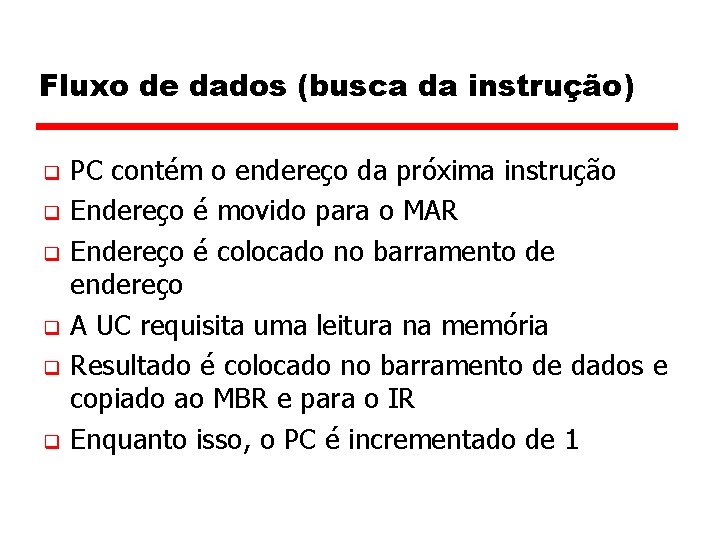

Fluxo de dados (busca da instrução) q q q PC contém o endereço da próxima instrução Endereço é movido para o MAR Endereço é colocado no barramento de endereço A UC requisita uma leitura na memória Resultado é colocado no barramento de dados e copiado ao MBR e para o IR Enquanto isso, o PC é incrementado de 1

Ciclo de busca

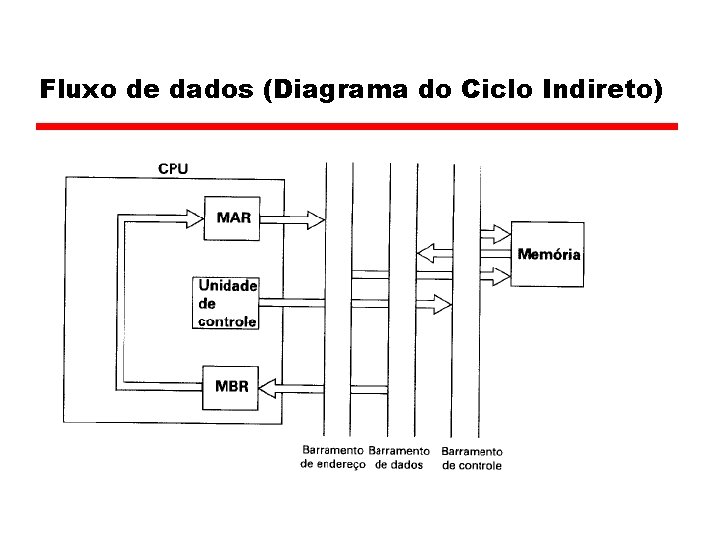

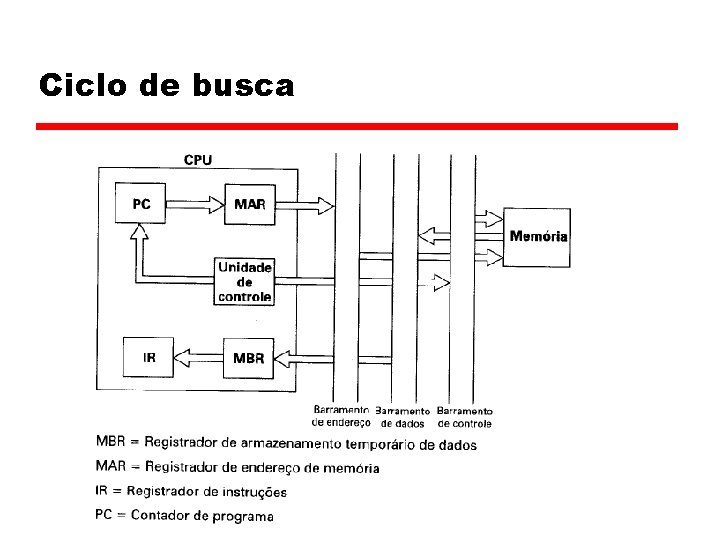

Fluxo de dados (busca de instruções) q q IR é examinado Se o endereçamento é indireto, o ciclo indireto é feito • Os N bits mais significativos de MBR são transferidos para MAR • A unidade de controle envia um pedido de leitura da memória • O resultado (endereço ou operando) é movido para o MBR

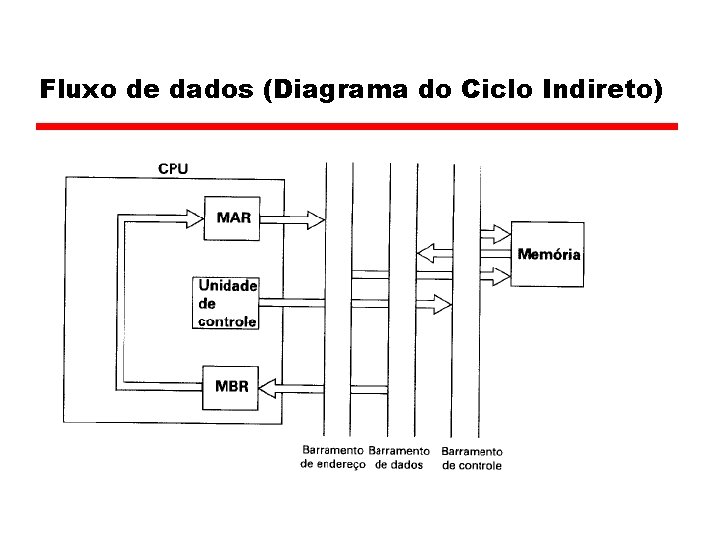

Fluxo de dados (Diagrama do Ciclo Indireto)

Fluxo de dados (Execução) q q q Pode ter várias formas Depende da instrução que está sendo executada Deve incluir • • escrita/leitura da memória Entrada/Saída Transferência entre registradores Operações da ULA

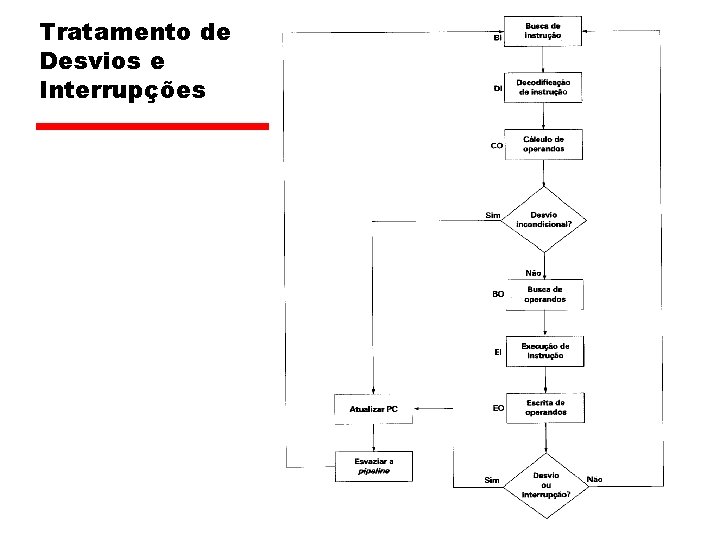

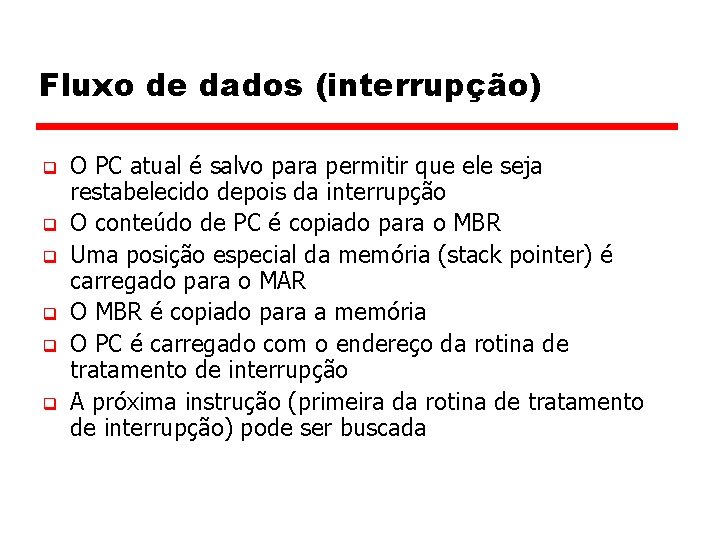

Fluxo de dados (interrupção) q q q O PC atual é salvo para permitir que ele seja restabelecido depois da interrupção O conteúdo de PC é copiado para o MBR Uma posição especial da memória (stack pointer) é carregado para o MAR O MBR é copiado para a memória O PC é carregado com o endereço da rotina de tratamento de interrupção A próxima instrução (primeira da rotina de tratamento de interrupção) pode ser buscada

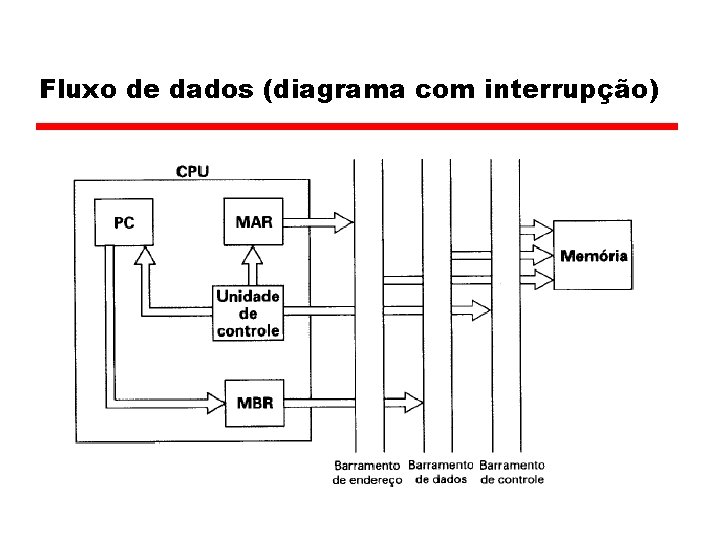

Fluxo de dados (diagrama com interrupção)

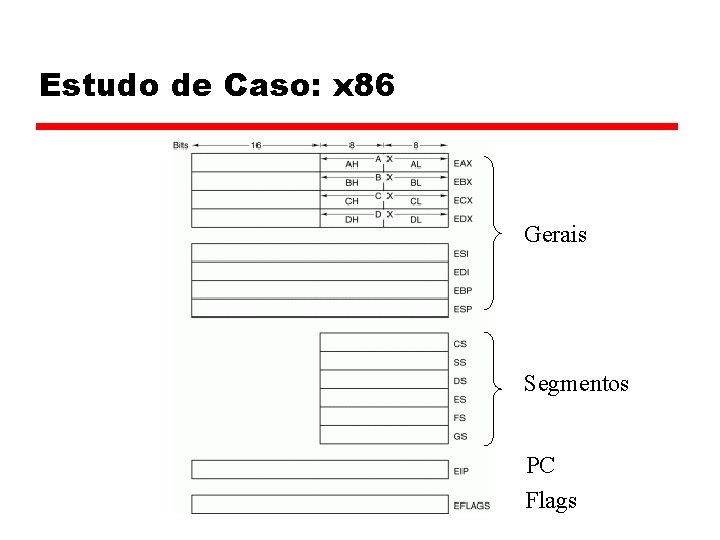

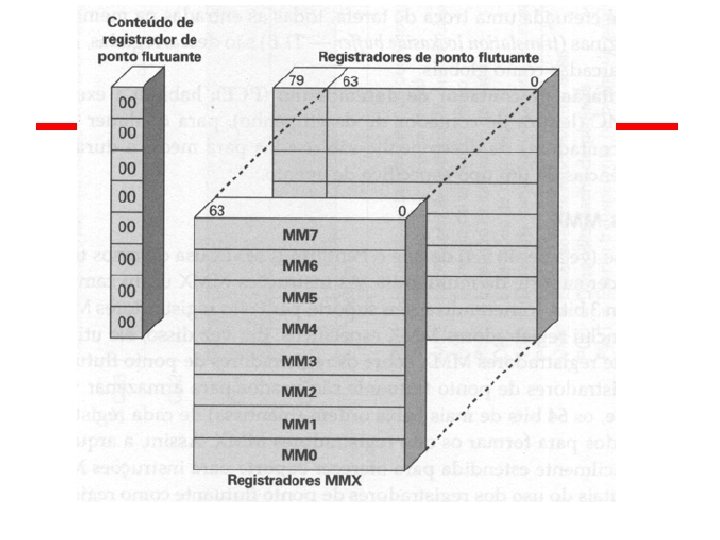

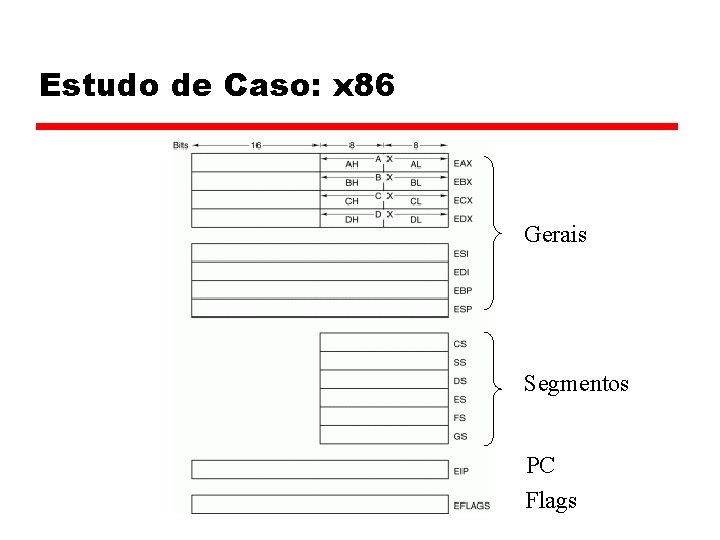

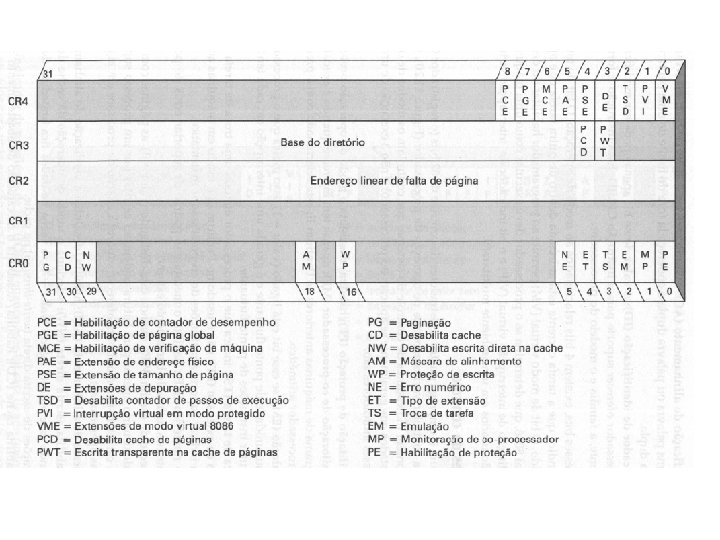

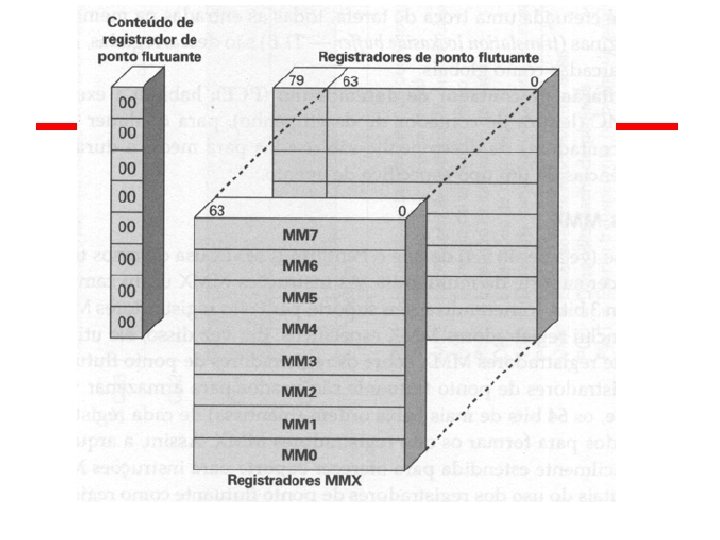

Estudo de Caso: x 86 Gerais Segmentos PC Flags

PSW

PSW

Exercícios q 11. 1

Parte II Pipeline

Pipeline q Evolução dos sistemas: • • Novos chips Mais registradores Cache Pipeline de Instruções

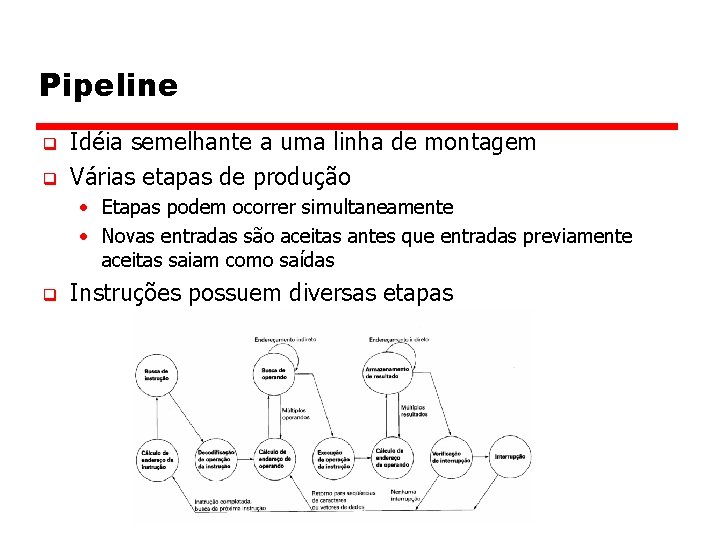

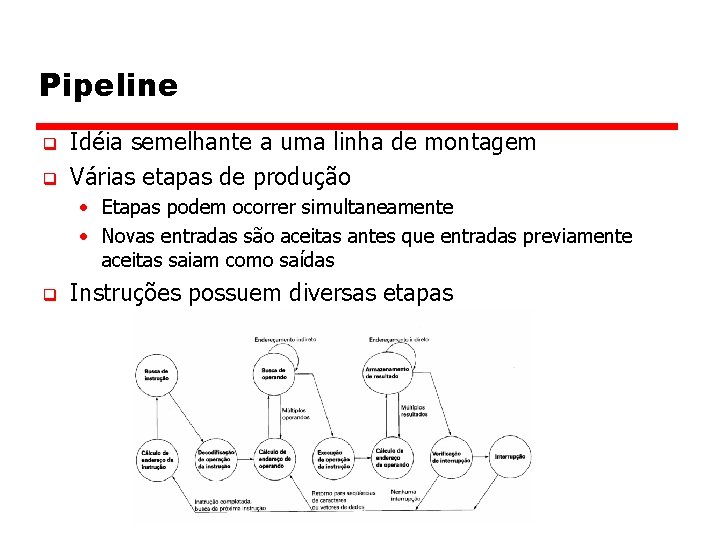

Pipeline q q Idéia semelhante a uma linha de montagem Várias etapas de produção • Etapas podem ocorrer simultaneamente • Novas entradas são aceitas antes que entradas previamente aceitas saiam como saídas q Instruções possuem diversas etapas

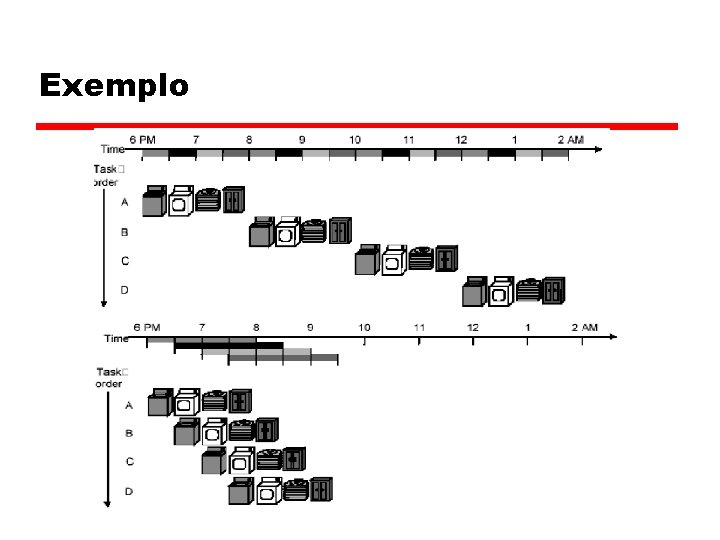

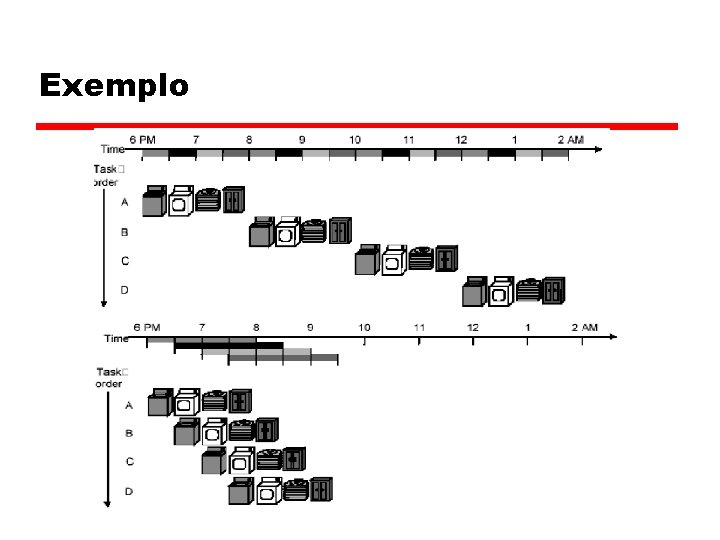

Exemplo

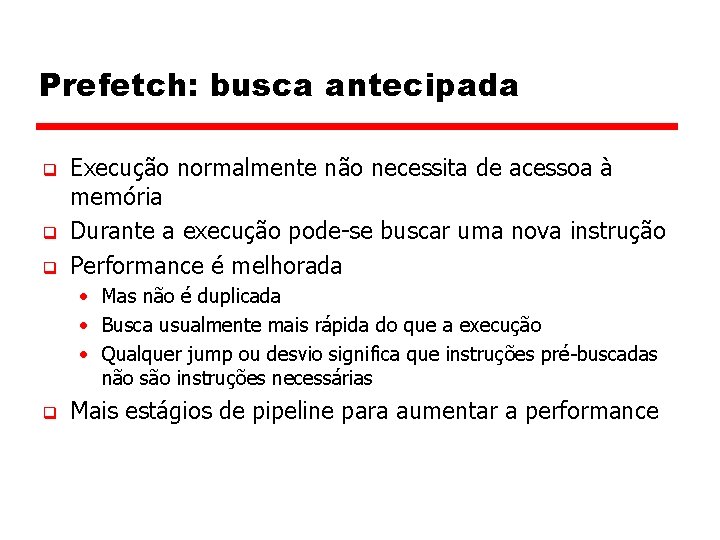

Prefetch: busca antecipada q q q Execução normalmente não necessita de acessoa à memória Durante a execução pode-se buscar uma nova instrução Performance é melhorada • Mas não é duplicada • Busca usualmente mais rápida do que a execução • Qualquer jump ou desvio significa que instruções pré-buscadas não são instruções necessárias q Mais estágios de pipeline para aumentar a performance

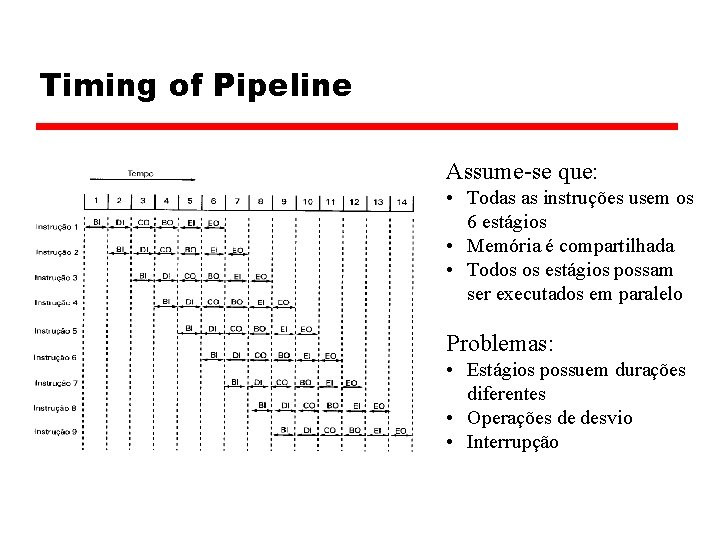

Pipelining q BI - Busca de instruções DI - Decodificação de instruções CO - Cálculo de operandos BO - Busca de operandos EI - Execução de instruções EO –Escrita de Operando q Sobreposição dessas operações q q q

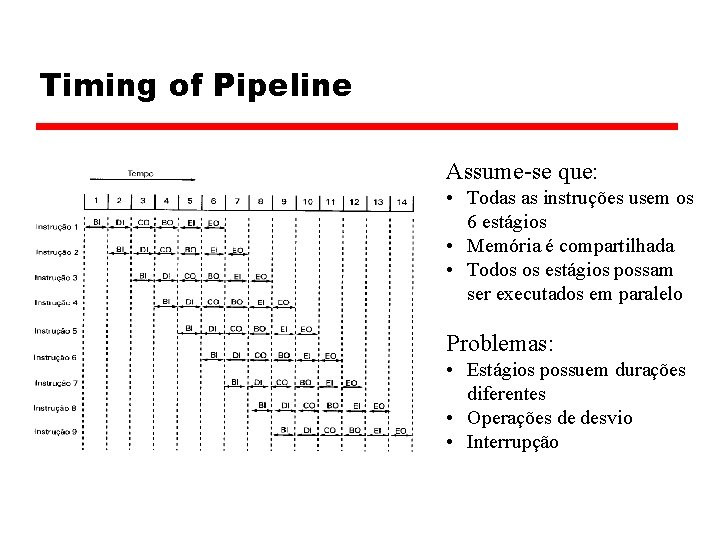

Timing of Pipeline Assume-se que: • Todas as instruções usem os 6 estágios • Memória é compartilhada • Todos os estágios possam ser executados em paralelo Problemas: • Estágios possuem durações diferentes • Operações de desvio • Interrupção

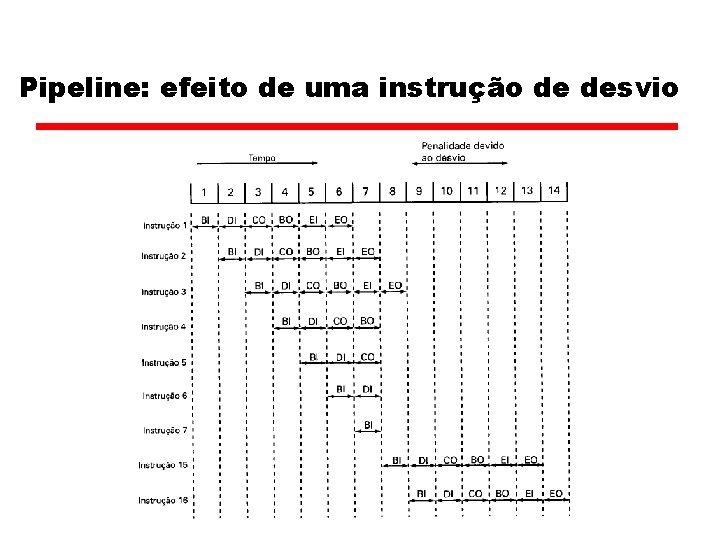

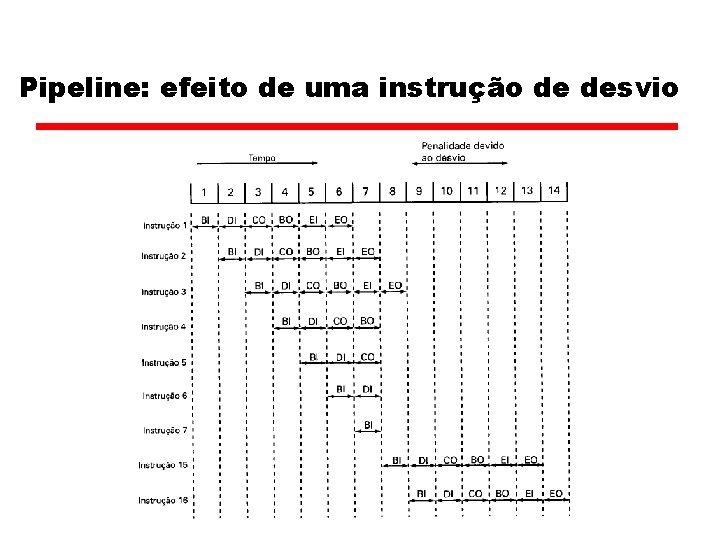

Pipeline: efeito de uma instrução de desvio

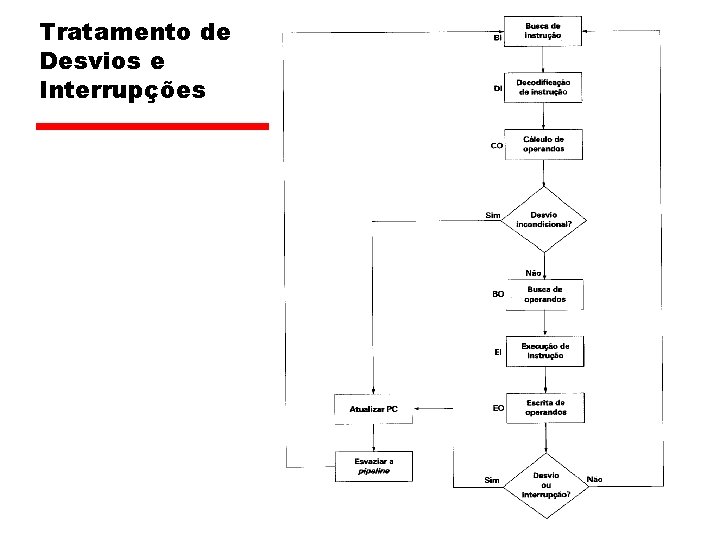

Tratamento de Desvios e Interrupções

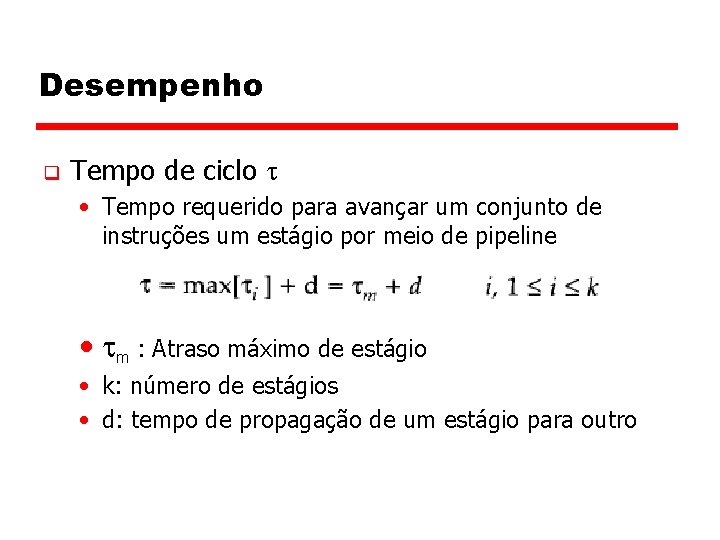

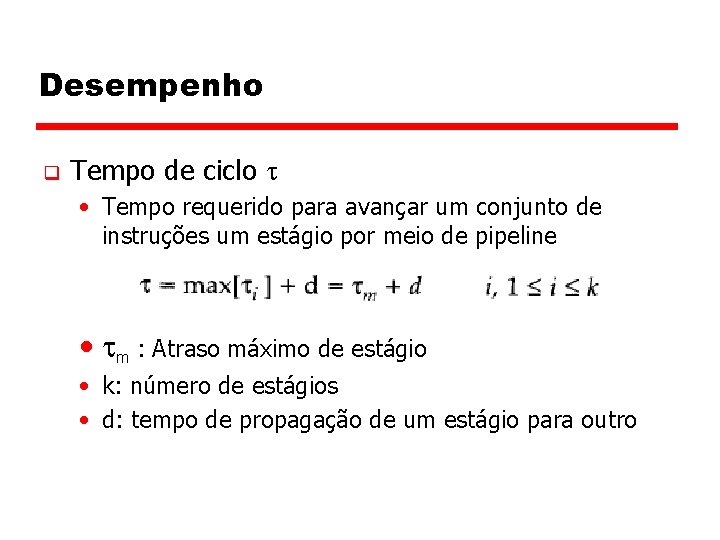

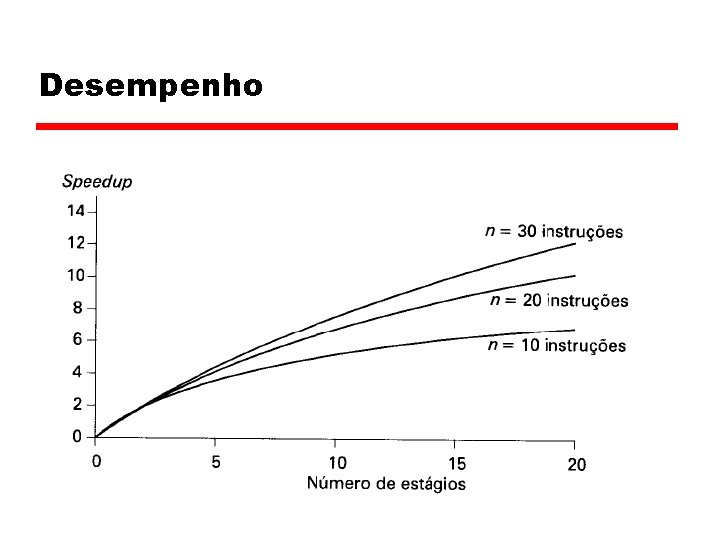

Desempenho q Tempo de ciclo • Tempo requerido para avançar um conjunto de instruções um estágio por meio de pipeline • m : Atraso máximo de estágio • k: número de estágios • d: tempo de propagação de um estágio para outro

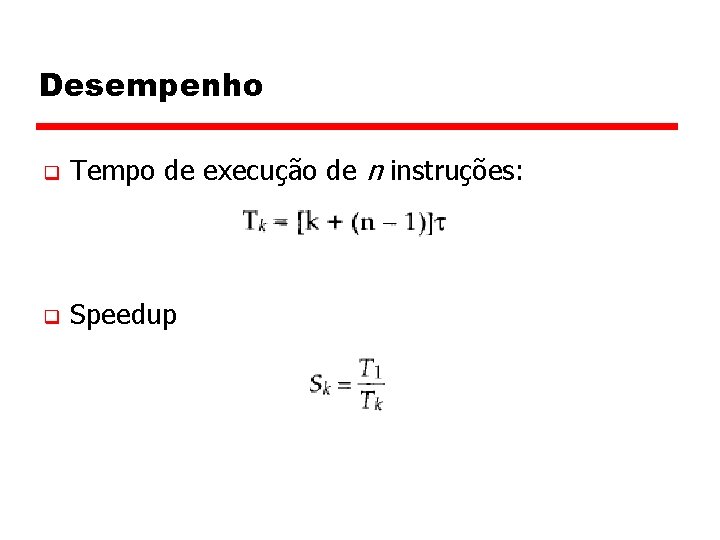

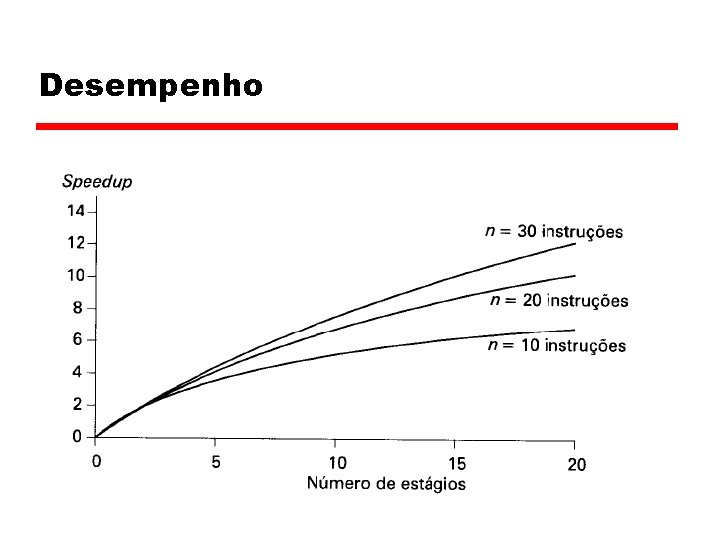

Desempenho q Tempo de execução de n instruções: q Speedup

Desempenho

Lidando com desvios q q Desvios: principal problema do uso de pipeline Algumas abordagens para amenizar o problema: • • • Múltiplos Fluxos Antecipação de busca da instrução alvo do desvio Memória para laços de repetição Previsão de Desvios Atraso de Desvio (delayed branch)

Múltiplos Fluxos q q Duplicar estágios iniciais do pipeline Pré-buscar cada desvio em pipelines separadas Utilizar as pipelines apropriadas Problemas: • Leva a contenção de registradores e do barramento • Múltiplos saltos levam a futuras necessidades dos pipelines

Antecipação de busca q q Destino dos desvios são buscados antecipadamente Mantém destino em um registrador até que o desvio seja executado

Memória para laços de repetição q q Uma memória rápida armazena as últimas n instruções Checa-se esta memória antes de buscar da memória principal Muito bom para pequenos loops ou jumps Funcionamento semelhante a uma cache de instruções

Previsão de Desvios q Várias técnicas: • Prever que desvios nunca serão tomados • Prever que desvios sempre serão tomados • Prever se desvios serão tomados ou não baseado no código da operação • Prever desvios com base em desvios tomados ou não tomados • Prever desvios baseados em históricos

Previsão de Desvios q Prever que desvios nunca serão tomados • Sempre busca a próxima instrução q Prever que desvios sempre serão tomados • Assume que aquele jump irá acontecer • Sempre busca a instrução de destino

Previsão de Branches q Previsto pelo código de operação • Algumas instruções são mais prováveis de resultarem em um jump do que outras • Tem alta taxa de acerto q Prever se desvios serão tomados ou não baseado no código da operação • Baseado na história prévia • Bom para loops

Previsão de Desvios q Desvios atrasados • Rearranja as instruções • Só executa quanto necessário

Pipeline do 486 q 5 estágios: • • • Busca de Instrução Decodificação 1 Decodificação 2 Execução de Instrução Escrita de Resultado

Exercícios (entregar final da aula) q q 11. 1 11. 2 11. 3 11. 6