Aula02 Arquitetura do conjunto de instrues ISA Instruction

![Exemplo ampliado swap(int v[], int k); { int temp; temp = v[k] = v[k+1]; Exemplo ampliado swap(int v[], int k); { int temp; temp = v[k] = v[k+1];](https://slidetodoc.com/presentation_image_h/72df42a38a504ebeffef9fc842f57684/image-6.jpg)

![Nosso Primeiro Exemplo swap(int v[], int k); { int temp; temp = v[k] = Nosso Primeiro Exemplo swap(int v[], int k); { int temp; temp = v[k] =](https://slidetodoc.com/presentation_image_h/72df42a38a504ebeffef9fc842f57684/image-16.jpg)

- Slides: 38

Aula-02 Arquitetura do conjunto de instruções – ISA (Instruction Set Architecture)

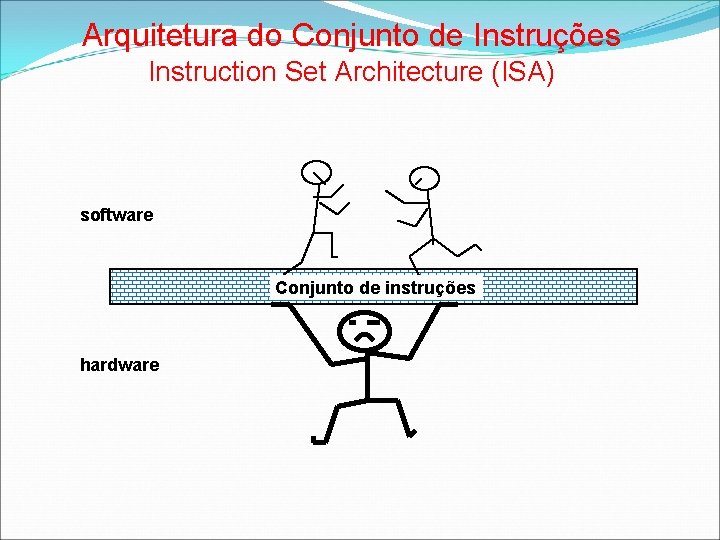

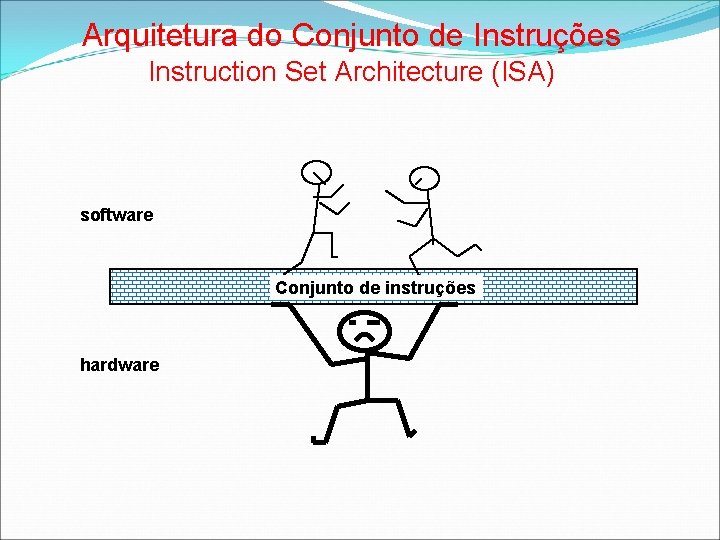

Arquitetura do Conjunto de Instruções Instruction Set Architecture (ISA) software Conjunto de instruções hardware

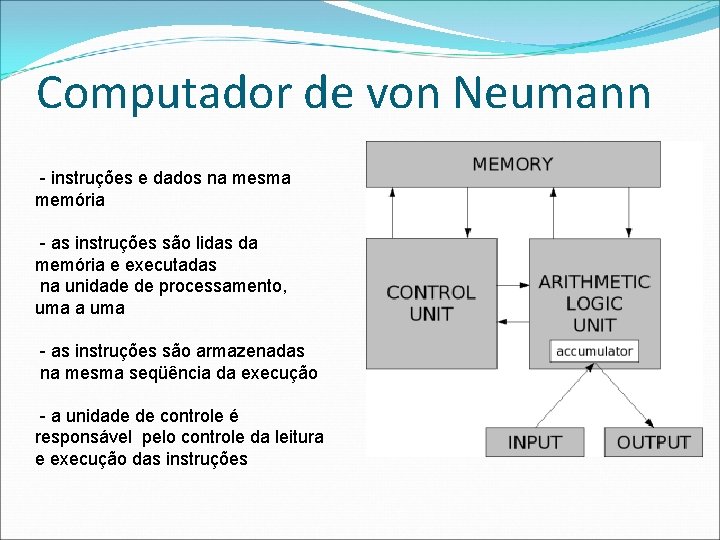

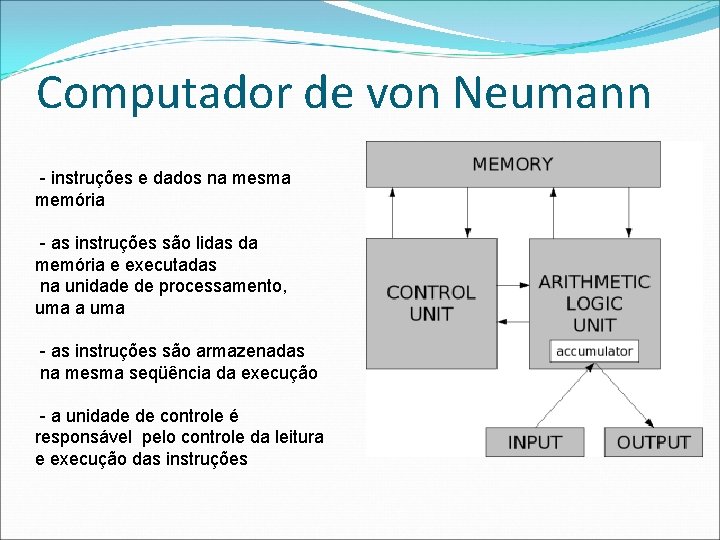

Computador de von Neumann - instruções e dados na mesma memória - as instruções são lidas da memória e executadas na unidade de processamento, uma a uma - as instruções são armazenadas na mesma seqüência da execução - a unidade de controle é responsável pelo controle da leitura e execução das instruções

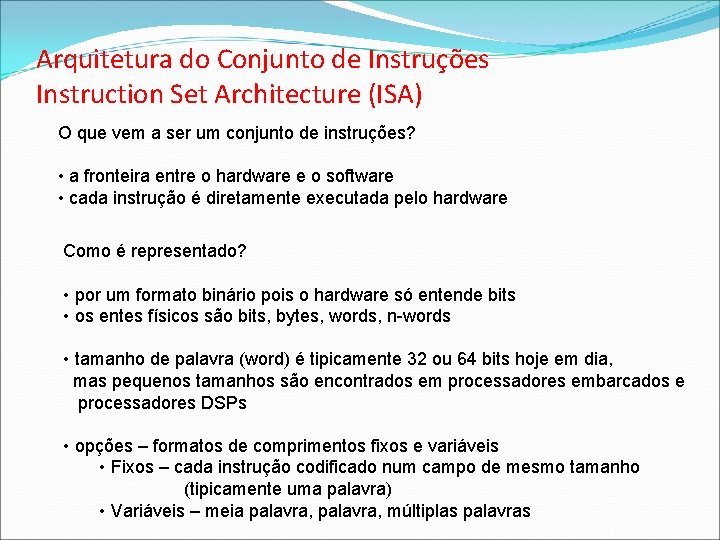

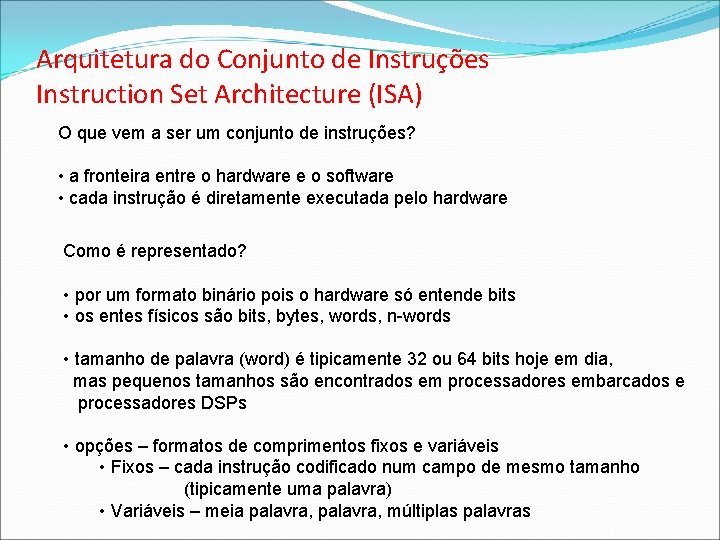

Arquitetura do Conjunto de Instruções Instruction Set Architecture (ISA) O que vem a ser um conjunto de instruções? • a fronteira entre o hardware e o software • cada instrução é diretamente executada pelo hardware Como é representado? • por um formato binário pois o hardware só entende bits • os entes físicos são bits, bytes, words, n-words • tamanho de palavra (word) é tipicamente 32 ou 64 bits hoje em dia, mas pequenos tamanhos são encontrados em processadores embarcados e processadores DSPs • opções – formatos de comprimentos fixos e variáveis • Fixos – cada instrução codificado num campo de mesmo tamanho (tipicamente uma palavra) • Variáveis – meia palavra, múltiplas palavras

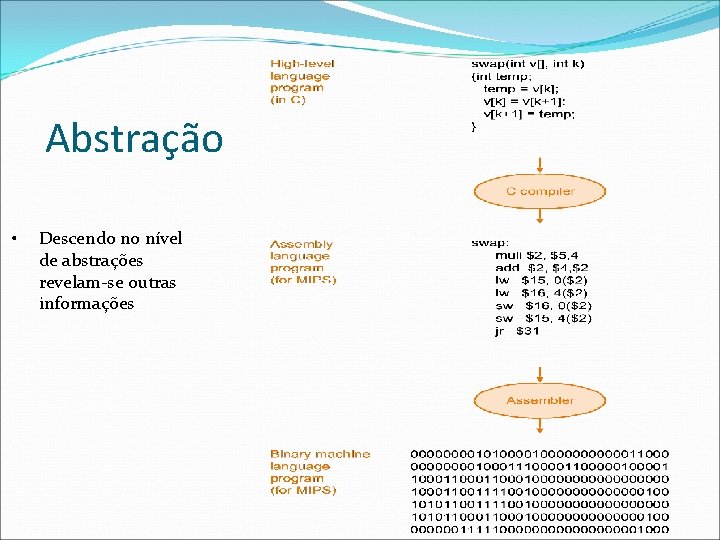

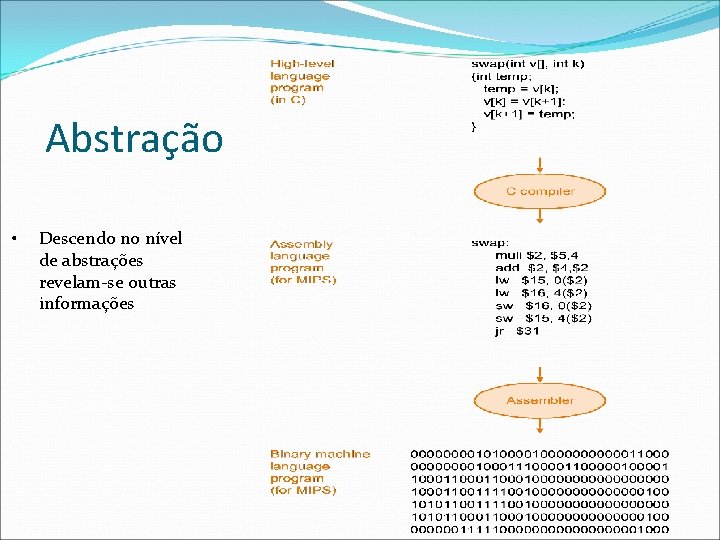

Abstração • Descendo no nível de abstrações revelam-se outras informações

![Exemplo ampliado swapint v int k int temp temp vk vk1 Exemplo ampliado swap(int v[], int k); { int temp; temp = v[k] = v[k+1];](https://slidetodoc.com/presentation_image_h/72df42a38a504ebeffef9fc842f57684/image-6.jpg)

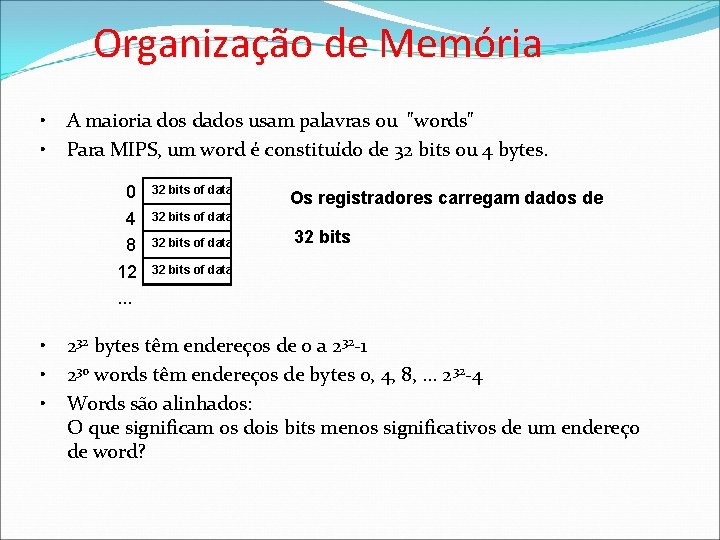

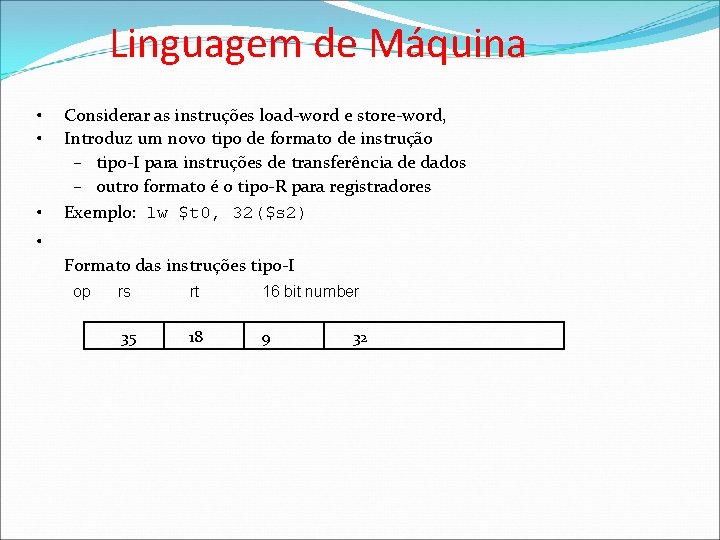

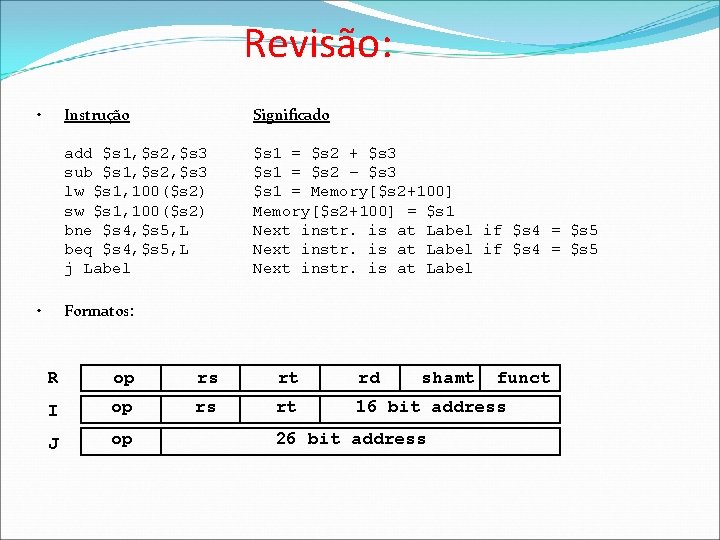

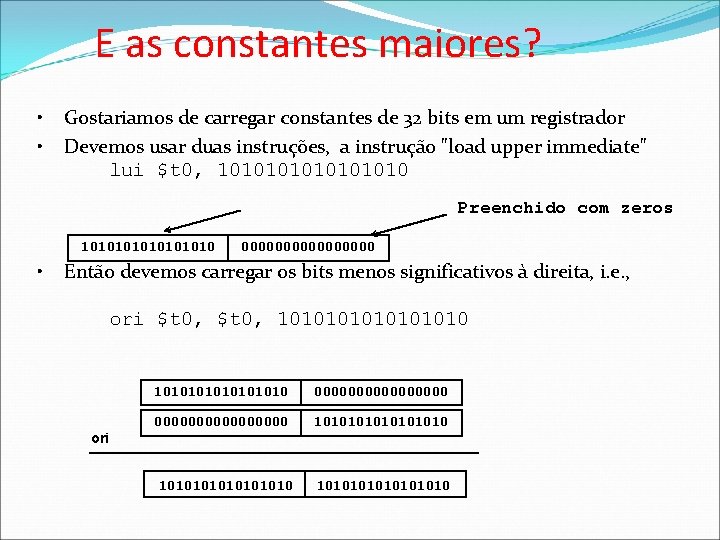

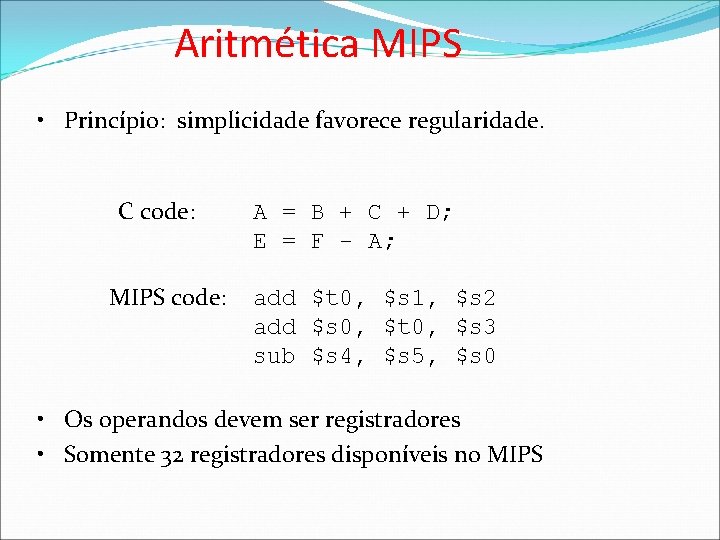

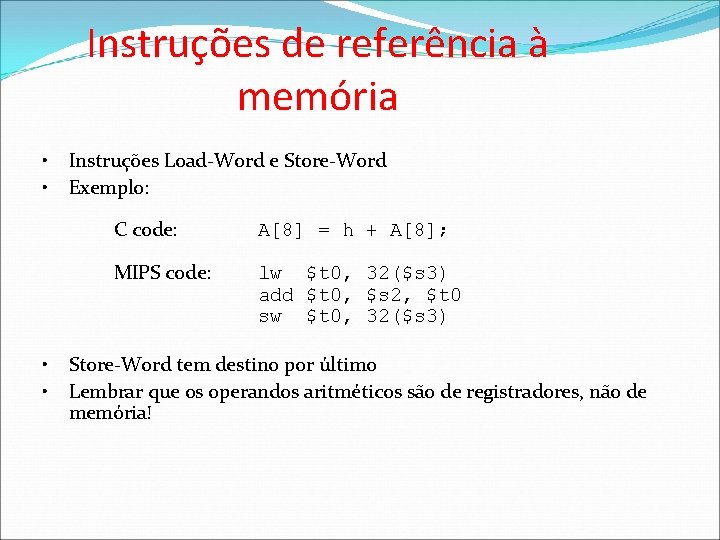

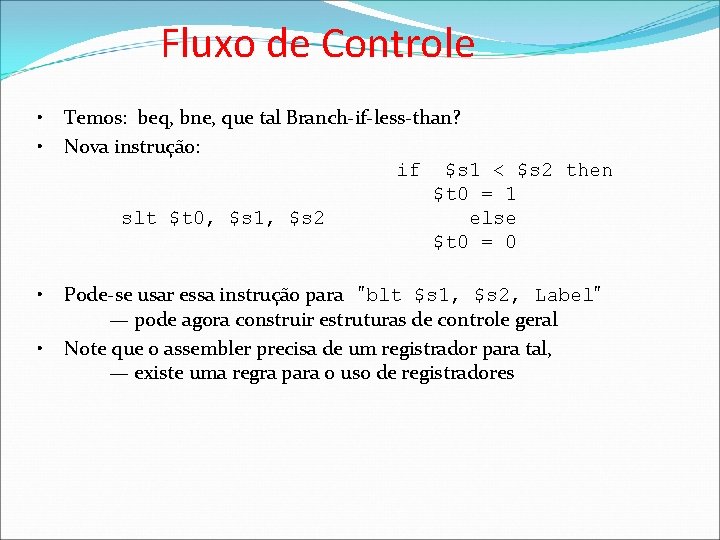

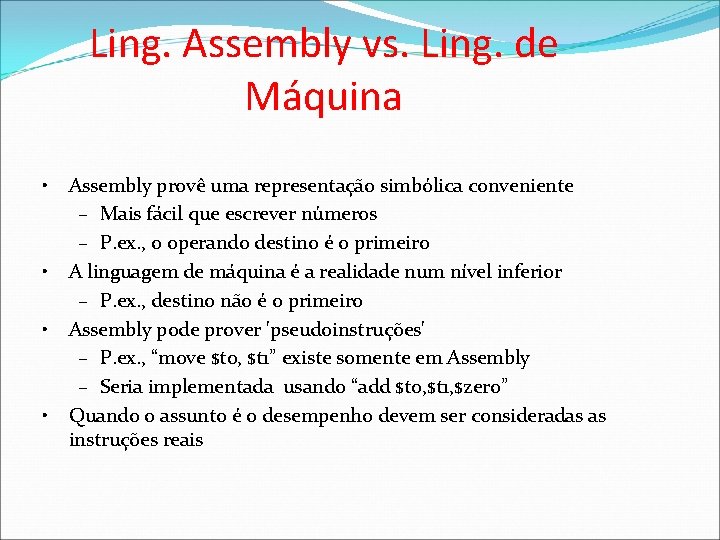

Exemplo ampliado swap(int v[], int k); { int temp; temp = v[k] = v[k+1]; } v[k+1] = temp; swap: muli $2, $5, 4 add $2, $4, $2 lw $15, 0($2) lw $16, 4($2) sw $16, 0($2) sw $15, 4($2) jr $31

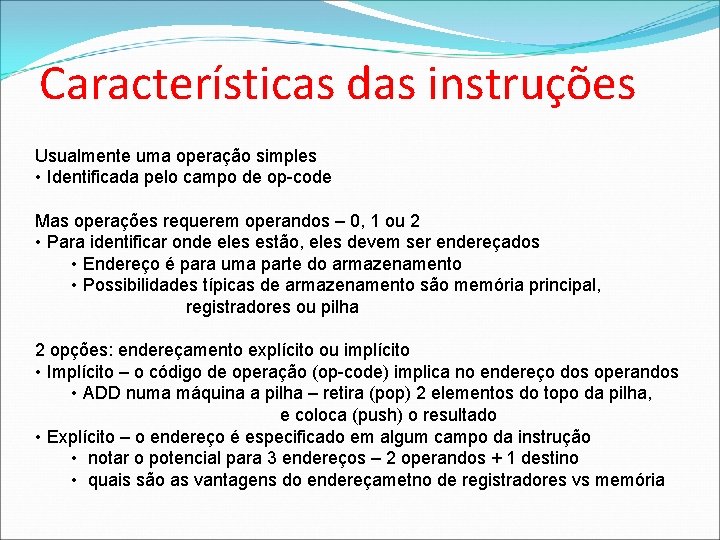

Características das instruções Usualmente uma operação simples • Identificada pelo campo de op-code Mas operações requerem operandos – 0, 1 ou 2 • Para identificar onde eles estão, eles devem ser endereçados • Endereço é para uma parte do armazenamento • Possibilidades típicas de armazenamento são memória principal, registradores ou pilha 2 opções: endereçamento explícito ou implícito • Implícito – o código de operação (op-code) implica no endereço dos operandos • ADD numa máquina a pilha – retira (pop) 2 elementos do topo da pilha, e coloca (push) o resultado • Explícito – o endereço é especificado em algum campo da instrução • notar o potencial para 3 endereços – 2 operandos + 1 destino • quais são as vantagens do endereçametno de registradores vs memória

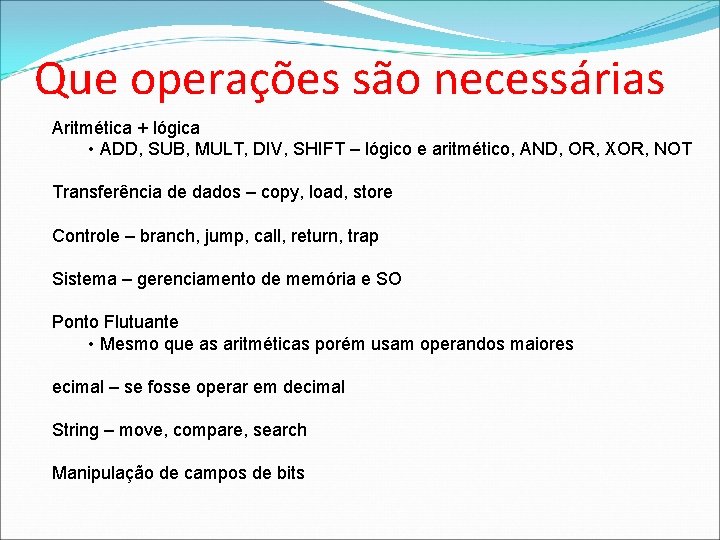

Que operações são necessárias Aritmética + lógica • ADD, SUB, MULT, DIV, SHIFT – lógico e aritmético, AND, OR, XOR, NOT Transferência de dados – copy, load, store Controle – branch, jump, call, return, trap Sistema – gerenciamento de memória e SO Ponto Flutuante • Mesmo que as aritméticas porém usam operandos maiores ecimal – se fosse operar em decimal String – move, compare, search Manipulação de campos de bits

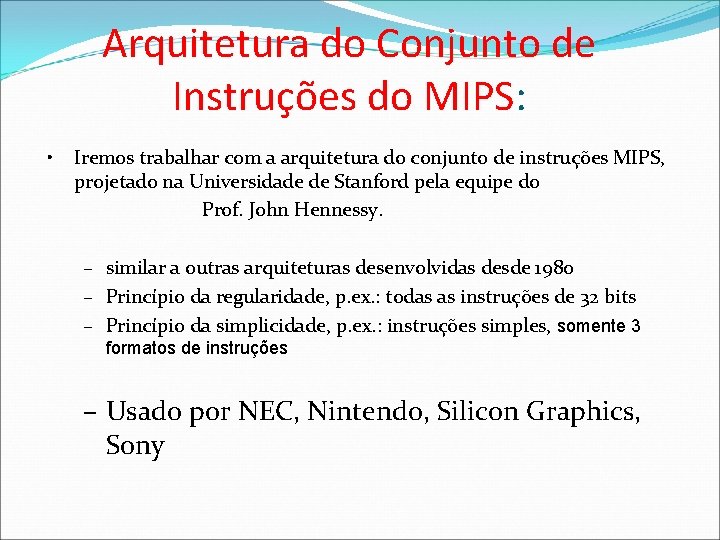

Arquitetura do Conjunto de Instruções do MIPS: • Iremos trabalhar com a arquitetura do conjunto de instruções MIPS, projetado na Universidade de Stanford pela equipe do Prof. John Hennessy. – similar a outras arquiteturas desenvolvidas desde 1980 – Princípio da regularidade, p. ex. : todas as instruções de 32 bits – Princípio da simplicidade, p. ex. : instruções simples, somente 3 formatos de instruções – Usado por NEC, Nintendo, Silicon Graphics, Sony

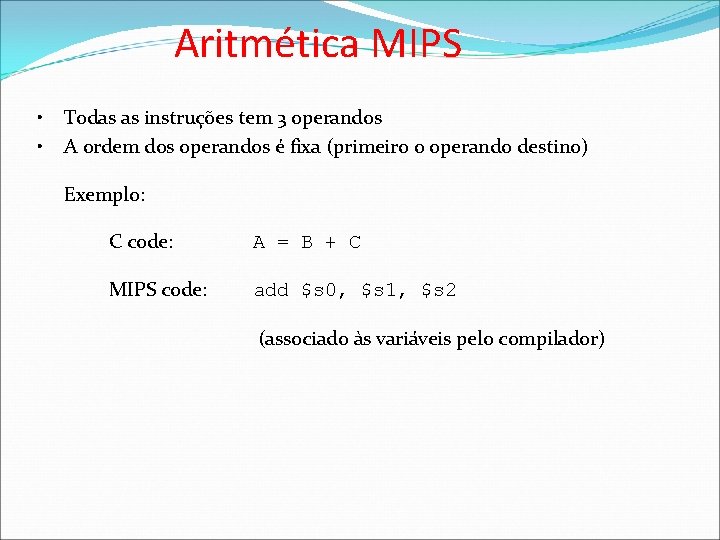

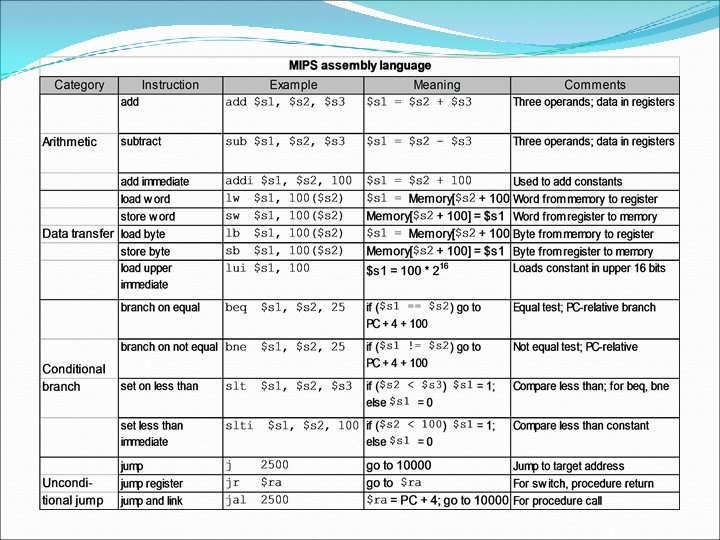

Aritmética MIPS • • Todas as instruções tem 3 operandos A ordem dos operandos é fixa (primeiro o operando destino) Exemplo: C code: A = B + C MIPS code: add $s 0, $s 1, $s 2 (associado às variáveis pelo compilador)

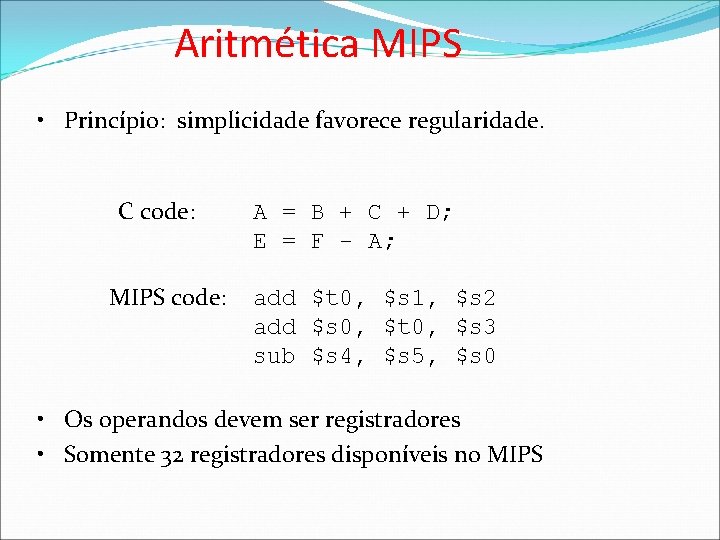

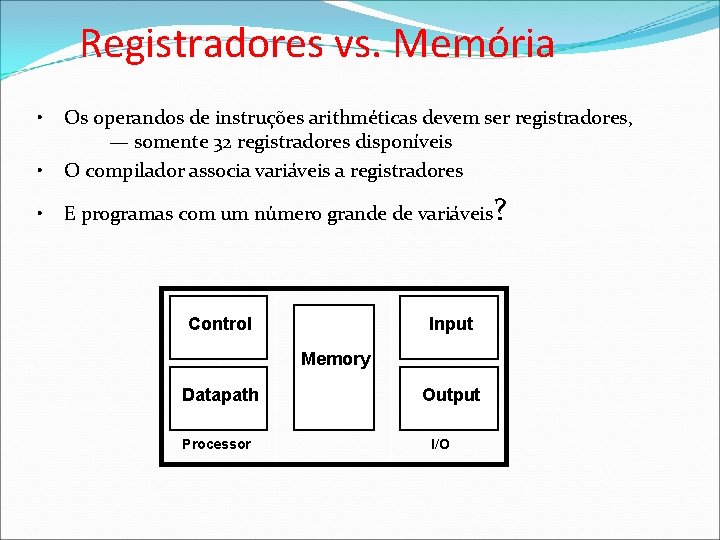

Aritmética MIPS • Princípio: simplicidade favorece regularidade. C code: MIPS code: A = B + C + D; E = F - A; add $t 0, $s 1, $s 2 add $s 0, $t 0, $s 3 sub $s 4, $s 5, $s 0 • Os operandos devem ser registradores • Somente 32 registradores disponíveis no MIPS

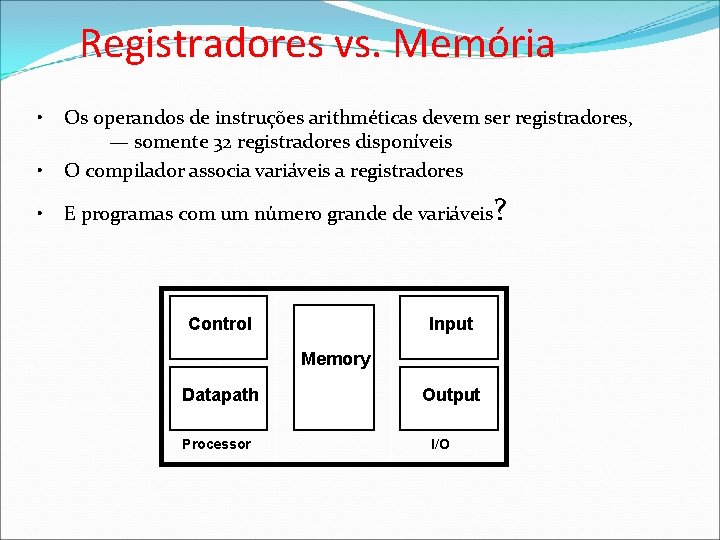

Registradores vs. Memória • • Os operandos de instruções arithméticas devem ser registradores, — somente 32 registradores disponíveis O compilador associa variáveis a registradores • E programas com um número grande de variáveis Control Input Memory Datapath Processor Output I/O ?

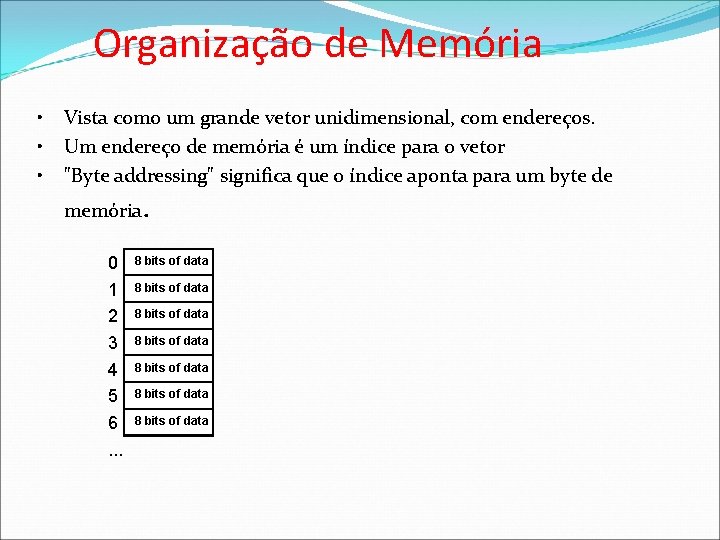

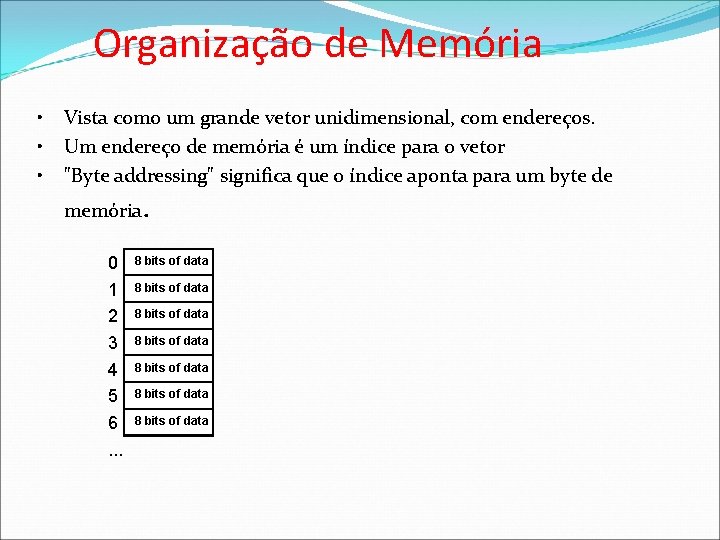

Organização de Memória • • • Vista como um grande vetor unidimensional, com endereços. Um endereço de memória é um índice para o vetor "Byte addressing" significa que o índice aponta para um byte de memória 0 1 2 3 4 5 6. . 8 bits of data 8 bits of data

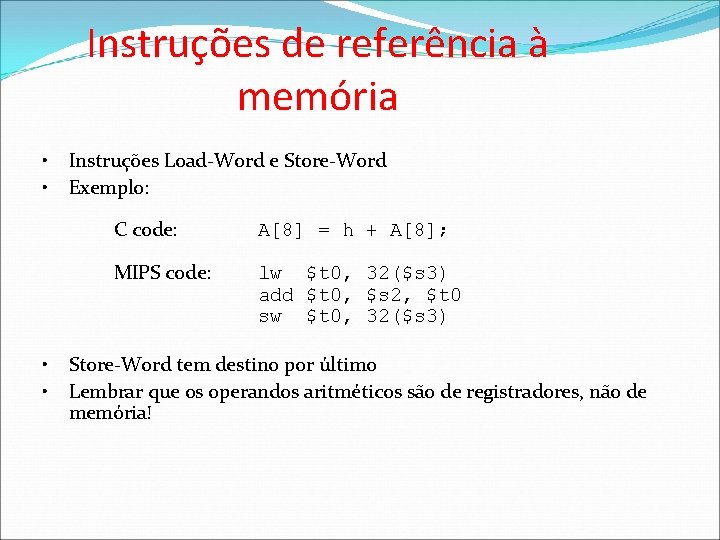

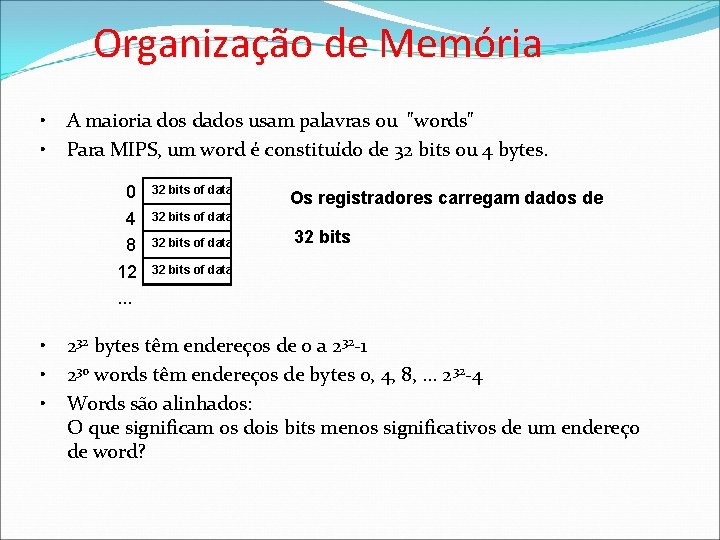

Organização de Memória • • A maioria dos dados usam palavras ou "words" Para MIPS, um word é constituído de 32 bits ou 4 bytes. 0 4 8 12. . . • • • 32 bits of data Os registradores carregam dados de 32 bits of data 232 bytes têm endereços de 0 a 232 -1 230 words têm endereços de bytes 0, 4, 8, . . . 232 -4 Words são alinhados: O que significam os dois bits menos significativos de um endereço de word?

Instruções de referência à memória • • Instruções Load-Word e Store-Word Exemplo: C code: A[8] = h + A[8]; MIPS code: lw $t 0, 32($s 3) add $t 0, $s 2, $t 0 sw $t 0, 32($s 3) Store-Word tem destino por último Lembrar que os operandos aritméticos são de registradores, não de memória!

![Nosso Primeiro Exemplo swapint v int k int temp temp vk Nosso Primeiro Exemplo swap(int v[], int k); { int temp; temp = v[k] =](https://slidetodoc.com/presentation_image_h/72df42a38a504ebeffef9fc842f57684/image-16.jpg)

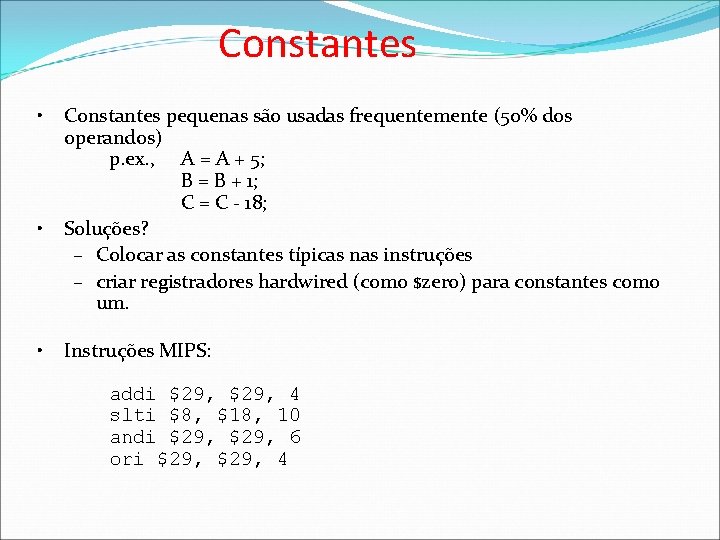

Nosso Primeiro Exemplo swap(int v[], int k); { int temp; temp = v[k] = v[k+1]; } v[k+1] = temp; swap: muli $2, $5, 4 add $2, $4, $2 lw $15, 0($2) lw $16, 4($2) sw $16, 0($2) sw $15, 4($2) jr $31

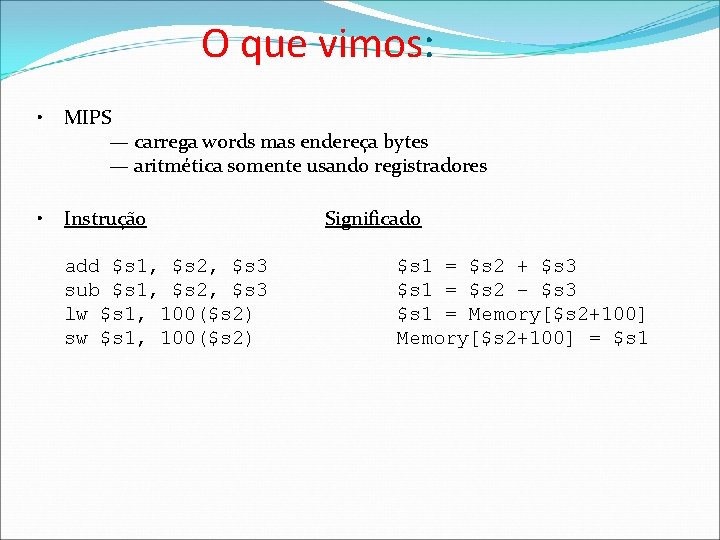

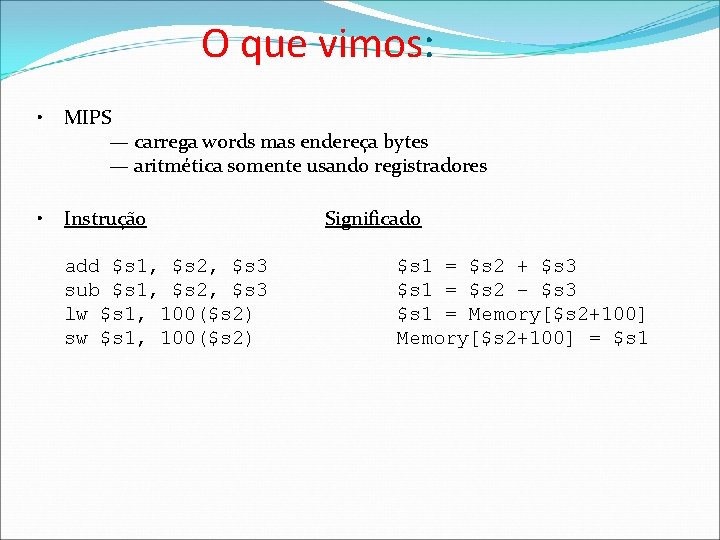

O que vimos: • MIPS — carrega words mas endereça bytes — aritmética somente usando registradores • Instrução add $s 1, $s 2, $s 3 sub $s 1, $s 2, $s 3 lw $s 1, 100($s 2) sw $s 1, 100($s 2) Significado $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = Memory[$s 2+100] = $s 1

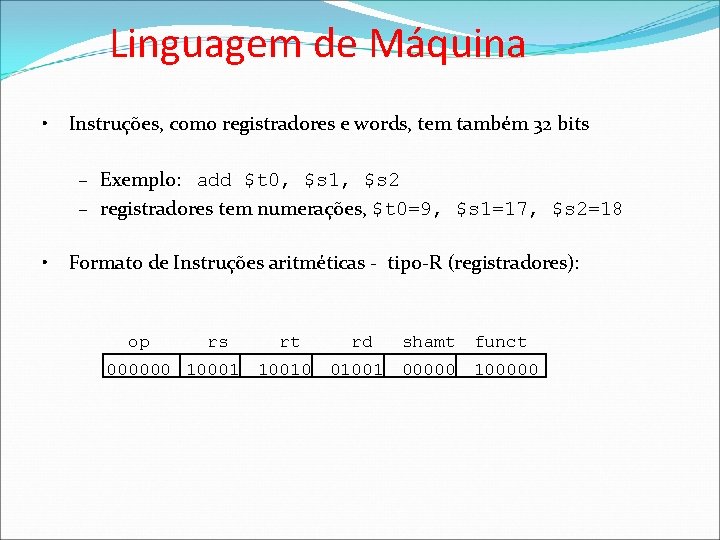

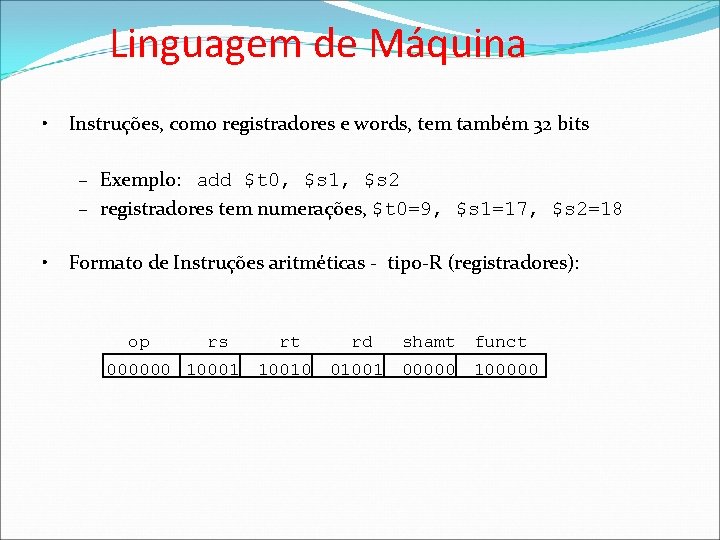

Linguagem de Máquina • Instruções, como registradores e words, tem também 32 bits – Exemplo: add $t 0, $s 1, $s 2 – registradores tem numerações, $t 0=9, $s 1=17, $s 2=18 • Formato de Instruções aritméticas - tipo-R (registradores): op rs rt rd shamt funct 000000 10001 10010 01001 00000 100000

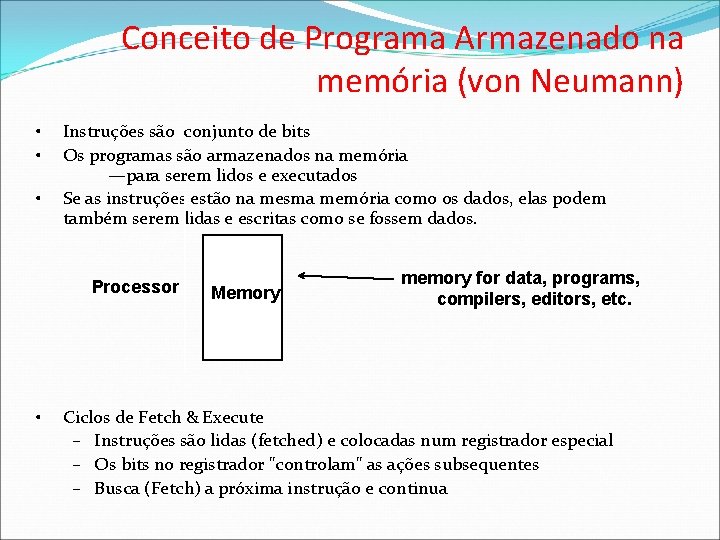

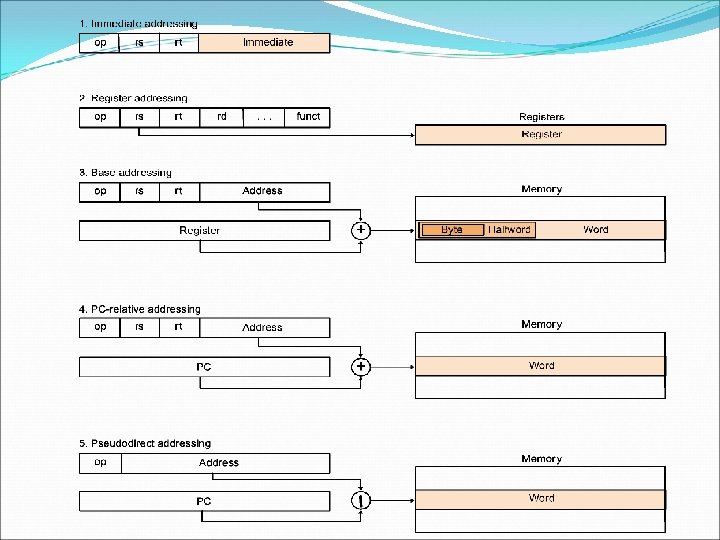

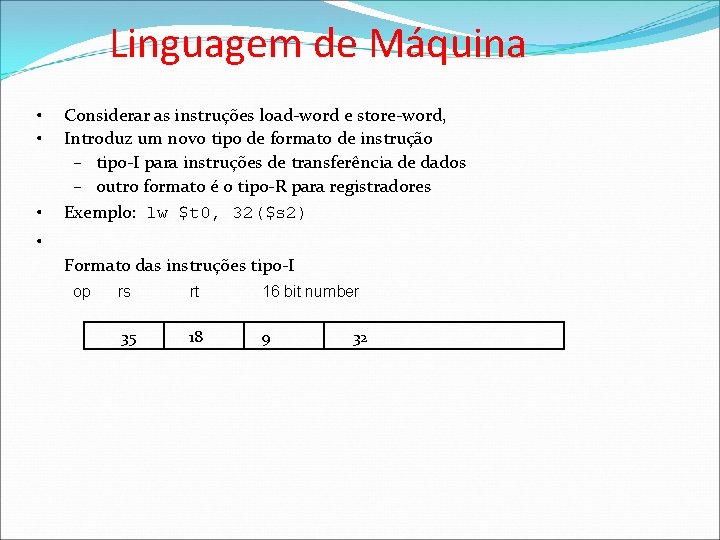

Linguagem de Máquina • • • Considerar as instruções load-word e store-word, Introduz um novo tipo de formato de instrução – tipo-I para instruções de transferência de dados – outro formato é o tipo-R para registradores Exemplo: lw $t 0, 32($s 2) • Formato das instruções tipo-I op rs rt 16 bit number 35 18 9 32

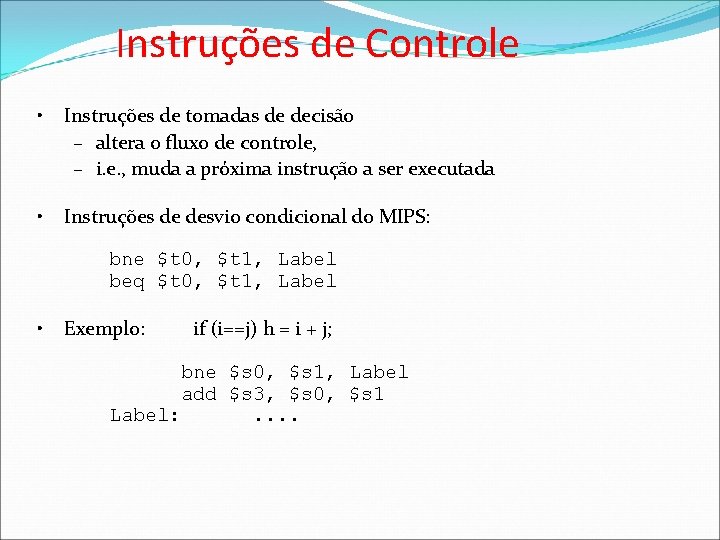

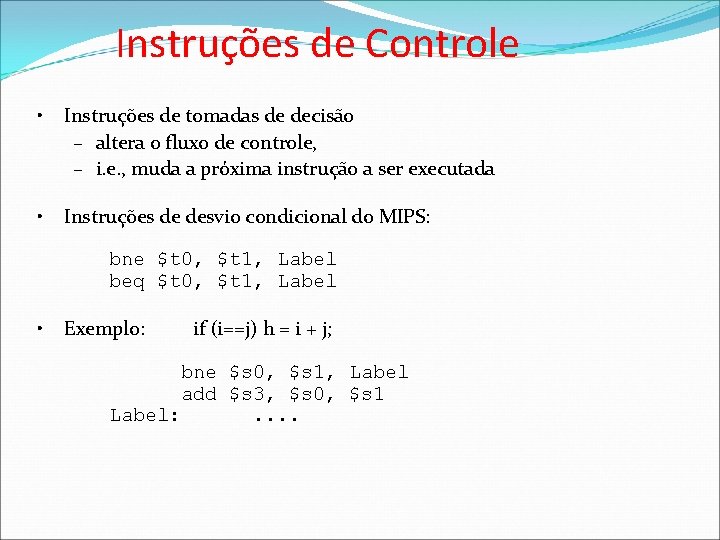

Conceito de Programa Armazenado na memória (von Neumann) • • • Instruções são conjunto de bits Os programas são armazenados na memória —para serem lidos e executados Se as instruções estão na mesma memória como os dados, elas podem também serem lidas e escritas como se fossem dados. Processor • Memory memory for data, programs, compilers, editors, etc. Ciclos de Fetch & Execute – Instruções são lidas (fetched) e colocadas num registrador especial – Os bits no registrador "controlam" as ações subsequentes – Busca (Fetch) a próxima instrução e continua

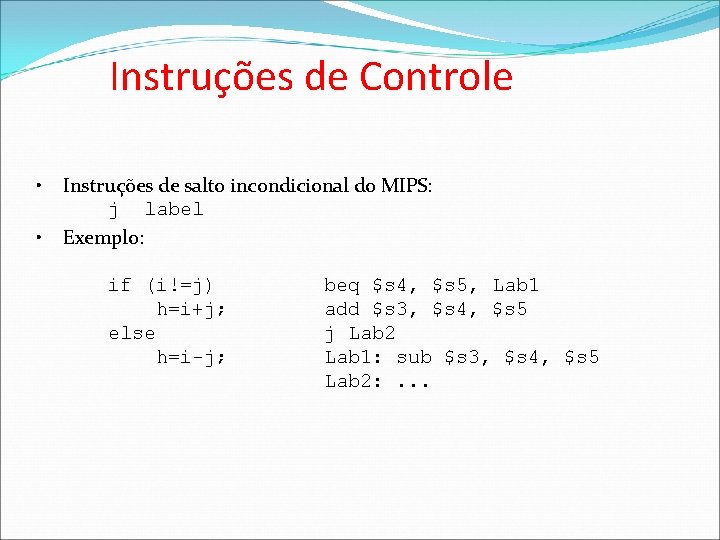

Instruções de Controle • Instruções de tomadas de decisão – altera o fluxo de controle, – i. e. , muda a próxima instrução a ser executada • Instruções de desvio condicional do MIPS: bne $t 0, $t 1, Label beq $t 0, $t 1, Label • Exemplo: if (i==j) h = i + j; bne $s 0, $s 1, Label add $s 3, $s 0, $s 1 Label: . .

Instruções de Controle • • Instruções de salto incondicional do MIPS: j label Exemplo: if (i!=j) h=i+j; else h=i-j; beq $s 4, $s 5, Lab 1 add $s 3, $s 4, $s 5 j Lab 2 Lab 1: sub $s 3, $s 4, $s 5 Lab 2: . . .

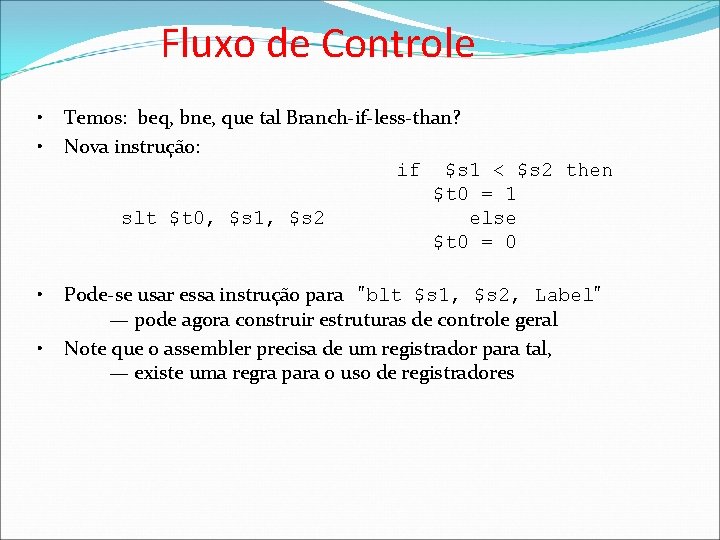

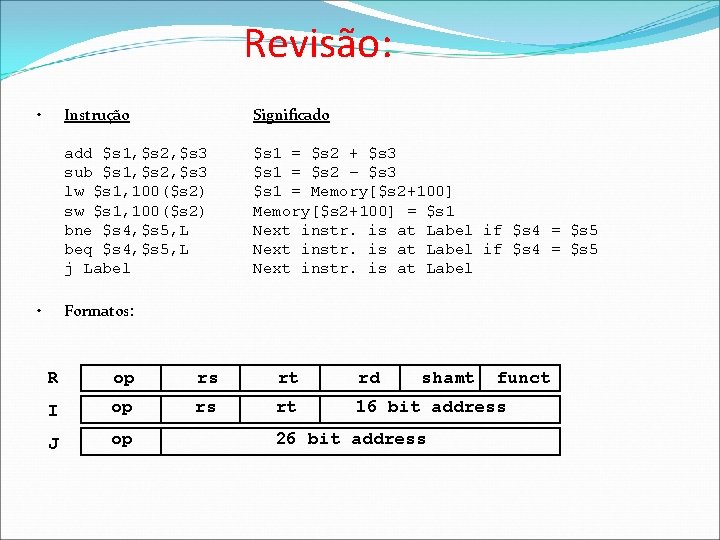

Revisão: • • Instrução Significado add $s 1, $s 2, $s 3 sub $s 1, $s 2, $s 3 lw $s 1, 100($s 2) sw $s 1, 100($s 2) bne $s 4, $s 5, L beq $s 4, $s 5, L j Label $s 1 = $s 2 + $s 3 $s 1 = $s 2 – $s 3 $s 1 = Memory[$s 2+100] = $s 1 Next instr. is at Label if $s 4 = $s 5 Next instr. is at Label Formatos: R op rs rt rd I op rs rt 16 bit address J op shamt 26 bit address funct

Fluxo de Controle • • Temos: beq, bne, que tal Branch-if-less-than? Nova instrução: if $s 1 < $s 2 then $t 0 = 1 slt $t 0, $s 1, $s 2 else $t 0 = 0 • Pode-se usar essa instrução para "blt $s 1, $s 2, Label" — pode agora construir estruturas de controle geral Note que o assembler precisa de um registrador para tal, — existe uma regra para o uso de registradores •

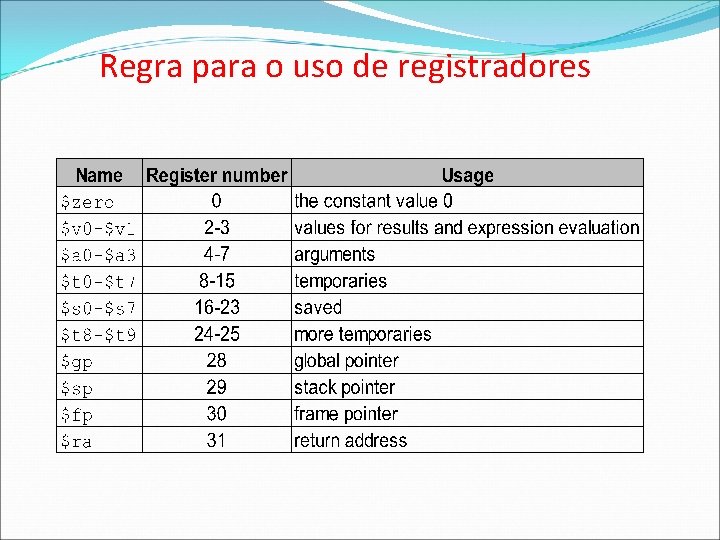

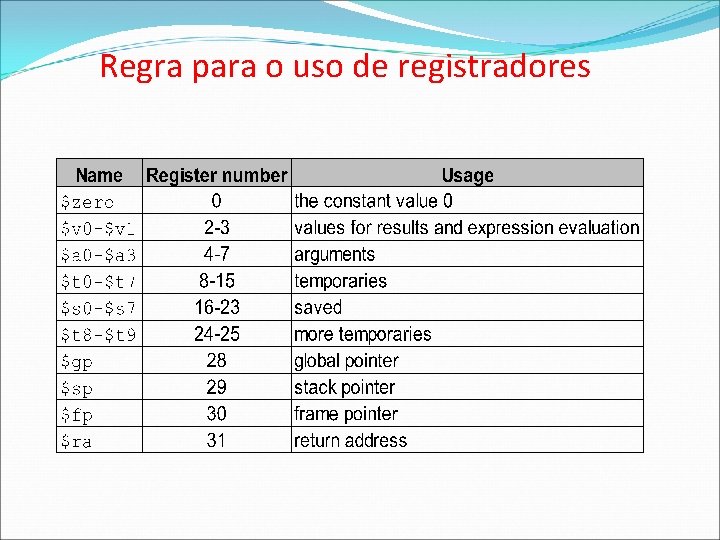

Regra para o uso de registradores

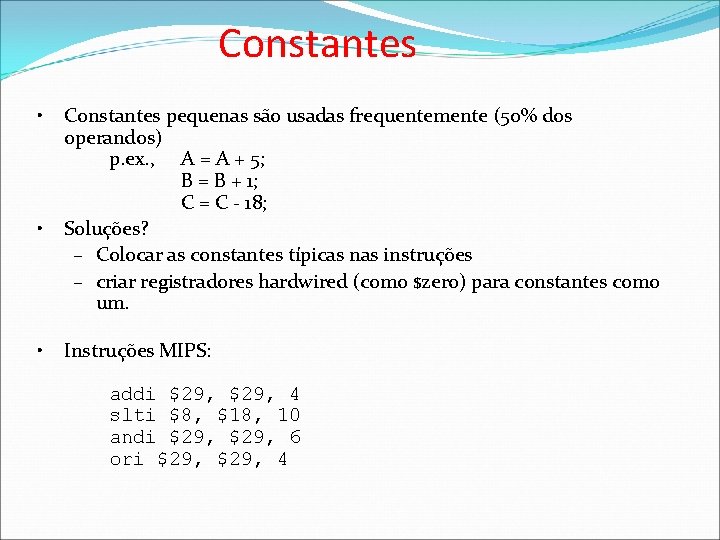

Constantes • • • Constantes pequenas são usadas frequentemente (50% dos operandos) p. ex. , A = A + 5; B = B + 1; C = C - 18; Soluções? – Colocar as constantes típicas nas instruções – criar registradores hardwired (como $zero) para constantes como um. Instruções MIPS: addi $29, 4 slti $8, $18, 10 andi $29, 6 ori $29, 4

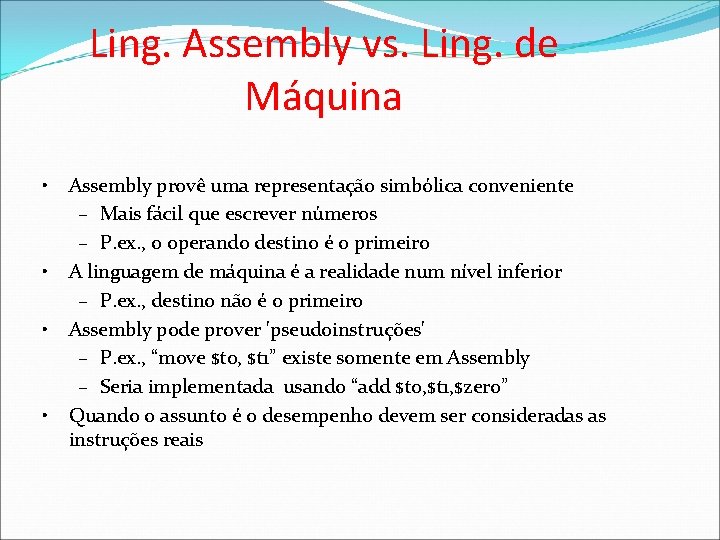

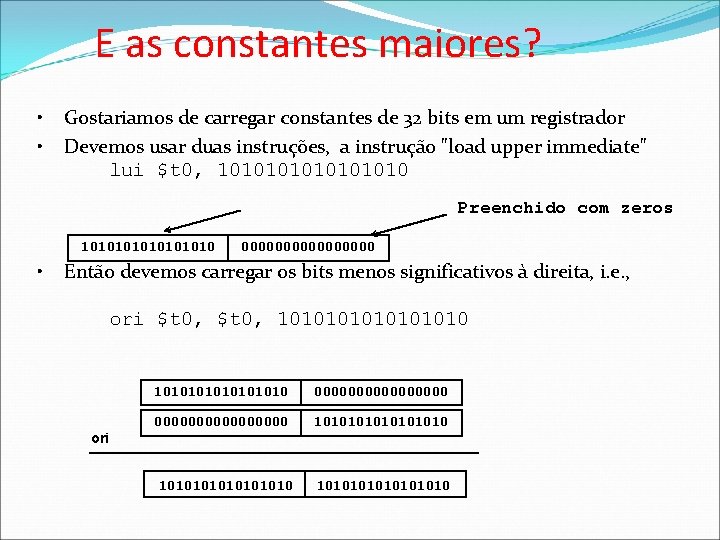

E as constantes maiores? • • Gostariamos de carregar constantes de 32 bits em um registrador Devemos usar duas instruções, a instrução "load upper immediate" lui $t 0, 10101010 Preenchido com zeros 10101010 • 00000000 Então devemos carregar os bits menos significativos à direita, i. e. , ori $t 0, 10101010 ori 10101010 0000000000000000 1010101010101010

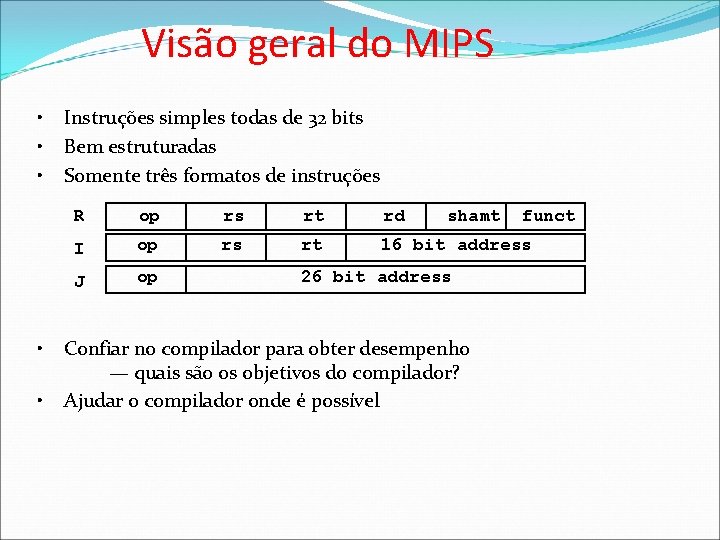

Ling. Assembly vs. Ling. de Máquina • • Assembly provê uma representação simbólica conveniente – Mais fácil que escrever números – P. ex. , o operando destino é o primeiro A linguagem de máquina é a realidade num nível inferior – P. ex. , destino não é o primeiro Assembly pode prover 'pseudoinstruções' – P. ex. , “move $t 0, $t 1” existe somente em Assembly – Seria implementada usando “add $t 0, $t 1, $zero” Quando o assunto é o desempenho devem ser consideradas as instruções reais

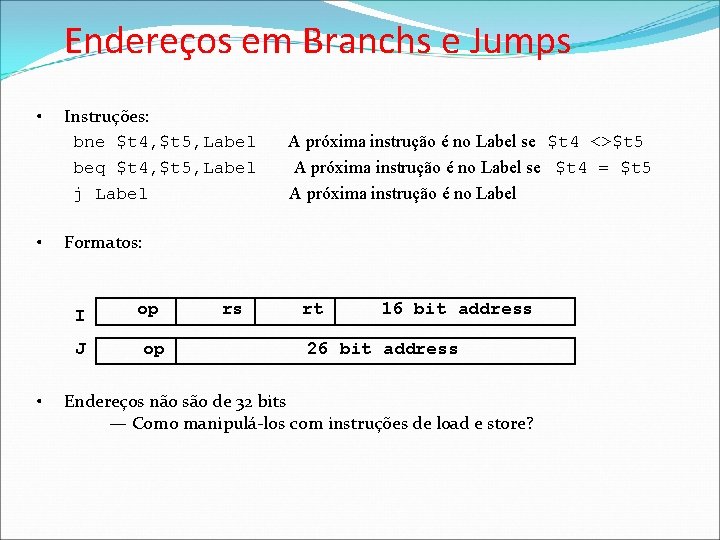

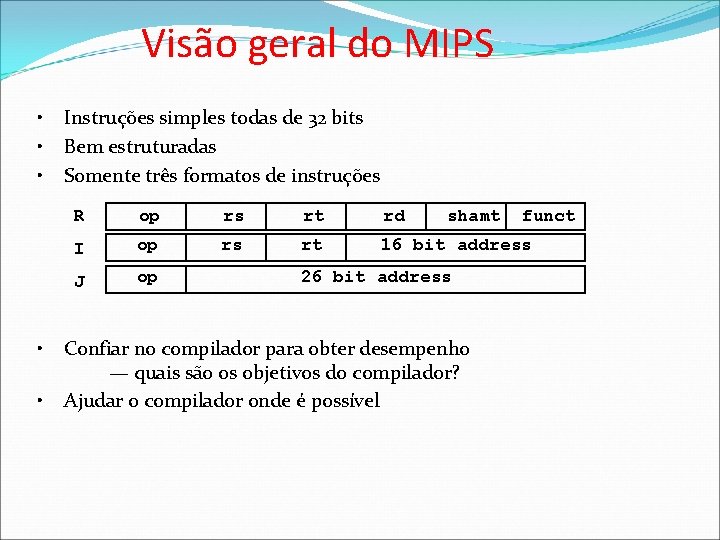

Visão geral do MIPS • • • Instruções simples todas de 32 bits Bem estruturadas Somente três formatos de instruções R op rs rt rd I op rs rt 16 bit address J op shamt 26 bit address Confiar no compilador para obter desempenho — quais são os objetivos do compilador? Ajudar o compilador onde é possível funct

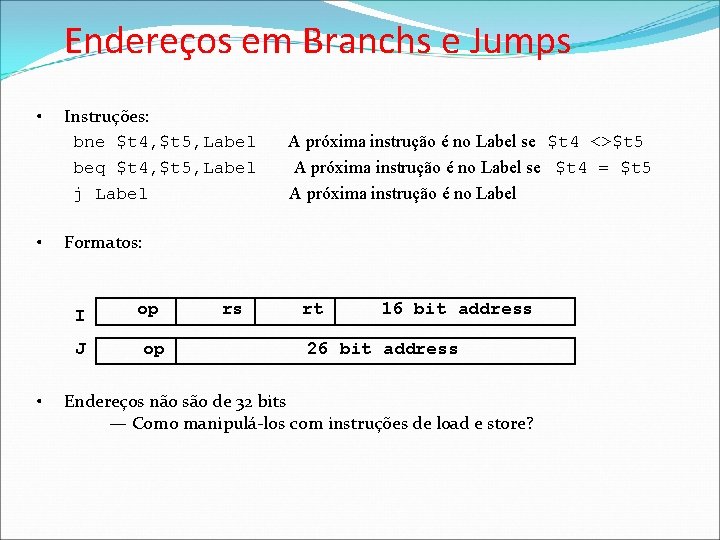

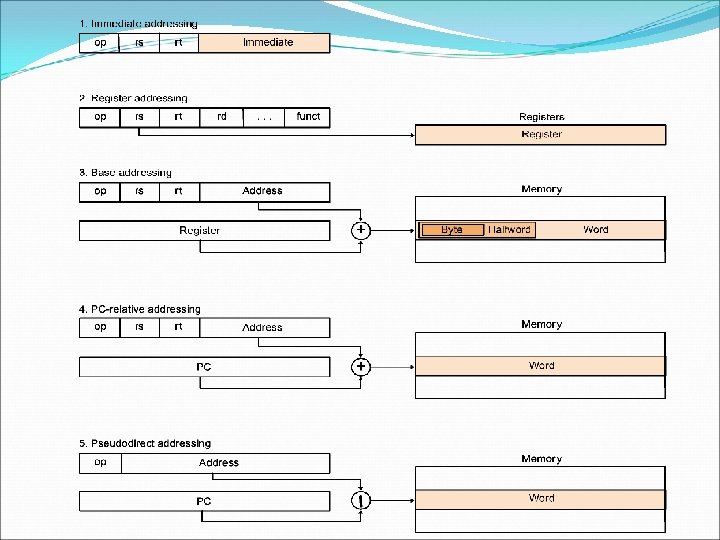

Endereços em Branchs e Jumps • • Instruções: bne $t 4, $t 5, Label beq $t 4, $t 5, Label j Label Formatos: I J • A próxima instrução é no Label se $t 4 <>$t 5 A próxima instrução é no Label se $t 4 = $t 5 A próxima instrução é no Label op op rs rt 16 bit address 26 bit address Endereços não são de 32 bits — Como manipulá-los com instruções de load e store?

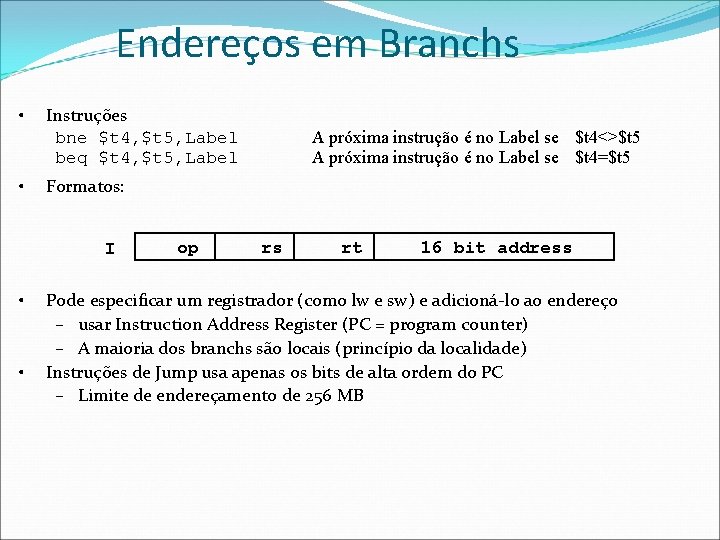

Endereços em Branchs • • Instruções bne $t 4, $t 5, Label beq $t 4, $t 5, Label Formatos: I • • A próxima instrução é no Label se $t 4<>$t 5 A próxima instrução é no Label se $t 4=$t 5 op rs rt 16 bit address Pode especificar um registrador (como lw e sw) e adicioná-lo ao endereço – usar Instruction Address Register (PC = program counter) – A maioria dos branchs são locais (princípio da localidade) Instruções de Jump usa apenas os bits de alta ordem do PC – Limite de endereçamento de 256 MB

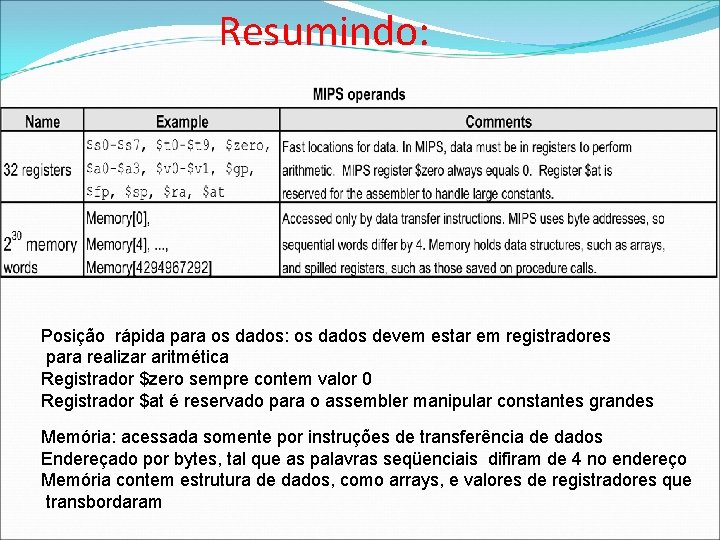

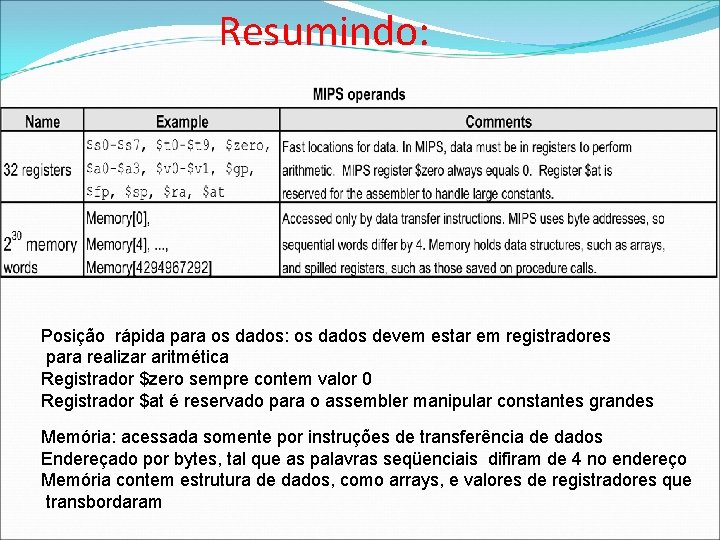

Resumindo: Posição rápida para os dados: os dados devem estar em registradores para realizar aritmética Registrador $zero sempre contem valor 0 Registrador $at é reservado para o assembler manipular constantes grandes Memória: acessada somente por instruções de transferência de dados Endereçado por bytes, tal que as palavras seqüenciais difiram de 4 no endereço Memória contem estrutura de dados, como arrays, e valores de registradores que transbordaram

Arquiteturas Alternativas • Alternativas de Projeto: – Prover operações mais potentes – A meta é reduzir o número de instruções executadas – O perigo é um tempo de ciclo mais lento e/ou um CPI maior • As vezes referidos como “RISC vs. CISC” – virtualmente todos os novos conjuntos de instruções desde 1982 tem sido RISC • Veremos o Power. PC e 80 x 86

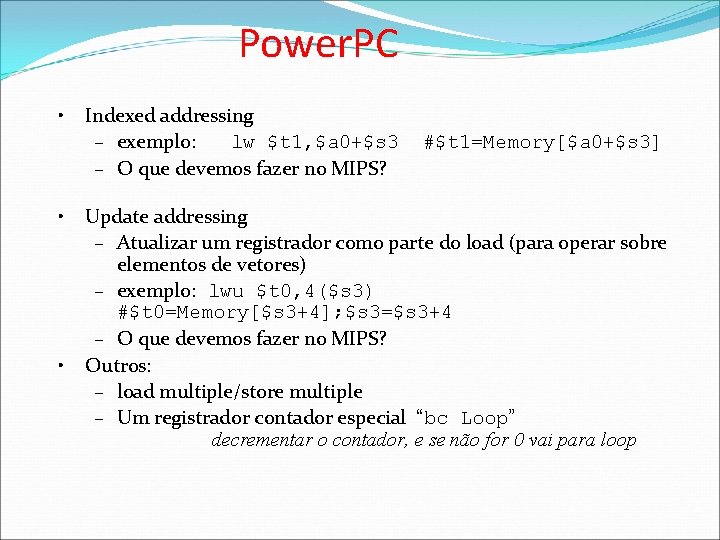

Power. PC • • • Indexed addressing – exemplo: lw $t 1, $a 0+$s 3 – O que devemos fazer no MIPS? #$t 1=Memory[$a 0+$s 3] Update addressing – Atualizar um registrador como parte do load (para operar sobre elementos de vetores) – exemplo: lwu $t 0, 4($s 3) #$t 0=Memory[$s 3+4]; $s 3=$s 3+4 – O que devemos fazer no MIPS? Outros: – load multiple/store multiple – Um registrador contador especial “bc Loop” decrementar o contador, e se não for 0 vai para loop

Intel 80 x 86 A partir do 80386 , também chamado de IA-32 • • • 1978: Intel 8086 é anunciado (arquitetura de 16 bits) 1980: 8087 é adicionado o coprocessador de ponto flutuante 1982: 80286 aumenta o espaço de endereçamento para 24 bits, + instruções 1985: 80386 estende para 32 bits, novos modos de endereçamento 1989 -1995: 80486, Pentium Pro e algumas novas instruções (a maioria para melhorar o desempenho) 1997: MMX é adicionado “This history illustrates the impact of the “golden handcuffs” of compatibility “adding new features as someone might add clothing to a packed bag” “an architecture that is difficult to explain and impossible to love”

Uma arquitetura dominante: 80 x 86 • Complexidade: – Instruções de 1 a 17 bytes – um operando deve agir como fonte e destino – um operando pode vir da memória – Modos de endereçamento complexos p. ex. , “base ou scaled index com deslocamento de 8 ou 32 bit” • Salvando a graça: – As instruções mais frequentemente usadas não são tão difíceis de serem construidas – Os compiladores evitam as porções da arquitetura que são lentas “what the 80 x 86 lacks in style is made up in quantity, making it beautiful from the right perspective”