Multiplicador e Forwarding no MIPS CMP 114 Arquitetura

- Slides: 20

Multiplicador e Forwarding no MIPS CMP 114 - Arquitetura e Projeto de Sistemas VLSI I Andre Resende

Sumário • Objetivos • MIPS Pipeline • Multiplicador – Implementação – Simulação • Forwarding – Implementação – Simulação • Conclusão/Sugestões

Objetivos • Implementar um multiplicador em hardware e o mecanismo de forwarding na descrição VHDL do processador MIPS com pipeline • Possibilitar a comparação com o processador Femto. Java

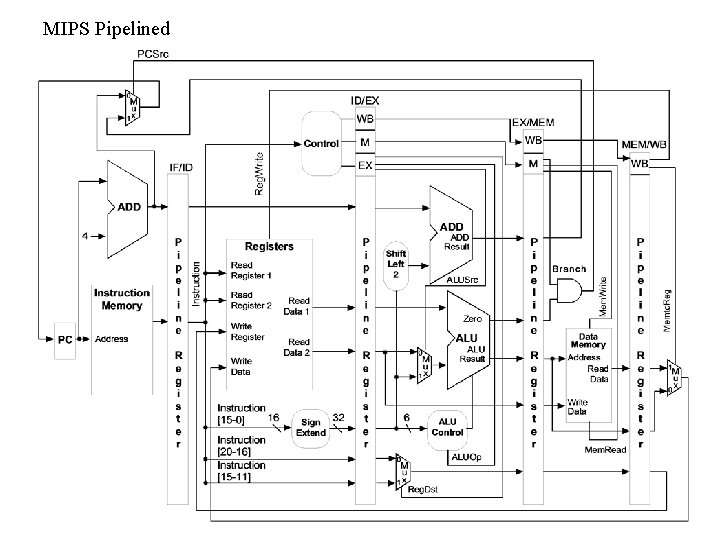

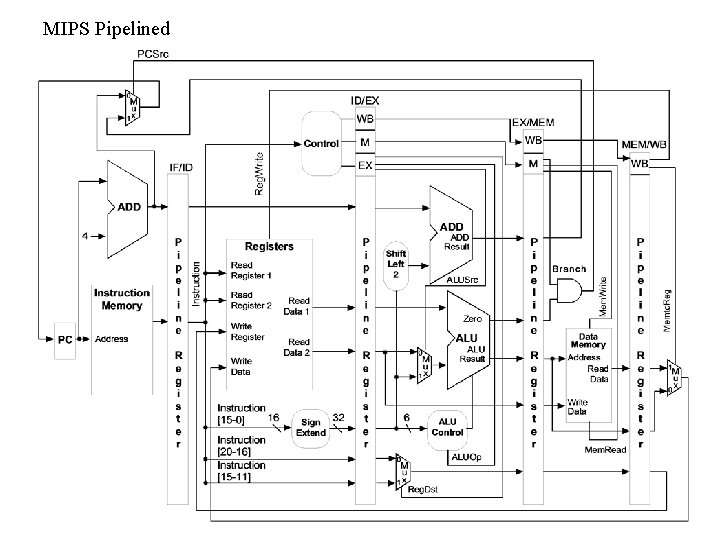

MIPS Pipelined

Multiplicador • Multiplicador em hardware no processador Mips • Reuso do código VHDL implementado para o Femto. Java: Multiplicador Booth Paralelo • 8 bits • Componente no módulo Execute

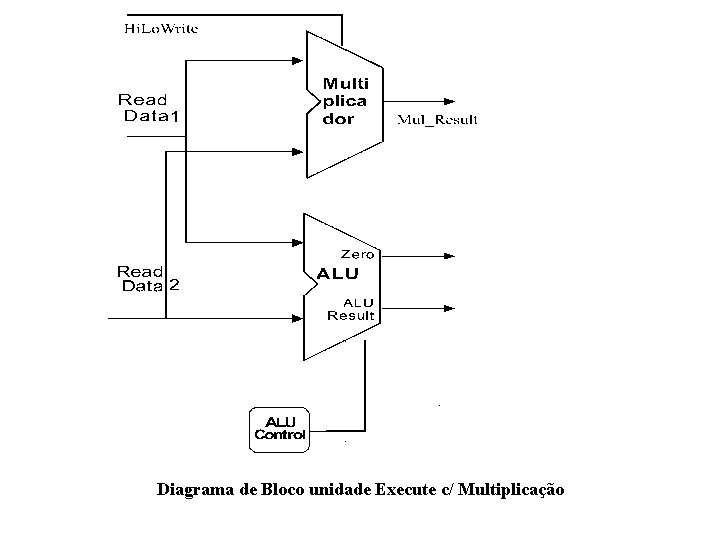

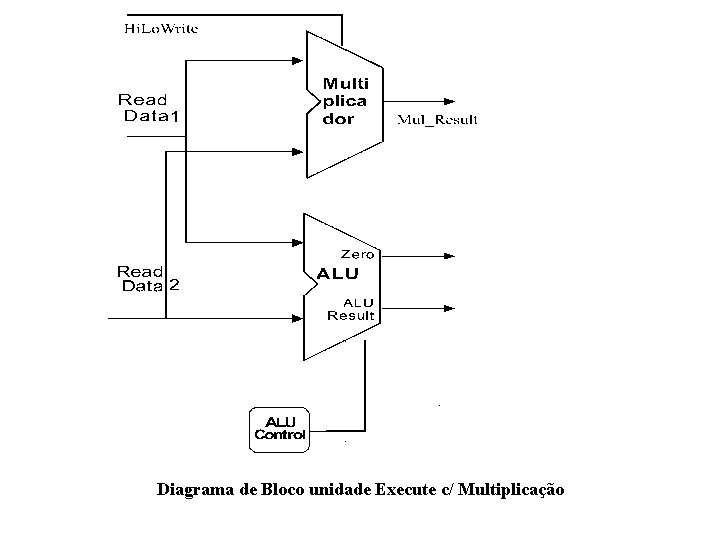

Multiplicador – Implementação • Entradas da ALU foram copiadas para o multiplicador • Foram criados 2 registradores para armazenar o resultado: Hi e Lo • Sinal de controle para a multiplicação gerado na unidade de Controle – Sinal de entrada com o functo code

Multiplicador – Implementação • Componente instanciado dentro da unidade Execute • Entradas do multiplicador conectadas ao mecanismo de forwarding

Diagrama de Bloco unidade Execute c/ Multiplicação

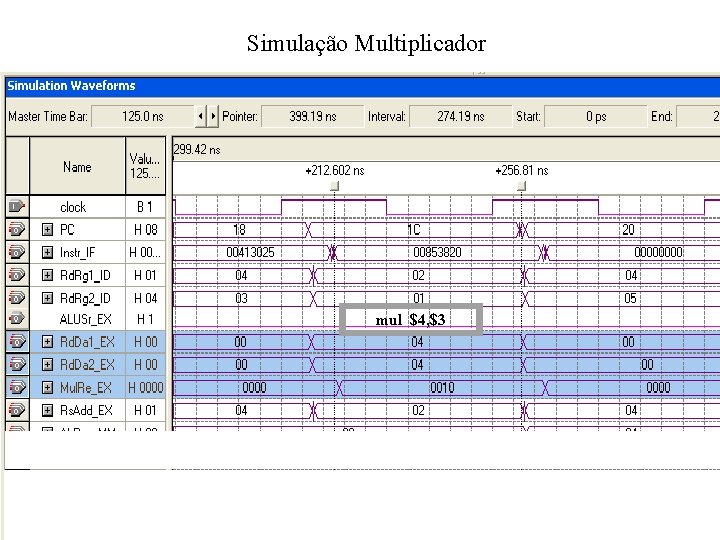

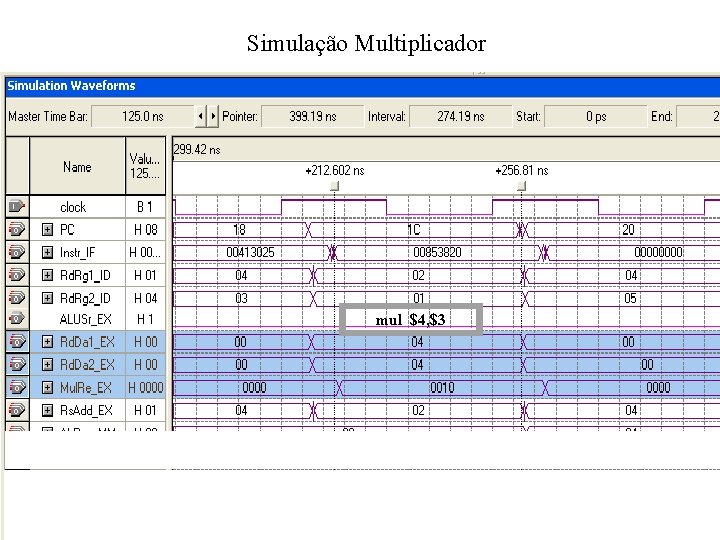

Simulação Multiplicador mul $4, $3

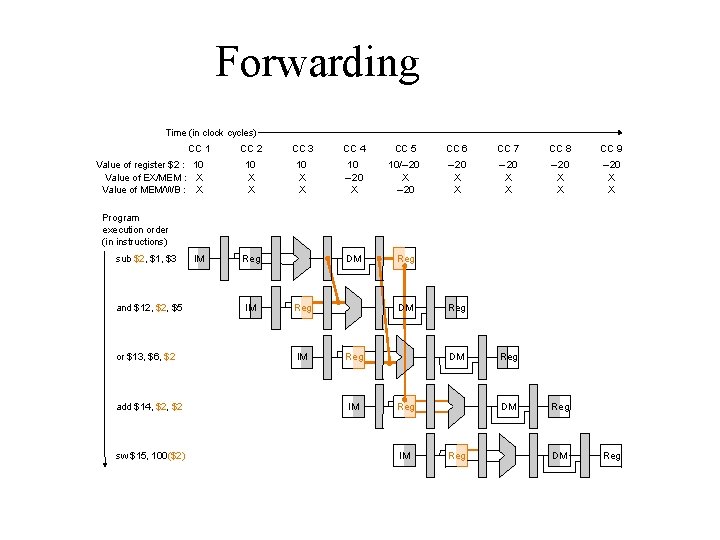

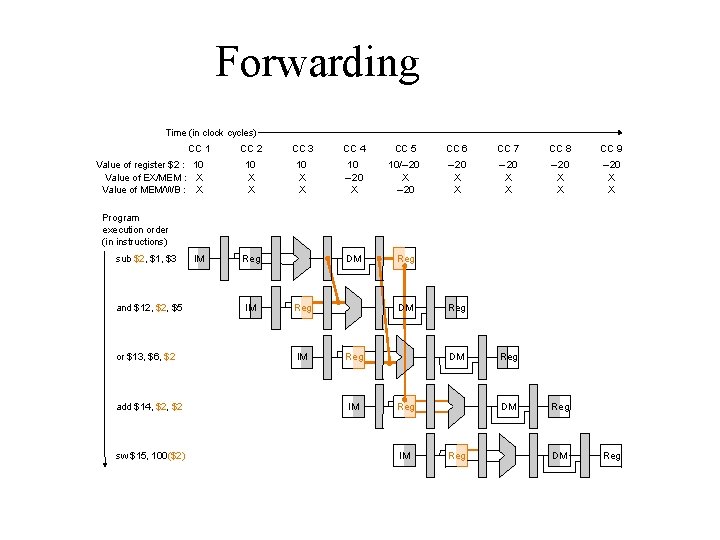

Forwarding Time (in clock cycles) CC 1 Value of register $2 : 10 Value of EX/MEM : X Value of MEM/WB : X CC 2 CC 3 CC 4 CC 5 CC 6 CC 7 CC 8 CC 9 10 X X 10 – 20 X 10/– 20 X X – 20 X X DM Reg Program execution order (in instructions) sub $2, $1, $3 and $12, $5 or $13, $6, $2 add $14, $2 sw $15, 100($2) IM Reg IM DM Reg IM Reg DM Reg

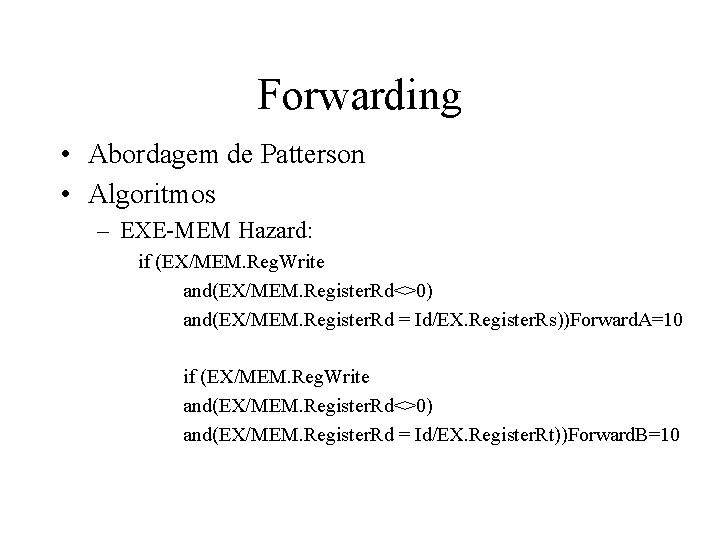

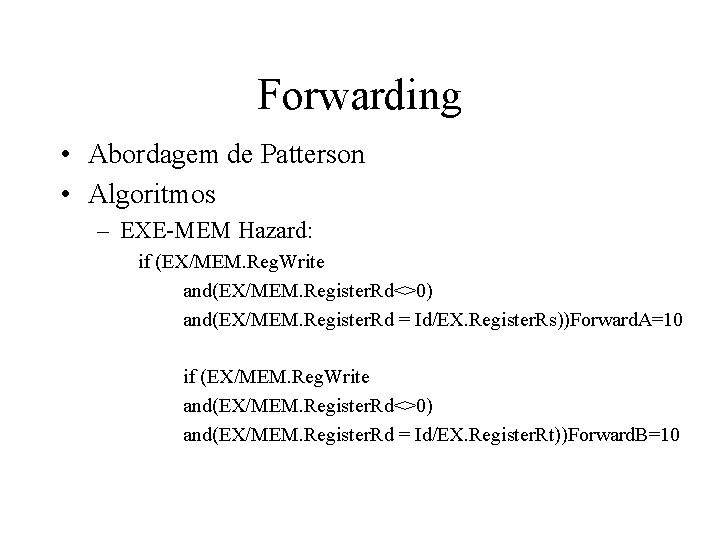

Forwarding • Abordagem de Patterson • Algoritmos – EXE-MEM Hazard: if (EX/MEM. Reg. Write and(EX/MEM. Register. Rd<>0) and(EX/MEM. Register. Rd = Id/EX. Register. Rs))Forward. A=10 if (EX/MEM. Reg. Write and(EX/MEM. Register. Rd<>0) and(EX/MEM. Register. Rd = Id/EX. Register. Rt))Forward. B=10

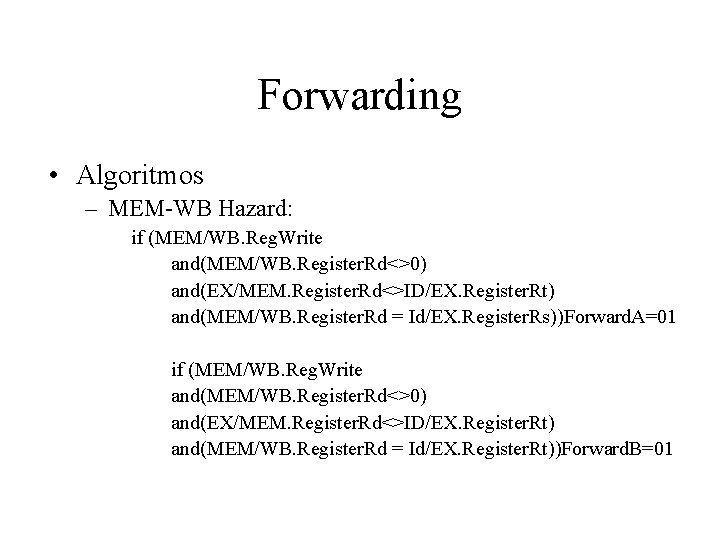

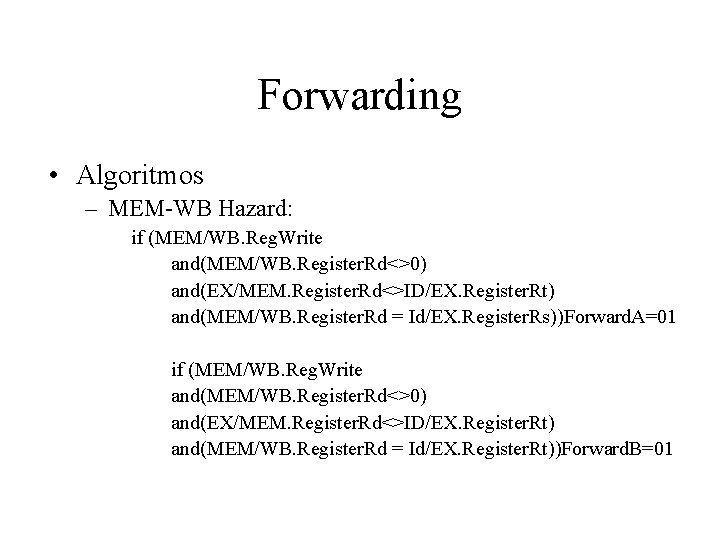

Forwarding • Algoritmos – MEM-WB Hazard: if (MEM/WB. Reg. Write and(MEM/WB. Register. Rd<>0) and(EX/MEM. Register. Rd<>ID/EX. Register. Rt) and(MEM/WB. Register. Rd = Id/EX. Register. Rs))Forward. A=01 if (MEM/WB. Reg. Write and(MEM/WB. Register. Rd<>0) and(EX/MEM. Register. Rd<>ID/EX. Register. Rt) and(MEM/WB. Register. Rd = Id/EX. Register. Rt))Forward. B=01

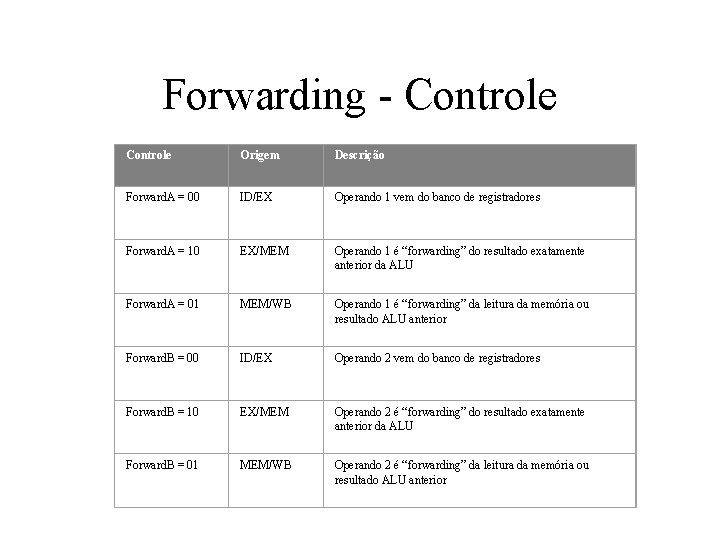

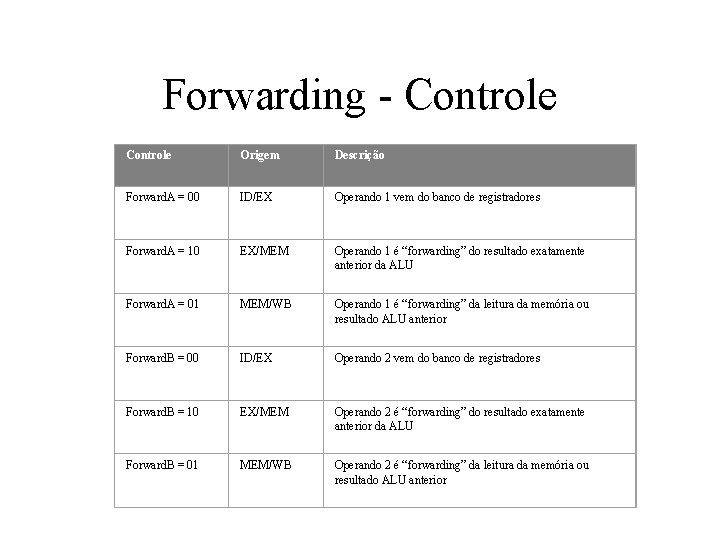

Forwarding - Controle Origem Descrição Forward. A = 00 ID/EX Operando 1 vem do banco de registradores Forward. A = 10 EX/MEM Operando 1 é “forwarding” do resultado exatamente anterior da ALU Forward. A = 01 MEM/WB Operando 1 é “forwarding” da leitura da memória ou resultado ALU anterior Forward. B = 00 ID/EX Operando 2 vem do banco de registradores Forward. B = 10 EX/MEM Operando 2 é “forwarding” do resultado exatamente anterior da ALU Forward. B = 01 MEM/WB Operando 2 é “forwarding” da leitura da memória ou resultado ALU anterior

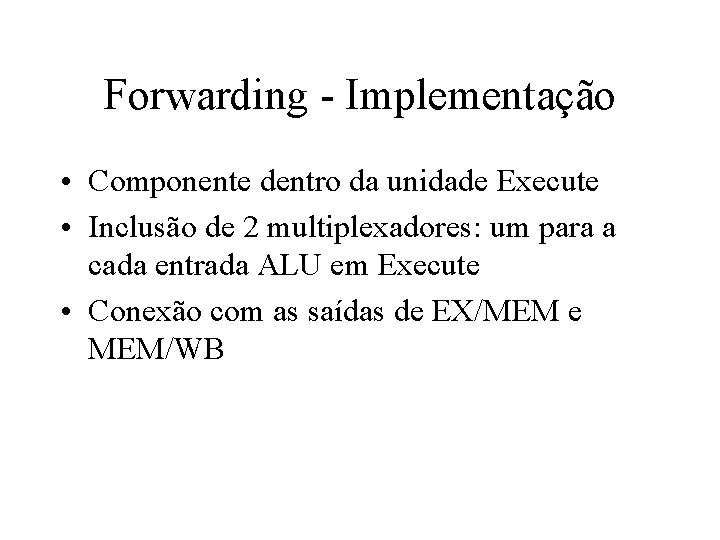

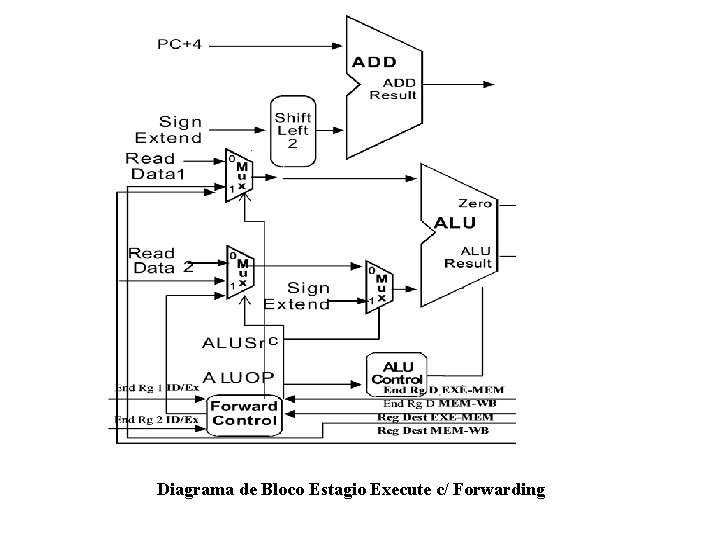

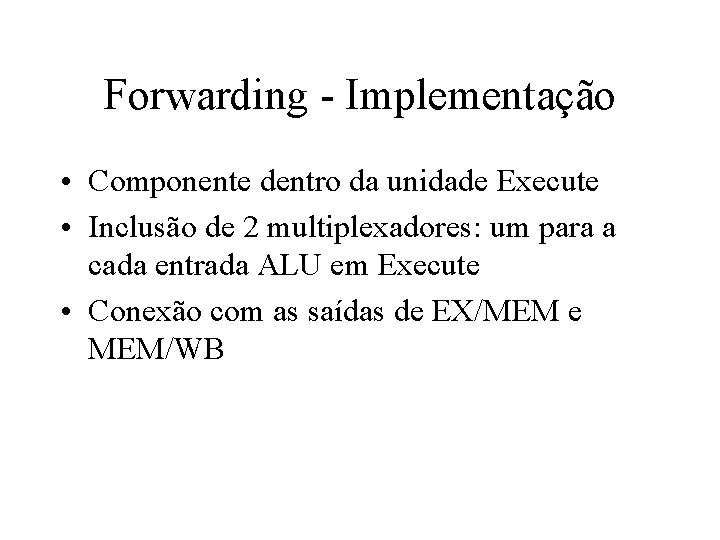

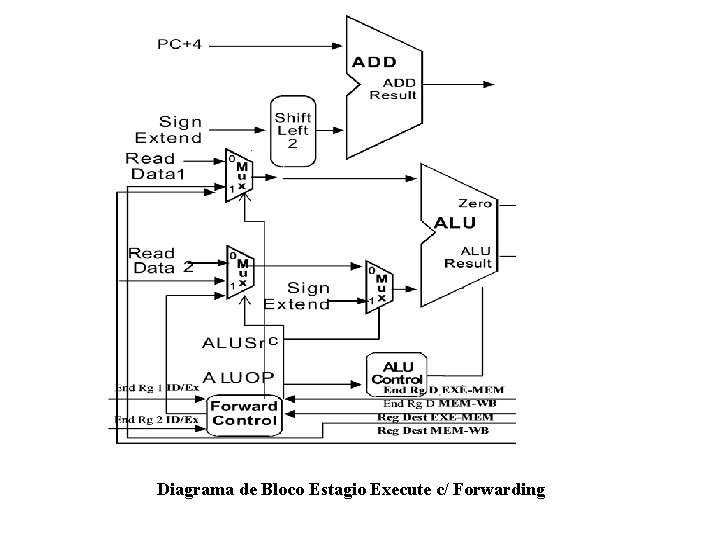

Forwarding - Implementação • Componente dentro da unidade Execute • Inclusão de 2 multiplexadores: um para a cada entrada ALU em Execute • Conexão com as saídas de EX/MEM e MEM/WB

Diagrama de Bloco Estagio Execute c/ Forwarding

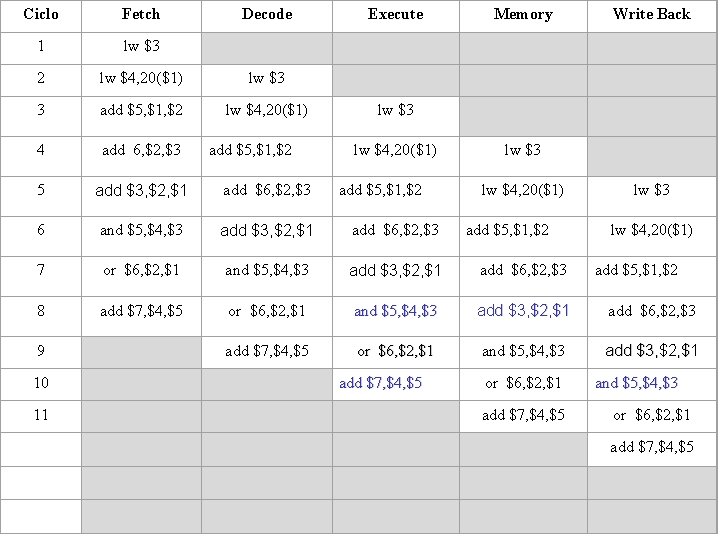

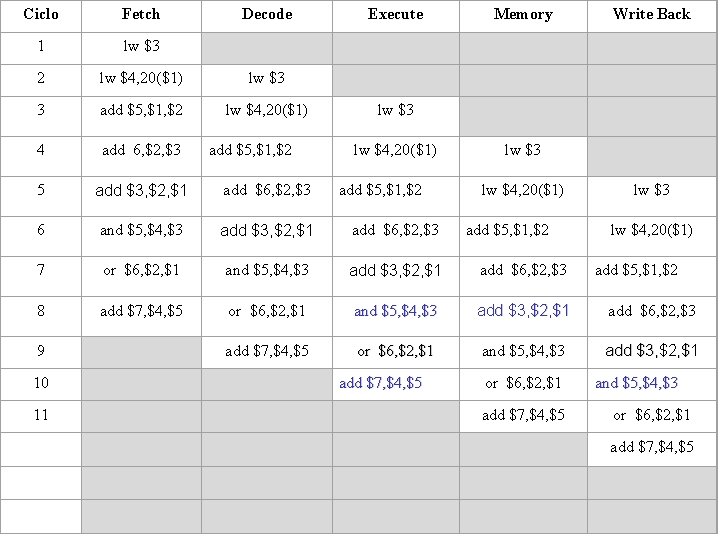

Ciclo Fetch 1 lw $3 2 lw $4, 20($1) lw $3 3 add $5, $1, $2 lw $4, 20($1) 4 add 6, $2, $3 5 add $3, $2, $1 add $6, $2, $3 6 and $5, $4, $3 add $3, $2, $1 add $6, $2, $3 7 or $6, $2, $1 and $5, $4, $3 add $3, $2, $1 add $6, $2, $3 8 add $7, $4, $5 or $6, $2, $1 and $5, $4, $3 add $3, $2, $1 add $6, $2, $3 add $7, $4, $5 or $6, $2, $1 and $5, $4, $3 add $3, $2, $1 9 Decode add $5, $1, $2 10 Execute Memory Write Back lw $3 lw $4, 20($1) lw $3 add $5, $1, $2 lw $4, 20($1) add $5, $1, $2 add $7, $4, $5 or $6, $2, $1 11 add $7, $4, $5 lw $3 lw $4, 20($1) add $5, $1, $2 and $5, $4, $3 or $6, $2, $1 add $7, $4, $5

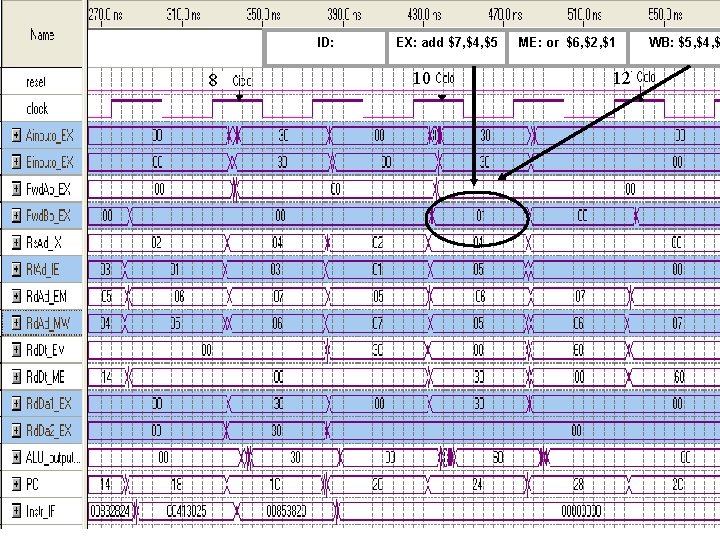

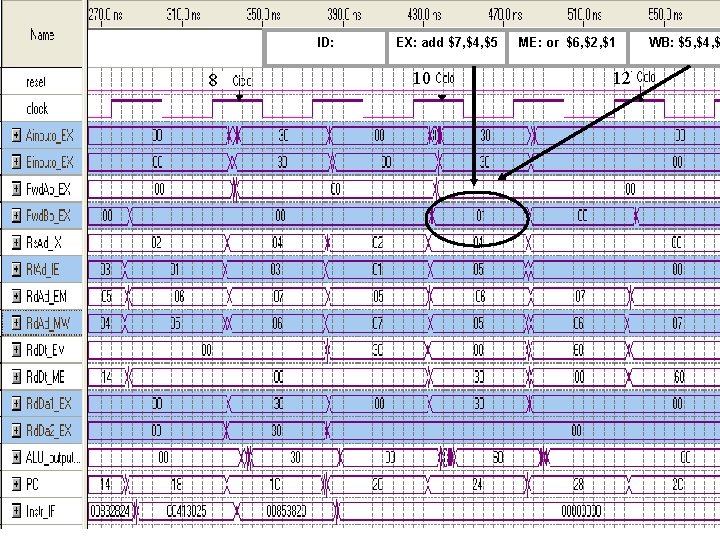

ID: 8 EX: add $7, $4, $5 10 ME: or $6, $2, $1 12 WB: $5, $4, $

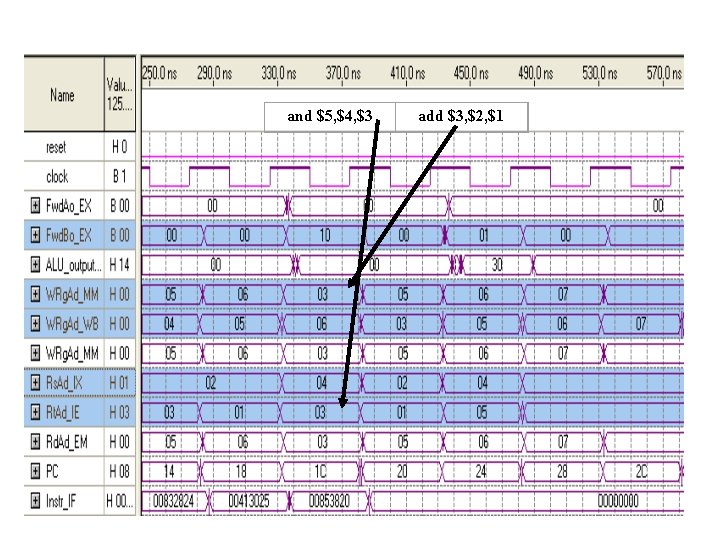

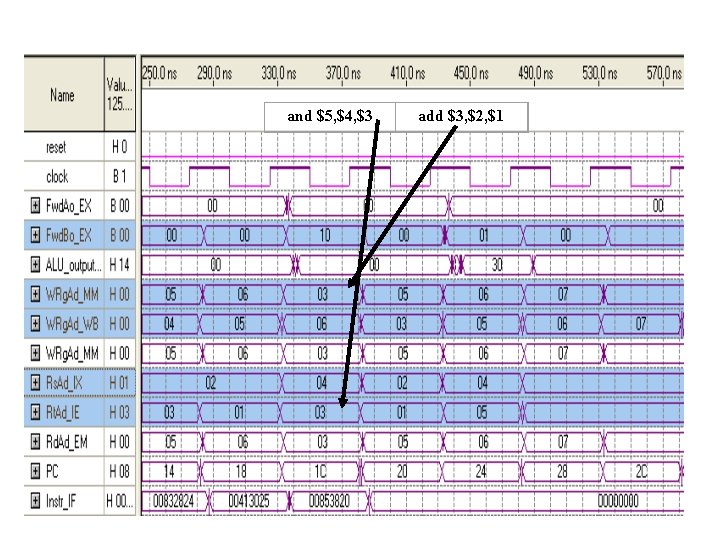

and $5, $4, $3 add $3, $2, $1

Conclusões • Compreensão código VHDL (1/2 trabalho) • Velocidade do multiplicador , não afetou o clock da versão pipeline (depende do hardware? ? ) • Baixa complexidade X dificuldade de implementação

Sugestões • Multiplicador sensível ao sinal de controle • Particionamento do multiplicador em ciclos • Sinal de controle para identificar qdo: Instrução(15 -11) Rd