Multiple Drain TransistorBased FPGA Architectures Gate Sidewall Drain

Multiple Drain Transistor-Based FPGA Architectures Gate Sidewall Drain 1 Drain 2 Source Drew Carlson Pankaj Kalra EE 241 Class Project May 9, 2005 1

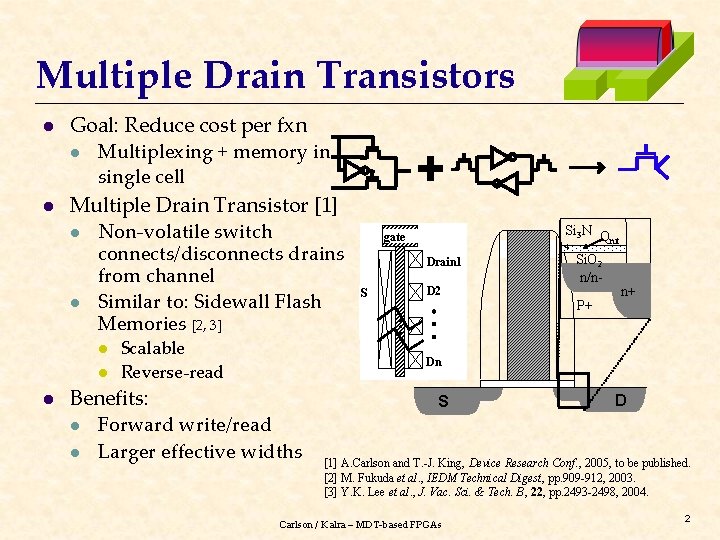

Multiple Drain Transistors l l Goal: Reduce cost per fxn l Multiplexing + memory in single cell Multiple Drain Transistor [1] l Non-volatile switch connects/disconnects drains from channel l Similar to: Sidewall Flash Memories [2, 3] l l l Scalable Reverse-read Si 3 N Q nit gate 4 Drain 1 S D 2 Si. O 2 n/n. P+ n+ Dn Benefits: l Forward write/read l Larger effective widths S D [1] A. Carlson and T. -J. King, Device Research Conf. , 2005, to be published. [2] M. Fukuda et al. , IEDM Technical Digest, pp. 909 -912, 2003. [3] Y. K. Lee et al. , J. Vac. Sci. & Tech. B, 22, pp. 2493 -2498, 2004. Carlson / Kalra – MDT-based FPGAs 2

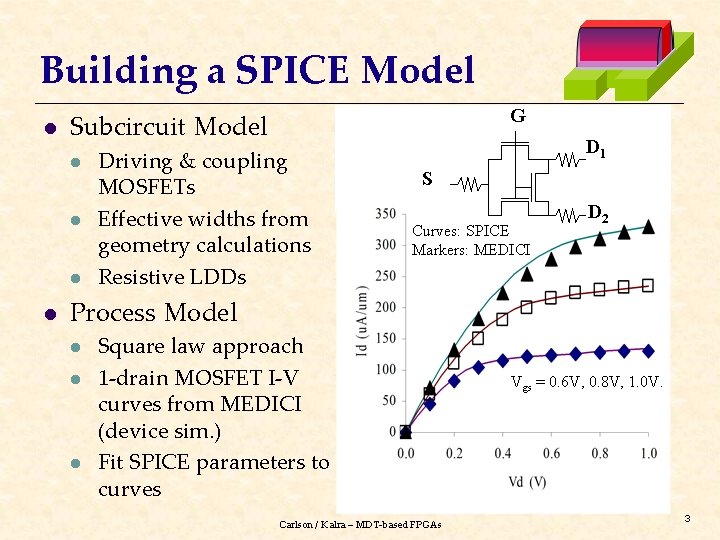

Building a SPICE Model l l G Subcircuit Model Driving & coupling MOSFETs Effective widths from geometry calculations Resistive LDDs D 1 S Curves: SPICE Markers: MEDICI D 2 Process Model l Square law approach 1 -drain MOSFET I-V curves from MEDICI (device sim. ) Fit SPICE parameters to curves Carlson / Kalra – MDT-based FPGAs Vgs = 0. 6 V, 0. 8 V, 1. 0 V. 3

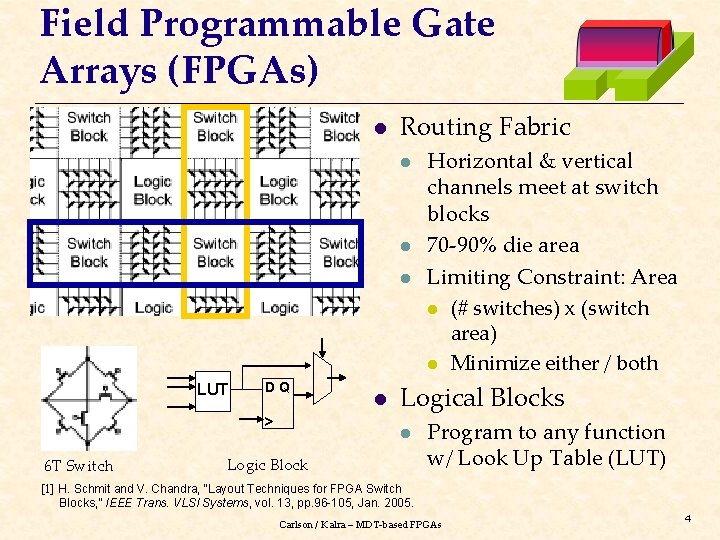

Field Programmable Gate Arrays (FPGAs) l Routing Fabric l l l LUT DQ > 6 T Switch l Horizontal & vertical channels meet at switch blocks 70 -90% die area Limiting Constraint: Area l (# switches) x (switch area) l Minimize either / both Logical Blocks l Logic Block Program to any function w/ Look Up Table (LUT) [1] H. Schmit and V. Chandra, “Layout Techniques for FPGA Switch Blocks, ” IEEE Trans. VLSI Systems, vol. 13, pp. 96 -105, Jan. 2005. Carlson / Kalra – MDT-based FPGAs 4

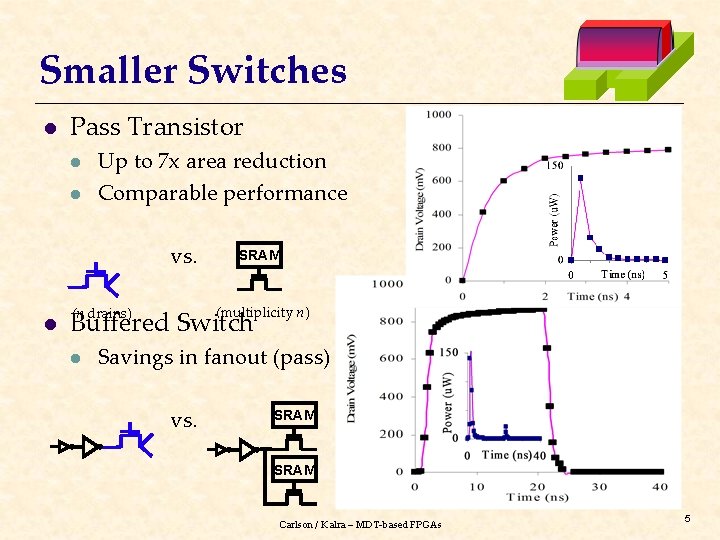

Smaller Switches l Pass Transistor l l Up to 7 x area reduction Comparable performance vs. l SRAM (multiplicity n) (n drains) Buffered Switch l Savings in fanout (pass) vs. SRAM Carlson / Kalra – MDT-based FPGAs 5

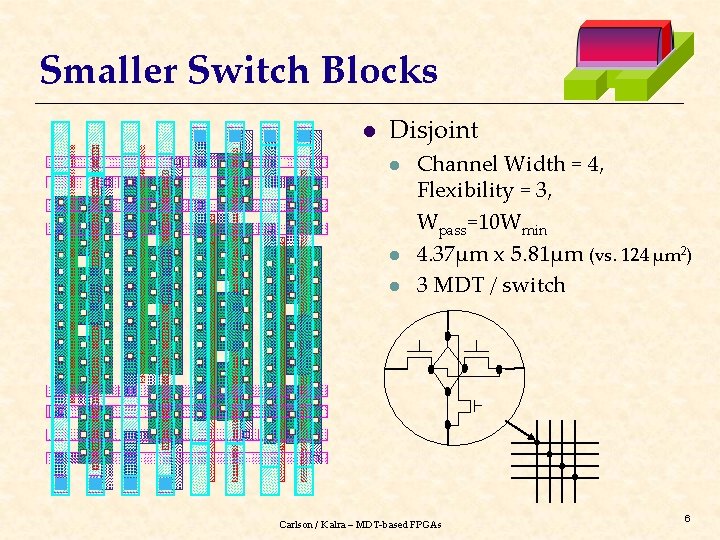

Smaller Switch Blocks l Disjoint l l l Channel Width = 4, Flexibility = 3, Wpass=10 Wmin 4. 37μm x 5. 81μm (vs. 124 μm 2) 3 MDT / switch Carlson / Kalra – MDT-based FPGAs 6

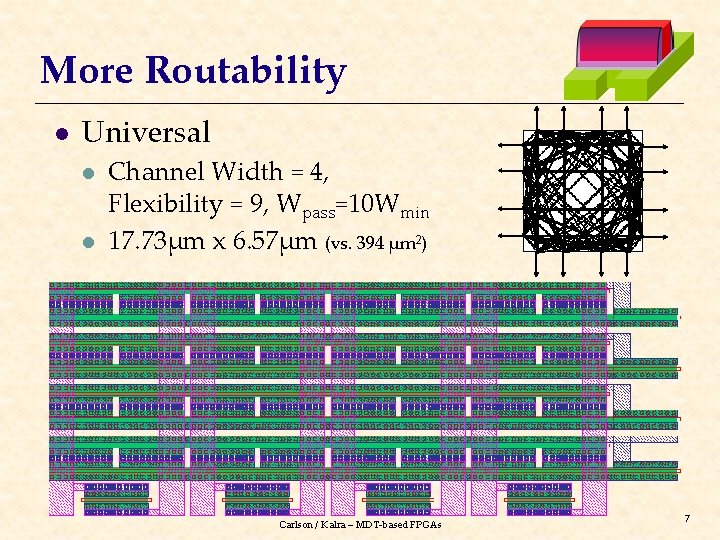

More Routability l Universal l l Channel Width = 4, Flexibility = 9, Wpass=10 Wmin 17. 73μm x 6. 57μm (vs. 394 μm 2) Carlson / Kalra – MDT-based FPGAs 7

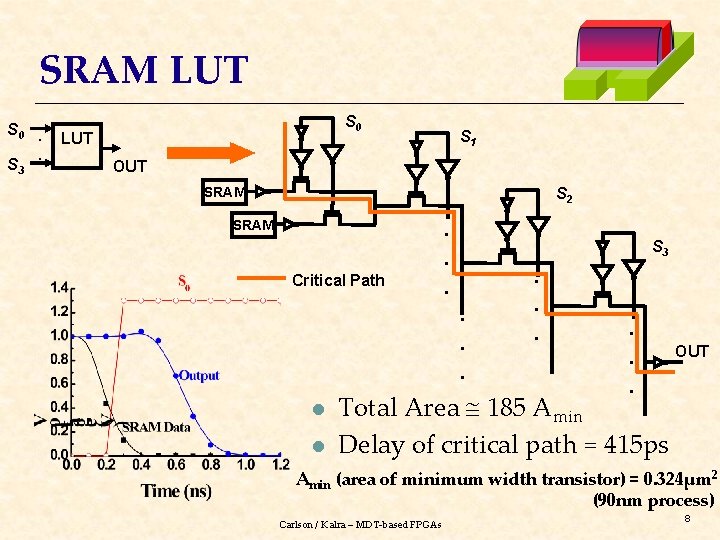

SRAM LUT S 0. . S 3 S 0 LUT S 1 OUT SRAM S 2 SRAM Critical Path . . . S 3 . . . l l . . . OUT Total Area 185 Amin Delay of critical path = 415 ps Amin (area of minimum width transistor) = 0. 324μm 2 (90 nm process) Carlson / Kalra – MDT-based FPGAs 8

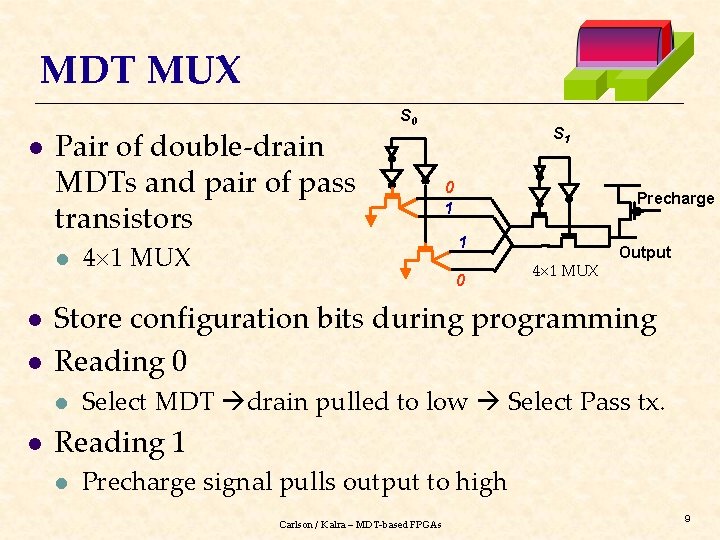

MDT MUX l Pair of double-drain MDTs and pair of pass transistors l l l 4 1 MUX S 1 0 1 Precharge 1 0 4 1 MUX Output Store configuration bits during programming Reading 0 l l S 0 Select MDT drain pulled to low Select Pass tx. Reading 1 l Precharge signal pulls output to high Carlson / Kalra – MDT-based FPGAs 9

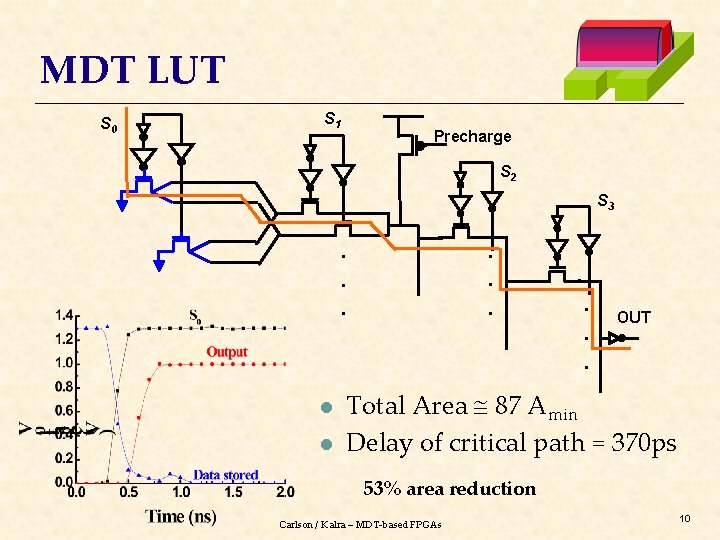

MDT LUT S 0 S 1 Precharge S 2 S 3 . . . l l . . . OUT Total Area 87 Amin Delay of critical path = 370 ps 53% area reduction Carlson / Kalra – MDT-based FPGAs 10

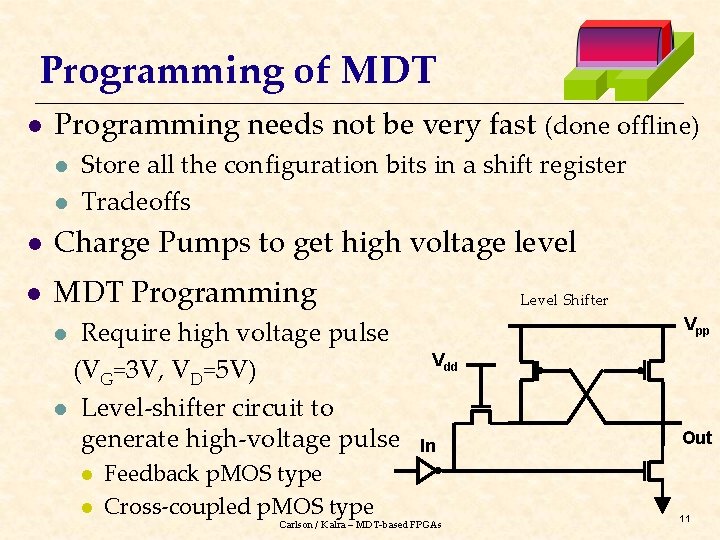

Programming of MDT l Programming needs not be very fast (done offline) l l Store all the configuration bits in a shift register Tradeoffs l Charge Pumps to get high voltage level l MDT Programming Require high voltage pulse (VG=3 V, VD=5 V) l Level-shifter circuit to generate high-voltage pulse Level Shifter Vpp l l l Feedback p. MOS type Cross-coupled p. MOS type Vdd In Carlson / Kalra – MDT-based FPGAs Out 11

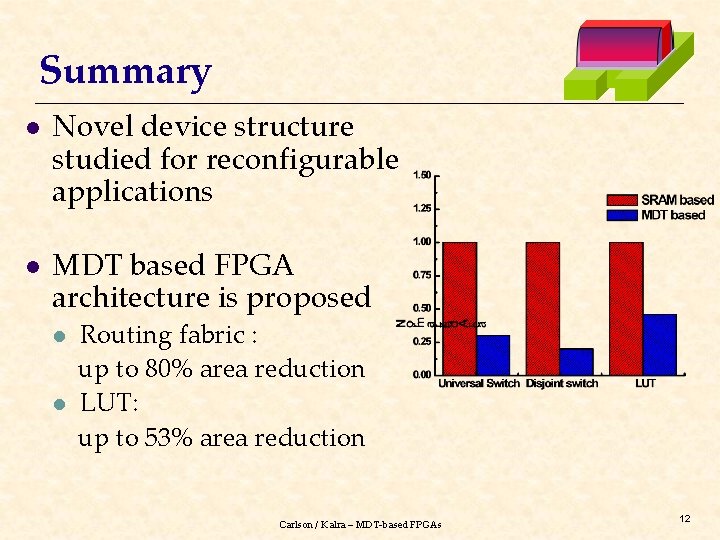

Summary l l Novel device structure studied for reconfigurable applications MDT based FPGA architecture is proposed l l Routing fabric : up to 80% area reduction LUT: up to 53% area reduction Carlson / Kalra – MDT-based FPGAs 12

- Slides: 12