MPIS and SPIM Instruction set architecture Registers Instruction

- Slides: 16

MPIS and SPIM § Instruction set architecture Registers Instruction format Memory layout Addressing mode Input/output Exception 6/16/2021 CMPUT 229 1

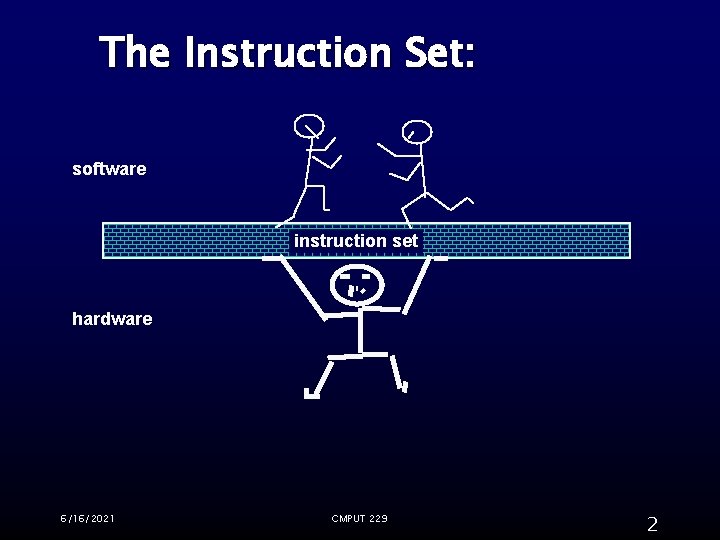

The Instruction Set: software instruction set hardware 6/16/2021 CMPUT 229 2

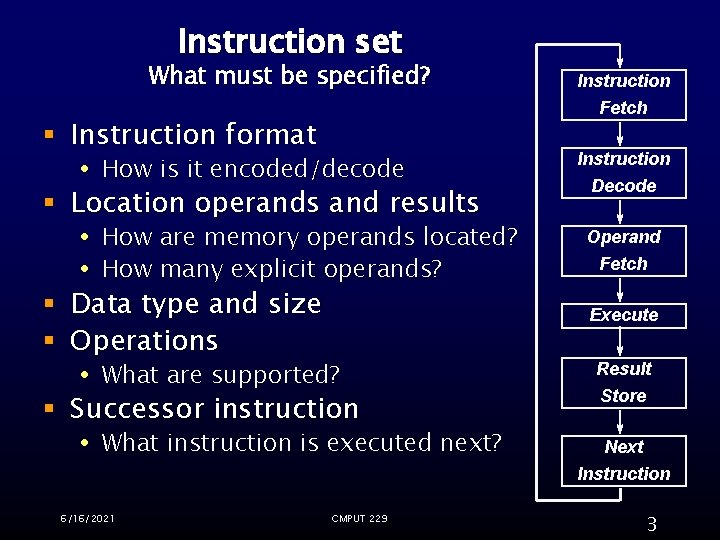

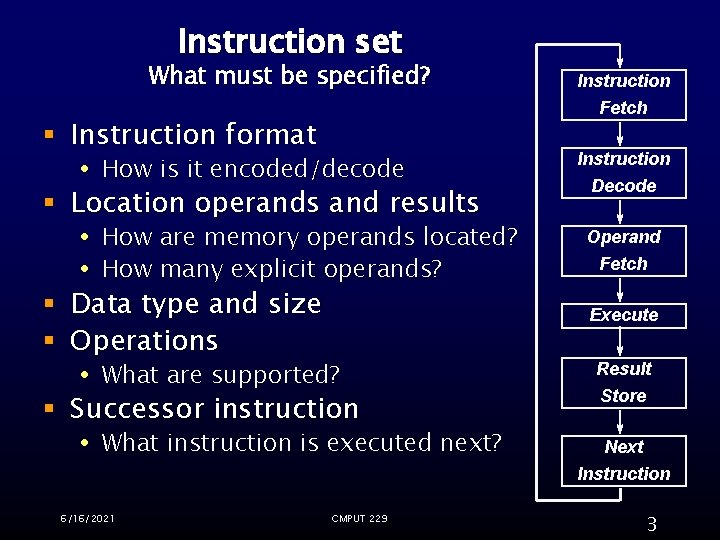

Instruction set What must be specified? Instruction Fetch § Instruction format How is it encoded/decode § Location operands and results How are memory operands located? How many explicit operands? § Data type and size § Operations Instruction Decode Operand Fetch Execute What are supported? § Successor instruction What instruction is executed next? Result Store Next Instruction 6/16/2021 CMPUT 229 3

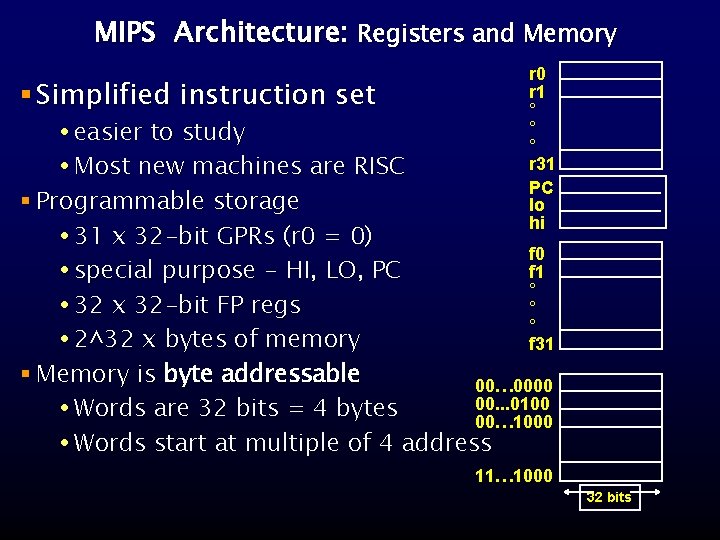

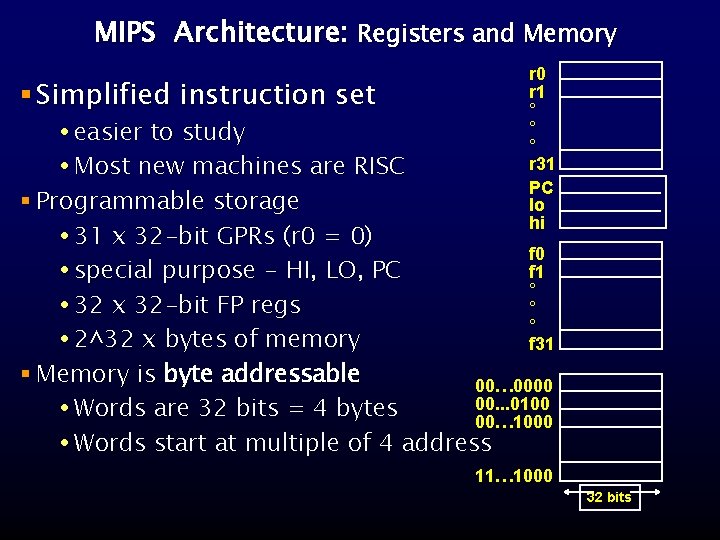

MIPS Architecture: Registers and Memory § Simplified instruction set r 0 r 1 ° ° ° r 31 PC lo hi easier to study Most new machines are RISC § Programmable storage 31 x 32 -bit GPRs (r 0 = 0) f 0 f 1 special purpose - HI, LO, PC ° 32 x 32 -bit FP regs ° ° 2^32 x bytes of memory f 31 § Memory is byte addressable 00… 0000 00. . . 0100 Words are 32 bits = 4 bytes 00… 1000 Words start at multiple of 4 address 11… 1000 32 bits

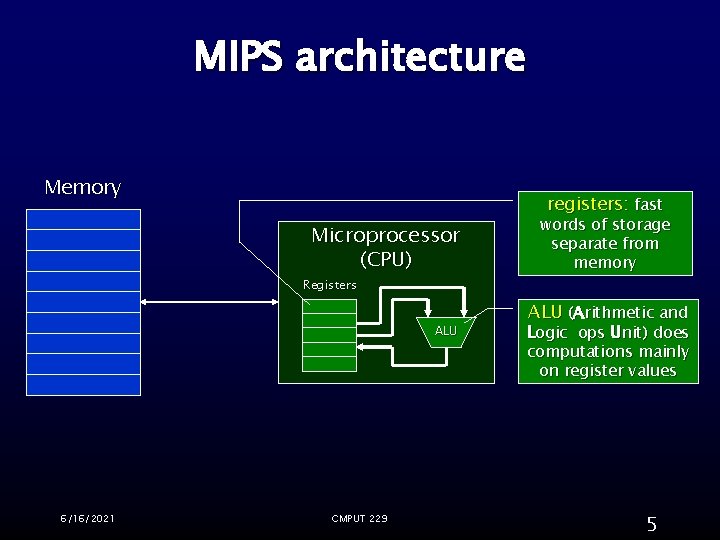

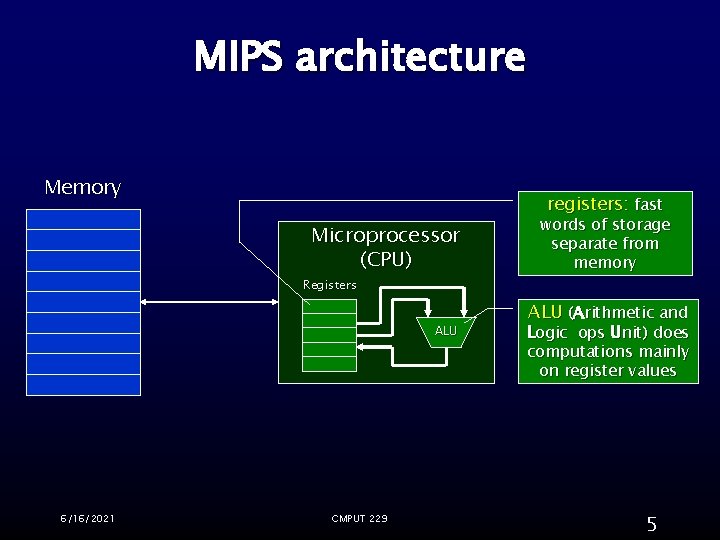

MIPS architecture Memory registers: fast Microprocessor (CPU) Registers ALU 6/16/2021 CMPUT 229 words of storage separate from memory ALU (Arithmetic and Logic ops Unit) does computations mainly on register values 5

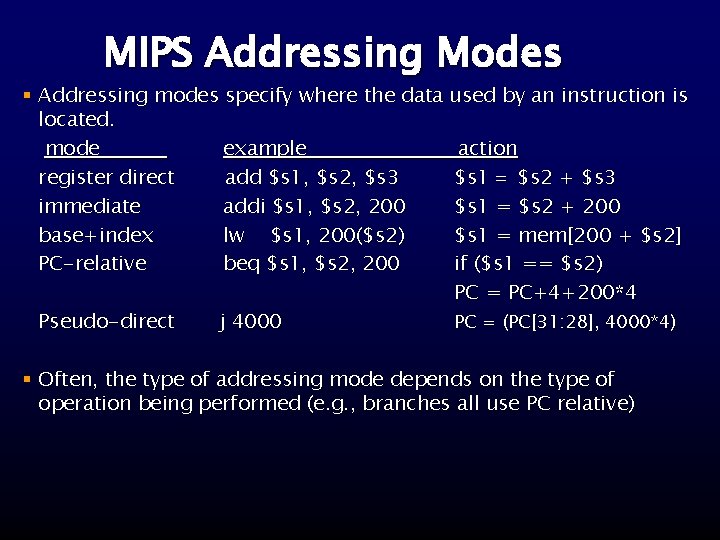

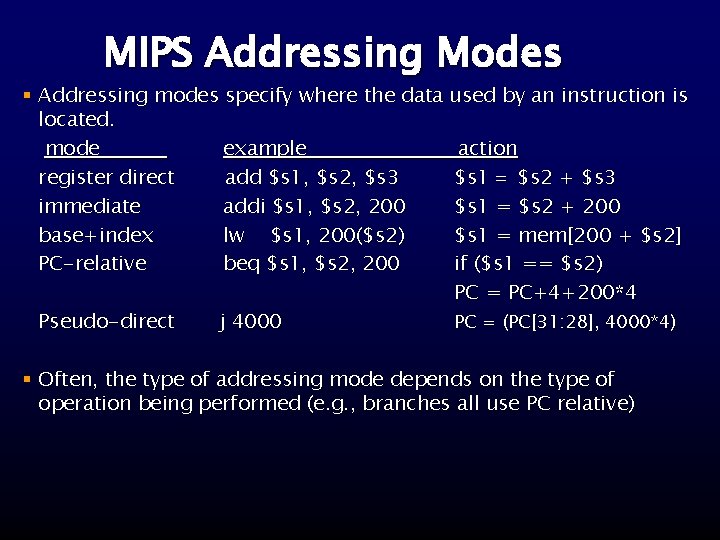

MIPS Addressing Modes § Addressing modes specify where the data used by an instruction is located. mode example action register direct add $s 1, $s 2, $s 3 $s 1 = $s 2 + $s 3 immediate addi $s 1, $s 2, 200 $s 1 = $s 2 + 200 base+index lw $s 1, 200($s 2) $s 1 = mem[200 + $s 2] PC-relative beq $s 1, $s 2, 200 if ($s 1 == $s 2) PC = PC+4+200*4 Pseudo-direct j 4000 PC = (PC[31: 28], 4000*4) § Often, the type of addressing mode depends on the type of operation being performed (e. g. , branches all use PC relative)

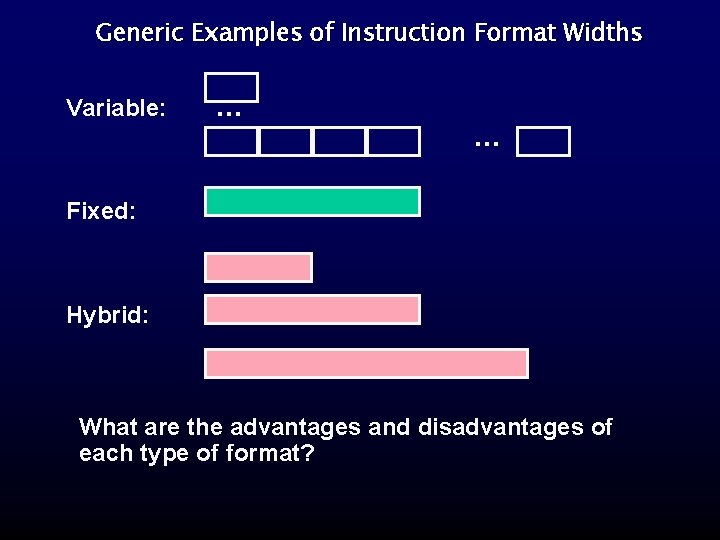

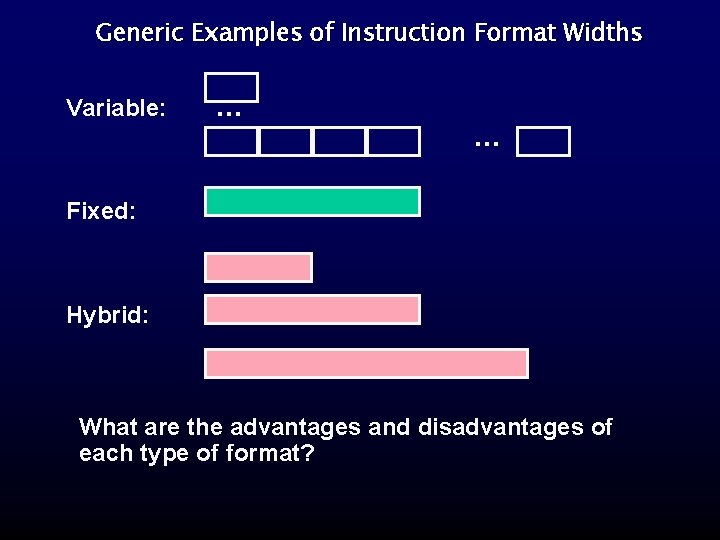

Generic Examples of Instruction Format Widths Variable: … … Fixed: Hybrid: What are the advantages and disadvantages of each type of format?

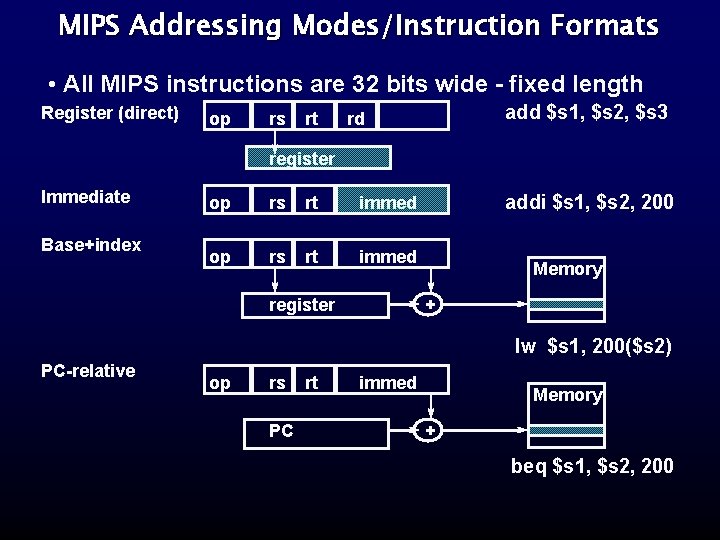

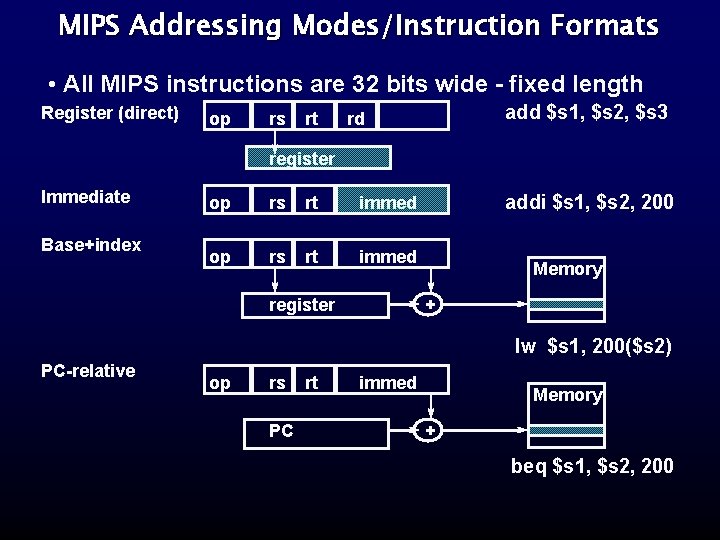

MIPS Addressing Modes/Instruction Formats • All MIPS instructions are 32 bits wide - fixed length Register (direct) op rs rt add $s 1, $s 2, $s 3 rd register Immediate Base+index op rs rt immed register addi $s 1, $s 2, 200 Memory + lw $s 1, 200($s 2) PC-relative op rs PC rt immed Memory + beq $s 1, $s 2, 200

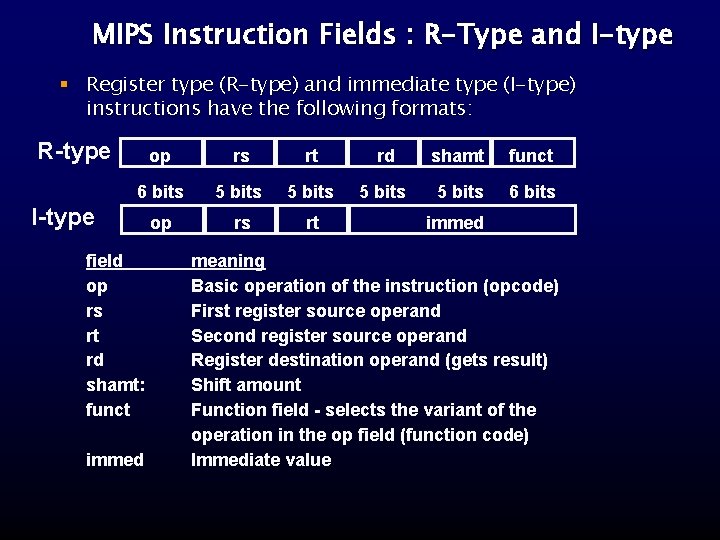

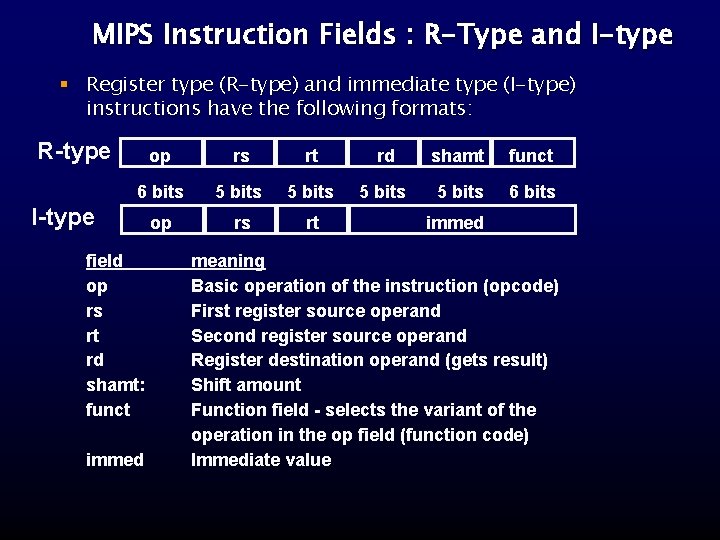

MIPS Instruction Fields : R-Type and I-type § Register type (R-type) and immediate type (I-type) instructions have the following formats: R-type op rs rt rd shamt funct 6 bits 5 bits 6 bits op rs rt I-type field op rs rt rd shamt: funct immed meaning Basic operation of the instruction (opcode) First register source operand Second register source operand Register destination operand (gets result) Shift amount Function field - selects the variant of the operation in the op field (function code) Immediate value

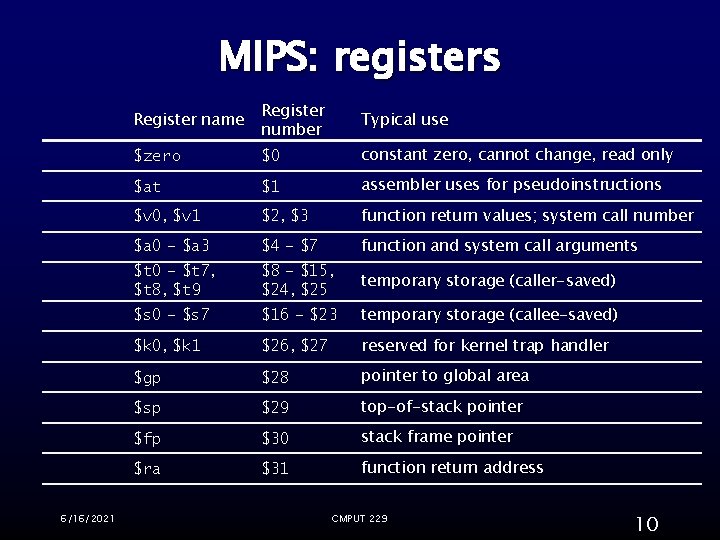

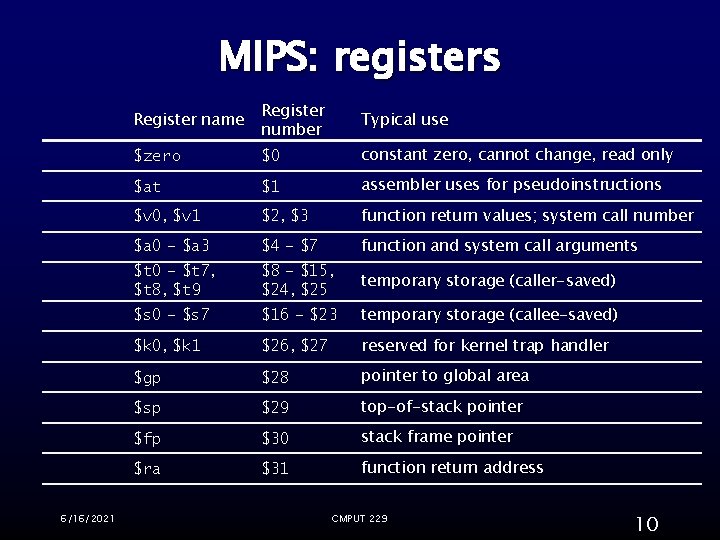

MIPS: registers Register name Register number $zero $0 constant zero, cannot change, read only $at $1 assembler uses for pseudoinstructions $v 0, $v 1 $2, $3 function return values; system call number $a 0 - $a 3 $4 - $7 function and system call arguments $t 0 - $t 7, $t 8, $t 9 $s 0 - $s 7 6/16/2021 Typical use $8 - $15, $24, $25 $16 - $23 temporary storage (caller-saved) temporary storage (callee-saved) $k 0, $k 1 $26, $27 reserved for kernel trap handler $gp $28 pointer to global area $sp $29 top-of-stack pointer $fp $30 stack frame pointer $ra $31 function return address CMPUT 229 10

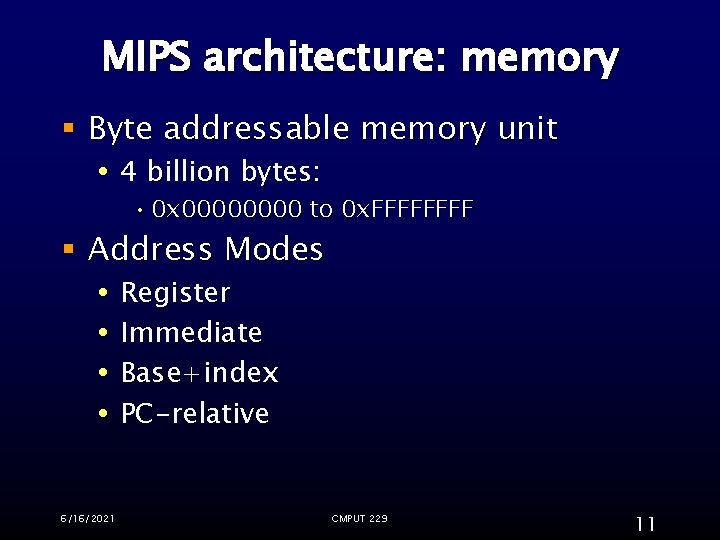

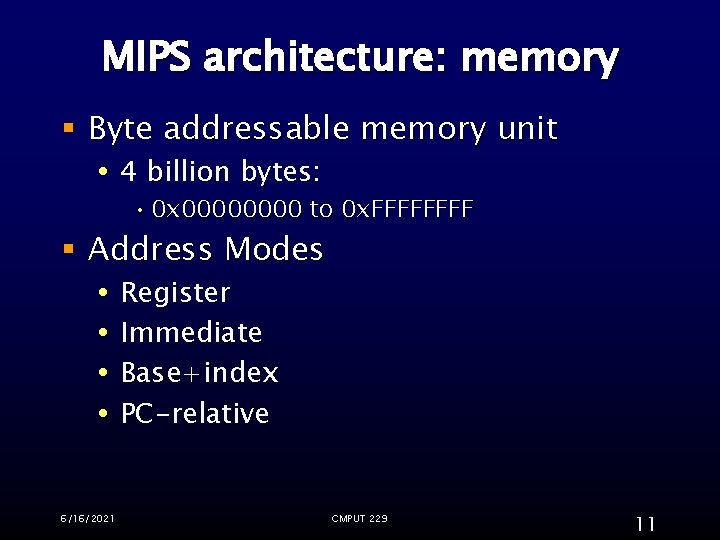

MIPS architecture: memory § Byte addressable memory unit 4 billion bytes: • 0 x 0000 to 0 x. FFFF § Address Modes Register Immediate Base+index PC-relative 6/16/2021 CMPUT 229 11

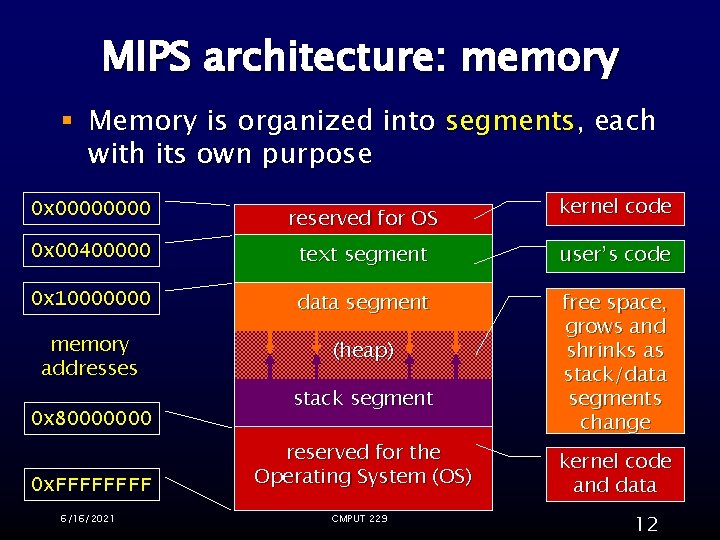

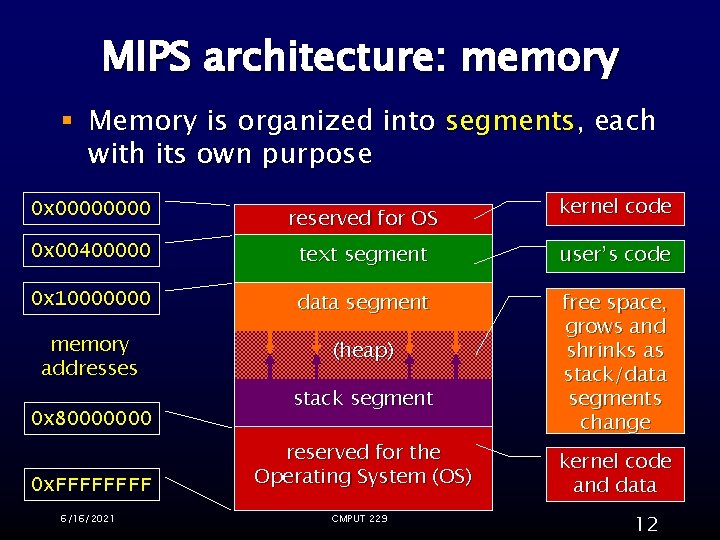

MIPS architecture: memory § Memory is organized into segments, each with its own purpose kernel code 0 x 0000 reserved for OS 0 x 00400000 text segment user’s code 0 x 10000000 data segment memory addresses (heap) free space, grows and shrinks as stack/data segments change 0 x 80000000 0 x. FFFF 6/16/2021 stack segment reserved for the Operating System (OS) CMPUT 229 kernel code and data 12

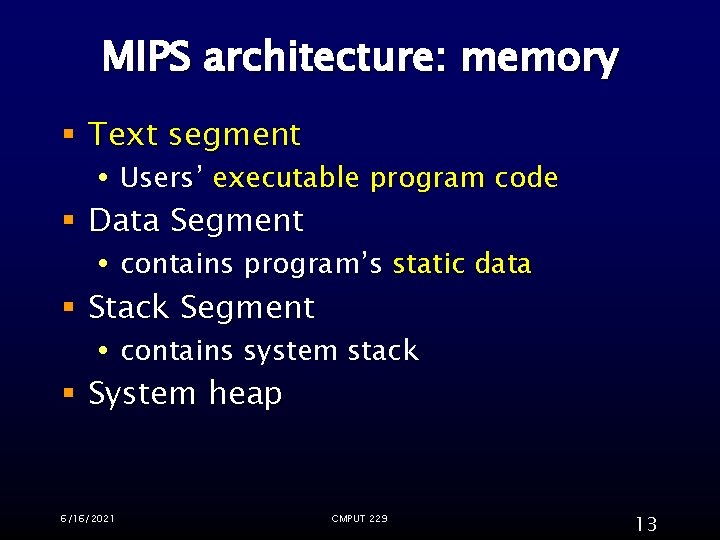

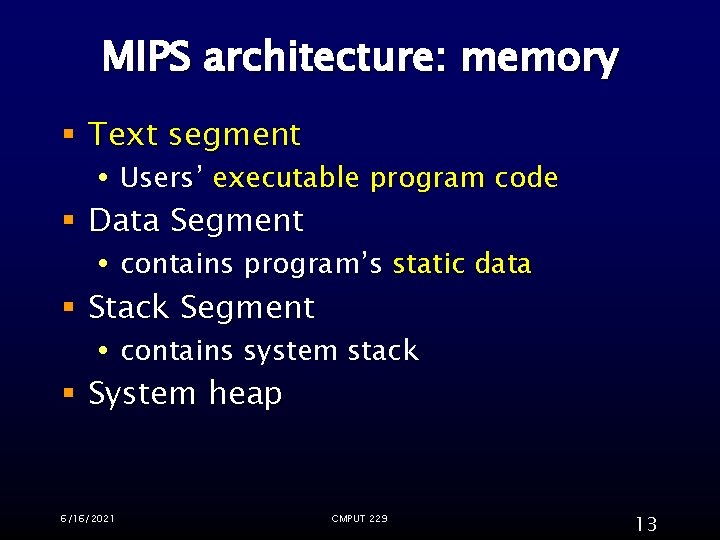

MIPS architecture: memory § Text segment Users’ executable program code § Data Segment contains program’s static data § Stack Segment contains system stack § System heap 6/16/2021 CMPUT 229 13

SPIM simulator § A freely-distributable program that simulates the operation of the MIPS R 2000/R 3000 architecture • Unix • X-window • MS Windows • Macintosh OS X 6/16/2021 CMPUT 229 14

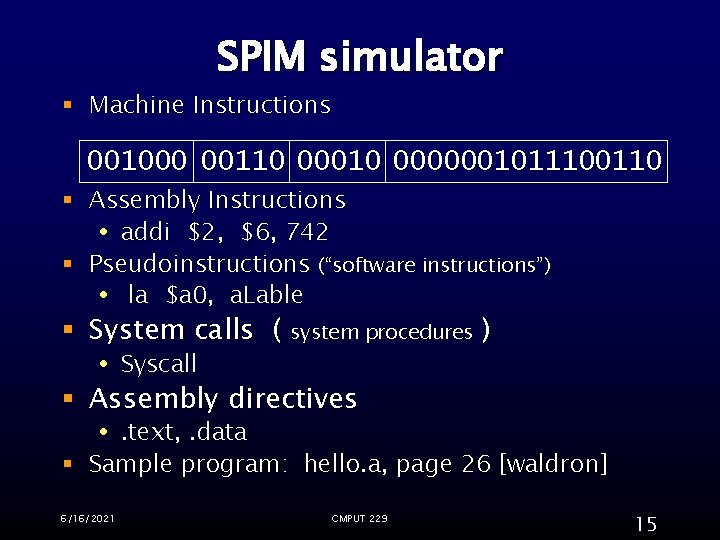

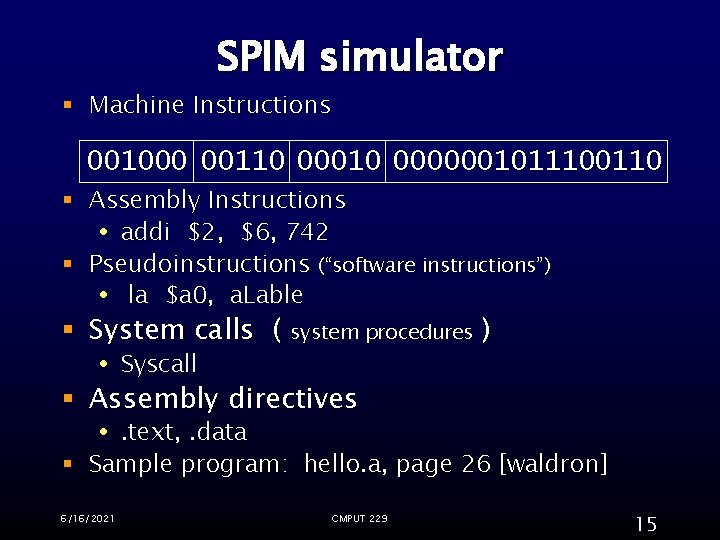

SPIM simulator § Machine Instructions 001000 00110 0000001011100110 § Assembly Instructions addi $2, $6, 742 § Pseudoinstructions (“software instructions”) la $a 0, a. Lable § System calls ( system procedures ) Syscall § Assembly directives . text, . data § Sample program: hello. a, page 26 [waldron] 6/16/2021 CMPUT 229 15

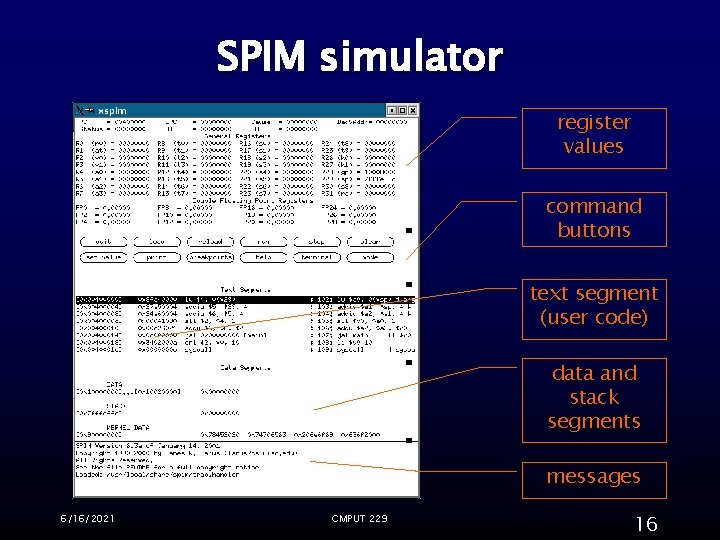

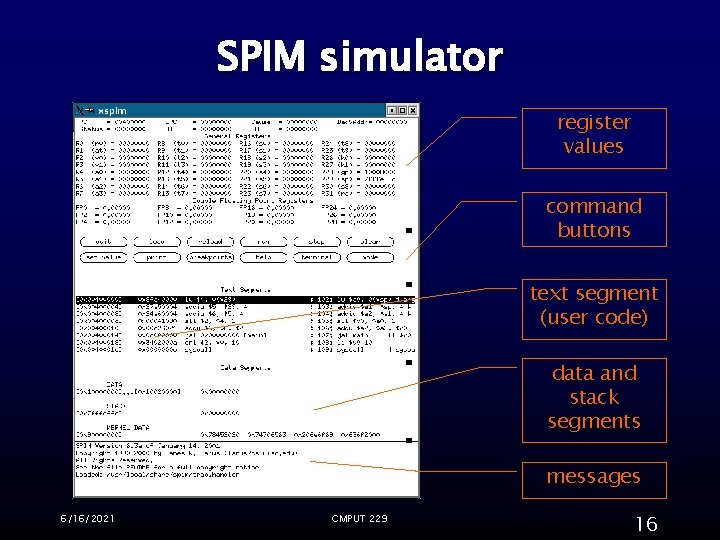

SPIM simulator register values command buttons text segment (user code) data and stack segments messages 6/16/2021 CMPUT 229 16