Memoryefficient Turbo decoding architecture for LDPC codes Mohammad

Memory-efficient Turbo decoding architecture for LDPC codes Mohammad M. Mansour and Naresh R. Shanbhag

Outline l l l l Introduction LDPC Codes Alternating View Turbo Decoding Message-Passing Algorithm Decoding Architecture Ramanujan Graphs Simulation results Conclusion

Introduction l l l LDPC codes were introduced by Gallager in 1961 and rediscovered by Mackay-Neal and Wiberg Irregular LDPC codes yielding bit-error rates that theoretically surpass the performance of the best codes known so far This paper attempts to promote LDPC codes as practical serious competitor to Turbo codes

Introduction (continue) l l TPMP: Two-phase message-passing algorithm Random and Stringent memory Interconnections complexity and Parallelism TDMP: Turbo-decoding messaging-passing

TPMP versus TDMP l l TDMP algorithm exhibits a faster convergence behavior and improvement in coding gain over the TPMP algorithm TDMP reduce > 75% memory overhead of the TPMP

LDPC codes l l LDPC is linear block code If all bit node have degree c and all check nodes have degree r, the code is call regular (c, r)-LDPC codes

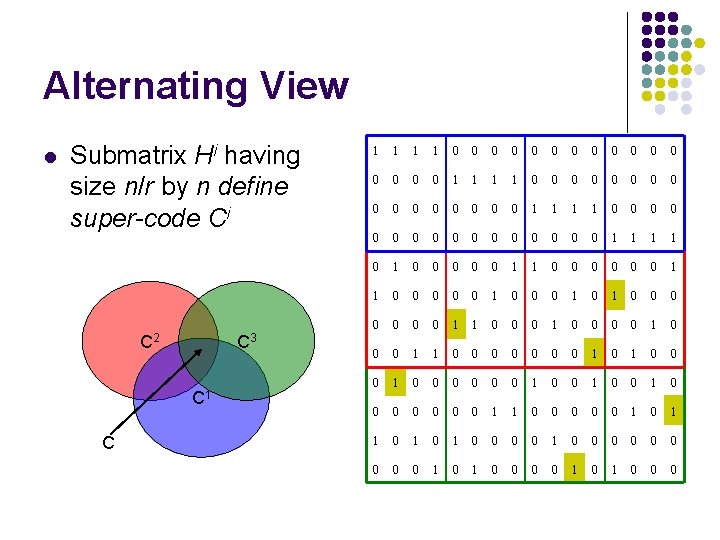

Alternating View l Submatrix Hi having size n/r by n define super-code Ci C 2 C 3 C 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 0 1 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 1 0 0 0 0 1 0 1 0 0 0

Construction H l l Hi are pseudo random permutation of the columns of H 1 Irregular LDPC codes can be similarly be defined by puncturing the super-code

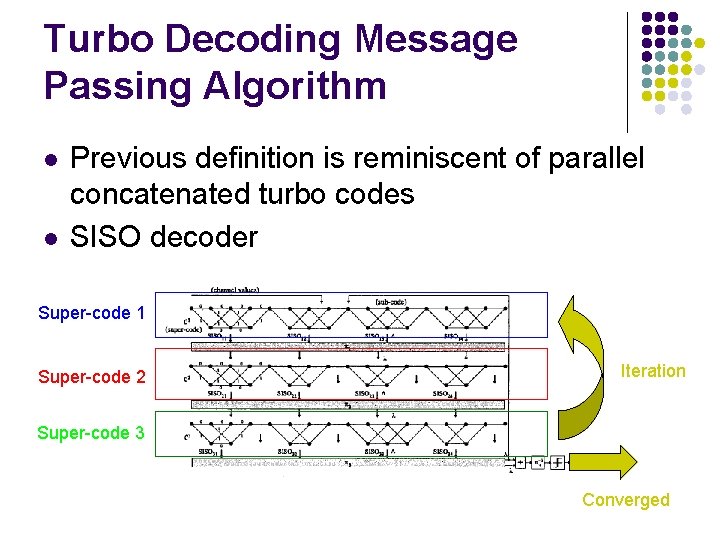

Turbo Decoding Message Passing Algorithm l l Previous definition is reminiscent of parallel concatenated turbo codes SISO decoder Super-code 1 Super-code 2 Iteration Super-code 3 Converged

Turbo Decoding Message Passing Algorithm (Continue) l l l Reduce memory requirement Fast convergence (20%~50% iteration) Reduce decoding latency

Decoding Architecture l Newly generated bit messages from preceding super-codes are directly used to generate bit messages of succeeding supercodes on the same iteration

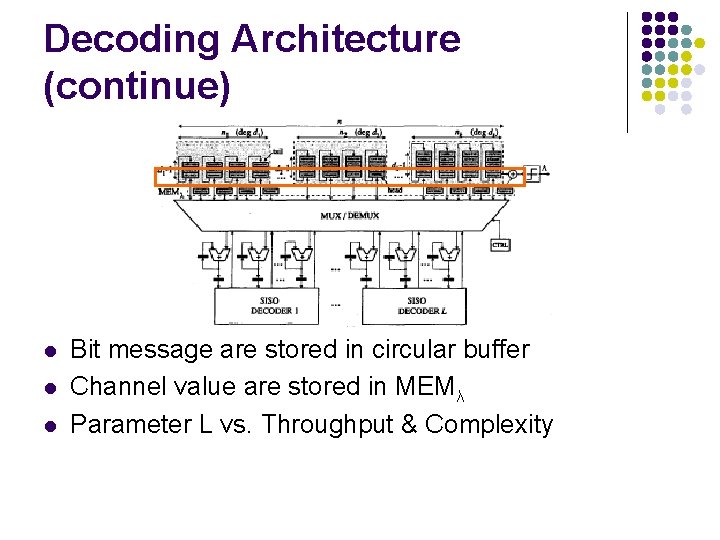

Decoding Architecture (continue) l l l Bit message are stored in circular buffer Channel value are stored in MEMλ Parameter L vs. Throughput & Complexity

Ramanujan Graph l l Non-trivial eigenvalues of adjacency matrix ARG(q, p) <= p is node-degree, q is number of vertices p and q are distinct odd primes If p is a quadratic non-residue modulo q, biregular bipartite graph having vertices in eachpartition and uniform node-degrees of (p+1)

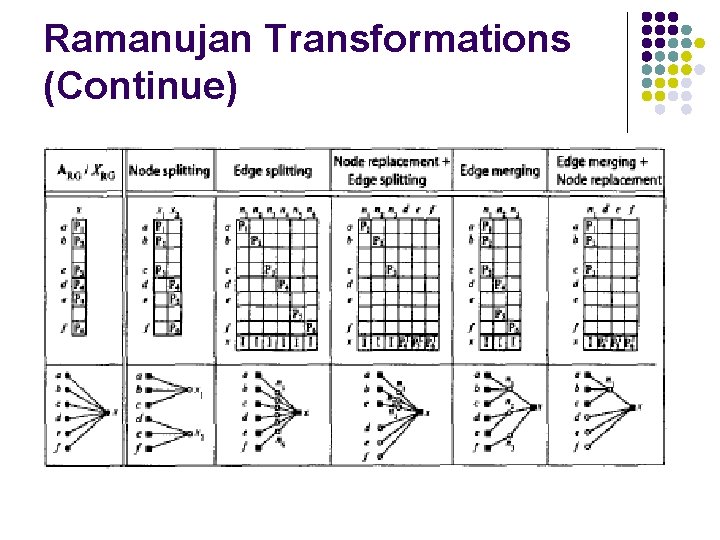

Ramanujan Transformations l l l Node Spitting Edge Splitting Node Replacement + Edge Splitting Edge Merging + Edge splitting

Ramanujan Transformations (Continue)

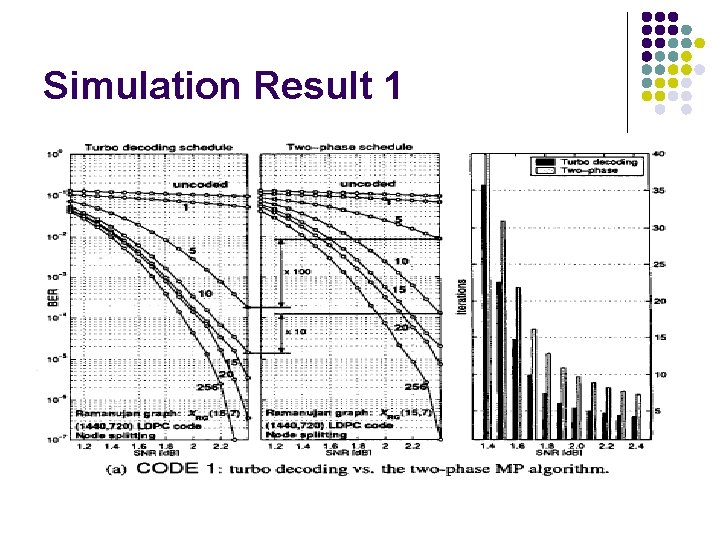

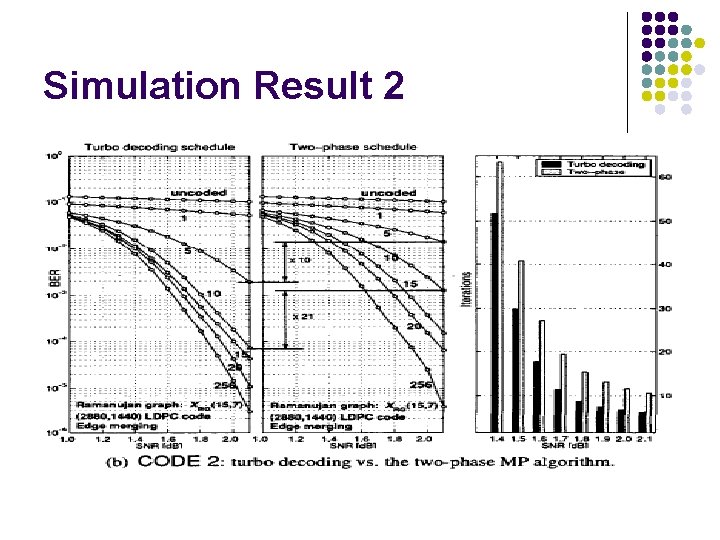

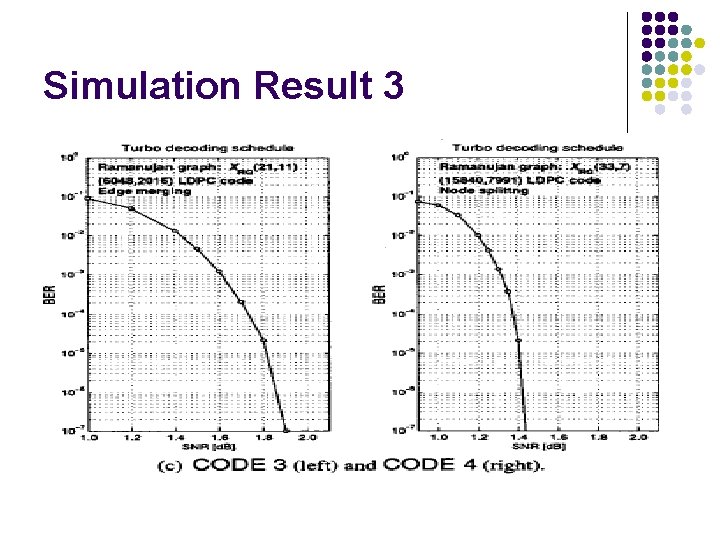

Simulations l l l Over AWGN channel with BPSK modulation Code 1: p=7, q=15, n=1440, R=1/2, using node splitting Code 2: p=7, q=15, n=2880, R=1/2, using edge merging Code 3: p=11, q=21, n=6048, R=1/3, using edge merging Code 4: p=7, q=33, n=15840 R=0. 504, using node splitting

Simulation Result 1

Simulation Result 2

Simulation Result 3

Conclusion l l l If we want to use this method we must study architecture of Turbo Code Study Algebra and Number Theory (for code search or code design) Build a simulation model to evaluate our code and architecture

- Slides: 20