Aggregated Circulant Matrix Based LDPC Codes Yuming Zhu

Aggregated Circulant Matrix Based LDPC Codes Yuming Zhu and Chaitali Chakrabarti Department of Electrical Engineering Arizona State University, Tempe 2006 -05 -19 @ICASSP 1

Outline Introduction to LDPC codes n Iterative decoding of LDPC codes n Aggregated Circulant Matrix (ACM) based LDPC codes n ¨ Construction algorithm ¨ BER performance ¨ Decoder architecture n Concluding remarks 2006 -05 -19 @ICASSP 2

Introduction to LDPC codes ¨ LDPC codes are linear block codes with sparse parity check matrix. (Low complexity) ¨ Can be represented by bipartite (Tanner) graph. ¨ LDPC codes were proposed by Gallager in 1962. Rediscovered in 90’s because of the success of Turbo codes. ¨ Adopted in IEEE 802. 16 e (Wi. Max), 10 G Base. T, DVB -S 2, IEEE 802. 11 n (in consideration) 2006 -05 -19 @ICASSP 3

Introduction (contd. ) ¨ LDPC n code is Shannon limit approaching. Chung (Trans. IT, Feb 2001) reported 0. 0045 d. B to AWGN channel Shannon limit with irregular LDPC code. ¨ Very simple data path. ¨ Potential to achieve massive parallelism and high throughput. n 1 G bps LDPC decoder (Blanksby and Howland 2001) 2006 -05 -19 @ICASSP 4

Related Work n High speed LDPC decoder architectures ¨ C. Howland 2001(Fully Parallel) ¨ T. Zhang 2001 (Partially Parallel) ¨ M. M. Mansour 2003 (Partially Parallel) ¨ D. E. Hocevar 2004 (Partially Parallel) n Partially Parallel decoding for sub-matrix with multiple shifted identity matrices ¨ Z. Wang 2005 (With restriction on the shift values; for geometrical LDPC codes) 2006 -05 -19 @ICASSP 5

Outline Introduction to LDPC codes n Iterative decoding of LDPC codes n Aggregated Circulant Matrix (ACM) based LDPC codes n ¨ Construction algorithm ¨ BER performance ¨ Decoder architecture n Conclusion and future work 2006 -05 -19 @ICASSP 6

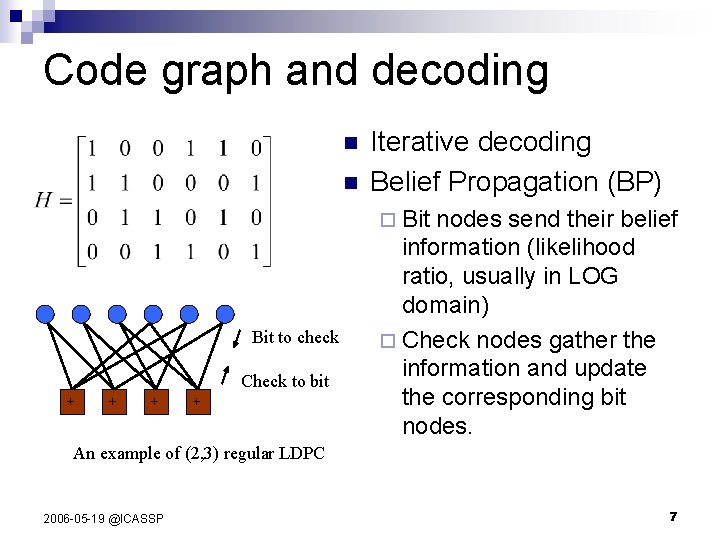

Code graph and decoding n n Iterative decoding Belief Propagation (BP) ¨ Bit to check Check to bit + + nodes send their belief information (likelihood ratio, usually in LOG domain) ¨ Check nodes gather the information and update the corresponding bit nodes. An example of (2, 3) regular LDPC 2006 -05 -19 @ICASSP 7

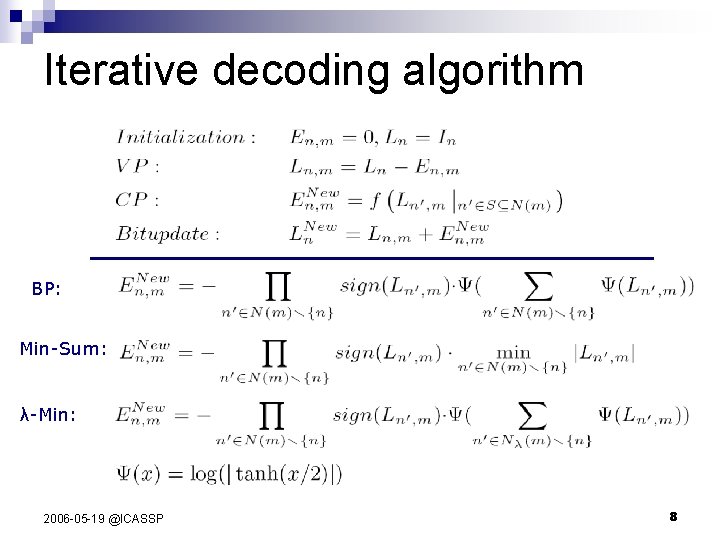

Iterative decoding algorithm BP: Min-Sum: λ-Min: 2006 -05 -19 @ICASSP 8

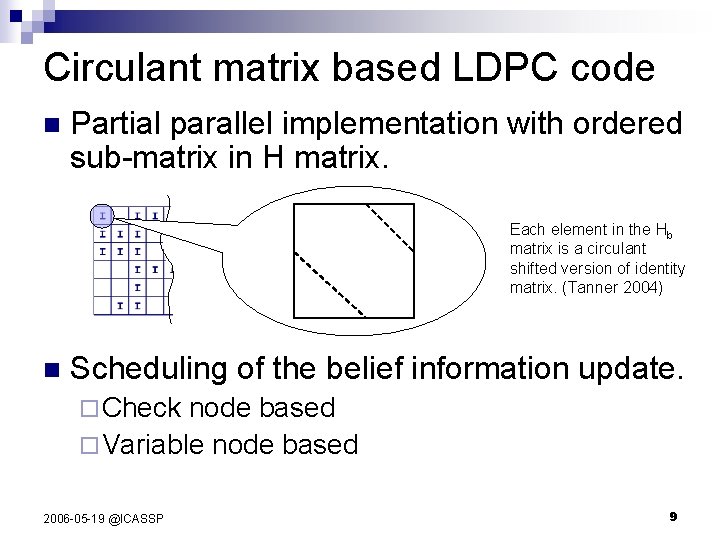

Circulant matrix based LDPC code n Partial parallel implementation with ordered sub-matrix in H matrix. Each element in the Hb matrix is a circulant shifted version of identity matrix. (Tanner 2004) n Scheduling of the belief information update. ¨ Check node based ¨ Variable node based 2006 -05 -19 @ICASSP 9

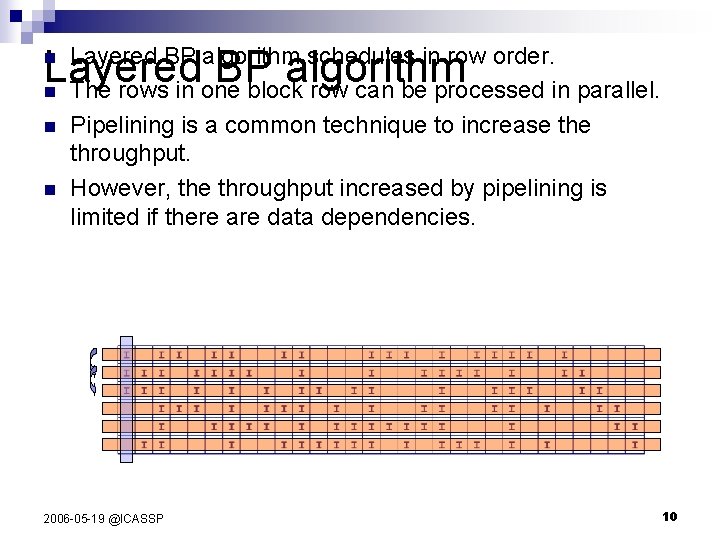

Layered BP algorithm schedules in row order. The rows in one block row can be processed in parallel. Pipelining is a common technique to increase throughput. However, the throughput increased by pipelining is limited if there are data dependencies. Layered BP algorithm n n 2006 -05 -19 @ICASSP 10

Outline Introduction to LDPC codes n Iterative decoding of LDPC codes n Aggregated Circulant Matrix (ACM) based LDPC codes n ¨ Construction algorithm ¨ BER performance ¨ Decoder architecture n Conclusion and future work 2006 -05 -19 @ICASSP 11

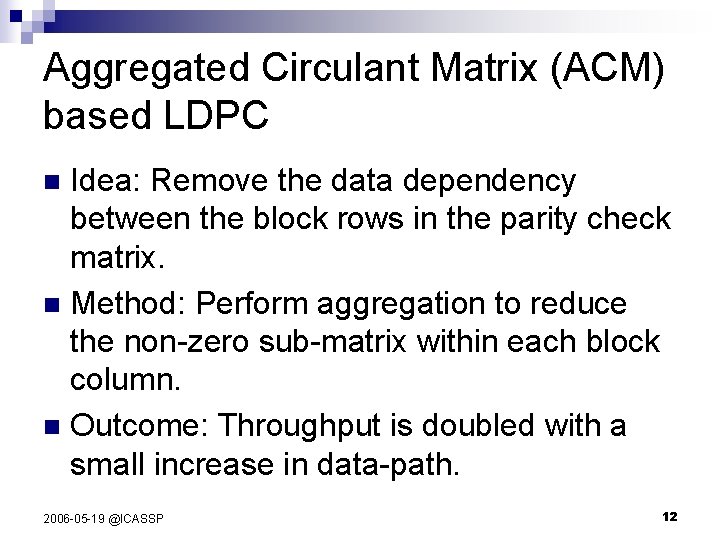

Aggregated Circulant Matrix (ACM) based LDPC Idea: Remove the data dependency between the block rows in the parity check matrix. n Method: Perform aggregation to reduce the non-zero sub-matrix within each block column. n Outcome: Throughput is doubled with a small increase in data-path. n 2006 -05 -19 @ICASSP 12

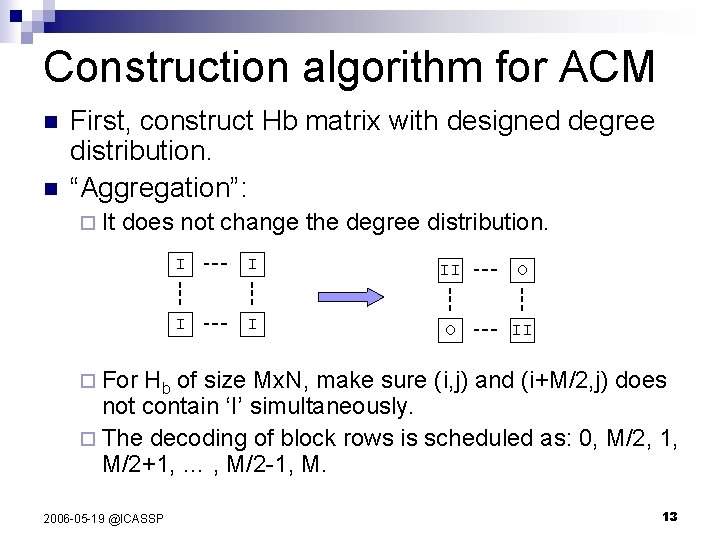

Construction algorithm for ACM n n First, construct Hb matrix with designed degree distribution. “Aggregation”: ¨ It does not change the degree distribution. I I II O II ¨ For Hb of size Mx. N, make sure (i, j) and (i+M/2, j) does not contain ‘I’ simultaneously. ¨ The decoding of block rows is scheduled as: 0, M/2, 1, M/2+1, … , M/2 -1, M. 2006 -05 -19 @ICASSP 13

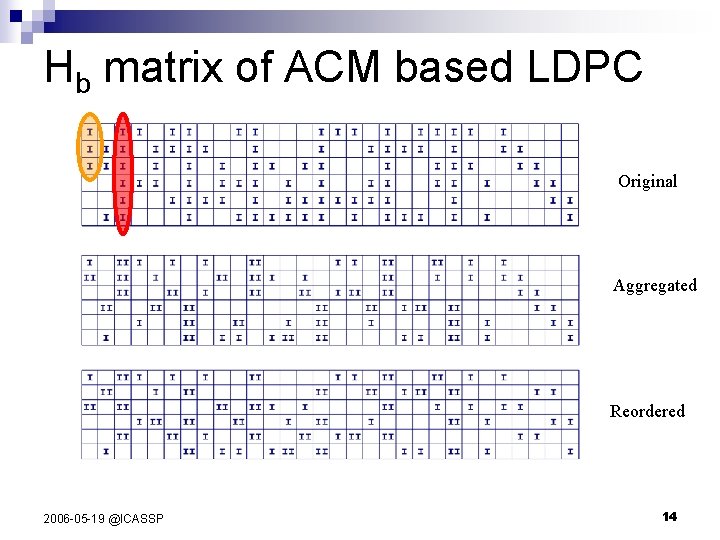

Hb matrix of ACM based LDPC Original Aggregated Reordered 2006 -05 -19 @ICASSP 14

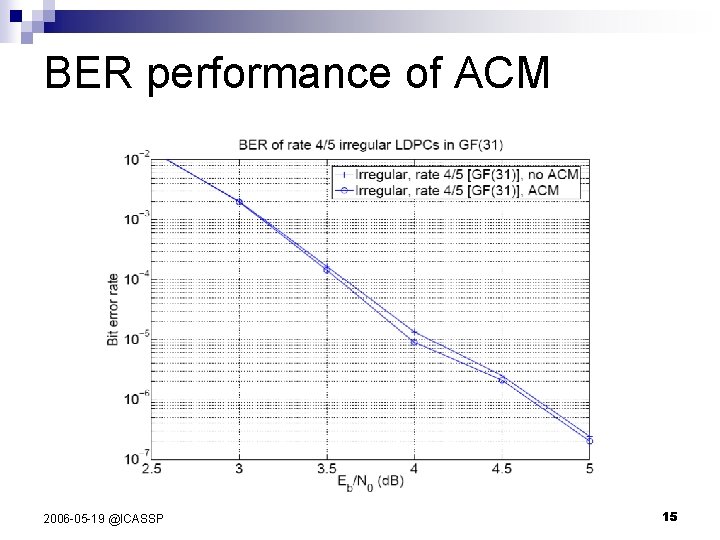

BER performance of ACM 2006 -05 -19 @ICASSP 15

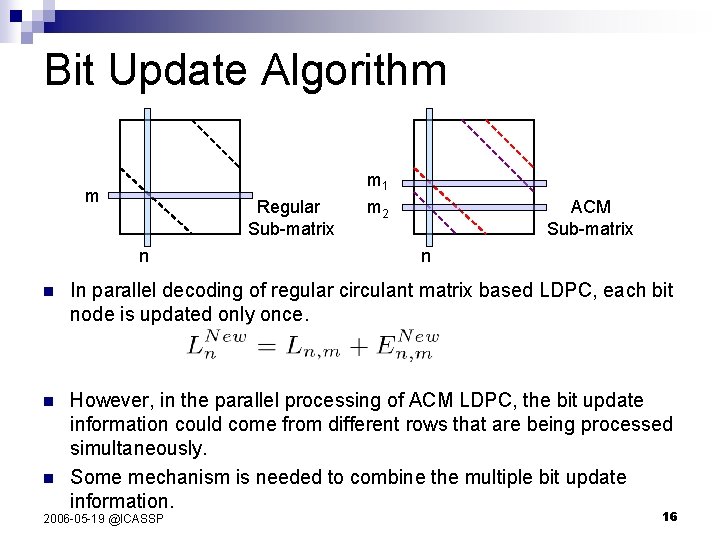

Bit Update Algorithm m 1 m Regular Sub-matrix n m 2 ACM Sub-matrix n n In parallel decoding of regular circulant matrix based LDPC, each bit node is updated only once. n However, in the parallel processing of ACM LDPC, the bit update information could come from different rows that are being processed simultaneously. Some mechanism is needed to combine the multiple bit update information. n 2006 -05 -19 @ICASSP 16

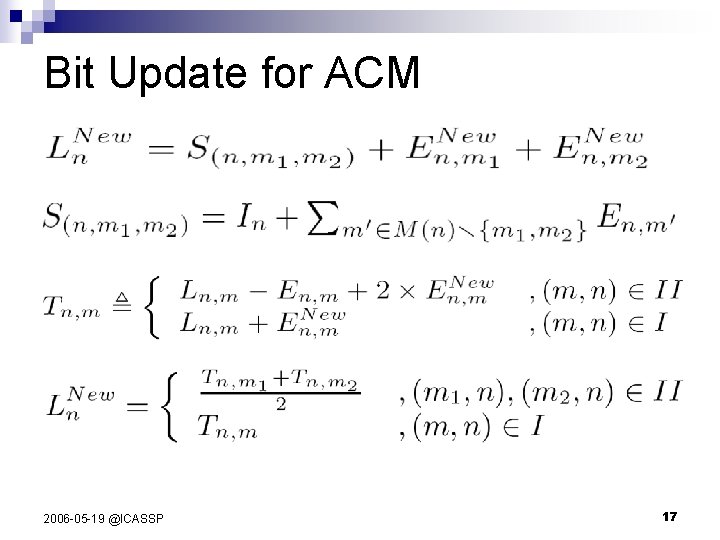

Bit Update for ACM 2006 -05 -19 @ICASSP 17

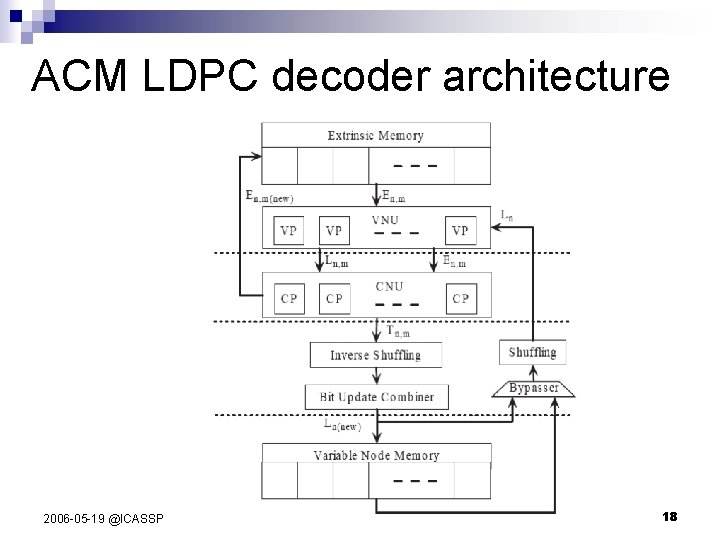

ACM LDPC decoder architecture 2006 -05 -19 @ICASSP 18

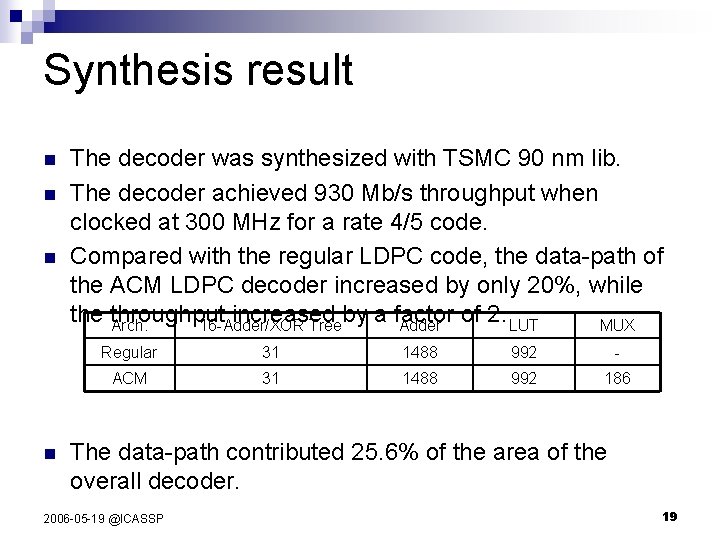

Synthesis result n n The decoder was synthesized with TSMC 90 nm lib. The decoder achieved 930 Mb/s throughput when clocked at 300 MHz for a rate 4/5 code. Compared with the regular LDPC code, the data-path of the ACM LDPC decoder increased by only 20%, while throughput increased by a factor of 2. LUT Arch. 16 -Adder/XOR Tree Adder MUX Regular 31 1488 992 - ACM 31 1488 992 186 The data-path contributed 25. 6% of the area of the overall decoder. 2006 -05 -19 @ICASSP 19

Outline Introduction to LDPC codes n Iterative decoding of LDPC codes n Aggregated Circulant Matrix (ACM) based LDPC codes n ¨ Construction algorithm ¨ BER performance ¨ Decoder architecture n Conclusion and future work 2006 -05 -19 @ICASSP 20

Concluding Remarks n n n The proposed ACM LDPC code has comparable performance with the regular LDPC codes. The advantage is that it can be decoded with a two-fold increase in the throughput at the expense of only 20% increase in data-path complexity. Efficient implementation of the aggregation algorithm with more than 2 identity matrices is still an open problem. 2006 -05 -19 @ICASSP 21

Thank You!! Questions? 2006 -05 -19 @ICASSP 22

- Slides: 22