Lect The FP adder test plan As noted

- Slides: 9

Lect : The FP adder test plan • As noted earlier – there is a difference in black box and while box testing and verificiation. • However much of what needs to be tested for is much the same. • The FP adder assignment is white box verification. – You are working for the same company as the design team and the detailed code is available. • The following slide are some of the analysis of floating point addition that needed to be taken into account in the verification. EE 694 v-Verification-Lect 11 -1 -

The input section • These tests can use the fact that this is white box verification and check internal values or just check the final output. • Basic assumption of the previous point is that the design is correct or near correct. • What needs to be checked. • First that inputs can be latched from the bus and that the bus can change after the latch closes and the input is not affected. • Also, that the input can be latched effectively. EE 694 v-Verification-Lect 11 -2 -

Input section operations • By checking the operation of two units the operation of multiplexors, crossbar, and fixed value selection, and control signal generation is verified. • Those two units are the exponent difference calculation and the linear shifter. • For this, exponent differences that result in no shift of the smaller input, to overshift by several positions is needed. This must be done for the exponent being in about 3 distinct ranges. – – – A exponent fixed at 48, B exponent at 16 to 80 A exponent fixed at 120, B exponent from 92 to 152 A exponent fixed at 210, B exponent from 182 to 242 Then hold B fixed and vary A Do for both A + B and A – B EE 694 v-Verification-Lect 11 -3 -

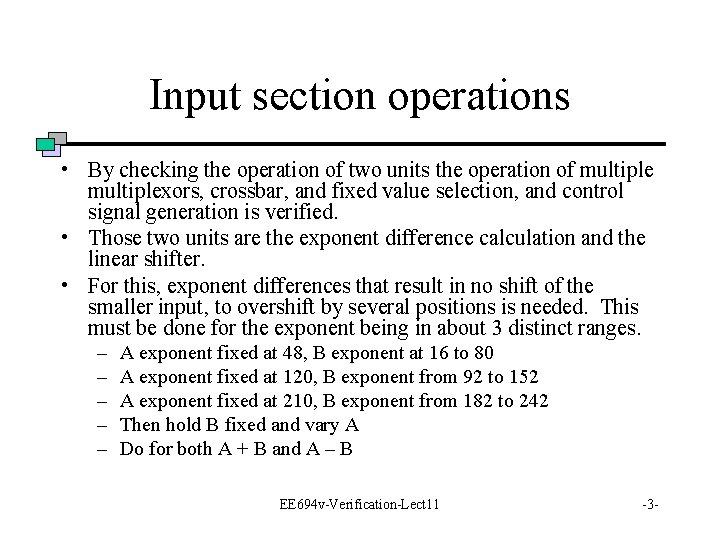

Scan of entire architecture 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 4

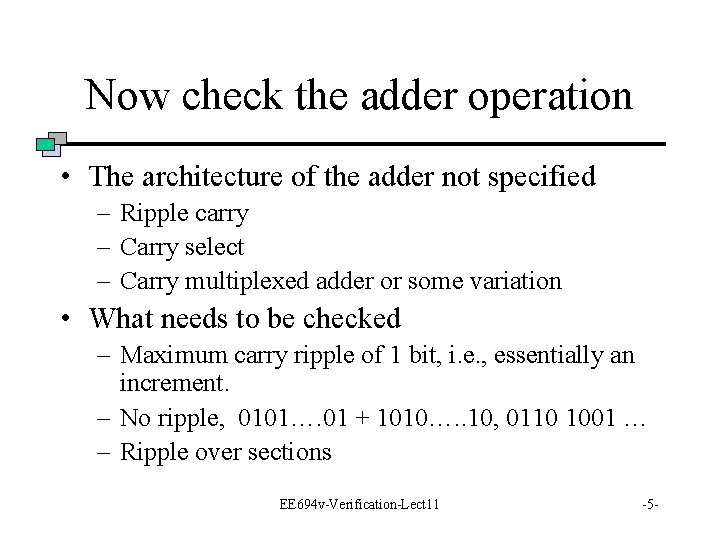

Now check the adder operation • The architecture of the adder not specified – Ripple carry – Carry select – Carry multiplexed adder or some variation • What needs to be checked – Maximum carry ripple of 1 bit, i. e. , essentially an increment. – No ripple, 0101…. 01 + 1010…. . 10, 0110 1001 … – Ripple over sections EE 694 v-Verification-Lect 11 -5 -

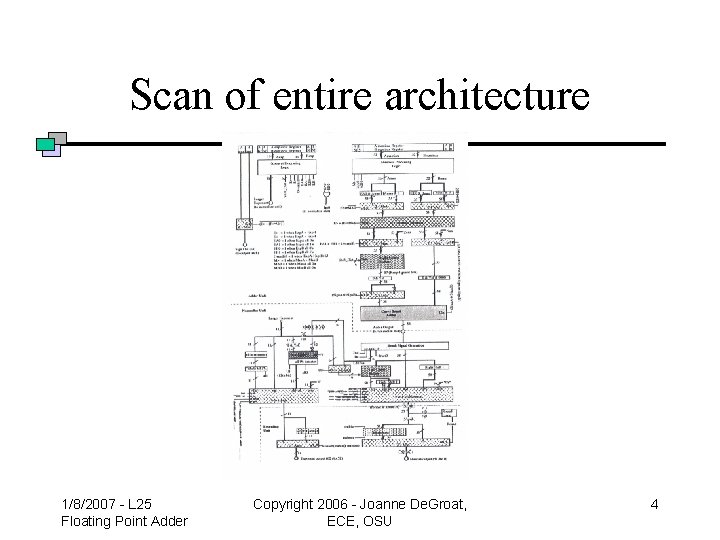

Scan of entire architecture 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 6

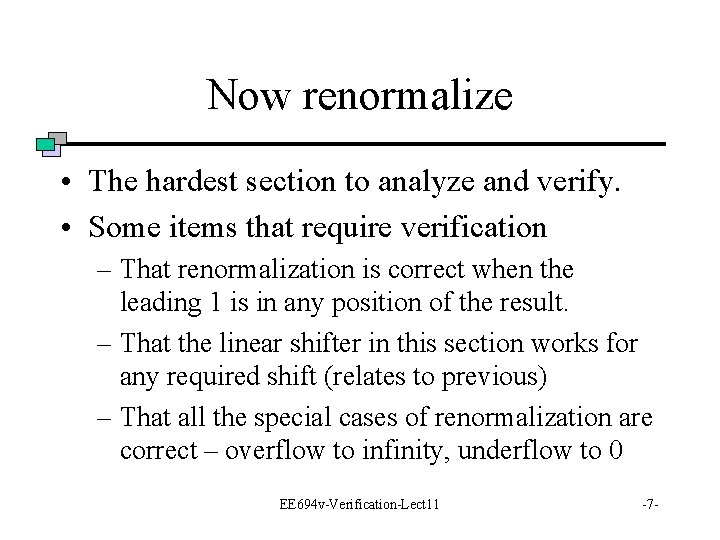

Now renormalize • The hardest section to analyze and verify. • Some items that require verification – That renormalization is correct when the leading 1 is in any position of the result. – That the linear shifter in this section works for any required shift (relates to previous) – That all the special cases of renormalization are correct – overflow to infinity, underflow to 0 EE 694 v-Verification-Lect 11 -7 -

Scan of entire architecture 1/8/2007 - L 25 Floating Point Adder Copyright 2006 - Joanne De. Groat, ECE, OSU 8

The plan content • The plan details the previous points along with how the tests will be generated and checked. • Also, the number of tests needed to raise the confidence level to acceptable and how it allows the effort to meet the criteria of success. EE 694 v-Verification-Lect 11 -9 -