RANGKAIAN LOGIKA KOMBINASIONAL 1 175 DEFINISI RANGKAIAN LOGIKA

RANGKAIAN LOGIKA KOMBINASIONAL (1) 175

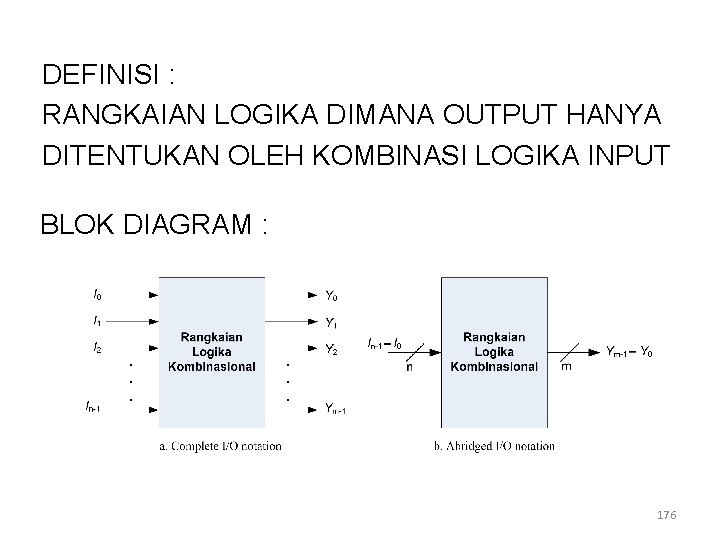

DEFINISI : RANGKAIAN LOGIKA DIMANA OUTPUT HANYA DITENTUKAN OLEH KOMBINASI LOGIKA INPUT BLOK DIAGRAM : 176

Prosedur Desain 1. 2. 3. 4. 5. 6. Menentukan Spesifikasi Rangkaian Menentukan Algoritma Menentukan Tabel Kebenaran Menentukan Fungsi Keluaran Rangkaian Menentukan Diagram Logika Menguji Hasil Keluaran 177

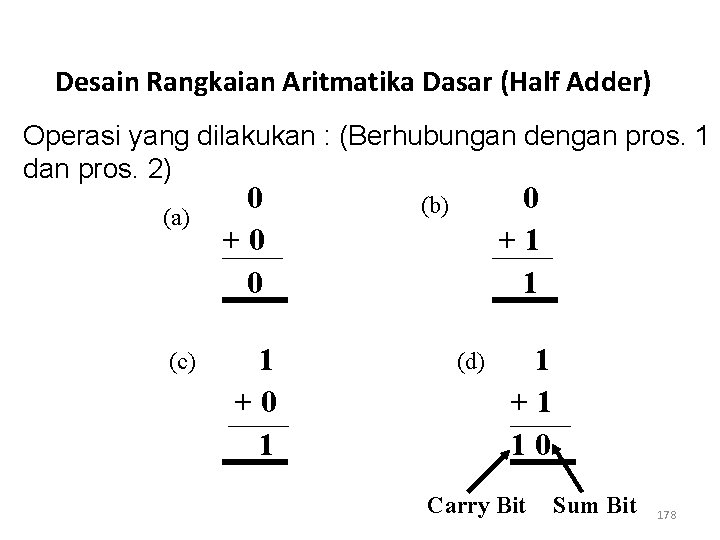

Desain Rangkaian Aritmatika Dasar (Half Adder) Operasi yang dilakukan : (Berhubungan dengan pros. 1 dan pros. 2) (a) (c) 0 +0 0 1 +0 1 0 +1 1 (b) (d) 1 +1 10 Carry Bit Sum Bit 178

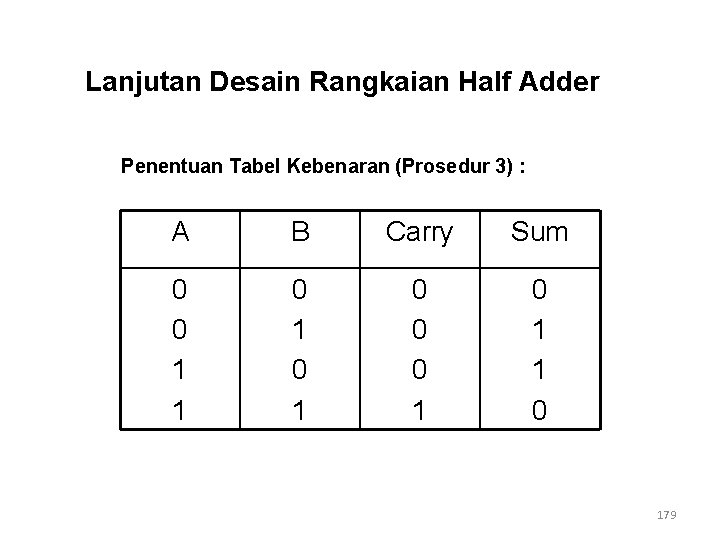

Lanjutan Desain Rangkaian Half Adder Penentuan Tabel Kebenaran (Prosedur 3) : A B Carry Sum 0 0 1 1 0 1 0 0 0 1 1 0 179

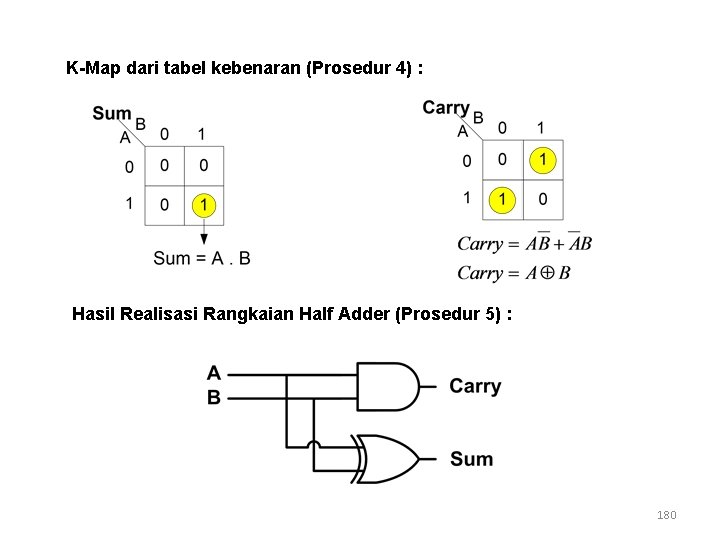

K-Map dari tabel kebenaran (Prosedur 4) : Hasil Realisasi Rangkaian Half Adder (Prosedur 5) : 180

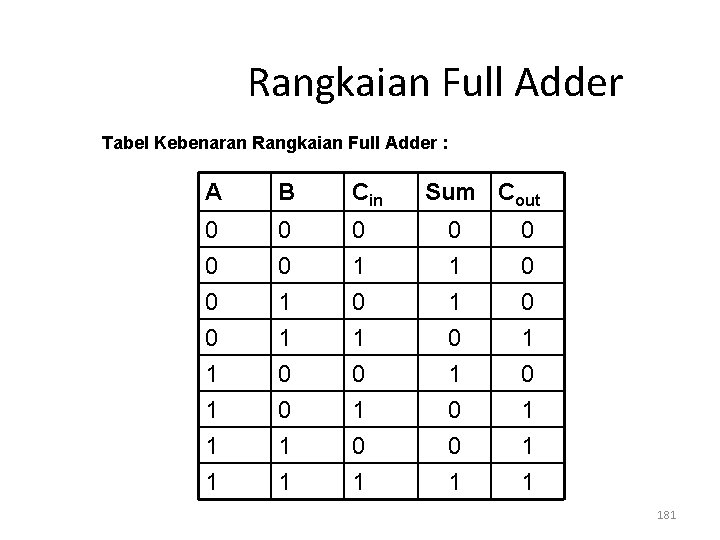

Rangkaian Full Adder Tabel Kebenaran Rangkaian Full Adder : A B Cin Sum Cout 0 0 0 1 1 0 0 1 1 1 0 1 0 0 1 1 1 181

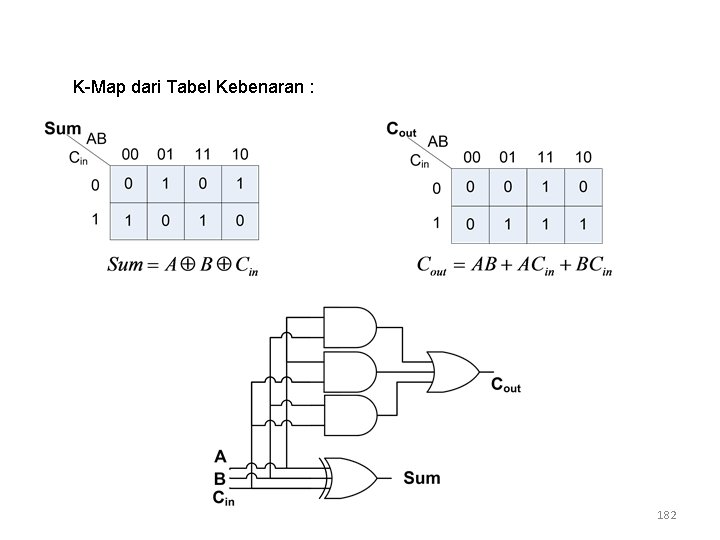

K-Map dari Tabel Kebenaran : 182

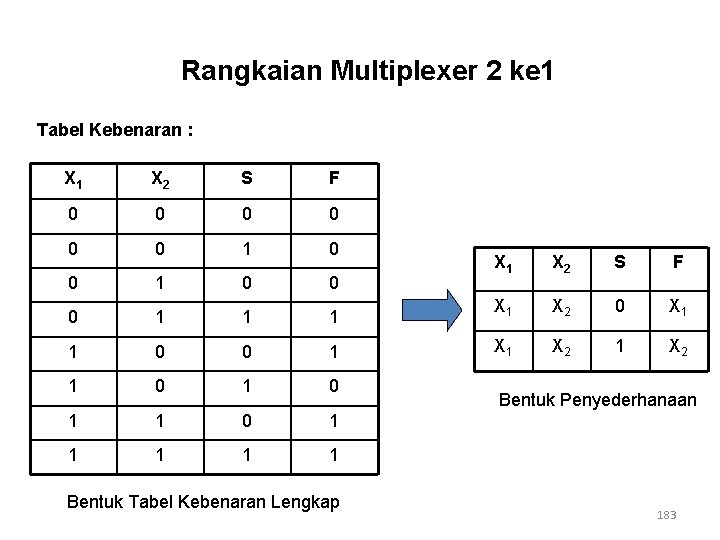

Rangkaian Multiplexer 2 ke 1 Tabel Kebenaran : X 1 X 2 S F 0 0 0 1 1 1 0 1 X 2 S F 1 X 2 0 X 1 0 1 X 2 0 1 1 1 Bentuk Tabel Kebenaran Lengkap Bentuk Penyederhanaan 183

K-Map dari Tabel Kebenaran : Realisasi dan Simbol Rangkaian : 184

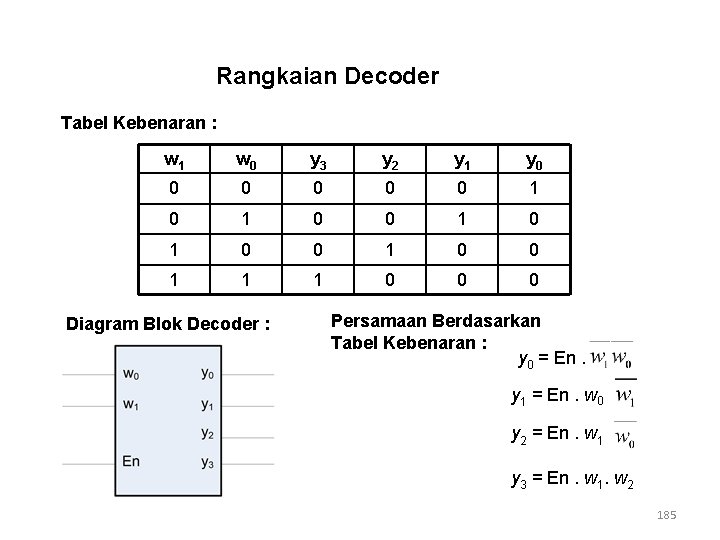

Rangkaian Decoder Tabel Kebenaran : w 1 w 0 y 3 y 2 y 1 y 0 0 0 1 0 1 0 0 1 1 1 0 0 0 Diagram Blok Decoder : Persamaan Berdasarkan Tabel Kebenaran : y 0 = En. y 1 = En. w 0 y 2 = En. w 1 y 3 = En. w 1. w 2 185

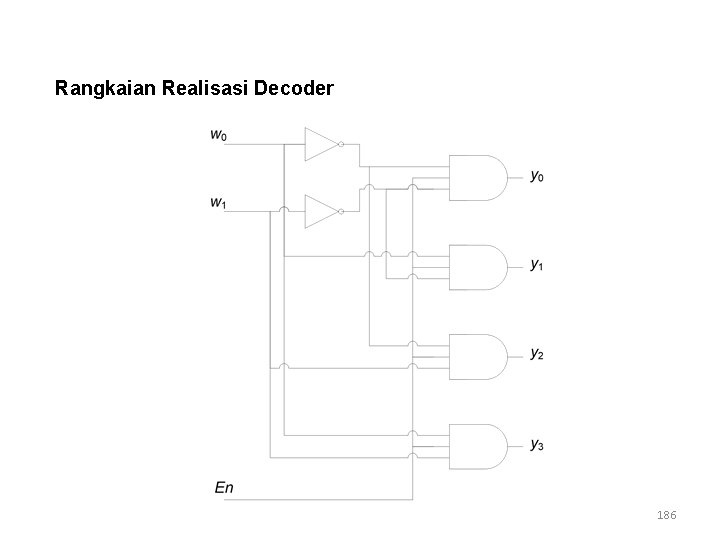

Rangkaian Realisasi Decoder 186

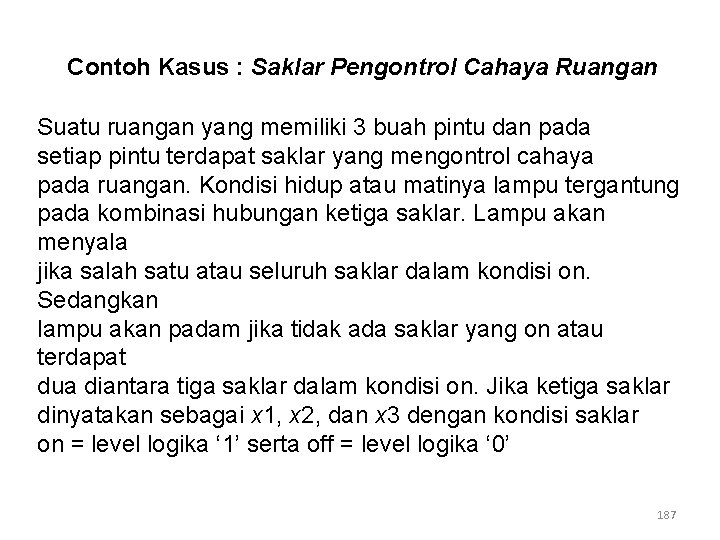

Contoh Kasus : Saklar Pengontrol Cahaya Ruangan Suatu ruangan yang memiliki 3 buah pintu dan pada setiap pintu terdapat saklar yang mengontrol cahaya pada ruangan. Kondisi hidup atau matinya lampu tergantung pada kombinasi hubungan ketiga saklar. Lampu akan menyala jika salah satu atau seluruh saklar dalam kondisi on. Sedangkan lampu akan padam jika tidak ada saklar yang on atau terdapat dua diantara tiga saklar dalam kondisi on. Jika ketiga saklar dinyatakan sebagai x 1, x 2, dan x 3 dengan kondisi saklar on = level logika ‘ 1’ serta off = level logika ‘ 0’ 187

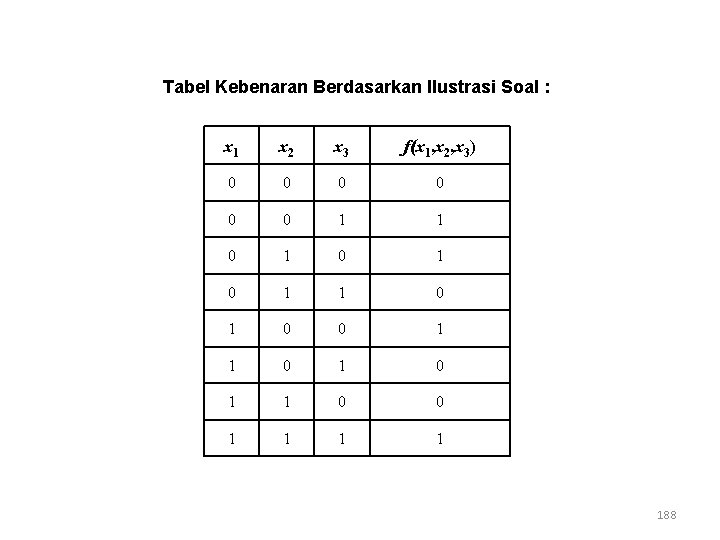

Tabel Kebenaran Berdasarkan Ilustrasi Soal : x 1 x 2 x 3 f(x 1, x 2, x 3) 0 0 0 1 1 0 1 0 1 0 0 1 1 0 0 1 1 188

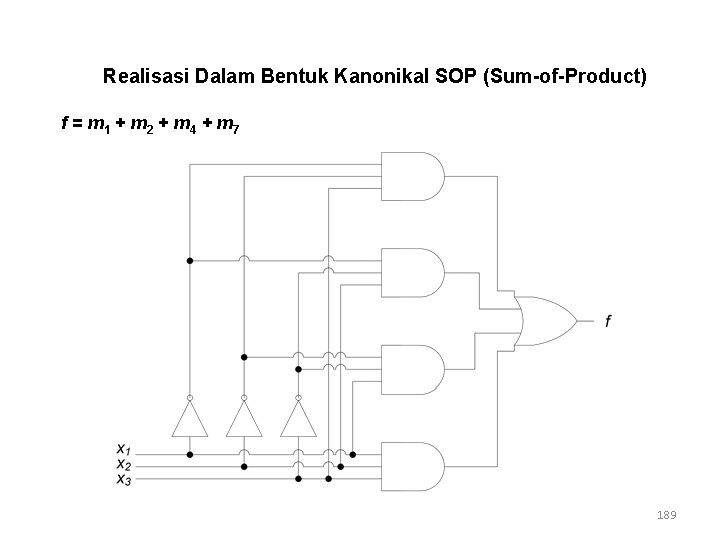

Realisasi Dalam Bentuk Kanonikal SOP (Sum-of-Product) f = m 1 + m 2 + m 4 + m 7 189

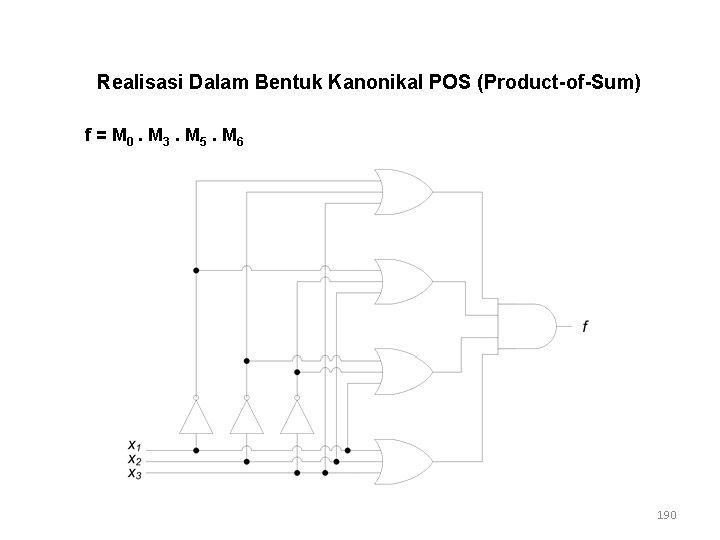

Realisasi Dalam Bentuk Kanonikal POS (Product-of-Sum) f = M 0. M 3. M 5. M 6 190

- Slides: 16