Half Adder Contd l Half Adder Module library

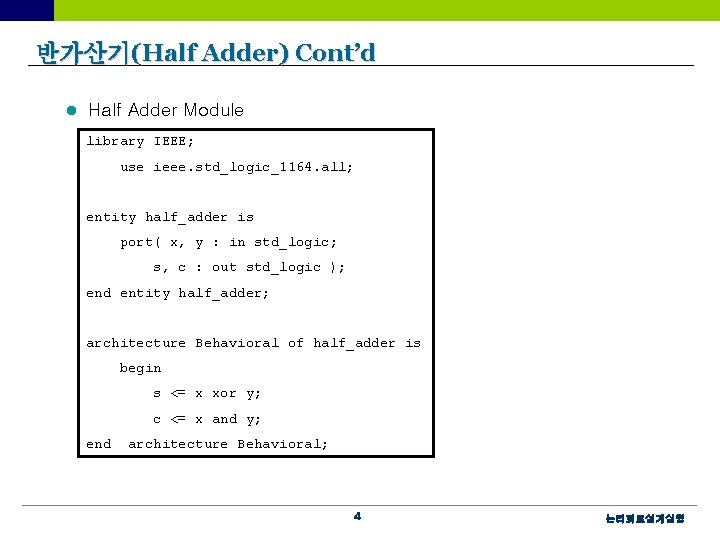

반가산기(Half Adder) Cont’d l Half Adder Module library IEEE; use ieee. std_logic_1164. all; entity half_adder is port( x, y : in std_logic; s, c : out std_logic ); end entity half_adder; architecture Behavioral of half_adder is begin s <= x xor y; c <= x and y; end architecture Behavioral; 4 논리회로설계실험

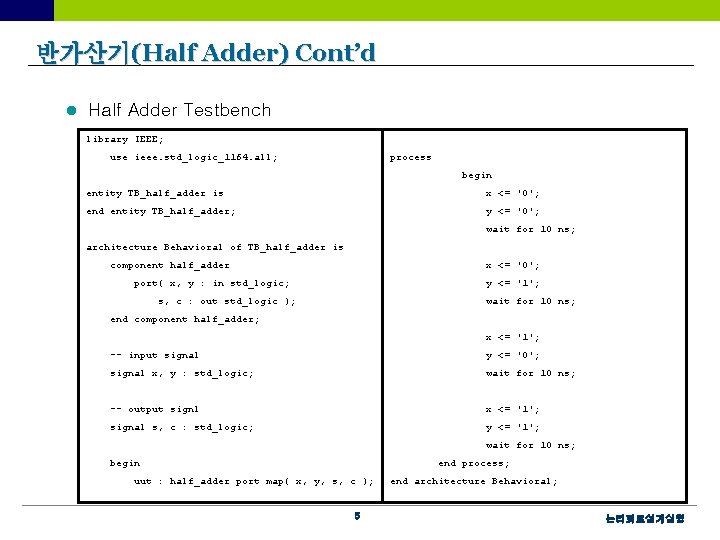

반가산기(Half Adder) Cont’d l Half Adder Testbench library IEEE; use ieee. std_logic_1164. all; process begin entity TB_half_adder is x <= '0'; end entity TB_half_adder; y <= '0'; wait for 10 ns; architecture Behavioral of TB_half_adder is component half_adder x <= '0'; port( x, y : in std_logic; y <= '1'; s, c : out std_logic ); wait for 10 ns; end component half_adder; x <= '1'; -- input signal y <= '0'; signal x, y : std_logic; wait for 10 ns; -- output signl x <= '1'; signal s, c : std_logic; y <= '1'; wait for 10 ns; begin end process; uut : half_adder port map( x, y, s, c ); 5 end architecture Behavioral; 논리회로설계실험

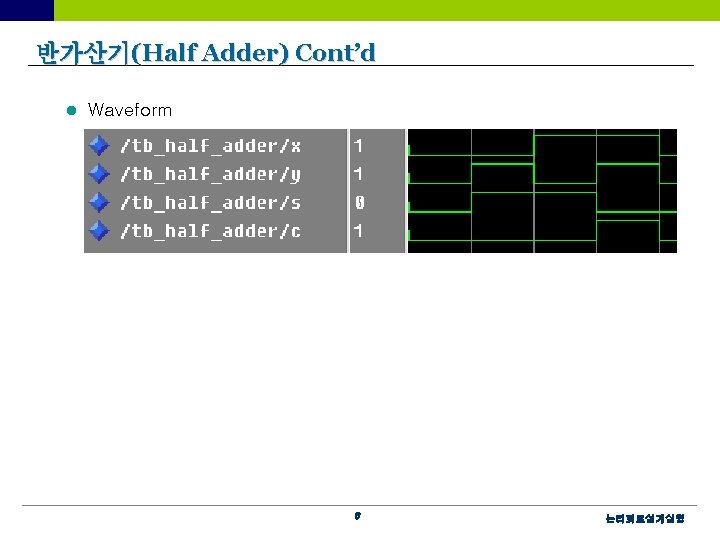

반가산기(Half Adder) Cont’d l Waveform 6 논리회로설계실험

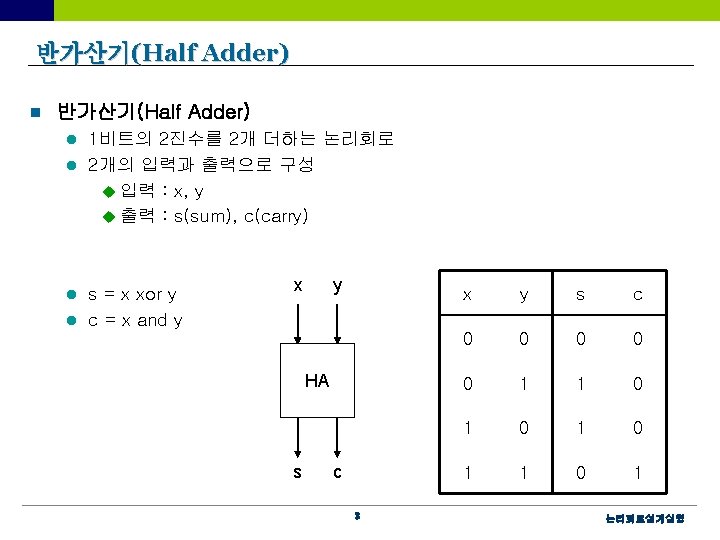

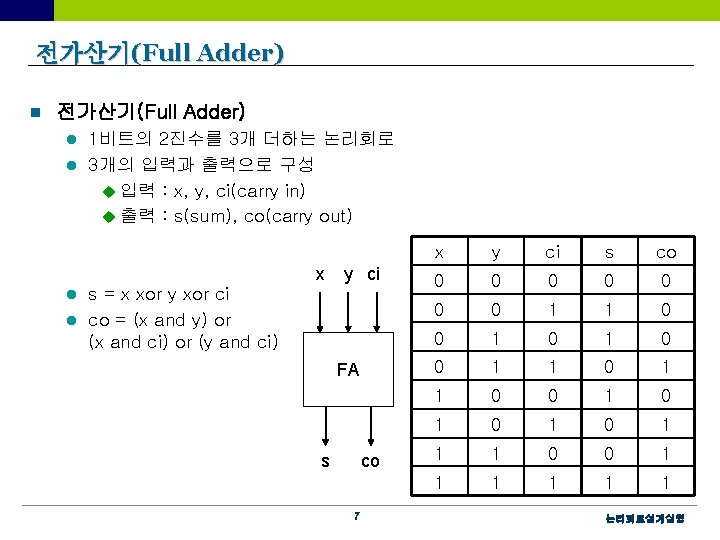

전가산기(Full Adder) n 전가산기(Full Adder) 1비트의 2진수를 3개 더하는 논리회로 l 3개의 입력과 출력으로 구성 u 입력 : x, y, ci(carry in) u 출력 : s(sum), co(carry out) l x y ci s = x xor y xor ci l co = (x and y) or (x and ci) or (y and ci) l FA s co 7 x y ci s co 0 0 0 0 1 1 0 0 1 0 1 1 1 0 0 1 1 1 논리회로설계실험

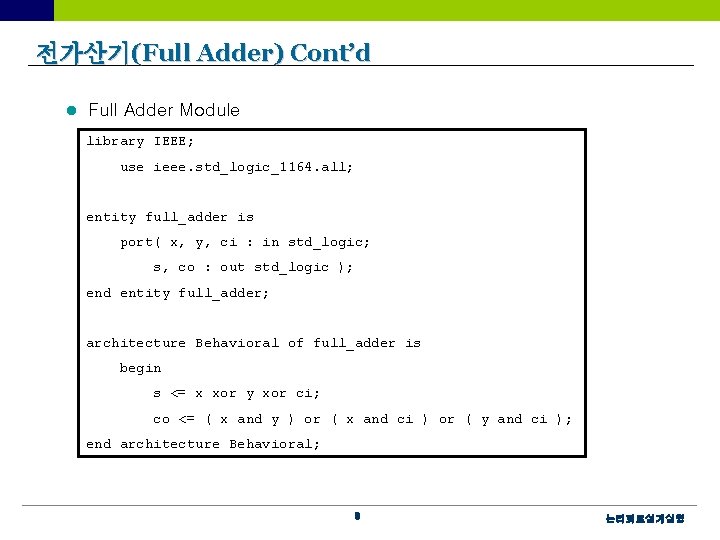

전가산기(Full Adder) Cont’d l Full Adder Module library IEEE; use ieee. std_logic_1164. all; entity full_adder is port( x, y, ci : in std_logic; s, co : out std_logic ); end entity full_adder; architecture Behavioral of full_adder is begin s <= x xor y xor ci; co <= ( x and y ) or ( x and ci ) or ( y and ci ); end architecture Behavioral; 8 논리회로설계실험

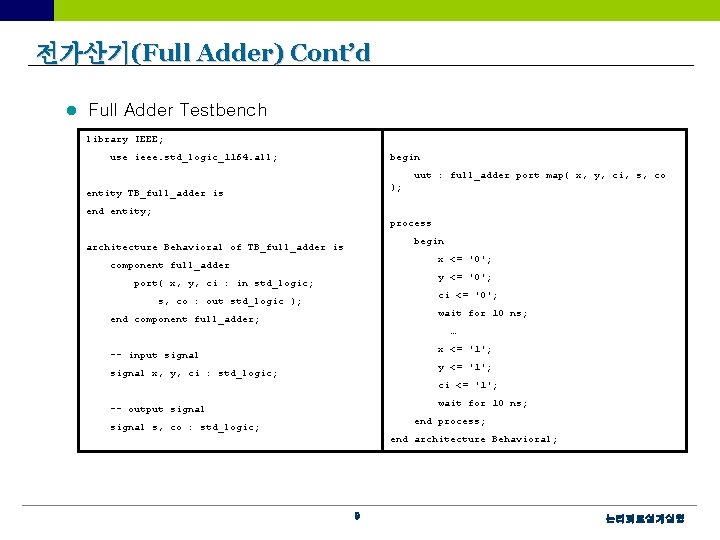

전가산기(Full Adder) Cont’d l Full Adder Testbench library IEEE; use ieee. std_logic_1164. all; begin uut : full_adder port map( x, y, ci, s, co ); entity TB_full_adder is end entity; process begin architecture Behavioral of TB_full_adder is x <= '0'; component full_adder y <= '0'; port( x, y, ci : in std_logic; ci <= '0'; s, co : out std_logic ); wait for 10 ns; end component full_adder; … x <= '1'; -- input signal y <= '1'; signal x, y, ci : std_logic; ci <= '1'; wait for 10 ns; -- output signal end process; signal s, co : std_logic; end architecture Behavioral; 9 논리회로설계실험

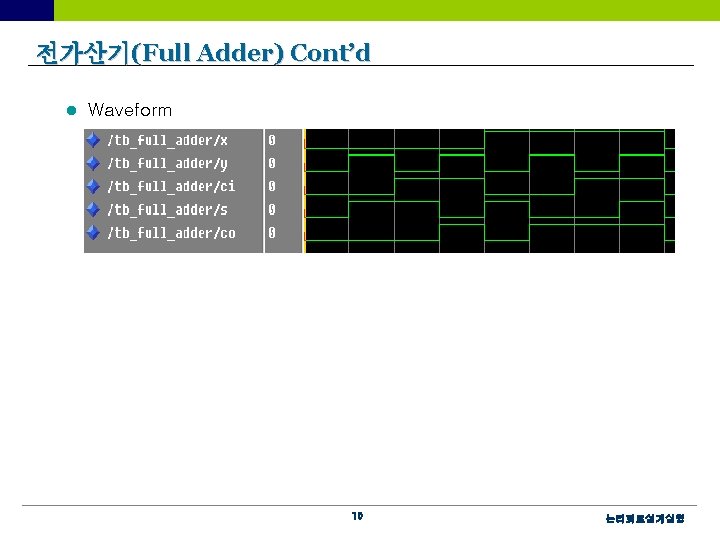

전가산기(Full Adder) Cont’d l Waveform 10 논리회로설계실험

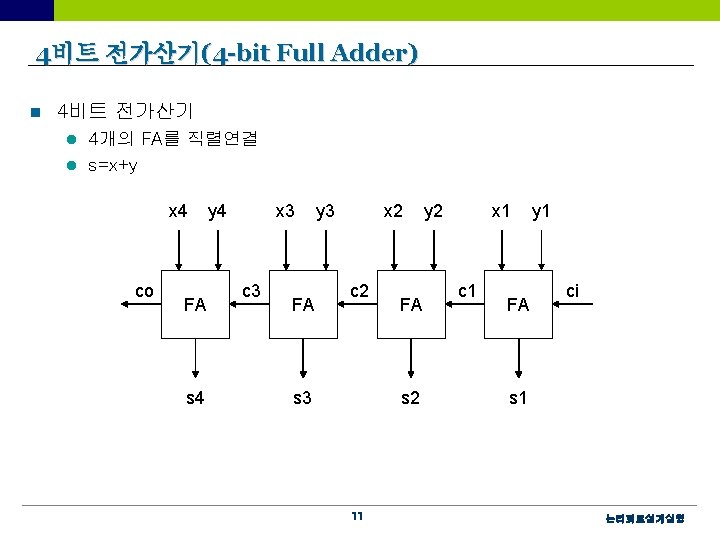

4비트 전가산기(4 -bit Full Adder) n 4비트 전가산기 4개의 FA를 직렬연결 l s=x+y l x 4 co FA s 4 y 4 x 3 c 3 FA y 3 x 2 c 2 s 3 FA s 2 11 y 2 x 1 c 1 FA y 1 ci s 1 논리회로설계실험

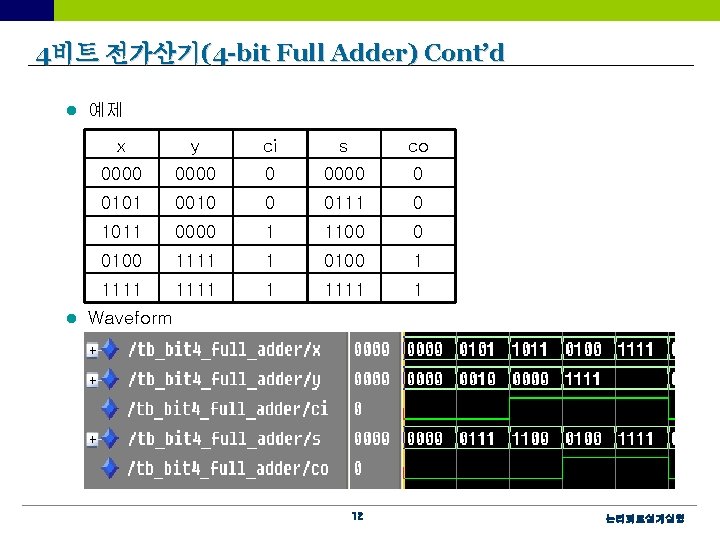

4비트 전가산기(4 -bit Full Adder) Cont’d l l 예제 x y ci s co 0000 0 0101 0010 0 0111 0 1011 0000 1 1100 0 0100 1111 1 0100 1 1111 1 Waveform 12 논리회로설계실험

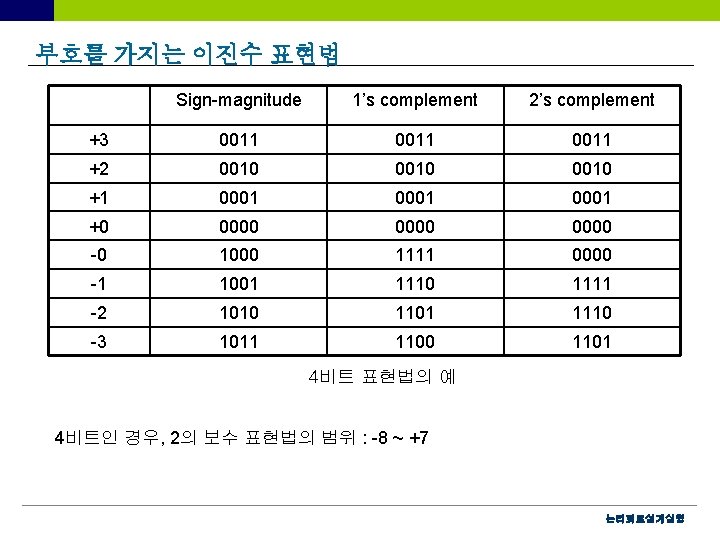

부호를 가지는 이진수 표현법 Sign-magnitude 1’s complement 2’s complement +3 0011 +2 0010 +1 0001 +0 0000 -0 1000 1111 0000 -1 1001 1110 1111 -2 1010 1101 1110 -3 1011 1100 1101 4비트 표현법의 예 4비트인 경우, 2의 보수 표현법의 범위 : -8 ~ +7 논리회로설계실험

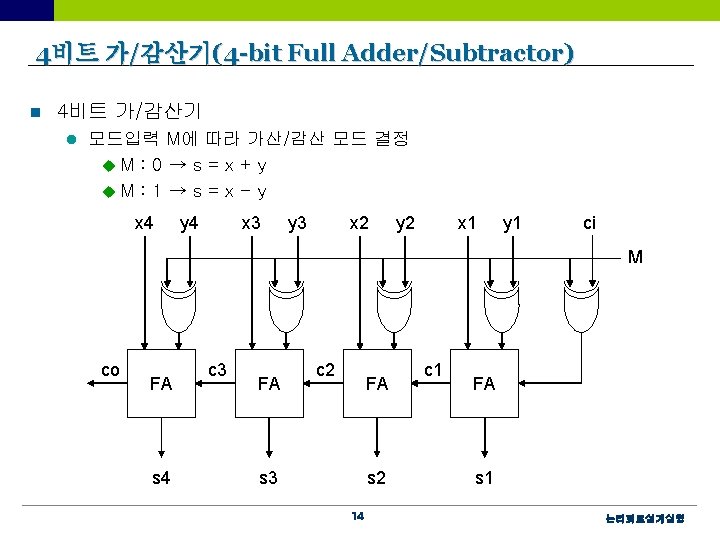

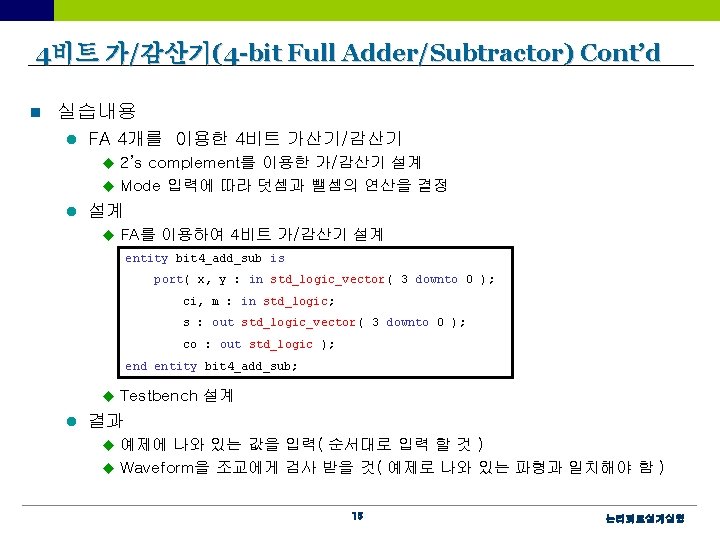

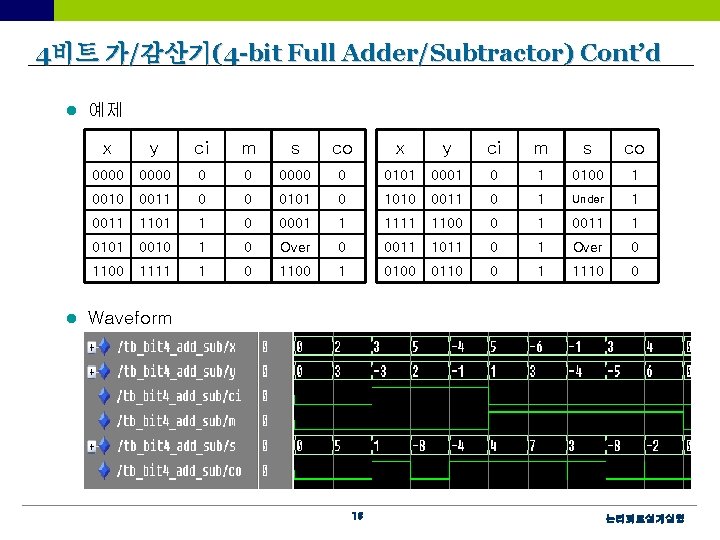

4비트 가/감산기(4 -bit Full Adder/Subtractor) Cont’d l l 예제 x y ci m s co 0000 0 0101 0001 0 1 0100 1 0010 0011 0 0 0101 0 1010 0011 0 1 Under 1 0011 1101 1 0 0001 1 1111 1100 0 1 0011 1 0101 0010 1 0 Over 0 0011 1011 0 1 Over 0 1100 1111 1 0 1100 1 0100 0110 0 1 1110 0 Waveform 16 논리회로설계실험

- Slides: 16