KIRK CH 08 FIGURE 8 1 Scanner kspace

- Slides: 20

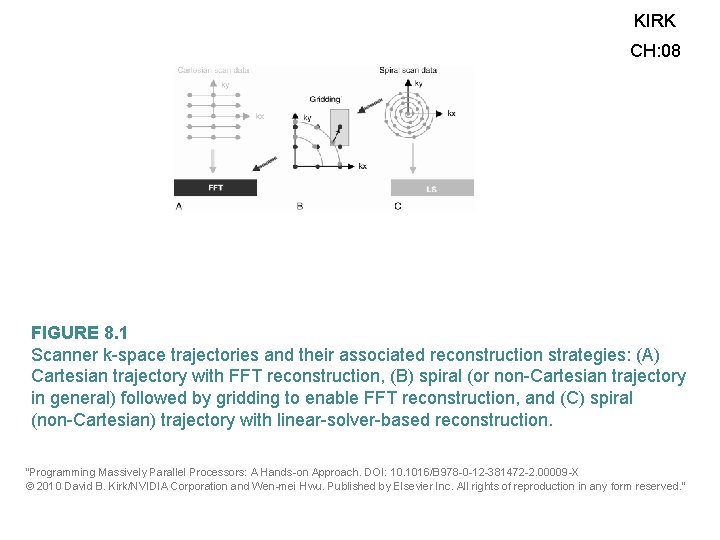

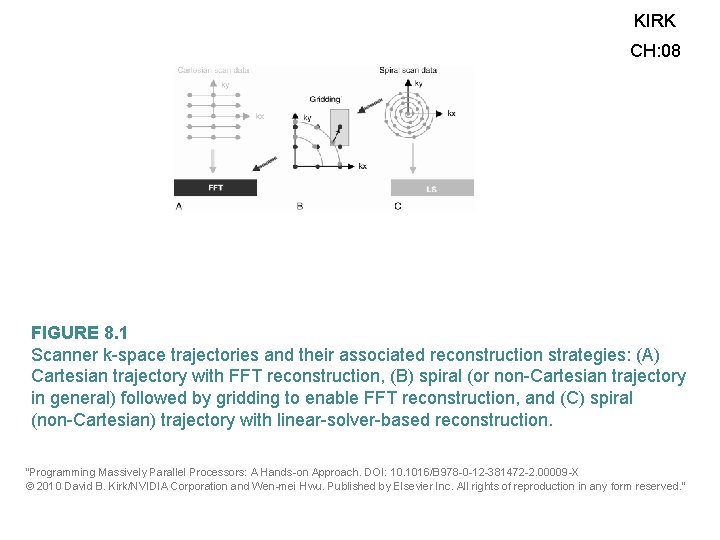

KIRK CH: 08 FIGURE 8. 1 Scanner k-space trajectories and their associated reconstruction strategies: (A) Cartesian trajectory with FFT reconstruction, (B) spiral (or non-Cartesian trajectory in general) followed by gridding to enable FFT reconstruction, and (C) spiral (non-Cartesian) trajectory with linear-solver-based reconstruction. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

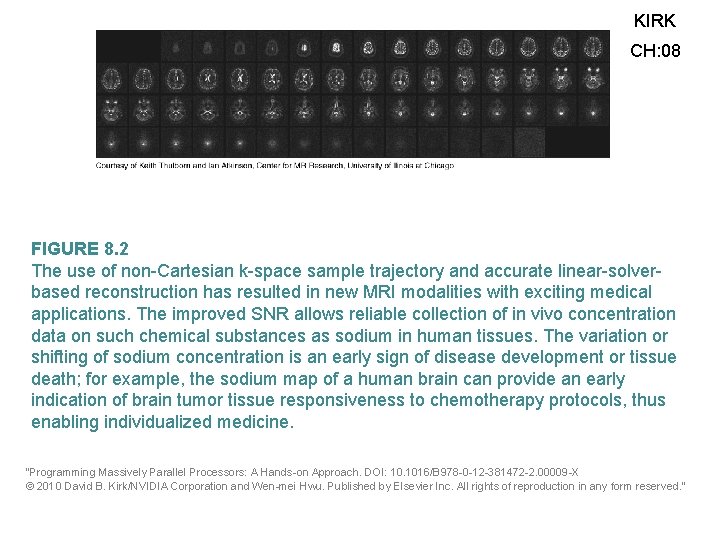

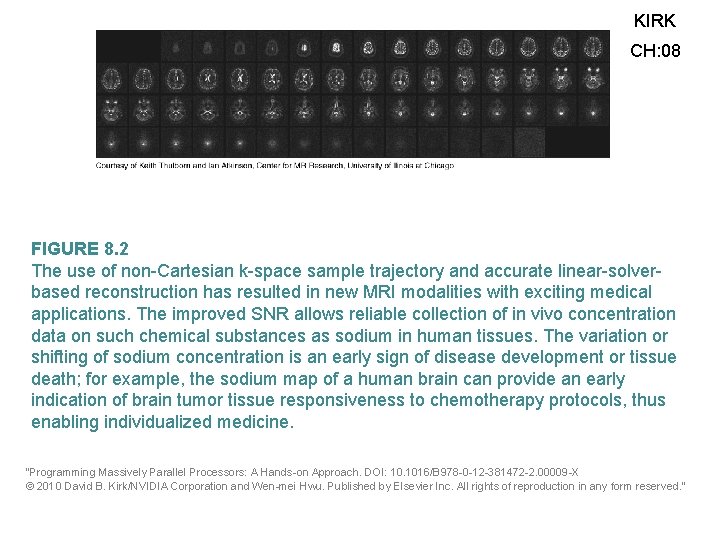

KIRK CH: 08 FIGURE 8. 2 The use of non-Cartesian k-space sample trajectory and accurate linear-solverbased reconstruction has resulted in new MRI modalities with exciting medical applications. The improved SNR allows reliable collection of in vivo concentration data on such chemical substances as sodium in human tissues. The variation or shifting of sodium concentration is an early sign of disease development or tissue death; for example, the sodium map of a human brain can provide an early indication of brain tumor tissue responsiveness to chemotherapy protocols, thus enabling individualized medicine. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

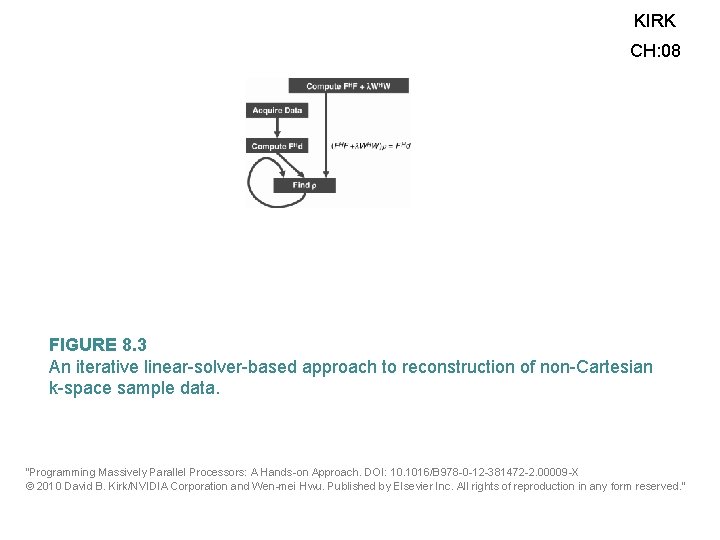

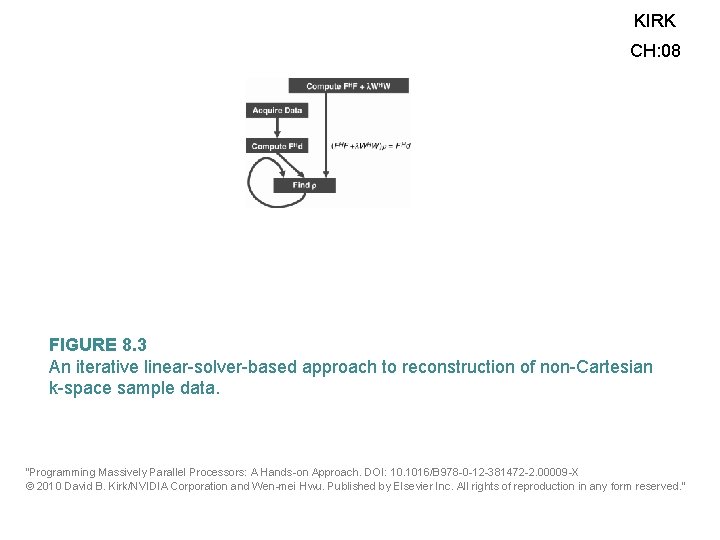

KIRK CH: 08 FIGURE 8. 3 An iterative linear-solver-based approach to reconstruction of non-Cartesian k-space sample data. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

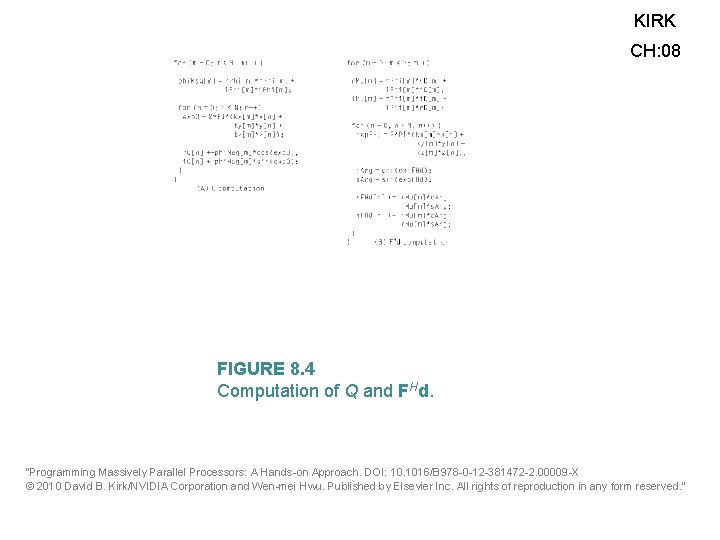

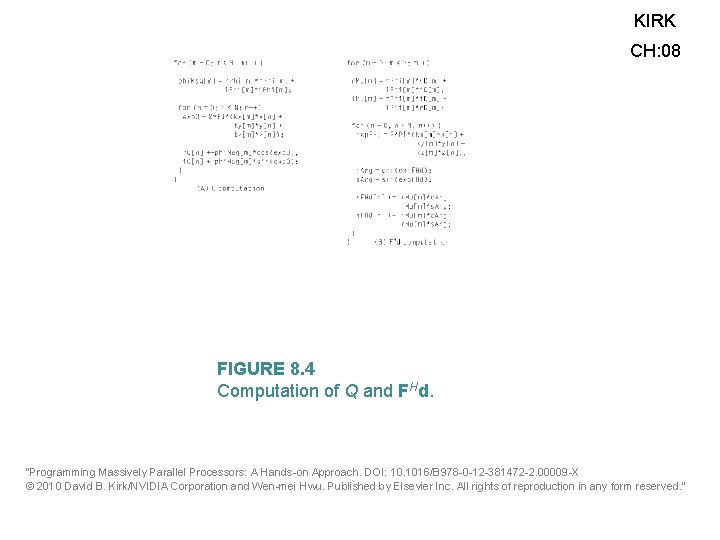

KIRK CH: 08 FIGURE 8. 4 Computation of Q and FHd. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

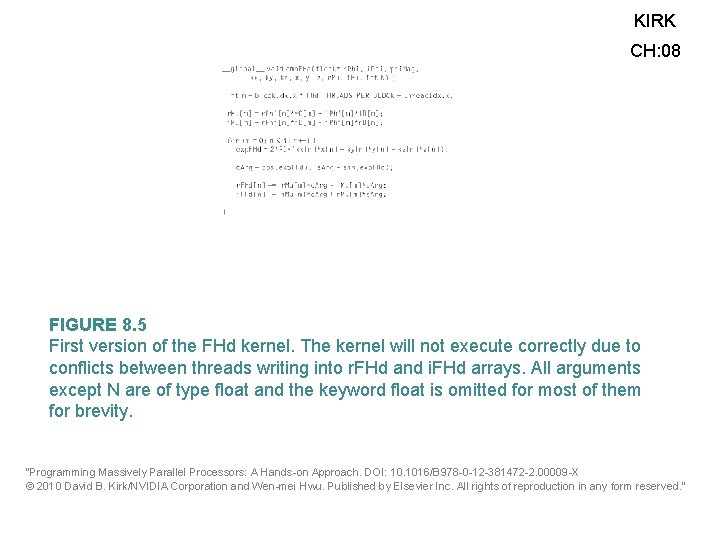

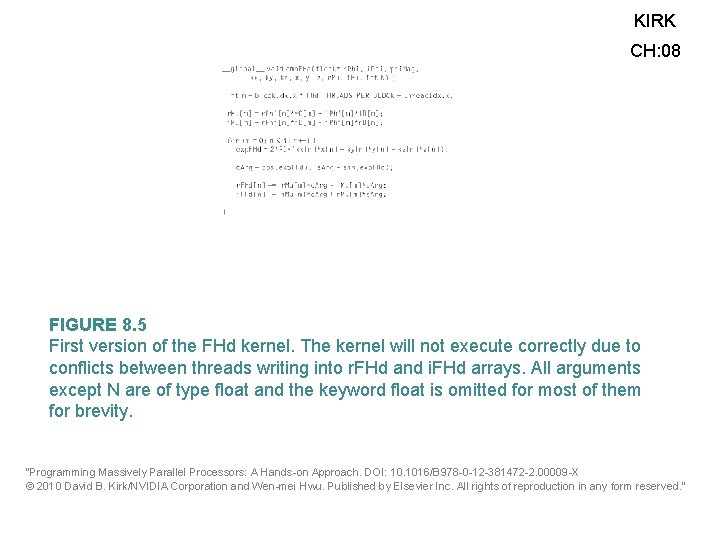

KIRK CH: 08 FIGURE 8. 5 First version of the FHd kernel. The kernel will not execute correctly due to conflicts between threads writing into r. FHd and i. FHd arrays. All arguments except N are of type float and the keyword float is omitted for most of them for brevity. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

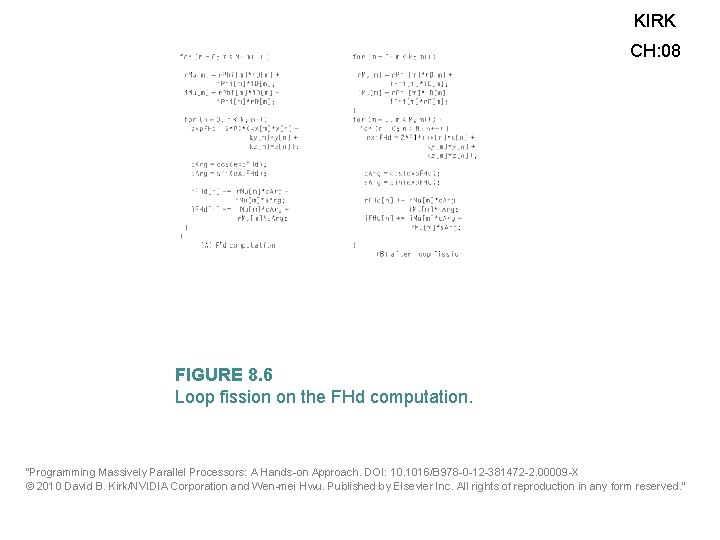

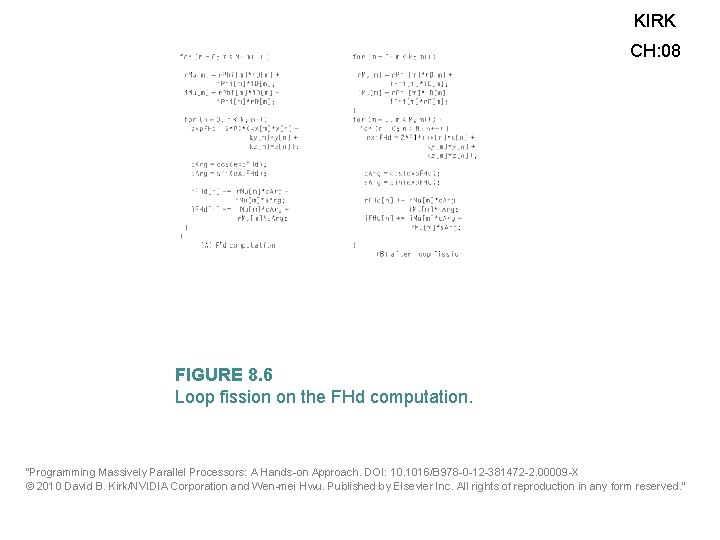

KIRK CH: 08 FIGURE 8. 6 Loop fission on the FHd computation. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

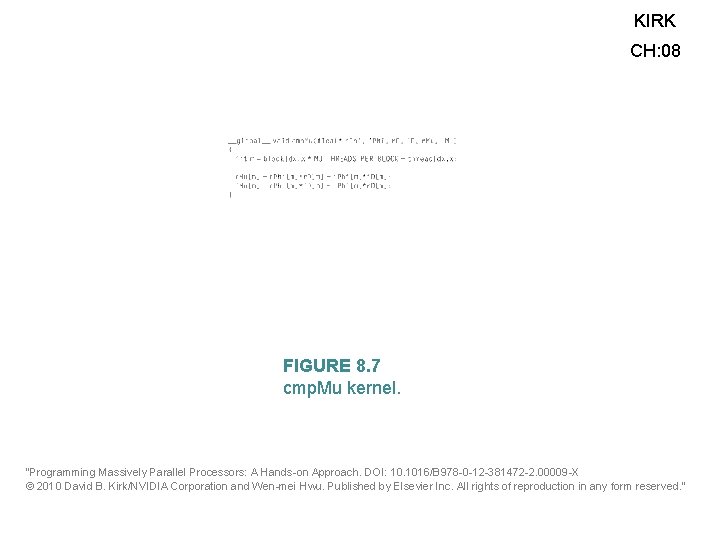

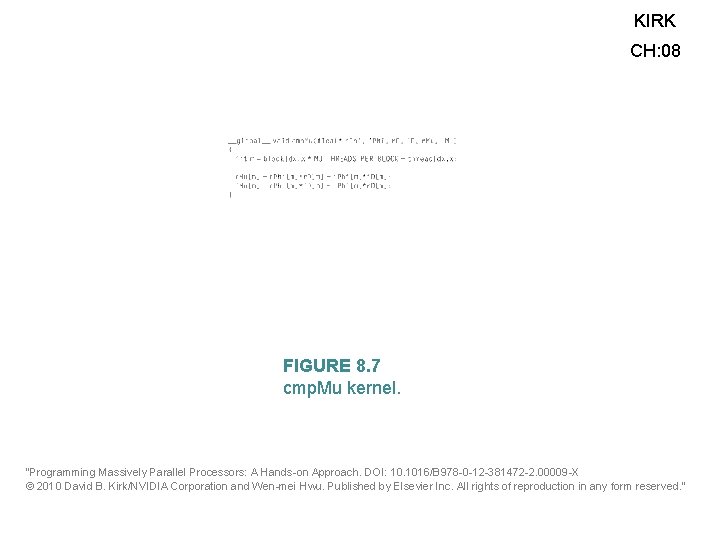

KIRK CH: 08 FIGURE 8. 7 cmp. Mu kernel. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

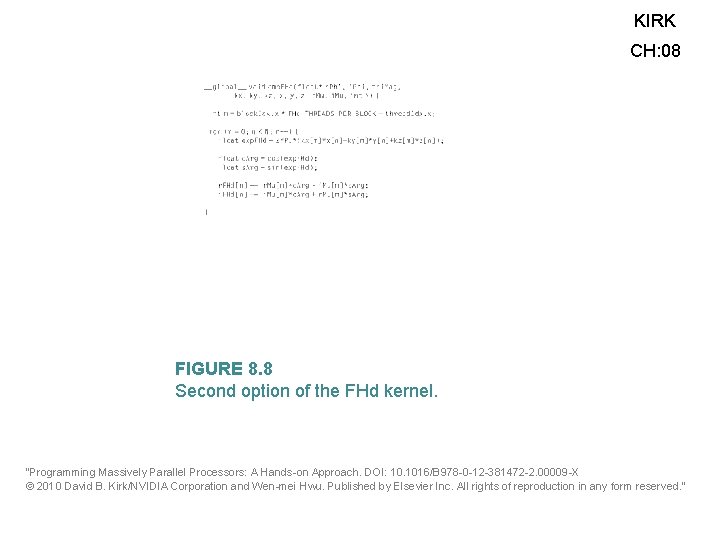

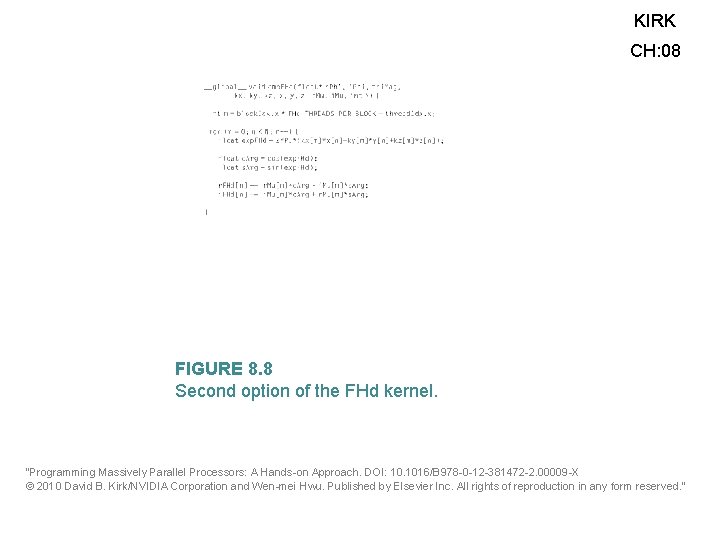

KIRK CH: 08 FIGURE 8. 8 Second option of the FHd kernel. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

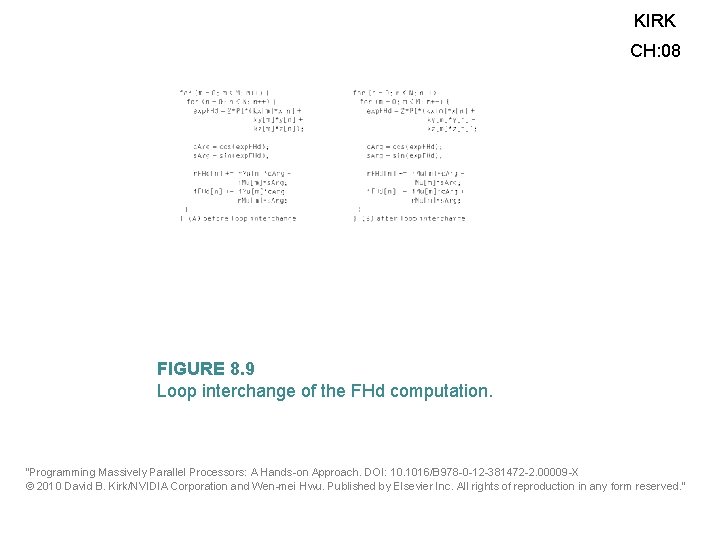

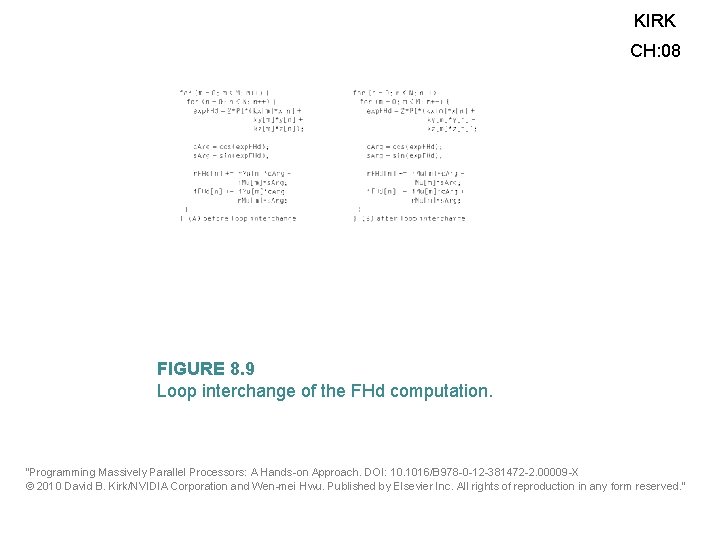

KIRK CH: 08 FIGURE 8. 9 Loop interchange of the FHd computation. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

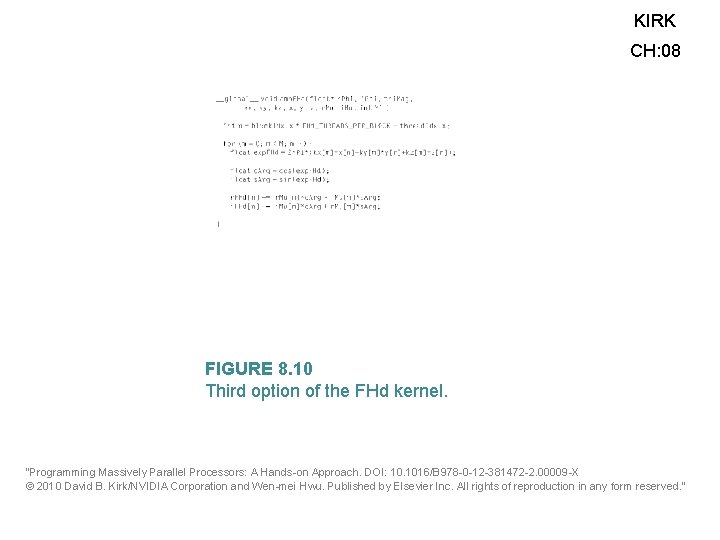

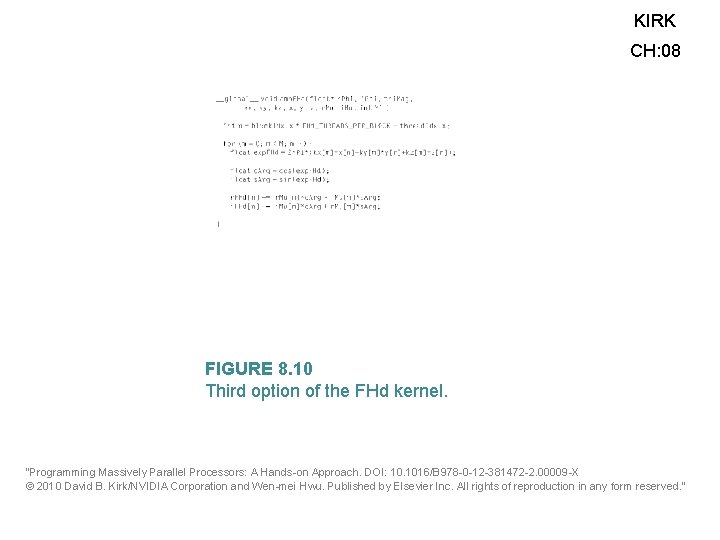

KIRK CH: 08 FIGURE 8. 10 Third option of the FHd kernel. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

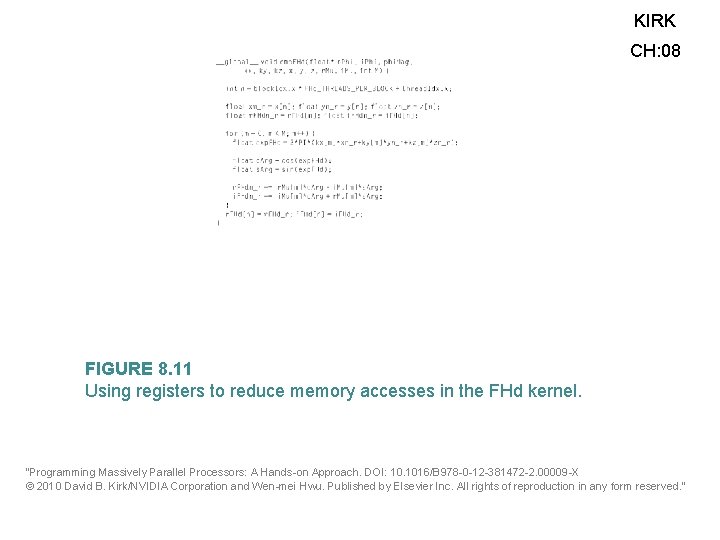

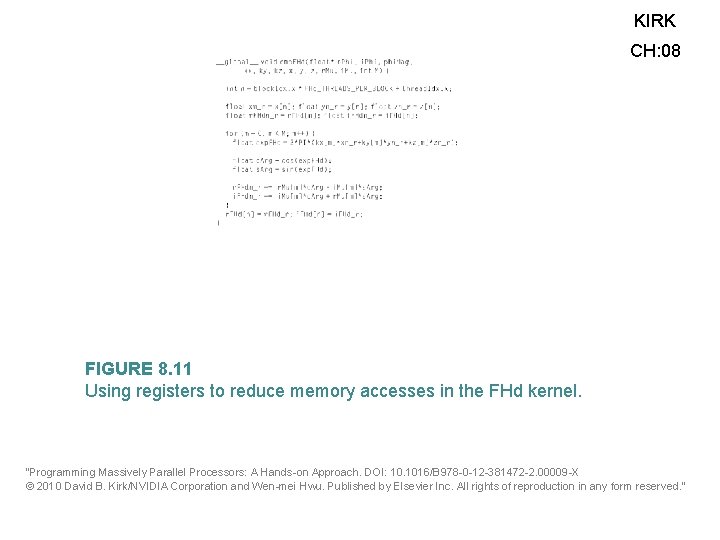

KIRK CH: 08 FIGURE 8. 11 Using registers to reduce memory accesses in the FHd kernel. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

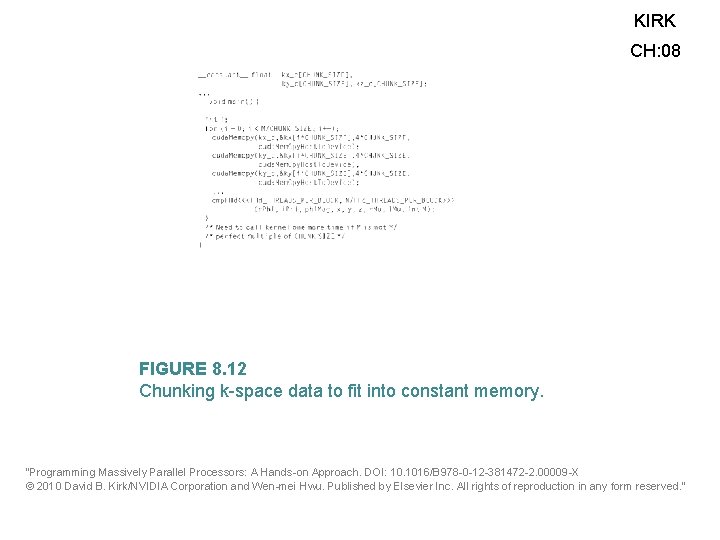

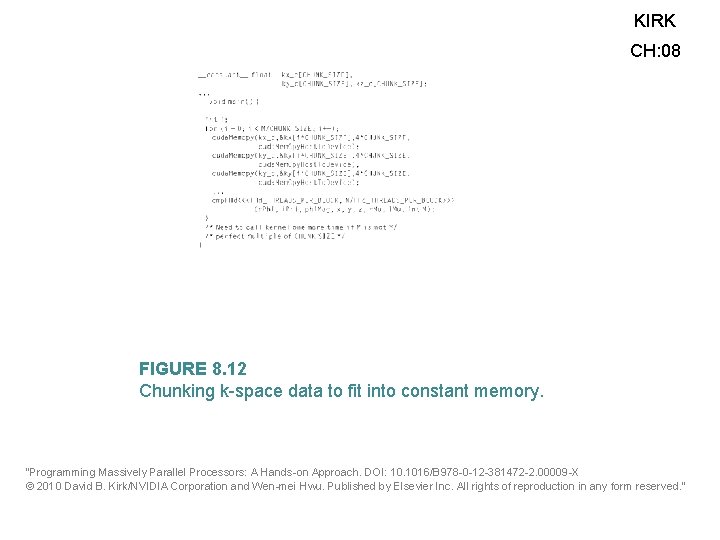

KIRK CH: 08 FIGURE 8. 12 Chunking k-space data to fit into constant memory. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

KIRK CH: 08 FIGURE 8. 13 FHd kernel revised to use constant memory. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

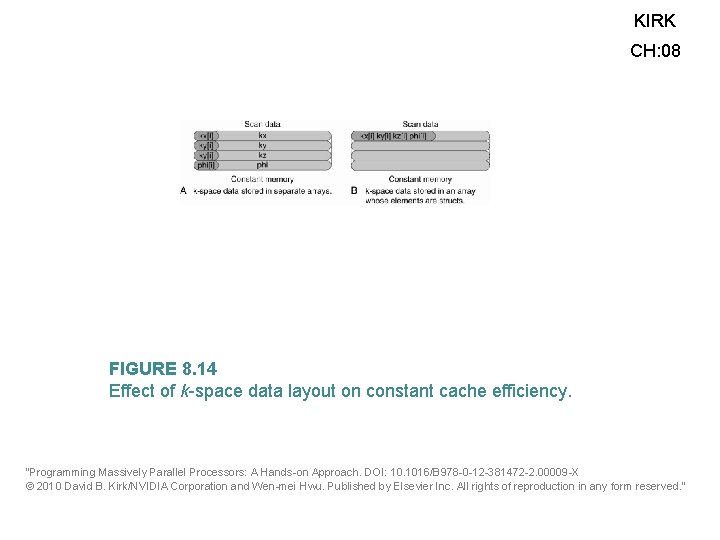

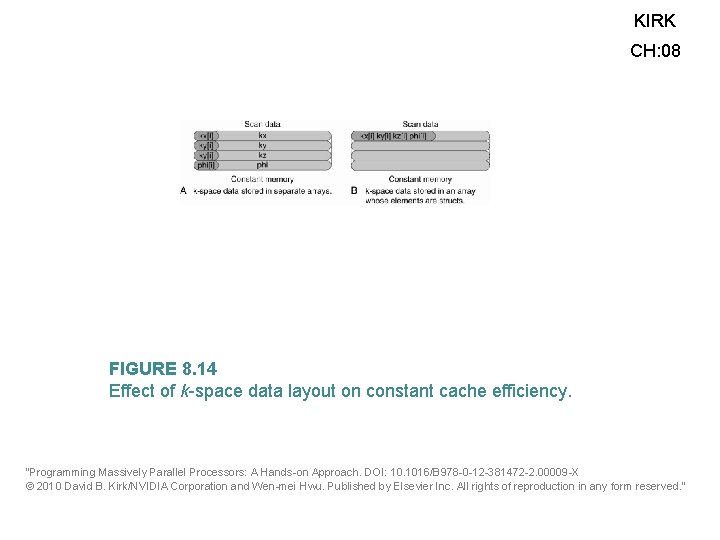

KIRK CH: 08 FIGURE 8. 14 Effect of k-space data layout on constant cache efficiency. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

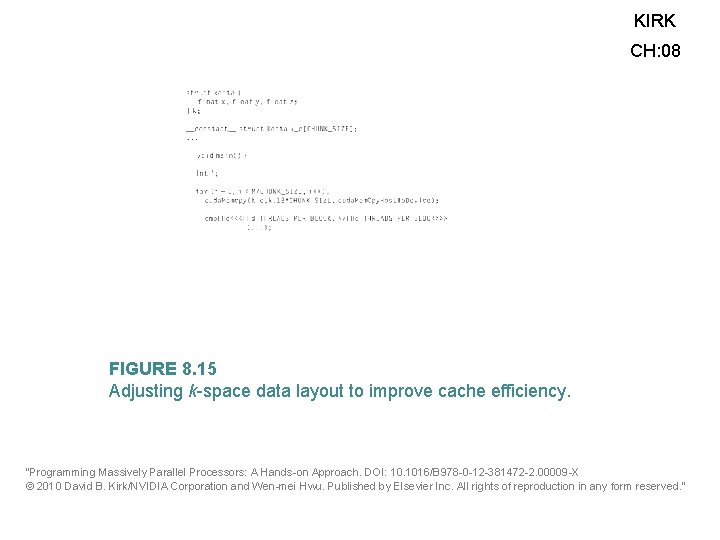

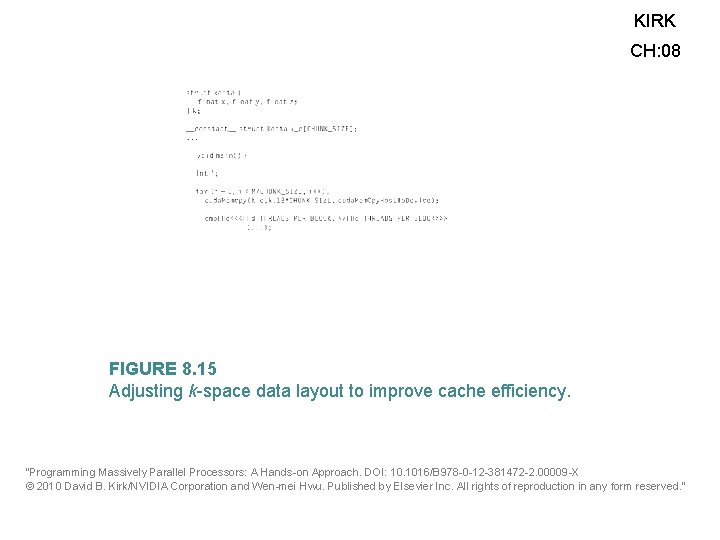

KIRK CH: 08 FIGURE 8. 15 Adjusting k-space data layout to improve cache efficiency. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

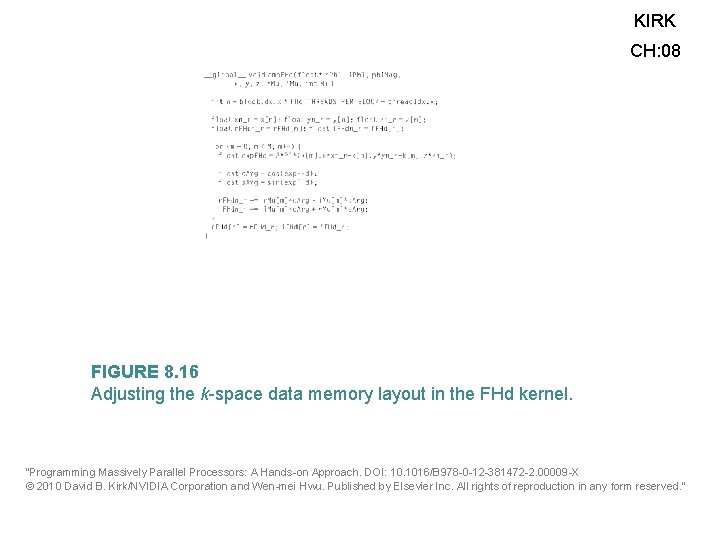

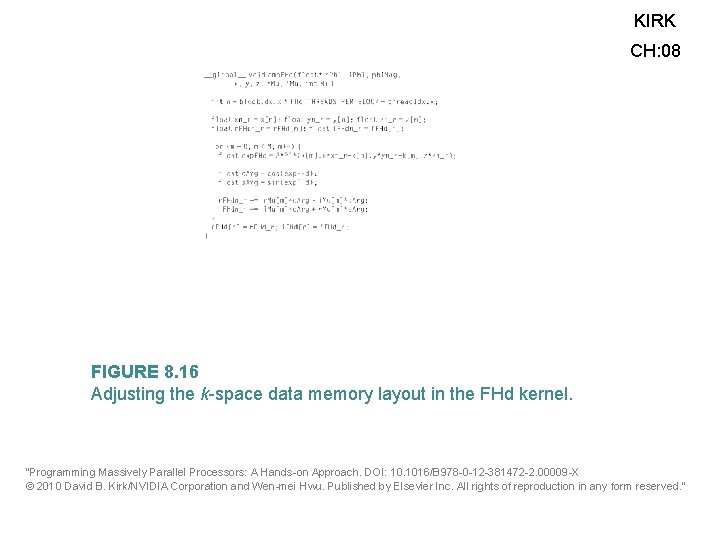

KIRK CH: 08 FIGURE 8. 16 Adjusting the k-space data memory layout in the FHd kernel. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

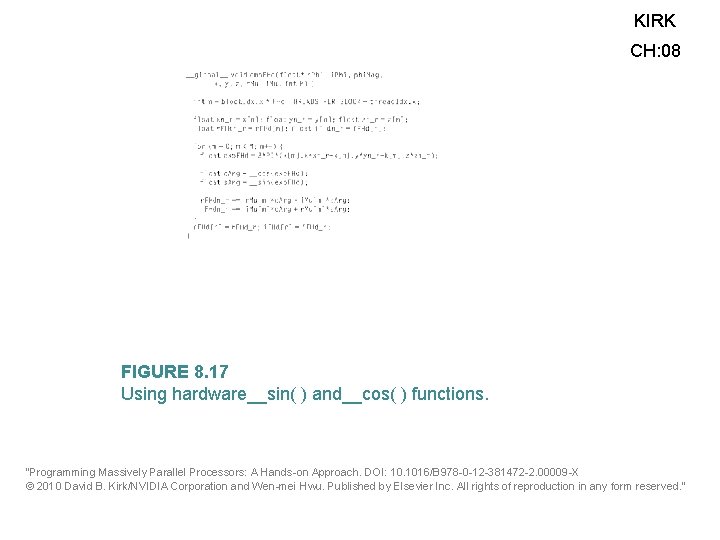

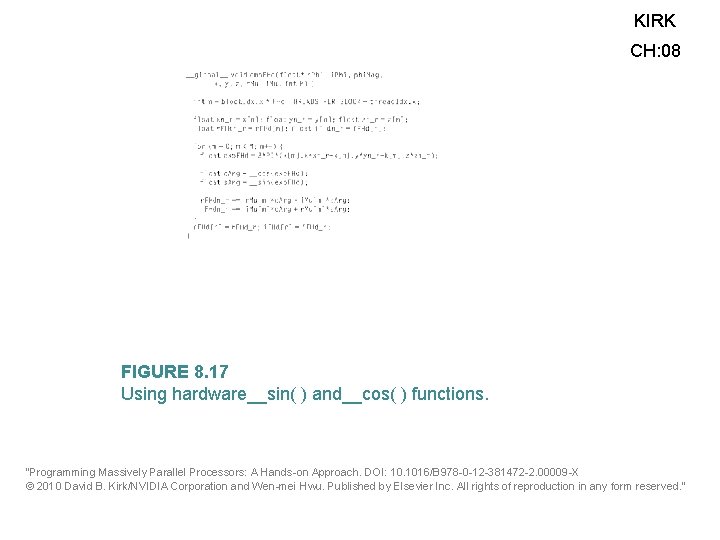

KIRK CH: 08 FIGURE 8. 17 Using hardware__sin( ) and__cos( ) functions. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

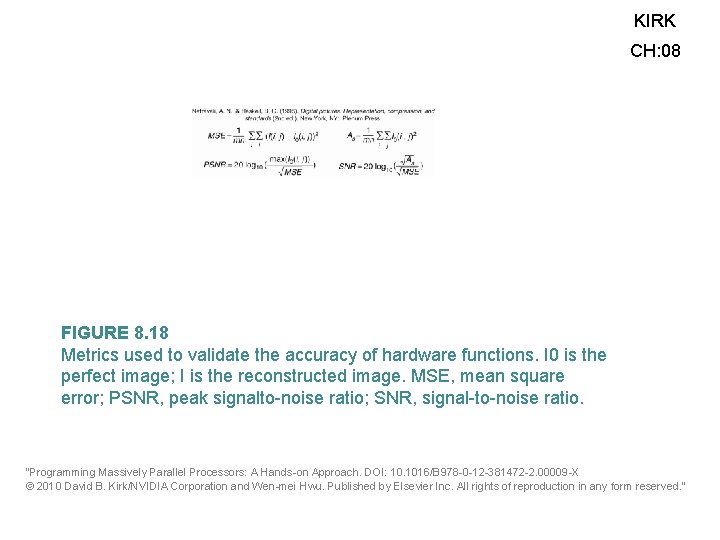

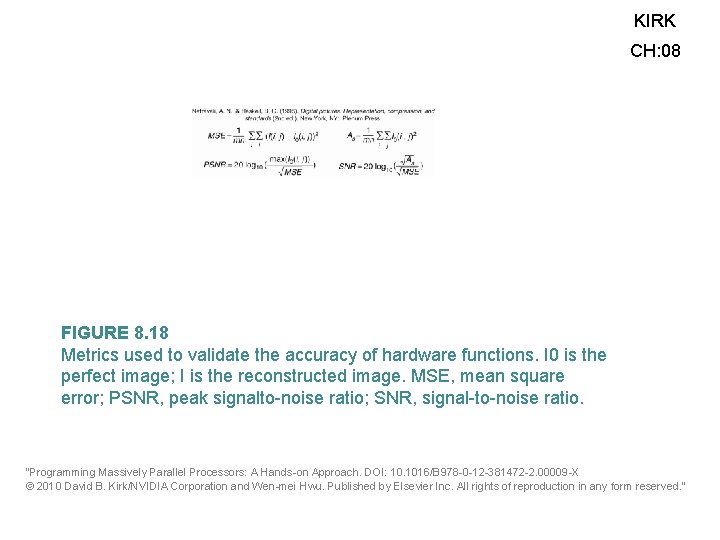

KIRK CH: 08 FIGURE 8. 18 Metrics used to validate the accuracy of hardware functions. I 0 is the perfect image; I is the reconstructed image. MSE, mean square error; PSNR, peak signalto-noise ratio; SNR, signal-to-noise ratio. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

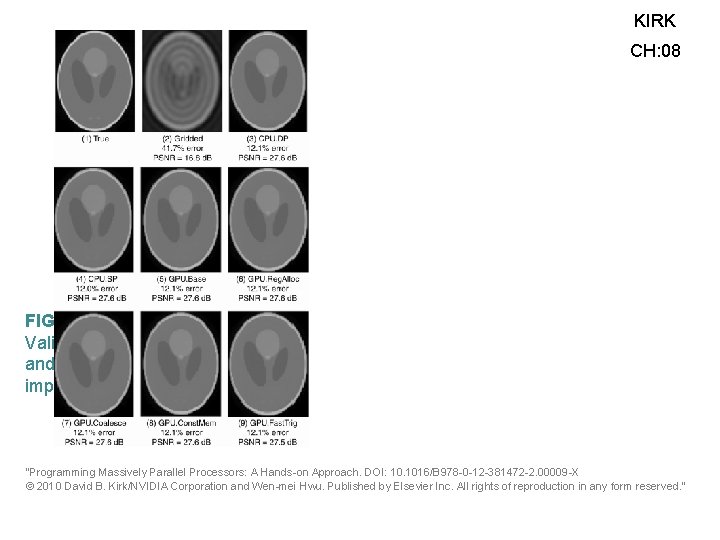

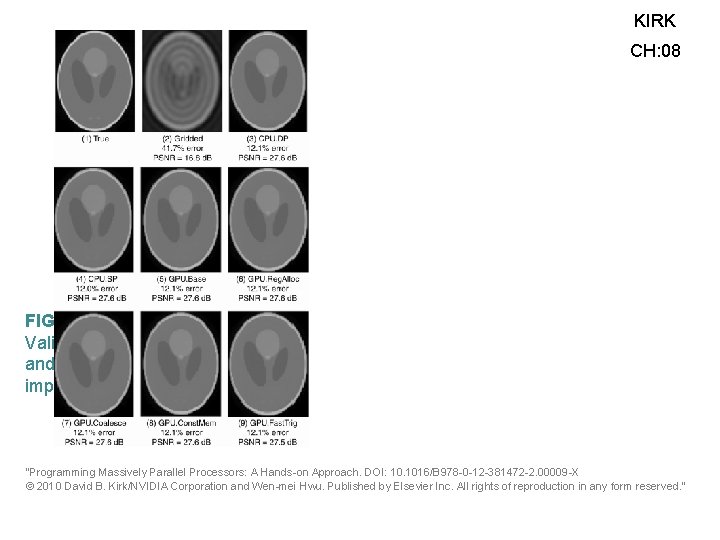

KIRK CH: 08 FIGURE 8. 19 Validation of floating-point precision and accuracy of the different FHd implementations. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”

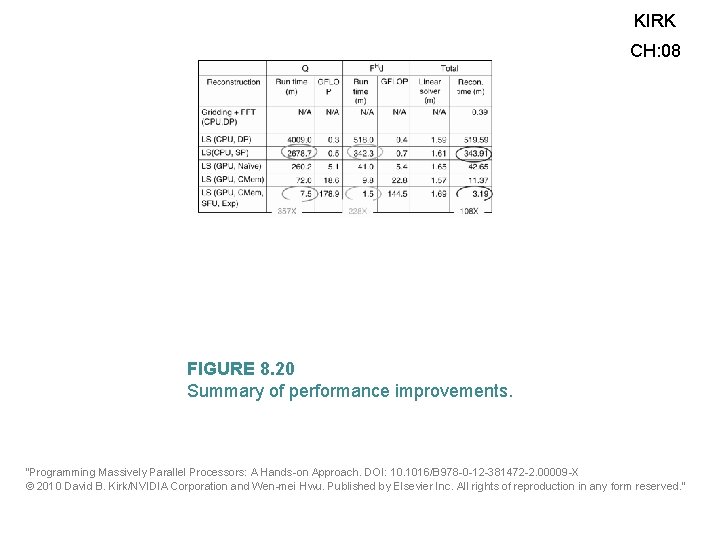

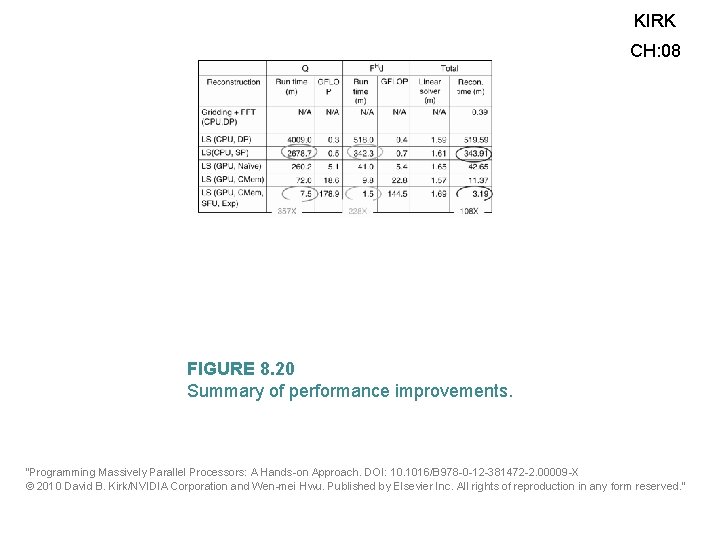

KIRK CH: 08 FIGURE 8. 20 Summary of performance improvements. “Programming Massively Parallel Processors: A Hands-on Approach. DOI: 10. 1016/B 978 -0 -12 -381472 -2. 00009 -X © 2010 David B. Kirk/NVIDIA Corporation and Wen-mei Hwu. Published by Elsevier Inc. All rights of reproduction in any form reserved. ”