INTERRUPCIONES Introduccin Interrupciones Una interrupcin es un evento

- Slides: 11

INTERRUPCIONES Introducción

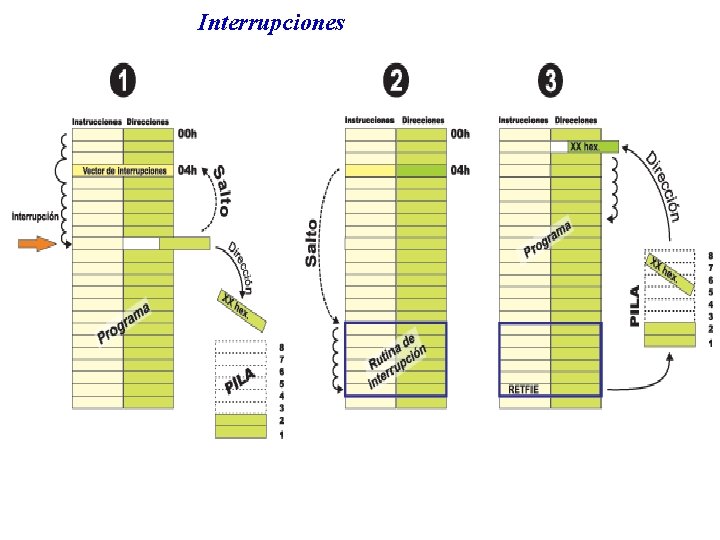

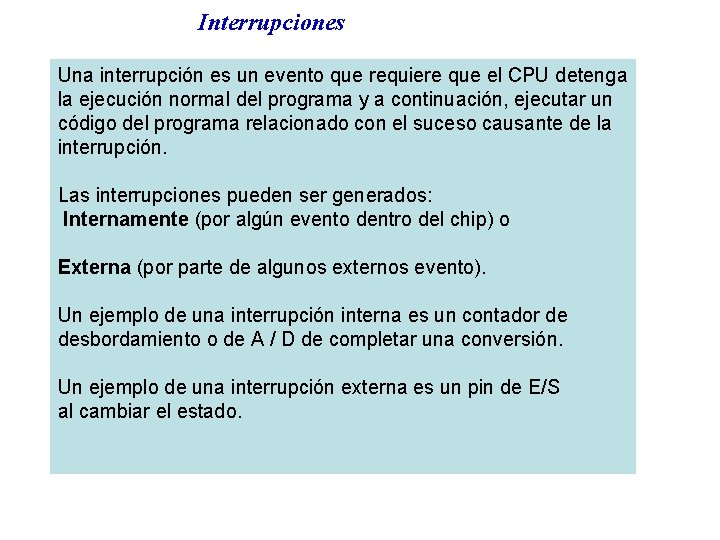

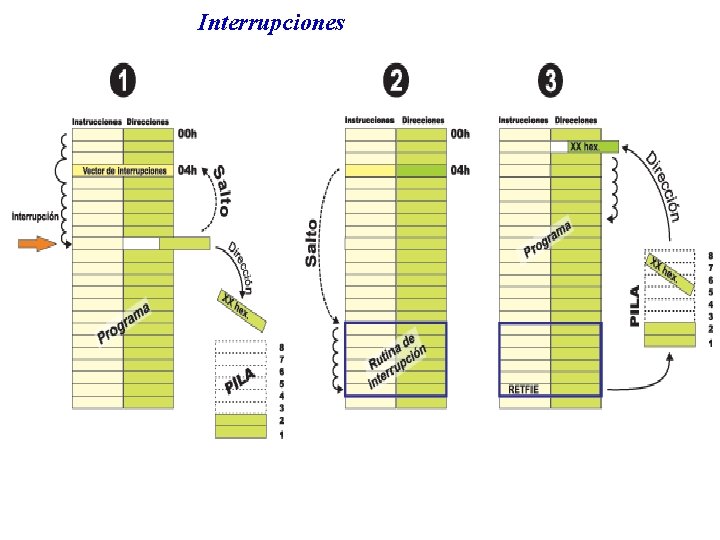

Interrupciones Una interrupción es un evento que requiere que el CPU detenga la ejecución normal del programa y a continuación, ejecutar un código del programa relacionado con el suceso causante de la interrupción. Las interrupciones pueden ser generados: Internamente (por algún evento dentro del chip) o Externa (por parte de algunos externos evento). Un ejemplo de una interrupción interna es un contador de desbordamiento o de A / D de completar una conversión. Un ejemplo de una interrupción externa es un pin de E/S al cambiar el estado.

Interrupciones

PIC 18 F 4550 El microcontrolador PIC 18 F 4550 tiene dos fuente principales de interrupción: del Núcleo y de los periféricos. La principales fuentes de interrupción del núcleo son: • Exteriores disparado por el interrupción en los pines : INT 0, INT 1 e INT 2. • Pines PORTB interrumpe cuando cambia el estado de uno de los pines RB 4 a RB 7. • Temporizador 0. Alguna de las fuentes de interrupción periférica son: • Conversión A / D completa. • USART interrupción de recepción. • USART interrupción de transmisión. • Detección de bajo voltaje. • Otros…

PIC 18 F 4550 Las interrupciones en la familia PIC 18 F se puede dividir en dos grupos: de alta prioridad y baja prioridad. Si en la aplicación no es necesario establecer prioridades para las interrupciones, el usuario puede optar por desactivar el esquema de prioridades para que todas las interrupciones se encuentran en la misma nivel de prioridad. El PIC 18 F 4550 utiliza varios registros para el control de la interrupción. Estos son: • RCON • INTCON 2 • INTCON 3 • PIR 1, PIR 2 • PIE 1, PIE 2 • IPR 1, IPR 2

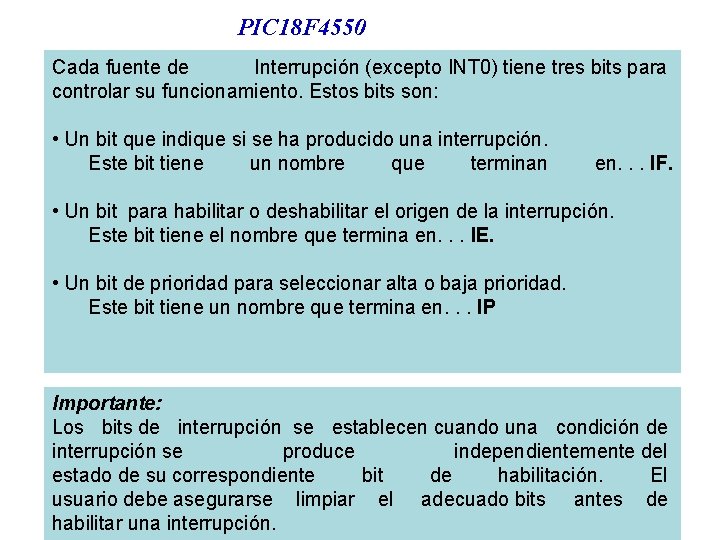

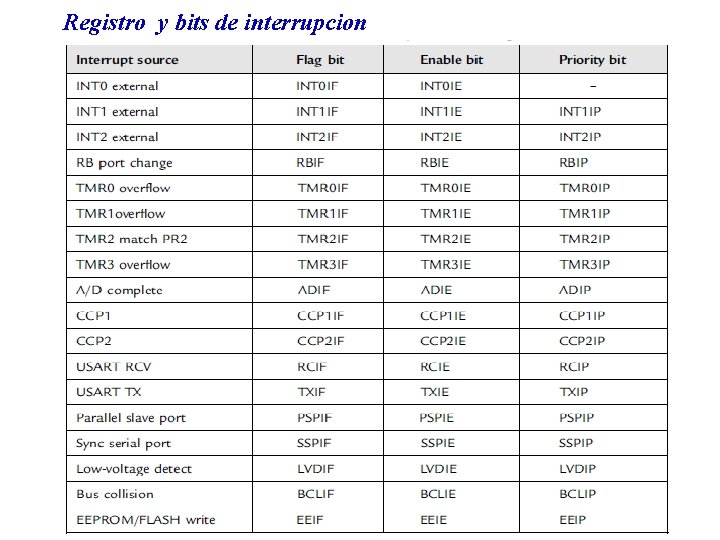

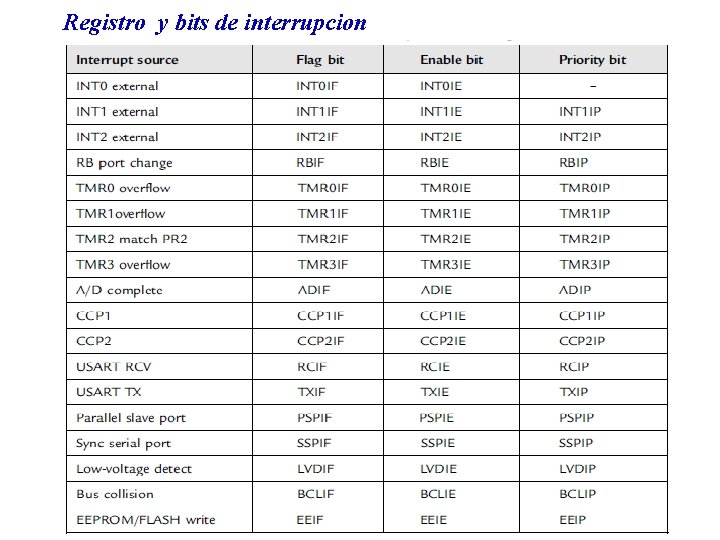

PIC 18 F 4550 Cada fuente de Interrupción (excepto INT 0) tiene tres bits para controlar su funcionamiento. Estos bits son: • Un bit que indique si se ha producido una interrupción. Este bit tiene un nombre que terminan en. . . IF. • Un bit para habilitar o deshabilitar el origen de la interrupción. Este bit tiene el nombre que termina en. . . IE. • Un bit de prioridad para seleccionar alta o baja prioridad. Este bit tiene un nombre que termina en. . . IP Importante: Los bits de interrupción se establecen cuando una condición de interrupción se produce independientemente del estado de su correspondiente bit de habilitación. El usuario debe asegurarse limpiar el adecuado bits antes de habilitar una interrupción.

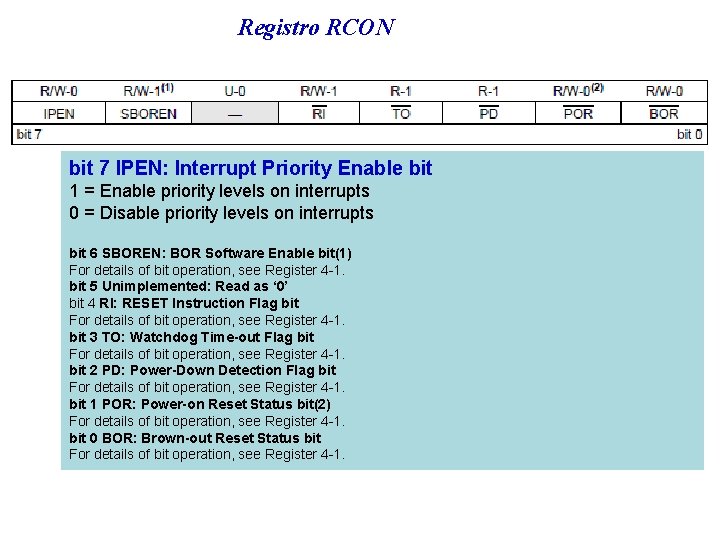

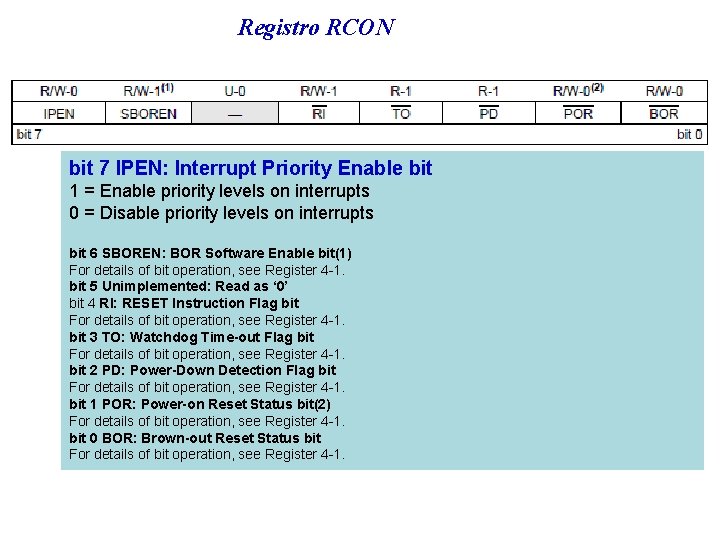

Registro RCON bit 7 IPEN: Interrupt Priority Enable bit 1 = Enable priority levels on interrupts 0 = Disable priority levels on interrupts bit 6 SBOREN: BOR Software Enable bit(1) For details of bit operation, see Register 4 -1. bit 5 Unimplemented: Read as ‘ 0’ bit 4 RI: RESET Instruction Flag bit For details of bit operation, see Register 4 -1. bit 3 TO: Watchdog Time-out Flag bit For details of bit operation, see Register 4 -1. bit 2 PD: Power-Down Detection Flag bit For details of bit operation, see Register 4 -1. bit 1 POR: Power-on Reset Status bit(2) For details of bit operation, see Register 4 -1. bit 0 BOR: Brown-out Reset Status bit For details of bit operation, see Register 4 -1.

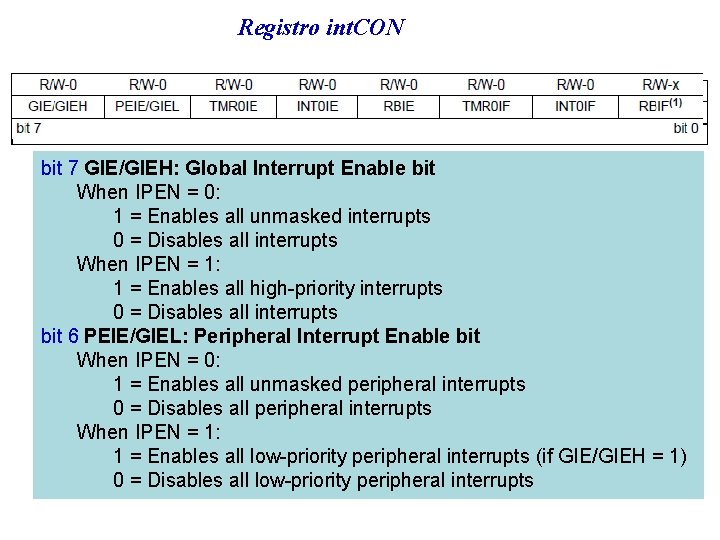

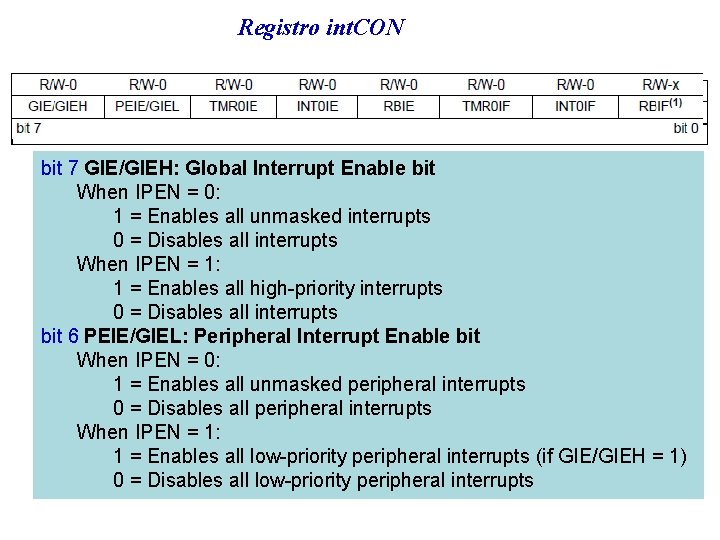

Registro int. CON bit 7 GIE/GIEH: Global Interrupt Enable bit When IPEN = 0: 1 = Enables all unmasked interrupts 0 = Disables all interrupts When IPEN = 1: 1 = Enables all high-priority interrupts 0 = Disables all interrupts bit 6 PEIE/GIEL: Peripheral Interrupt Enable bit When IPEN = 0: 1 = Enables all unmasked peripheral interrupts 0 = Disables all peripheral interrupts When IPEN = 1: 1 = Enables all low-priority peripheral interrupts (if GIE/GIEH = 1) 0 = Disables all low-priority peripheral interrupts

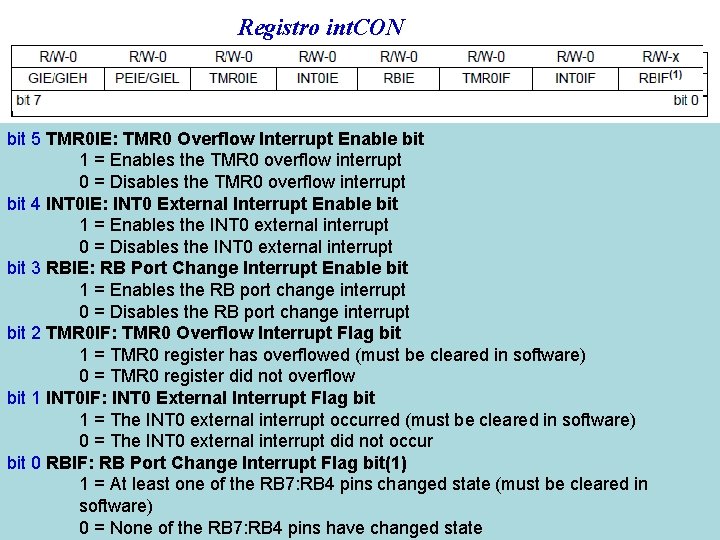

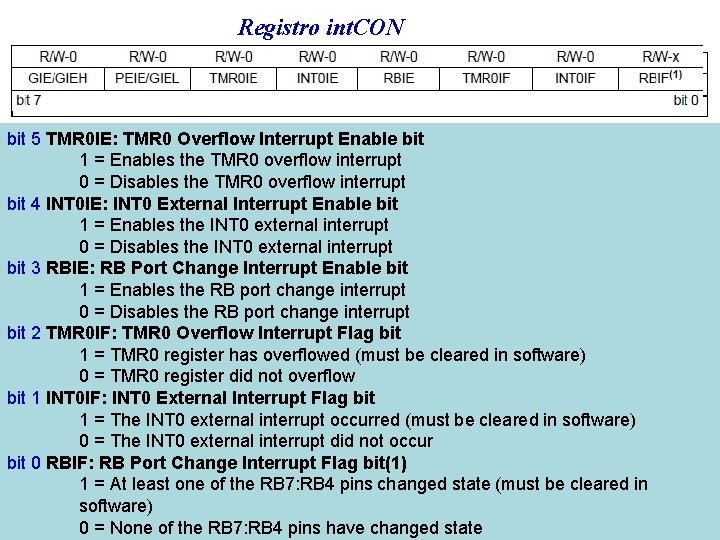

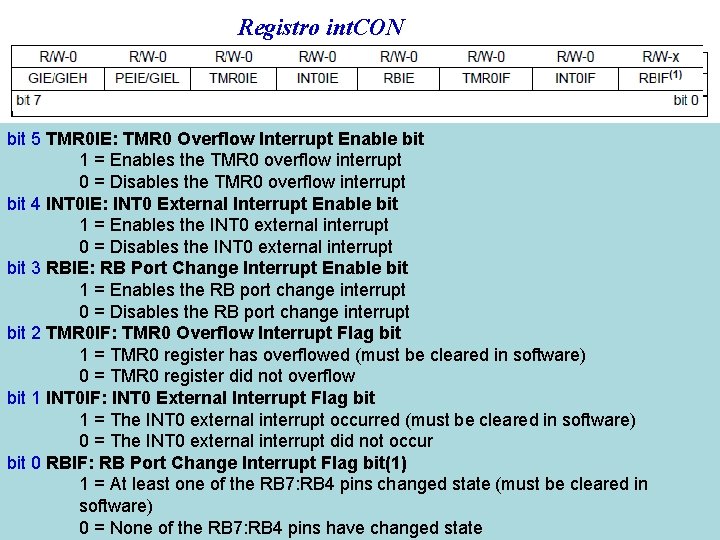

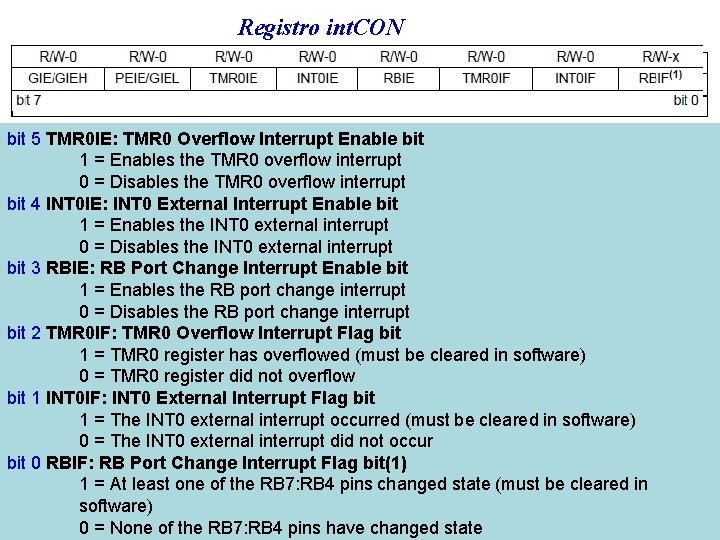

Registro int. CON bit 5 TMR 0 IE: TMR 0 Overflow Interrupt Enable bit 1 = Enables the TMR 0 overflow interrupt 0 = Disables the TMR 0 overflow interrupt bit 4 INT 0 IE: INT 0 External Interrupt Enable bit 1 = Enables the INT 0 external interrupt 0 = Disables the INT 0 external interrupt bit 3 RBIE: RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt 0 = Disables the RB port change interrupt bit 2 TMR 0 IF: TMR 0 Overflow Interrupt Flag bit 1 = TMR 0 register has overflowed (must be cleared in software) 0 = TMR 0 register did not overflow bit 1 INT 0 IF: INT 0 External Interrupt Flag bit 1 = The INT 0 external interrupt occurred (must be cleared in software) 0 = The INT 0 external interrupt did not occur bit 0 RBIF: RB Port Change Interrupt Flag bit(1) 1 = At least one of the RB 7: RB 4 pins changed state (must be cleared in software) 0 = None of the RB 7: RB 4 pins have changed state

Registro int. CON bit 5 TMR 0 IE: TMR 0 Overflow Interrupt Enable bit 1 = Enables the TMR 0 overflow interrupt 0 = Disables the TMR 0 overflow interrupt bit 4 INT 0 IE: INT 0 External Interrupt Enable bit 1 = Enables the INT 0 external interrupt 0 = Disables the INT 0 external interrupt bit 3 RBIE: RB Port Change Interrupt Enable bit 1 = Enables the RB port change interrupt 0 = Disables the RB port change interrupt bit 2 TMR 0 IF: TMR 0 Overflow Interrupt Flag bit 1 = TMR 0 register has overflowed (must be cleared in software) 0 = TMR 0 register did not overflow bit 1 INT 0 IF: INT 0 External Interrupt Flag bit 1 = The INT 0 external interrupt occurred (must be cleared in software) 0 = The INT 0 external interrupt did not occur bit 0 RBIF: RB Port Change Interrupt Flag bit(1) 1 = At least one of the RB 7: RB 4 pins changed state (must be cleared in software) 0 = None of the RB 7: RB 4 pins have changed state

Registro y bits de interrupcion