Innovative Sequential Synthesis and Verification Logic Synthesis and

- Slides: 16

Innovative Sequential Synthesis and Verification Logic Synthesis and Verification Group Department of EECS UC Berkeley Robert Brayton Mike Case Satrajit Chatterjee Sungmin Cho Aaron Hurst Alan Mishchenko Zile Wei

Overview l l l Introduction Innovations in synthesis and verification Overview of current R&D activities Recent publications Future work Conclusions

Introduction l Research goals l l l researching solutions for a variety of EDA problems producing algorithms that are competitive in quality but faster than the currently used ones developing new efficient implementations and releasing the source code to the community

Innovations l Synthesis l l l from SOP/BDD logic representations ― to AIGs and truth tables from combinational ― to “sequentially transparent” from one-snapshot ― to multiple-snapshot synthesis from separated ― to integrated (synthesis/mapping/retiming) from complex and slow algorithms ― to simple and fast l l l AIG rewriting vs. traditional synthesis flows priority-cut-based mapping vs. traditional cut-based mapping Verification l l l from predominantly combinational ― to sequential from trusted ― to independently verifiable using certificates from separate ― to synergistically combined with synthesis l l using fast synthesis as a preprocessing/intermediate step using synthesis information to speed up verification

Overview of Current Activities l Current research directions l l l l Logic synthesis based on AIGs Improvements to AIG rewriting FPGA mapping using priority cuts Integrated synthesis/mapping/retiming Fast retiming algorithms Co-developing synthesis and verification Developing new implementations in ABC l l l ABC is a growing logic synthesis and verification system It reflects the current state of our research findings It is increasingly adopted in academia and industry

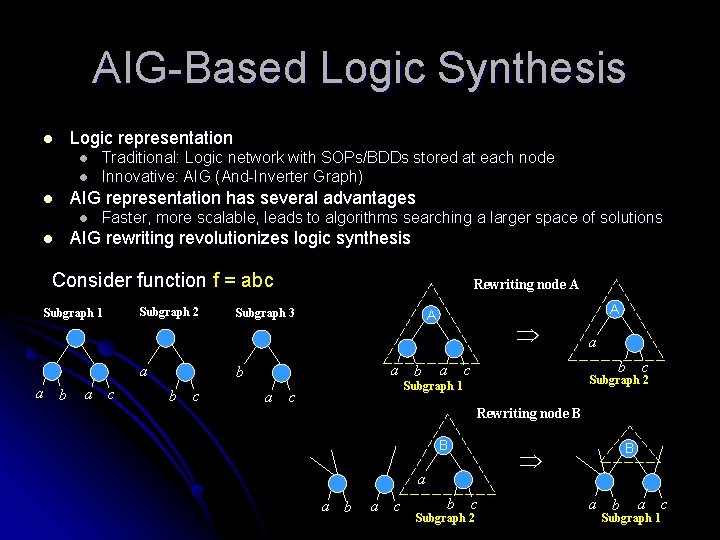

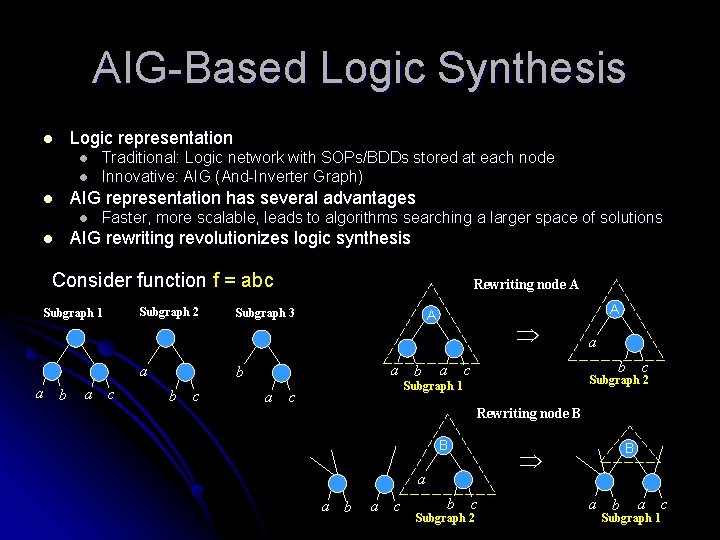

AIG-Based Logic Synthesis l Logic representation l l l AIG representation has several advantages l l Traditional: Logic network with SOPs/BDDs stored at each node Innovative: AIG (And-Inverter Graph) Faster, more scalable, leads to algorithms searching a larger space of solutions AIG rewriting revolutionizes logic synthesis Consider function f = abc Subgraph 1 Subgraph 2 a a b a c Rewriting node A Subgraph 3 a b b b c a A A b a c c Subgraph 2 Subgraph 1 c a Rewriting node B B a a b a c b B c Subgraph 2 a b a c Subgraph 1

Why AIG Rewriting is Efficient? l Using all K-feasible cuts explores all fanin-limited node boundaries l l Using all fanin-limited Boolean divisors l l Traditional sequential synthesis is limited to retiming Iterating fast local transforms many times l l Traditional synthesis is limited to algebraic kernels extracted from the current SOPs of the nodes AIG-based synthesis uses all sequential cuts l l Traditional synthesis is limited to only one node boundary Traditional synthesis is often too slow to allow multiple iterations Experimental results can be found in DAC 2006 paper

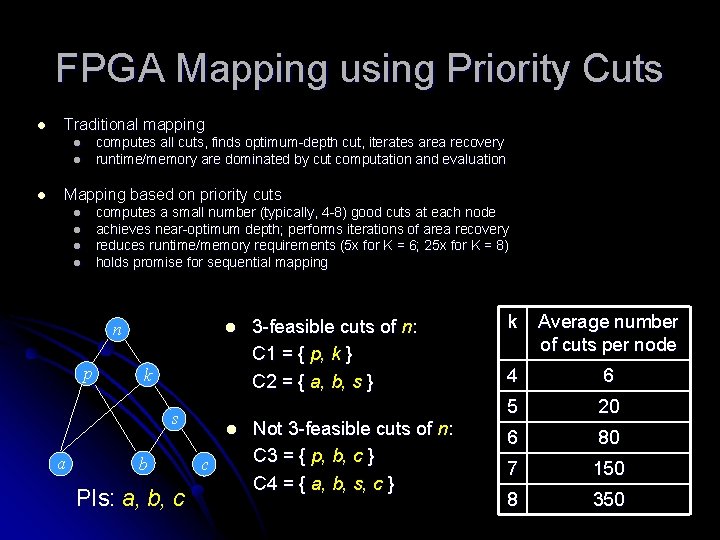

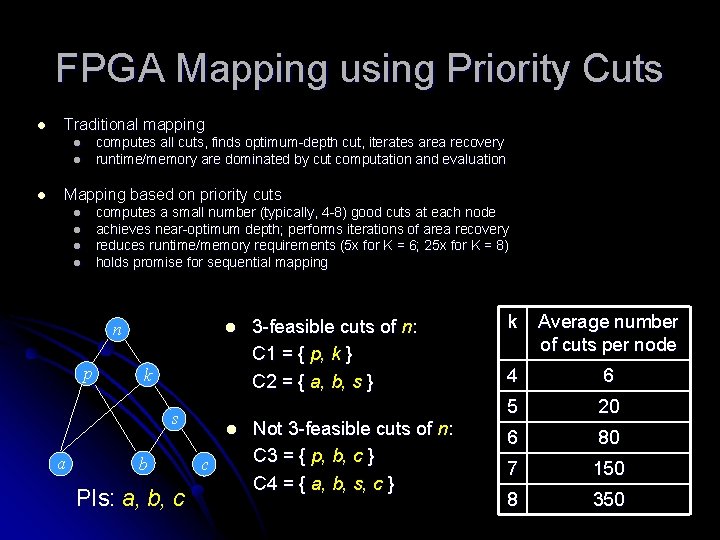

FPGA Mapping using Priority Cuts l Traditional mapping computes all cuts, finds optimum-depth cut, iterates area recovery runtime/memory are dominated by cut computation and evaluation l l l Mapping based on priority cuts computes a small number (typically, 4 -8) good cuts at each node achieves near-optimum depth; performs iterations of area recovery reduces runtime/memory requirements (5 x for K = 6; 25 x for K = 8) holds promise for sequential mapping l l n p l k s a b PIs: a, b, c l c 3 -feasible cuts of n: C 1 = { p, k } C 2 = { a, b, s } Not 3 -feasible cuts of n: C 3 = { p, b, c } C 4 = { a, b, s, c } k Average number of cuts per node 4 6 5 20 6 80 7 150 8 350

Recent Work on Retiming l Implemented three flavors of retiming: l Delay-oriented retiming based on iterative sequential arrival time computation [P. Pan, ICCD ’ 97 and FPGA ‘ 98] l l Incremental heuristic delay-oriented retiming [D. P. Singh, DAC ’ 05] l l Fast and scalable Doing a good job on both delay and register count Another possibility is to combine retiming and clock skewing l l Start with minimum-register retiming Find a trade-off between retiming and skewing, which takes into account l l l Minimizes the number of registers but ignored the delay Need a hybrid approach that is l l l The register increase is better controllable but still possible New minimum-register retiming based a simplified version of maximum-flow [submitted to DAC ’ 07] l l Often increases the number of registers considerably (50 -100%) The cost of additional registers due to partial retiming The cost of additional buffers due to partial skewing Studying new promising delay-optimal algorithm [H. Zhou, ASPDAC ’ 05]

Integrated Mapping and Retiming l A year ago, developed an integrated solution for minimizing delay while performing synthesis/mapping/retiming l l Currently working on a second-generation solution l l l The approach suffers from area penalty Uses priority cuts Reduces mapping/retiming to combinational mapping while guaranteeing delay optimality in almost all cases Promising results l l l Delay improvement ~28% (compared to 4 -19% for retiming alone) Area is comparable to area after combinational mapping Faster and more scalable due to using priority cuts

Verification Capabilities l Combinational equivalence checking (ICCAD 2006) l l Incremental verification after synthesis (IWLS 2006) l l l will leverage the strengths of the robust CEC engine will be based on a synergistic combination of induction and interpolation may benefit greatly from fast logic synthesis as a pro-processor Recording verification certificates and verifying them (accepted to DAC ’ 07) l l uses synthesis information stored in the form of a history AIG verification runtime does not exceed synthesis runtime scalable verification is a consequence of scalable synthesis General purpose sequential equivalence checking (work in progress) l l l developed an AIG package with functional reduction (“SAT sweeping”) developed a CEC engine based on AIGs, simulation, and SAT successfully used them in several academic and industrial projects Producing extended resolution proofs of each step in verification Composing individual proofs into one final proof Independently verifying this proof using a very simple resolution checker Synthesis and verification are two sides of the same coin

ABC: Logic Synthesis and Verification System l Public-domain source code and manuals: http: //www. eecs. berkeley. edu/~alanmi/abc/ l New release will be out in about a week l Variety of input formats (BLIF, BENCH, AIGER) l l l l recently added: hierarchical BLIF, hierarchical Verilog (structural netlist) Improved AIG rewriting package Improved FPGA mapper Improved CEC engine New retiming engine (min-register, min-delay, etc) Experimental code for sequential rewriting and choice accumulation Designed to handle very large designs

Recent Publications l Combinational AIG rewriting A. Mishchenko, S. Chatterjee, and R. Brayton, "DAG-aware AIG rewriting: A fresh look at combinational logic synthesis", Proc. DAC '06, pp. 532 -536. http: //www. eecs. berkeley. edu/~alanmi/publications/2006/dac 06_rwr. pdf l Synthesis/mapping/retiming combined A. Mishchenko, S. Chatterjee, R. K. Brayton, and P. Pan, "Integrating logic synthesis, technology mapping, and retiming", ERL Technical Report, UC Berkeley, April '06. http: //www. eecs. berkeley. edu/~alanmi/publications/2006/tech 06_int. pdf l Improved LUT-mapping based on cut enumeration A. Mishchenko, S. Chatterjee, and R. Brayton, "Improvements to technology mapping for LUT-based FPGAs". IEEE TCAD, Vol. 26(2), Feb 2007, pp. 240 -253. . http: //www. eecs. berkeley. edu/~alanmi/publications/2006/tcad 06_map. pdf l Combinational equivalence checking A. Mishchenko, S. Chatterjee, R. Brayton, and N. Een, "Improvements to combinational equivalence checking", Proc. ICCAD '06. http: //www. eecs. berkeley. edu/~alanmi/publications/2006/iccad 06_cec. pdf l Verifying verification tools S. Chatterjee, A. Mishchenko, R. Brayton, and A. Kuehlmann, "On resolution proofs for combinational equivalence checking", Accepted to DAC ‘ 07. http: //www. eecs. berkeley. edu/~alanmi/publications/2007/dac 07_res. pdf

Papers Submitted to IWLS l Integrating logic synthesis and placement l l Logic optimization and mapping l l l Mapping with priority cuts SAT-based logic optimization and re-synthisis Sequential rewriting Scalable exploration of functional dependency by interpolation and incremental SAT solving Benchmarking logic synthesis for FPGAs Retiming l l l Optimum placement of non-reconvergent DAGs by dynamic programming Fast minimum-register retiming via binary maximum-flow Minimizing implementation costs with end-to-end retiming Model checking l Automated extraction of inductive invariants to aid model checking

Ongoing and Future Work l Synthesis l l Verification l l Placement-aware AIG-based synthesis and technology mapping Integrated synthesis/mapping/retiming using priority cuts AIG optimizations with don’t-cares and Boolean decomposition Developing a verification system with information from synthesis Developing a new sequential equivalence checking package Recording resolution proofs of CEC and SEC Releasing updated versions of ABC

Conclusions l Reviewed current state of our research l l l l Logic synthesis based on AIGs Improvements to AIG rewriting LUT mapping using priority cuts Integrated synthesis/mapping/retiming Fast retiming capabilities Bridging the gap between synthesis and verification Listed recent publications Outlined future work