Implementing an Instruction Set David E Culler CS

![Tiny. MIPS • Reg-Reg instructions (op == 0) – addu – subu R[rd] : Tiny. MIPS • Reg-Reg instructions (op == 0) – addu – subu R[rd] :](https://slidetodoc.com/presentation_image/57a54df511939427fcb5077b6d1cdbdf/image-11.jpg)

![Ifetch: IR : = Mem[PC] RAM D A + • RAM_addr <- A <- Ifetch: IR : = Mem[PC] RAM D A + • RAM_addr <- A <-](https://slidetodoc.com/presentation_image/57a54df511939427fcb5077b6d1cdbdf/image-14.jpg)

- Slides: 25

Implementing an Instruction Set David E. Culler CS 61 CL Oct 28, 2009 Lecture 9 10/28/09 UCB CS 61 CL F 09 Lec 9 1

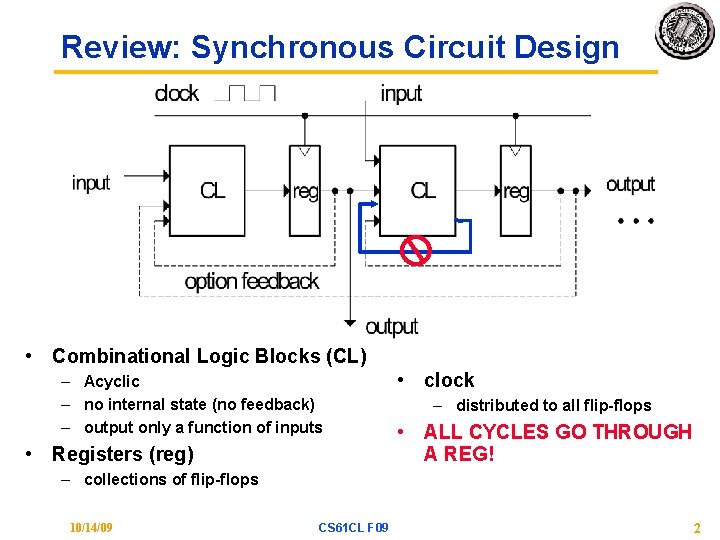

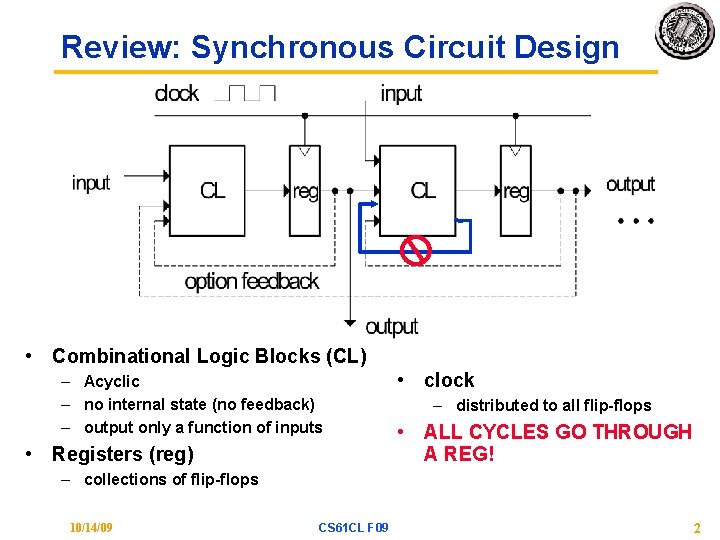

Review: Synchronous Circuit Design • Combinational Logic Blocks (CL) – Acyclic – no internal state (no feedback) – output only a function of inputs • Registers (reg) • clock – distributed to all flip-flops • ALL CYCLES GO THROUGH A REG! – collections of flip-flops 10/14/09 CS 61 CL F 09 2

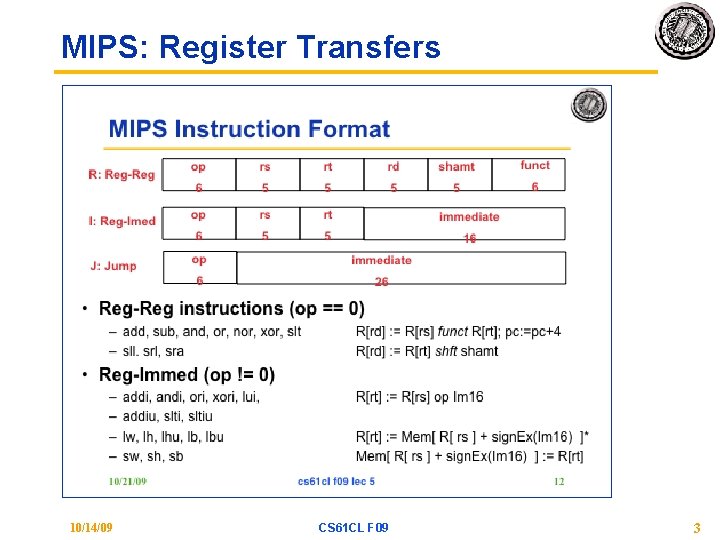

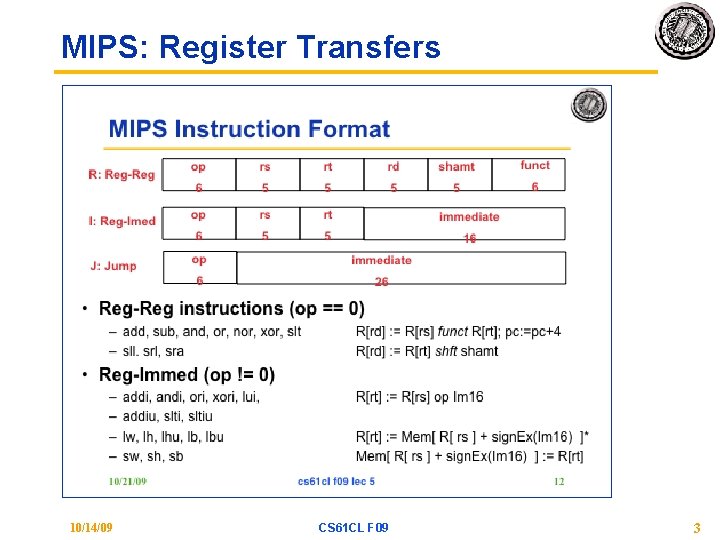

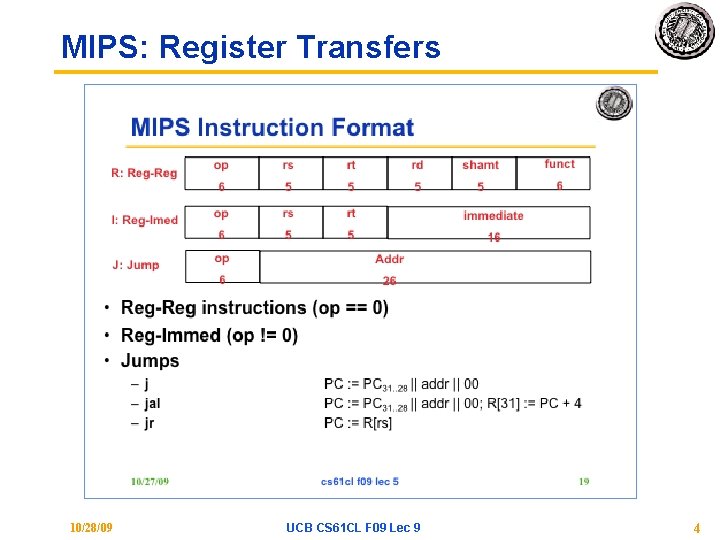

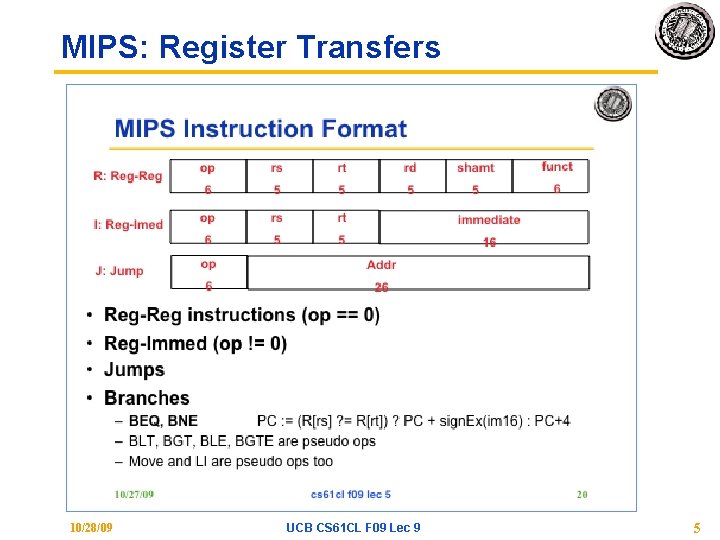

MIPS: Register Transfers 10/14/09 CS 61 CL F 09 3

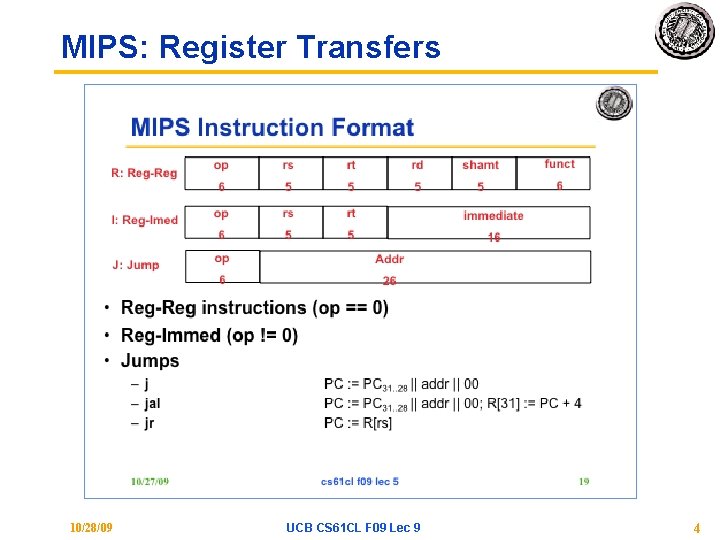

MIPS: Register Transfers 10/28/09 UCB CS 61 CL F 09 Lec 9 4

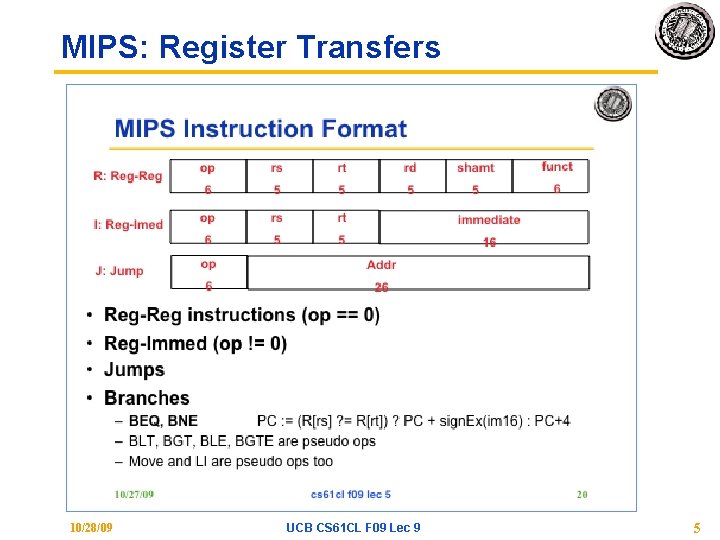

MIPS: Register Transfers 10/28/09 UCB CS 61 CL F 09 Lec 9 5

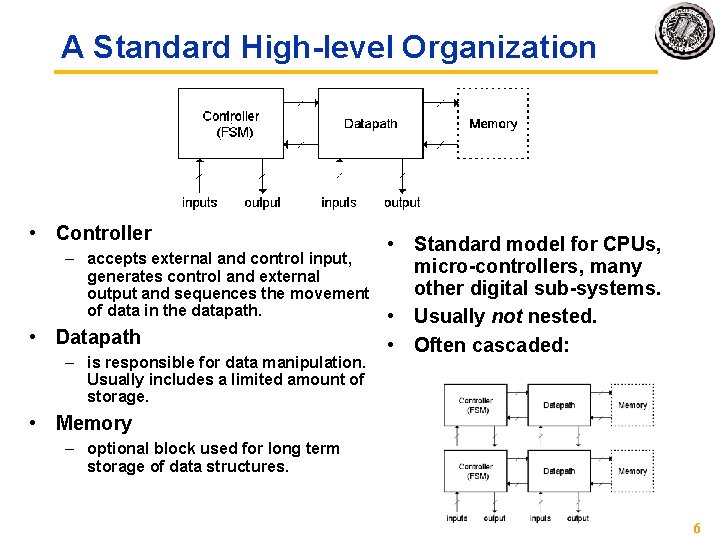

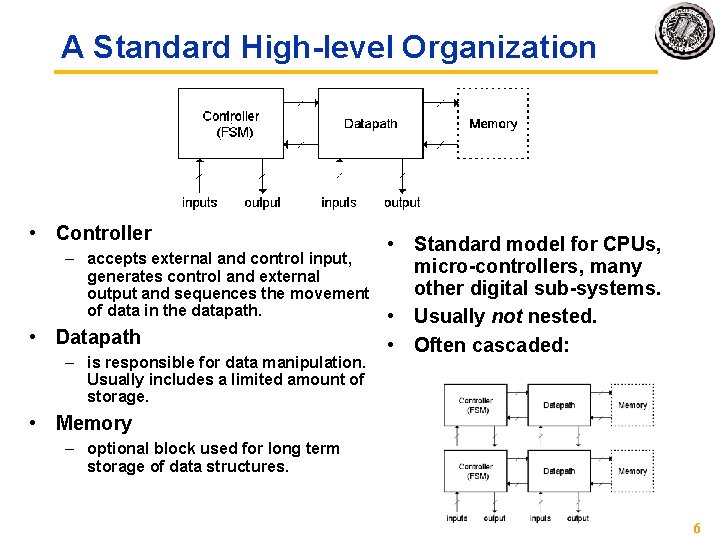

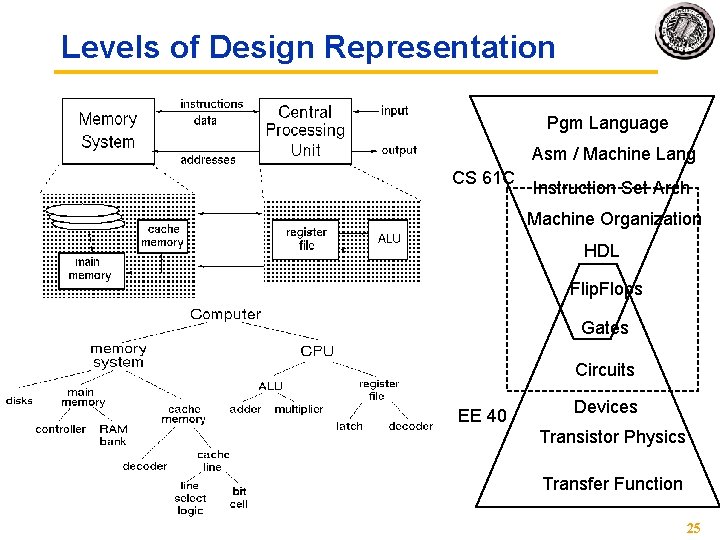

A Standard High-level Organization • Controller – accepts external and control input, generates control and external output and sequences the movement of data in the datapath. • Datapath – is responsible for data manipulation. Usually includes a limited amount of storage. • Standard model for CPUs, micro-controllers, many other digital sub-systems. • Usually not nested. • Often cascaded: • Memory – optional block used for long term storage of data structures. 6

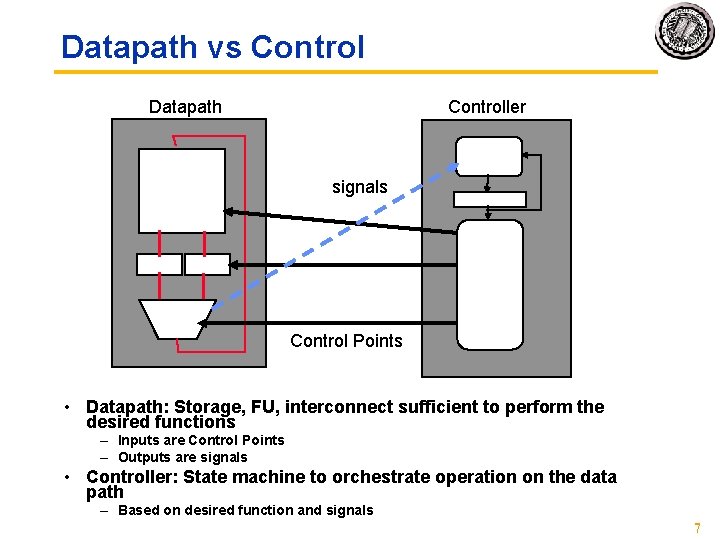

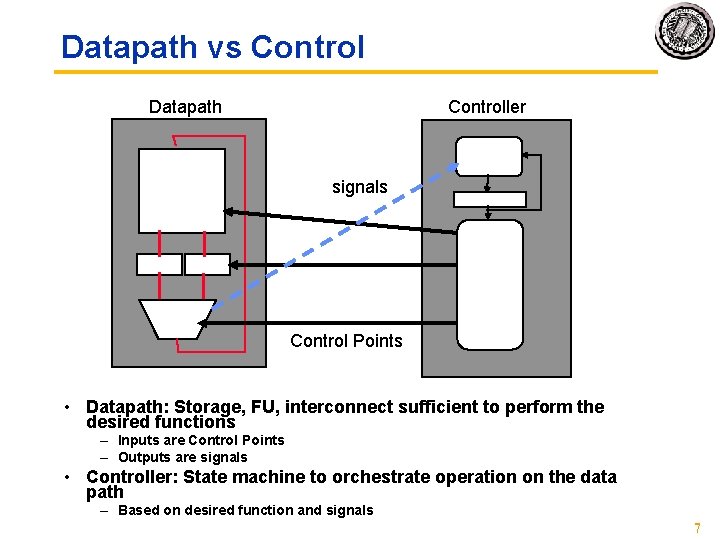

Datapath vs Control Datapath Controller signals Control Points • Datapath: Storage, FU, interconnect sufficient to perform the desired functions – Inputs are Control Points – Outputs are signals • Controller: State machine to orchestrate operation on the data path – Based on desired function and signals 7

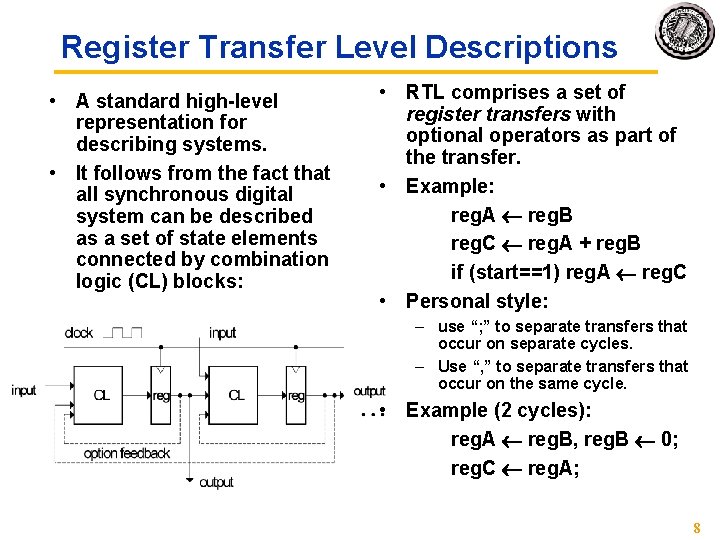

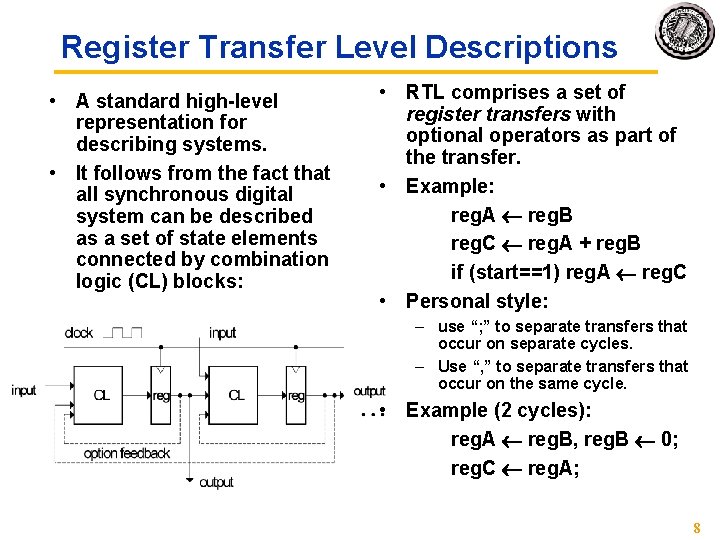

Register Transfer Level Descriptions • A standard high-level representation for describing systems. • It follows from the fact that all synchronous digital system can be described as a set of state elements connected by combination logic (CL) blocks: • RTL comprises a set of register transfers with optional operators as part of the transfer. • Example: reg. A reg. B reg. C reg. A + reg. B if (start==1) reg. A reg. C • Personal style: – use “; ” to separate transfers that occur on separate cycles. – Use “, ” to separate transfers that occur on the same cycle. • Example (2 cycles): reg. A reg. B, reg. B 0; reg. C reg. A; 8

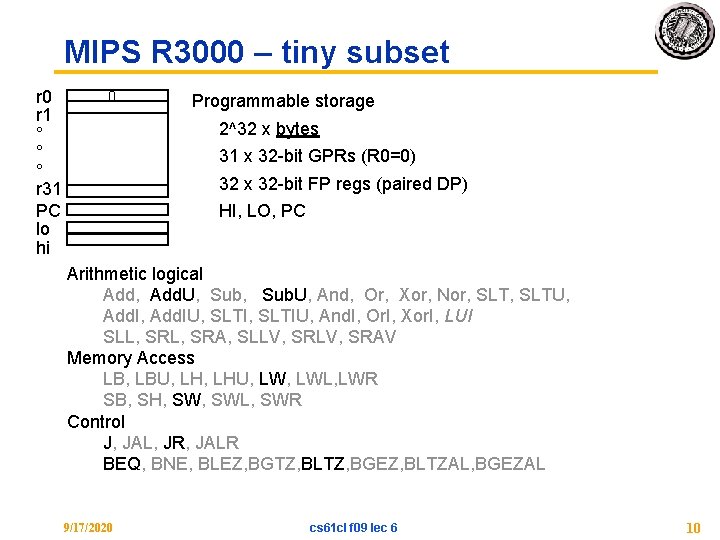

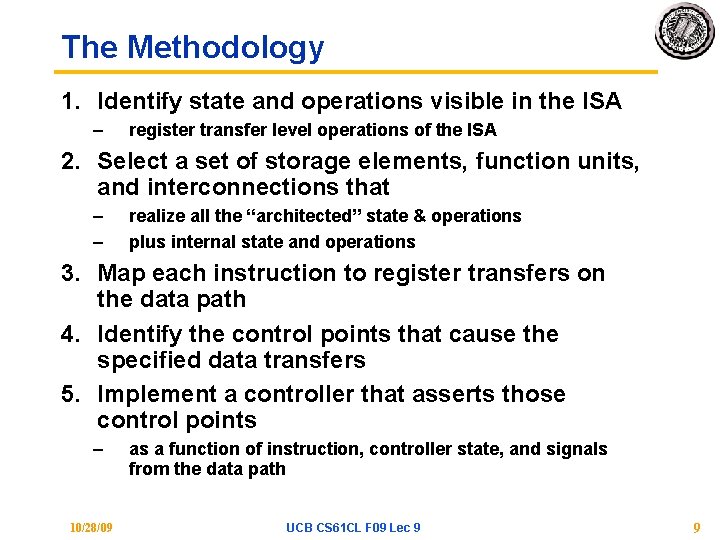

The Methodology 1. Identify state and operations visible in the ISA – register transfer level operations of the ISA 2. Select a set of storage elements, function units, and interconnections that – – realize all the “architected” state & operations plus internal state and operations 3. Map each instruction to register transfers on the data path 4. Identify the control points that cause the specified data transfers 5. Implement a controller that asserts those control points – 10/28/09 as a function of instruction, controller state, and signals from the data path UCB CS 61 CL F 09 Lec 9 9

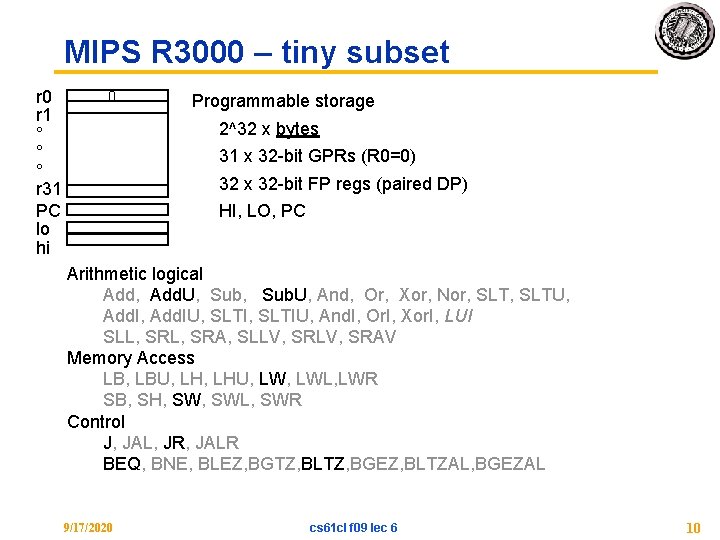

MIPS R 3000 – tiny subset r 0 r 1 ° ° ° r 31 PC lo hi 0 Programmable storage 2^32 x bytes 31 x 32 -bit GPRs (R 0=0) 32 x 32 -bit FP regs (paired DP) HI, LO, PC Arithmetic logical Add, Add. U, Sub. U, And, Or, Xor, Nor, SLTU, Add. IU, SLTIU, And. I, Or. I, Xor. I, LUI SLL, SRA, SLLV, SRAV Memory Access LB, LBU, LHU, LWL, LWR SB, SH, SWL, SWR Control J, JAL, JR, JALR BEQ, BNE, BLEZ, BGTZ, BLTZ, BGEZ, BLTZAL, BGEZAL 9/17/2020 cs 61 cl f 09 lec 6 10

![Tiny MIPS RegReg instructions op 0 addu subu Rrd Tiny. MIPS • Reg-Reg instructions (op == 0) – addu – subu R[rd] :](https://slidetodoc.com/presentation_image/57a54df511939427fcb5077b6d1cdbdf/image-11.jpg)

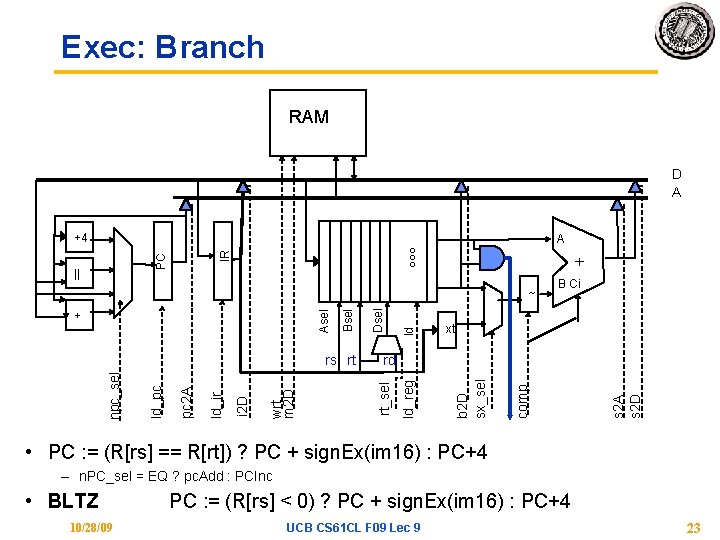

Tiny. MIPS • Reg-Reg instructions (op == 0) – addu – subu R[rd] : = R[rs] + R[rt]; pc: =pc+4 R[rd] : = R[rs] - R[rt]; pc: =pc+4 • Reg-Immed (op != 0) – lw – sw R[rt] : = Mem[ R[ rs ] + sign. Ex(Im 16) ] : = R[rt] • Jumps – jr PC : = PC 31. . 28 || addr || 00 PC : = R[rs] • Branches – BEQ – BLTZ 10/28/09 PC : = (R[rs] == R[rt]) ? PC + sign. Ex(im 16) : PC+4 PC : = (R[rs] < 0) ? PC + sign. Ex(im 16) : PC+4 UCB CS 61 CL F 09 Lec 9 11

Administration • Project 3 is out – due Sun 11/15 • Homework 7 is out – due Wed 11/4 • Midterm 2 is Monday 11/9 10/28/09 UCB CS 61 CL F 09 Lec 9 12

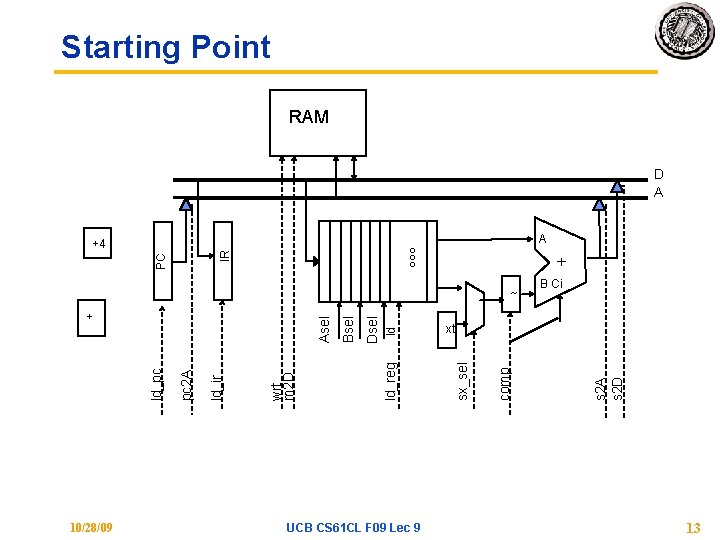

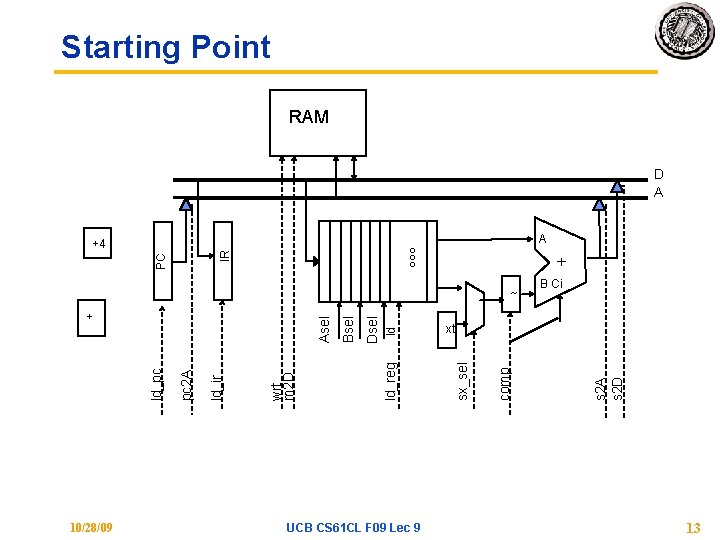

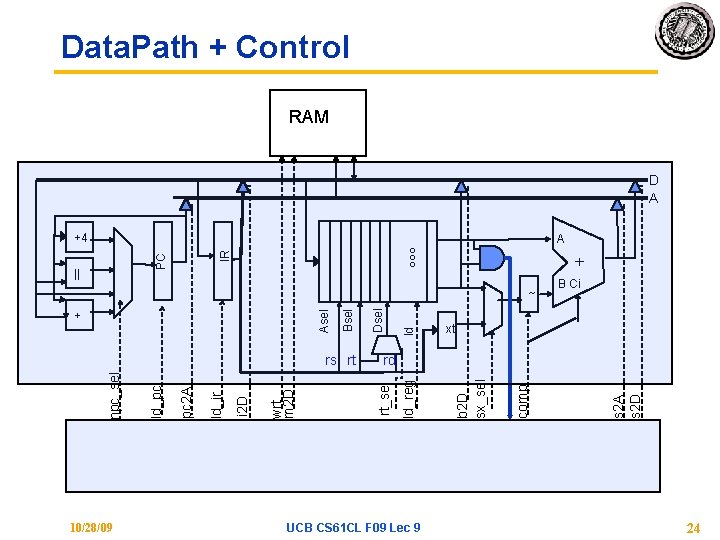

10/28/09 UCB CS 61 CL F 09 Lec 9 ~ s 2 A s 2 D comp sx_sel ld Dsel Bsel Asel + ld_reg wrt m 2 D °°° IR PC +4 ld_ir pc 2 A ld_pc Starting Point RAM D A A + B Ci xt 13

![Ifetch IR MemPC RAM D A RAMaddr A Ifetch: IR : = Mem[PC] RAM D A + • RAM_addr <- A <-](https://slidetodoc.com/presentation_image/57a54df511939427fcb5077b6d1cdbdf/image-14.jpg)

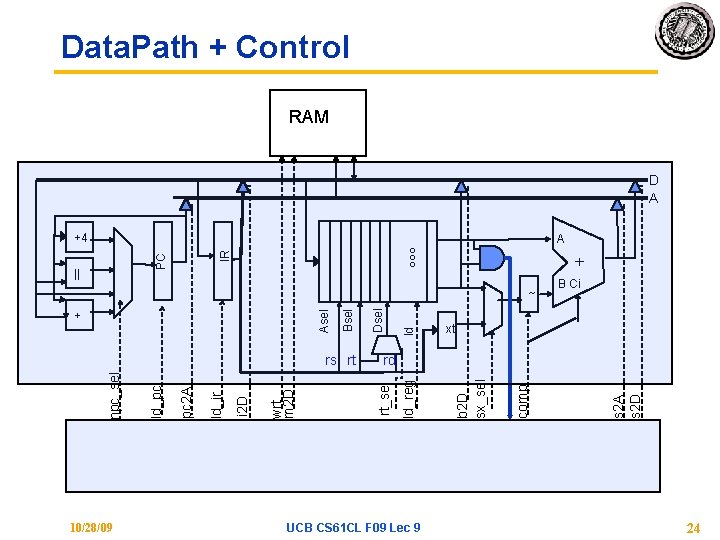

Ifetch: IR : = Mem[PC] RAM D A + • RAM_addr <- A <- PC; • IR_in <- D <- RAM_data; • IR : = IR_in; 10/28/09 B Ci comp xt sx_sel ld Dsel ld_reg wrt m 2 D ld_ir pc 2 A ld_pc Asel + Bsel ~ s 2 A s 2 D PC IR °°° A +4 (pc 2 A) (m 2 D, ~wrt) (ld_ir) UCB CS 61 CL F 09 Lec 9 14

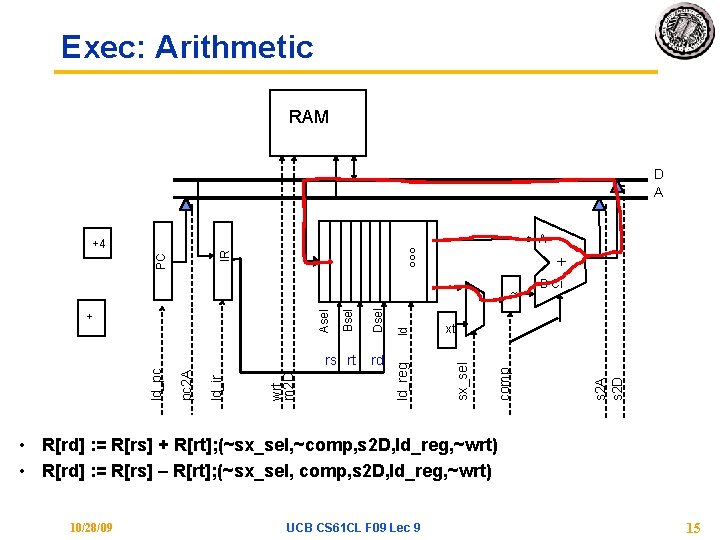

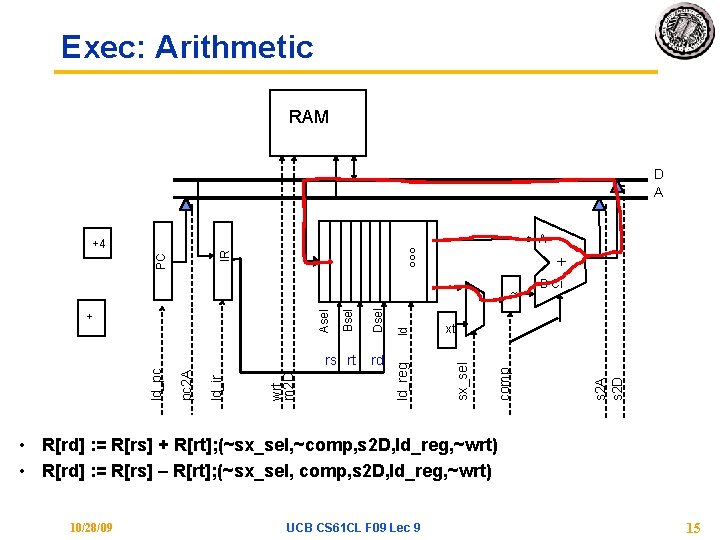

Exec: Arithmetic RAM D A + comp ld rd B Ci xt sx_sel wrt m 2 D ld_ir pc 2 A ld_pc + ld_reg Dsel rs rt Asel Bsel ~ s 2 A s 2 D PC IR °°° A +4 • R[rd] : = R[rs] + R[rt]; (~sx_sel, ~comp, s 2 D, ld_reg, ~wrt) • R[rd] : = R[rs] – R[rt]; (~sx_sel, comp, s 2 D, ld_reg, ~wrt) 10/28/09 UCB CS 61 CL F 09 Lec 9 15

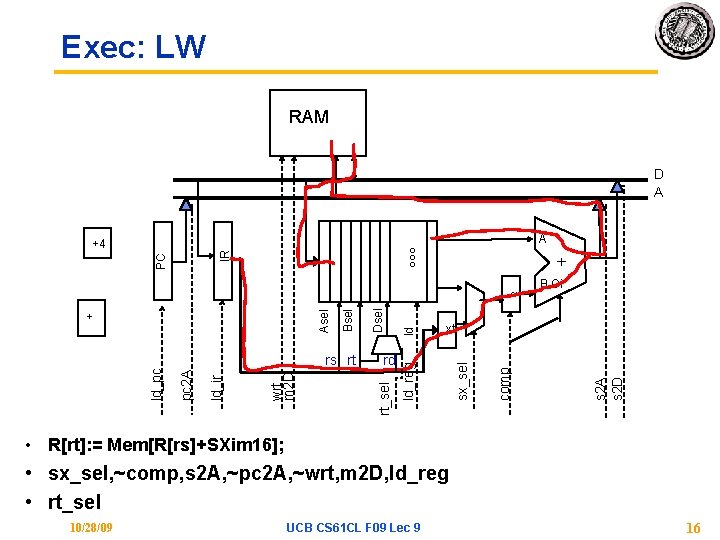

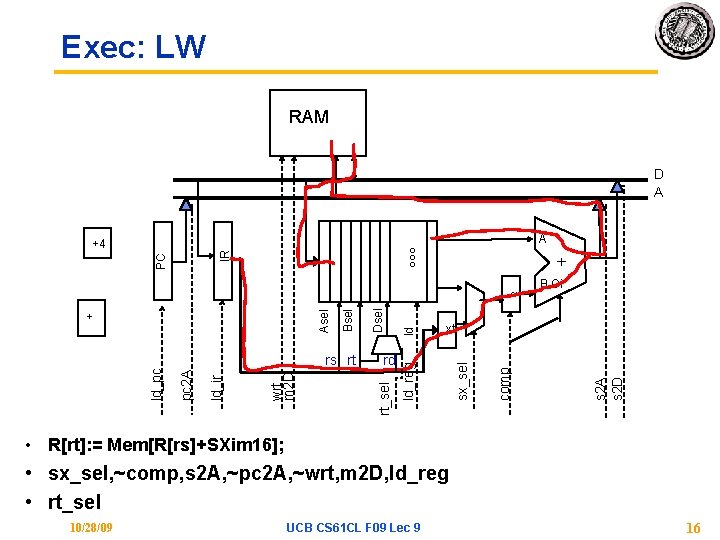

Exec: LW RAM D A + comp sx_sel ld B Ci xt ld_reg Dsel rd rt_sel wrt m 2 D ld_ir rs rt pc 2 A ld_pc + Bsel Asel ~ s 2 A s 2 D PC IR °°° A +4 • R[rt]: = Mem[R[rs]+SXim 16]; • sx_sel, ~comp, s 2 A, ~pc 2 A, ~wrt, m 2 D, ld_reg • rt_sel 10/28/09 UCB CS 61 CL F 09 Lec 9 16

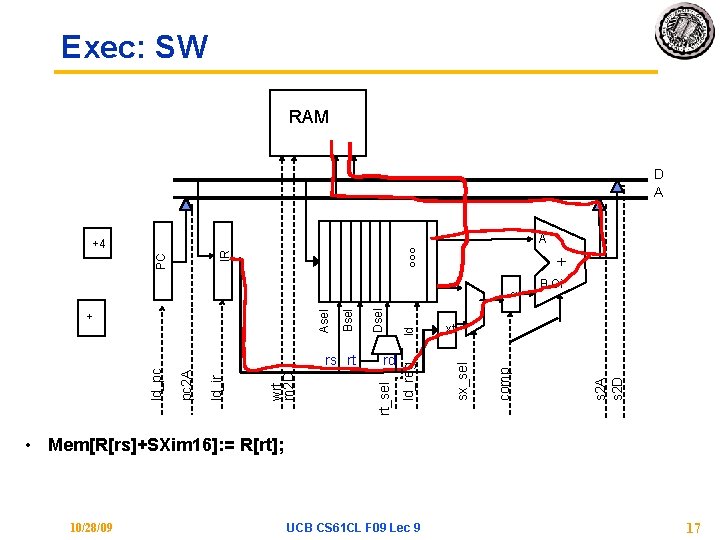

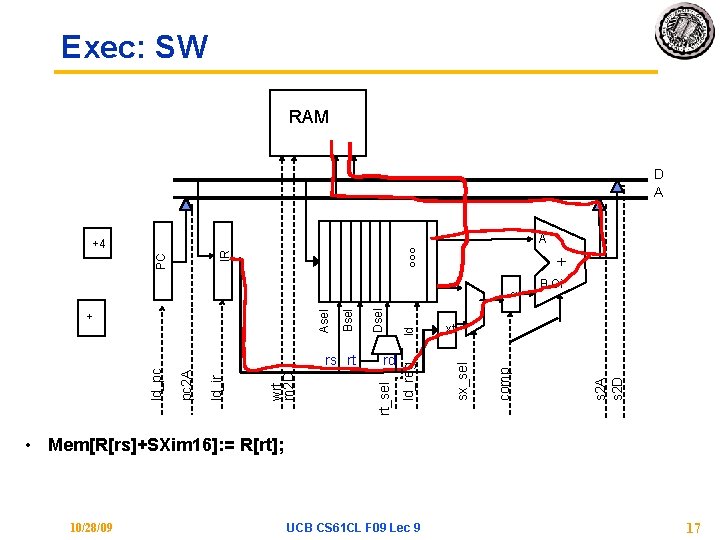

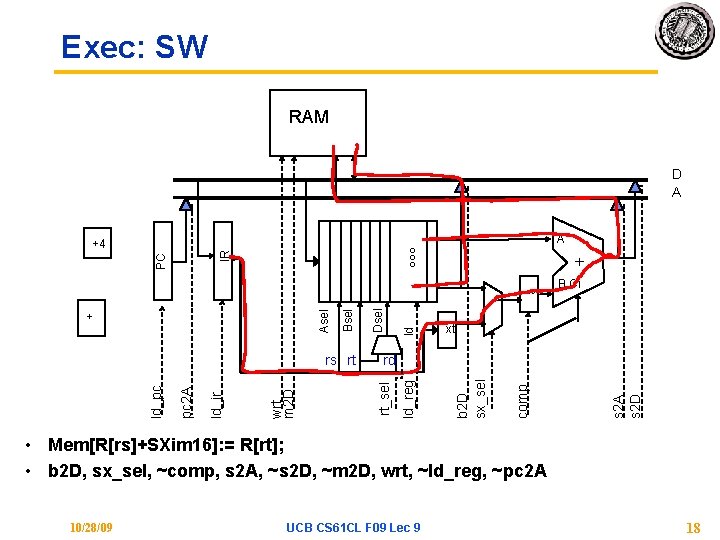

Exec: SW RAM D A + B Ci comp xt sx_sel ld ld_reg Dsel rd rt_sel wrt m 2 D ld_ir rs rt pc 2 A ld_pc + Bsel Asel ~ s 2 A s 2 D PC IR °°° A +4 • Mem[R[rs]+SXim 16]: = R[rt]; 10/28/09 UCB CS 61 CL F 09 Lec 9 17

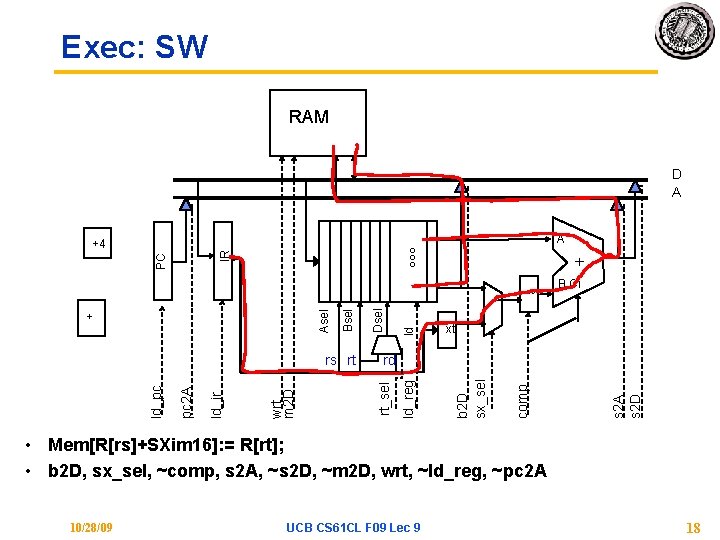

Exec: SW RAM D A + ld Dsel B Ci xt comp b 2 D sx_sel rd ld_reg wrt m 2 D ld_ir pc 2 A ld_pc rs rt rt_sel + Bsel Asel ~ s 2 A s 2 D PC IR °°° A +4 • Mem[R[rs]+SXim 16]: = R[rt]; • b 2 D, sx_sel, ~comp, s 2 A, ~s 2 D, ~m 2 D, wrt, ~ld_reg, ~pc 2 A 10/28/09 UCB CS 61 CL F 09 Lec 9 18

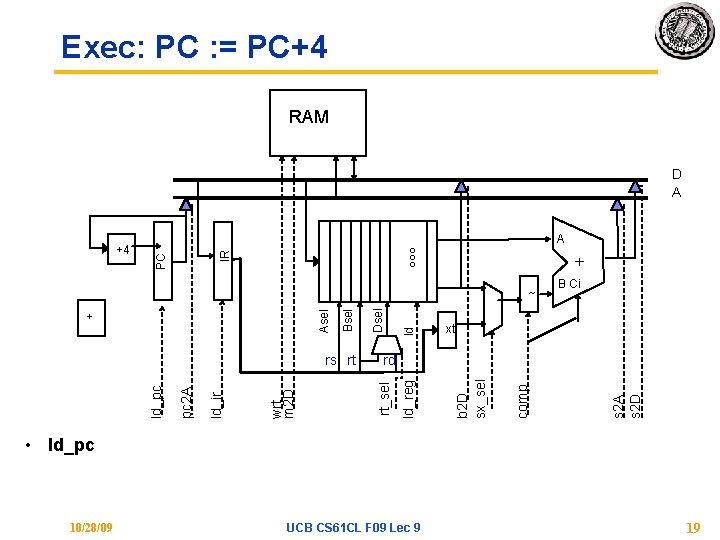

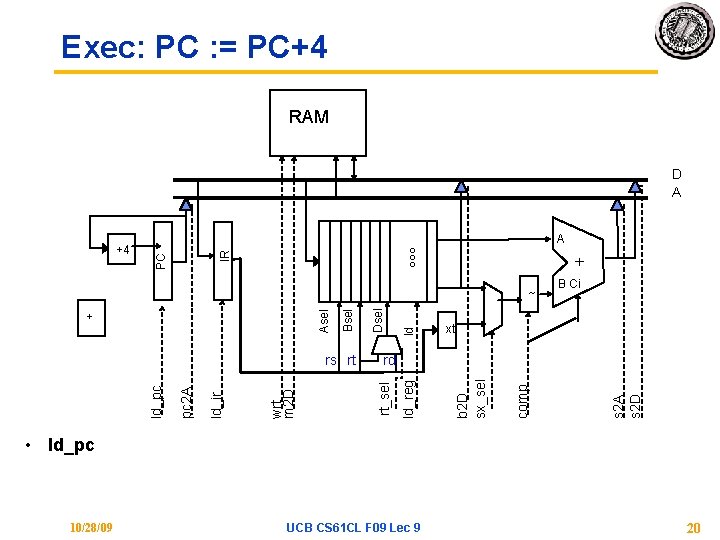

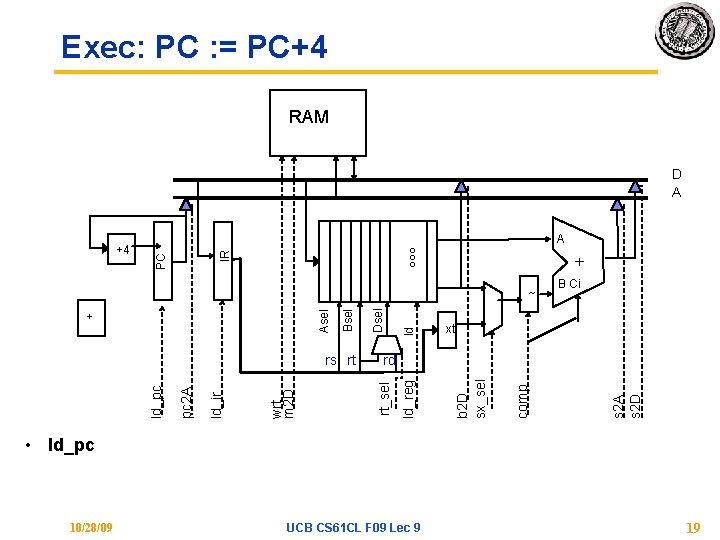

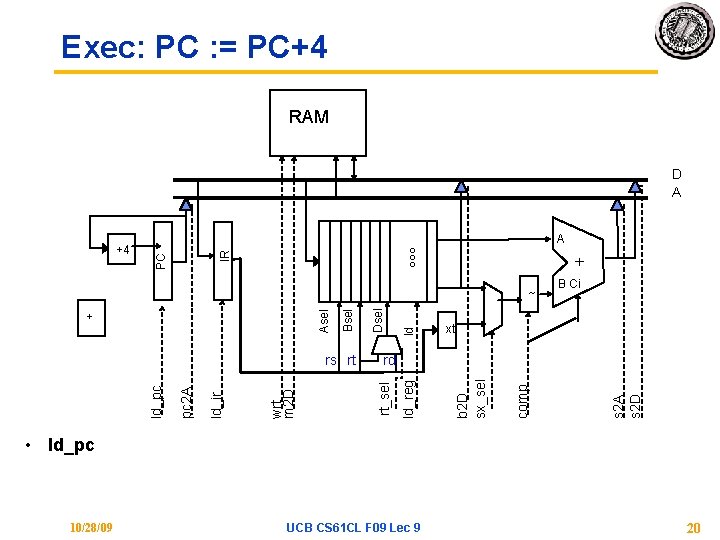

Exec: PC : = PC+4 RAM D A IR °°° A + ld Dsel B Ci xt comp b 2 D sx_sel rd ld_reg wrt m 2 D ld_ir pc 2 A ld_pc rs rt rt_sel + Bsel Asel ~ s 2 A s 2 D PC +4 • ld_pc 10/28/09 UCB CS 61 CL F 09 Lec 9 19

Exec: PC : = PC+4 RAM D A IR °°° A + ld Dsel B Ci xt comp b 2 D sx_sel rd ld_reg wrt m 2 D ld_ir pc 2 A ld_pc rs rt rt_sel + Bsel Asel ~ s 2 A s 2 D PC +4 • ld_pc 10/28/09 UCB CS 61 CL F 09 Lec 9 20

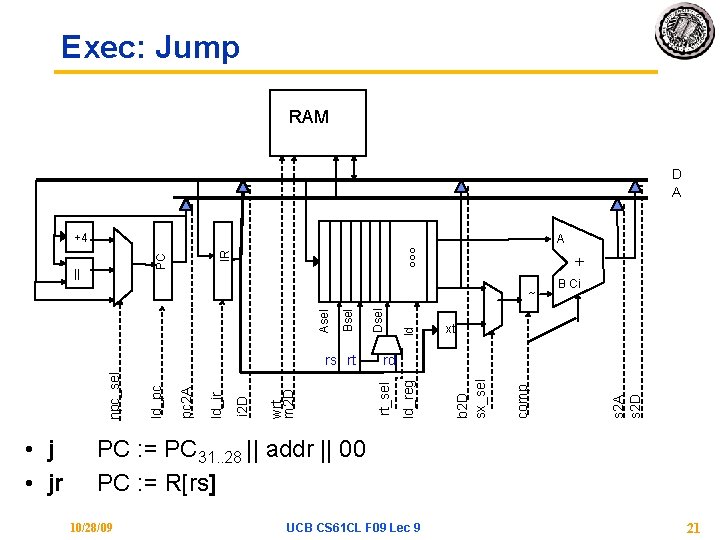

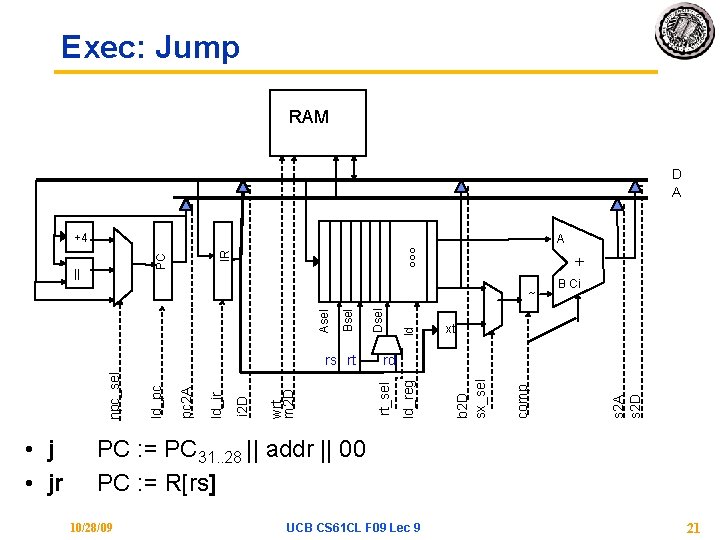

Exec: Jump RAM D A +4 IR + • jr ld Dsel B Ci xt comp b 2 D sx_sel rd ld_reg wrt m 2 D i 2 D ld_ir pc 2 A ld_pc npc_sel rs rt rt_sel Bsel Asel ~ s 2 A s 2 D PC || °°° A PC : = PC 31. . 28 || addr || 00 PC : = R[rs] 10/28/09 UCB CS 61 CL F 09 Lec 9 21

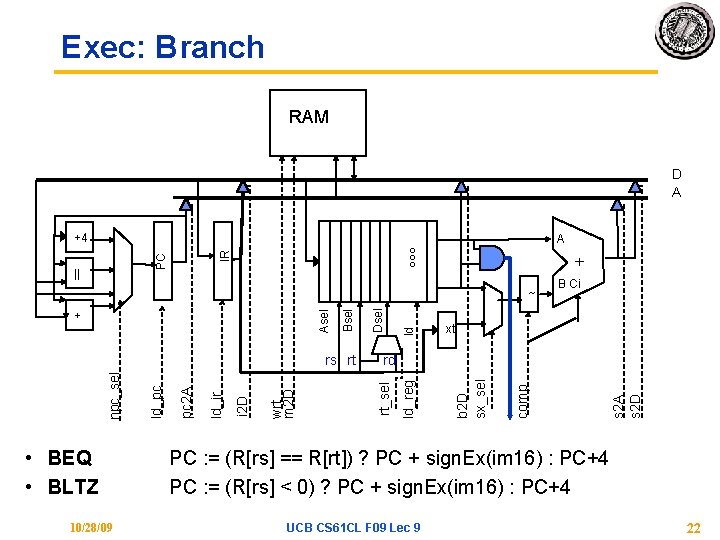

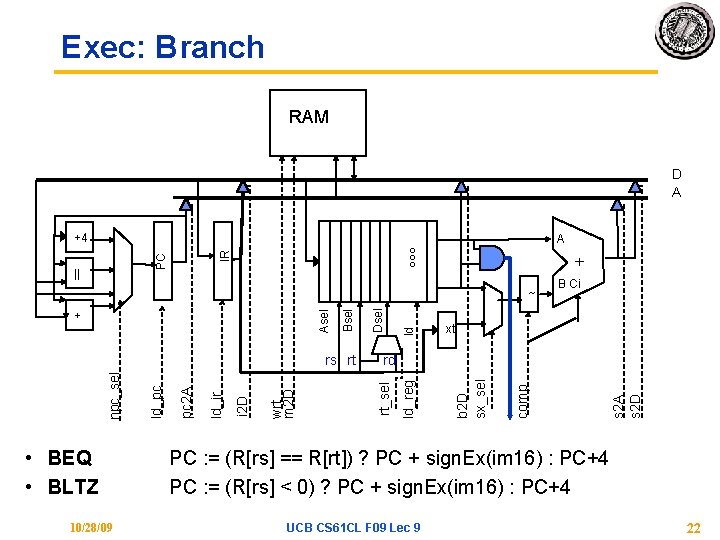

Exec: Branch RAM D A +4 IR + • BEQ • BLTZ 10/28/09 ld Dsel B Ci xt comp b 2 D sx_sel rd ld_reg wrt m 2 D i 2 D ld_ir pc 2 A ld_pc npc_sel rs rt rt_sel + Bsel Asel ~ s 2 A s 2 D PC || °°° A PC : = (R[rs] == R[rt]) ? PC + sign. Ex(im 16) : PC+4 PC : = (R[rs] < 0) ? PC + sign. Ex(im 16) : PC+4 UCB CS 61 CL F 09 Lec 9 22

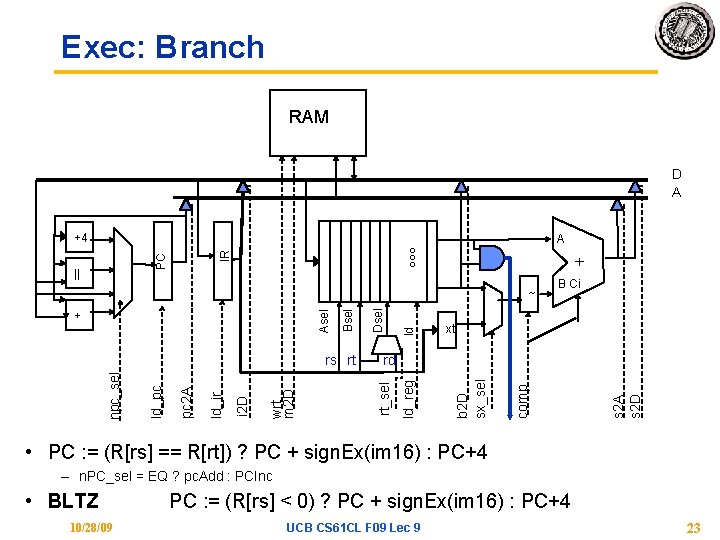

Exec: Branch RAM D A +4 IR + ld Dsel B Ci xt comp b 2 D sx_sel rd ld_reg wrt m 2 D i 2 D ld_ir pc 2 A ld_pc npc_sel rs rt rt_sel + Bsel Asel ~ s 2 A s 2 D PC || °°° A • PC : = (R[rs] == R[rt]) ? PC + sign. Ex(im 16) : PC+4 – n. PC_sel = EQ ? pc. Add : PCInc • BLTZ 10/28/09 PC : = (R[rs] < 0) ? PC + sign. Ex(im 16) : PC+4 UCB CS 61 CL F 09 Lec 9 23

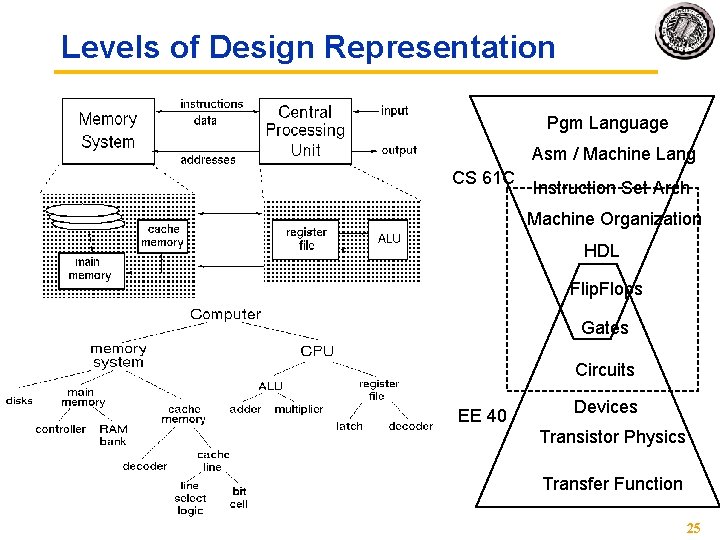

10/28/09 UCB CS 61 CL F 09 Lec 9 ld °°° IR +4 ~ s 2 A s 2 D comp b 2 D sx_sel ld_reg rs rt Dsel Bsel Asel + rt_sel wrt m 2 D i 2 D ld_ir pc 2 A PC || ld_pc npc_sel Data. Path + Control RAM D A A + B Ci xt rd 24

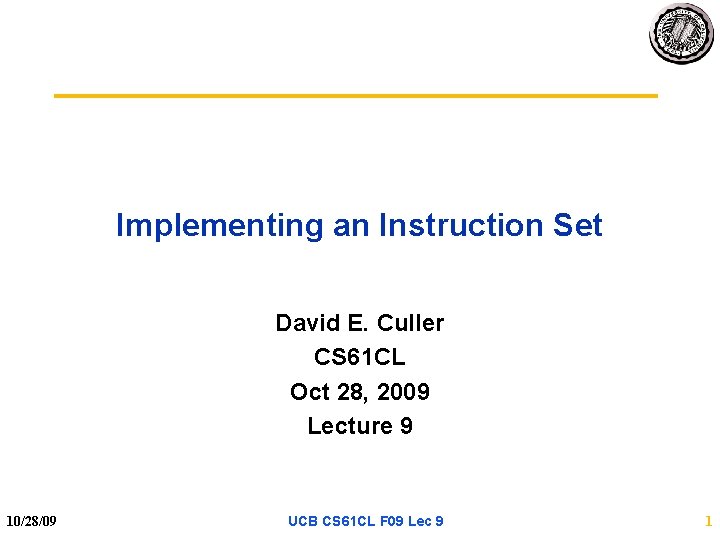

Levels of Design Representation Pgm Language Asm / Machine Lang CS 61 C Instruction Set Arch Machine Organization HDL Flip. Flops Gates Circuits EE 40 Devices Transistor Physics Transfer Function 25