Implementation of the Jet Algorithm ATLAS Level1 Calorimeter

- Slides: 18

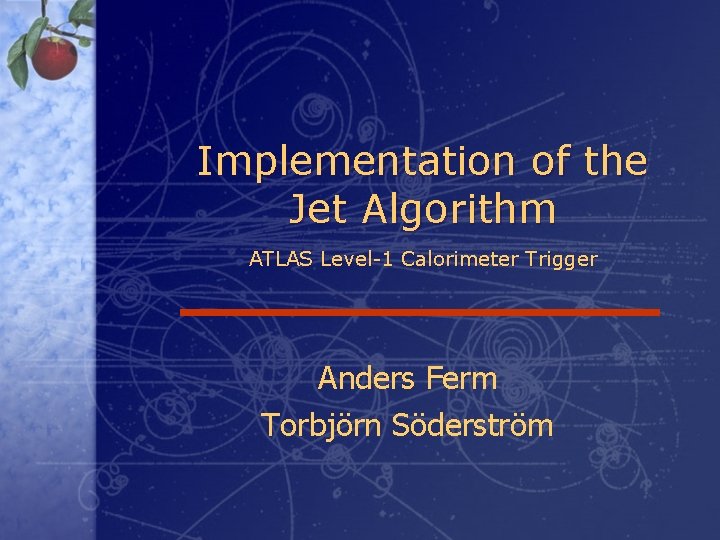

Implementation of the Jet Algorithm ATLAS Level-1 Calorimeter Trigger Anders Ferm Torbjörn Söderström

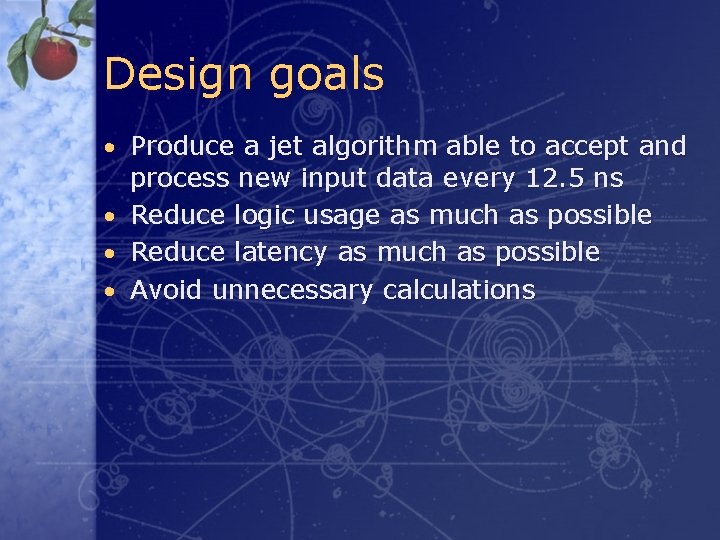

Design goals • Produce a jet algorithm able to accept and process new input data every 12. 5 ns • Reduce logic usage as much as possible • Reduce latency as much as possible • Avoid unnecessary calculations

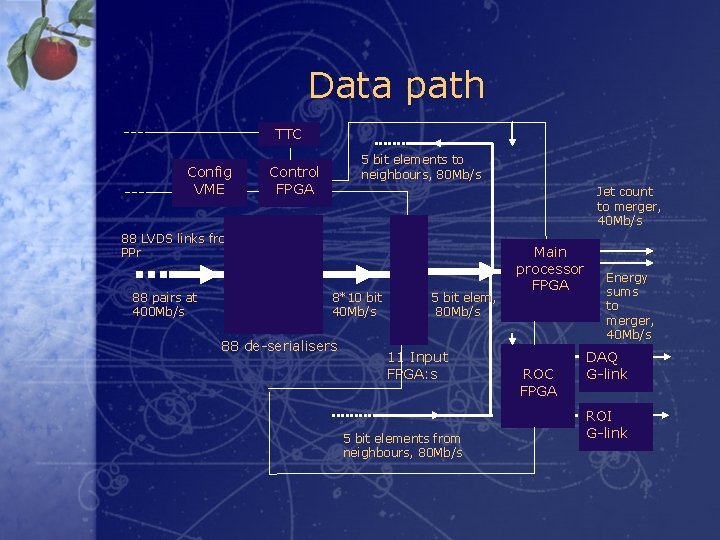

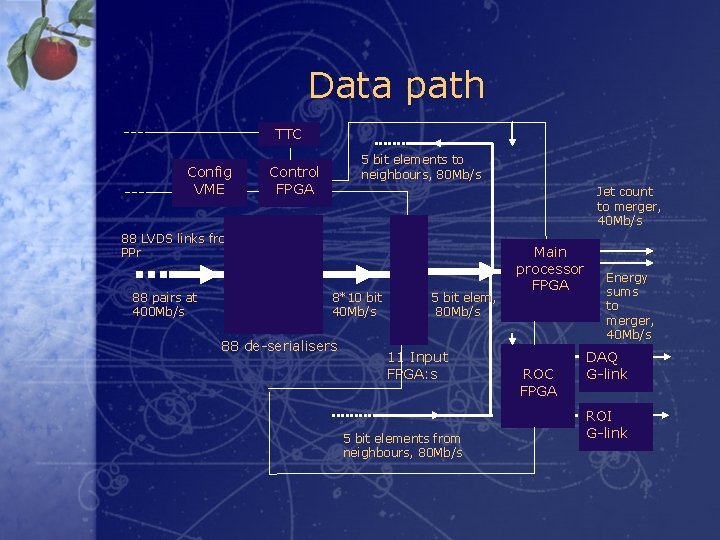

Data path TTC Config VME 5 bit elements to neighbours, 80 Mb/s Control FPGA Jet count to merger, 40 Mb/s 88 LVDS links from PPr 88 pairs at 400 Mb/s 8*10 bit 40 Mb/s 88 de-serialisers 5 bit elem, 80 Mb/s 11 Input FPGA: s 5 bit elements from neighbours, 80 Mb/s Main processor FPGA ROC FPGA Energy sums to merger, 40 Mb/s DAQ G-link ROI G-link

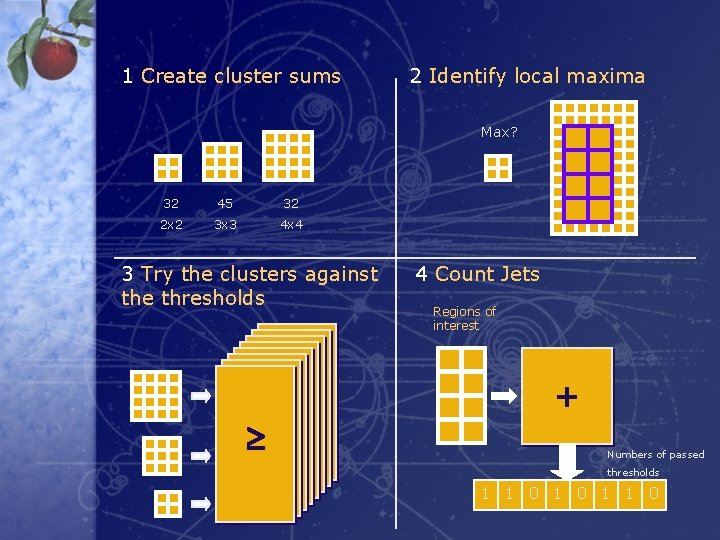

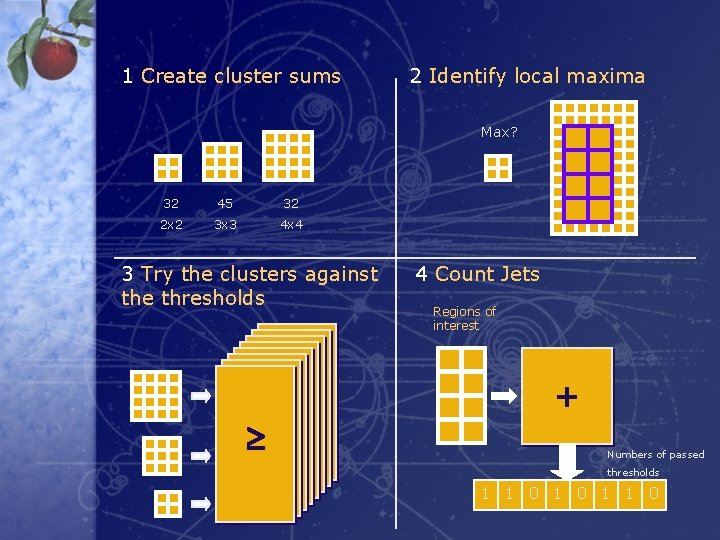

1 Create cluster sums 2 Identify local maxima Max? 32 45 32 2 x 2 3 x 3 4 x 4 3 Try the clusters against the thresholds 4 Count Jets Regions of interest + Numbers of passed thresholds 1 1 0

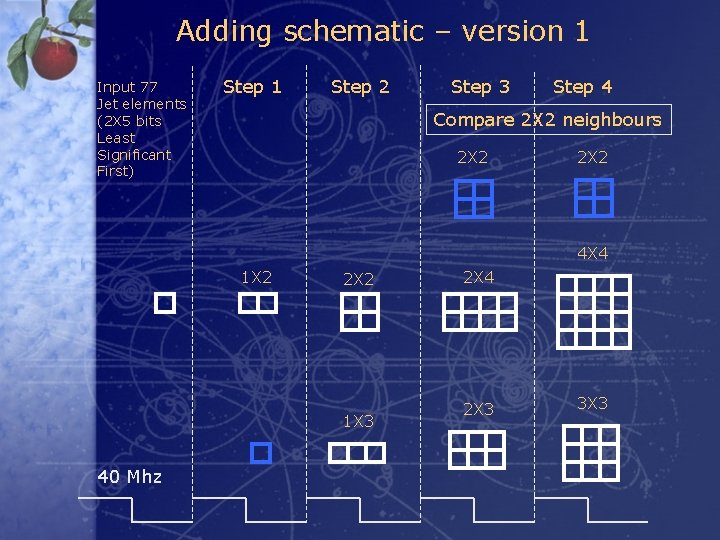

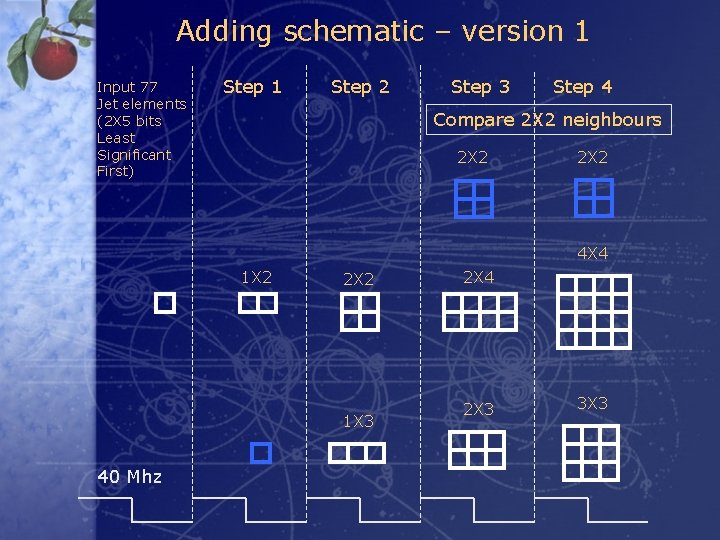

Adding schematic – version 1 Input 77 Jet elements (2 X 5 bits Least Significant First) Step 1 Step 2 Step 3 Step 4 Compare 2 X 2 neighbours 2 X 2 4 X 4 1 X 2 2 X 2 1 X 3 40 Mhz 2 X 4 2 X 3 3 X 3

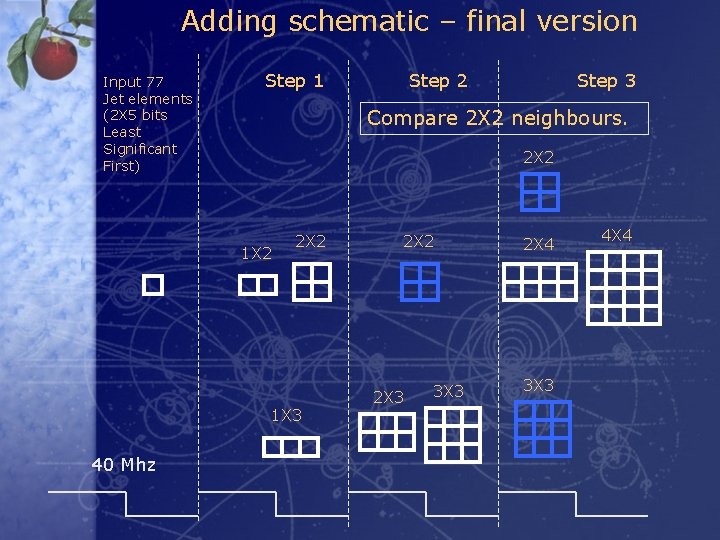

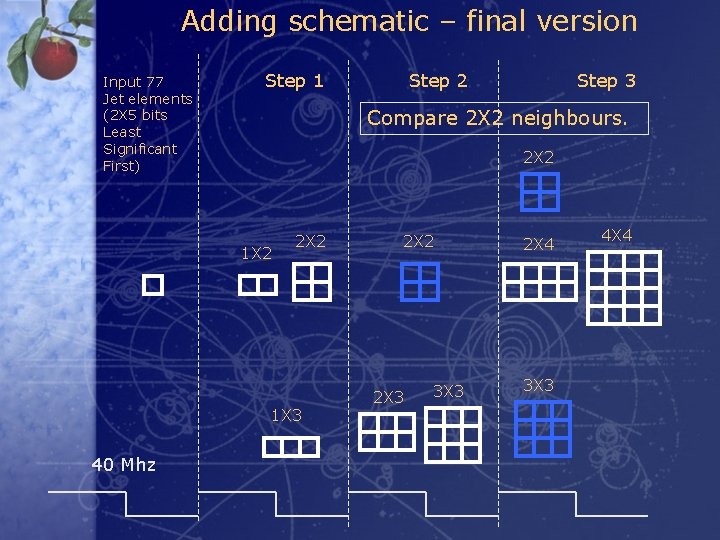

Adding schematic – final version Input 77 Jet elements (2 X 5 bits Least Significant First) Step 1 Step 3 Compare 2 X 2 neighbours. 2 X 2 1 X 2 2 X 2 1 X 3 40 Mhz Step 2 2 X 3 3 X 3 2 X 4 3 X 3 4 X 4

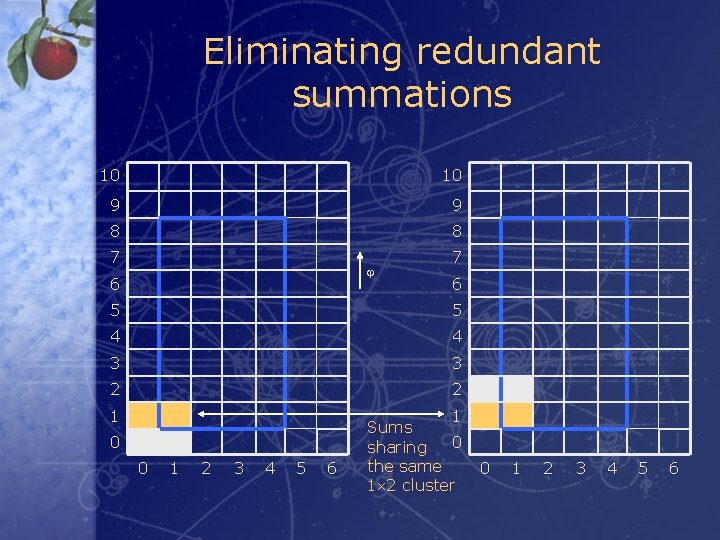

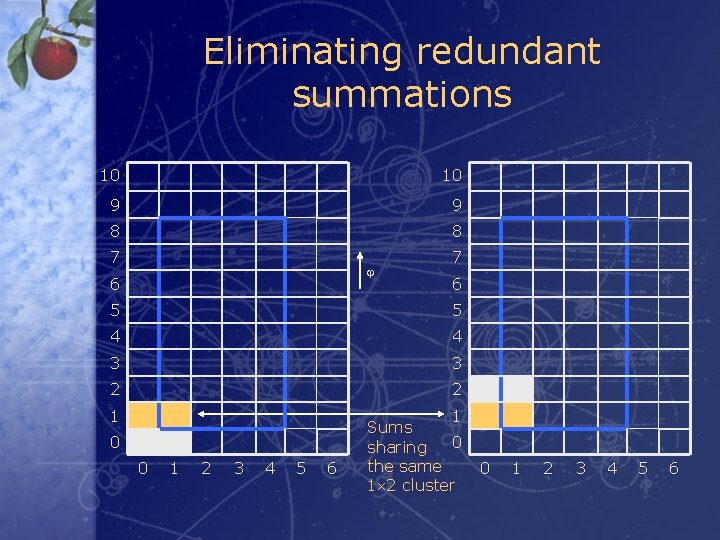

Eliminating redundant summations 10 10 9 9 8 8 7 7 6 6 5 5 4 4 3 3 2 2 1 1 Sums 0 sharing the same 1 2 cluster 0 0 1 2 3 4 5 6

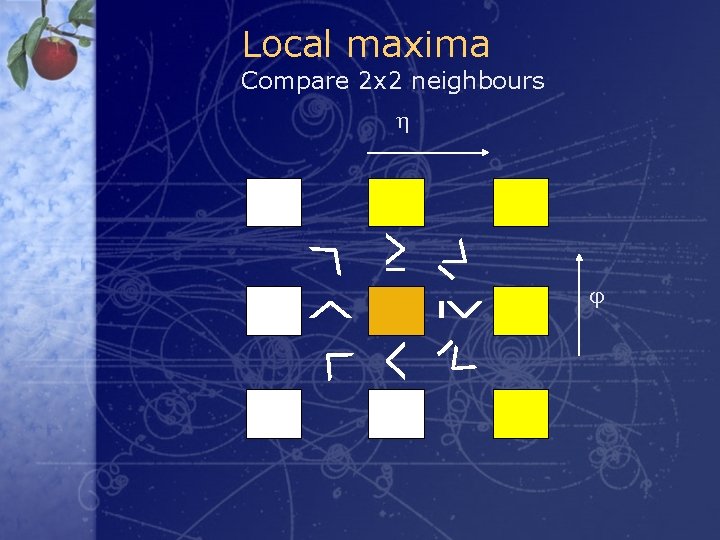

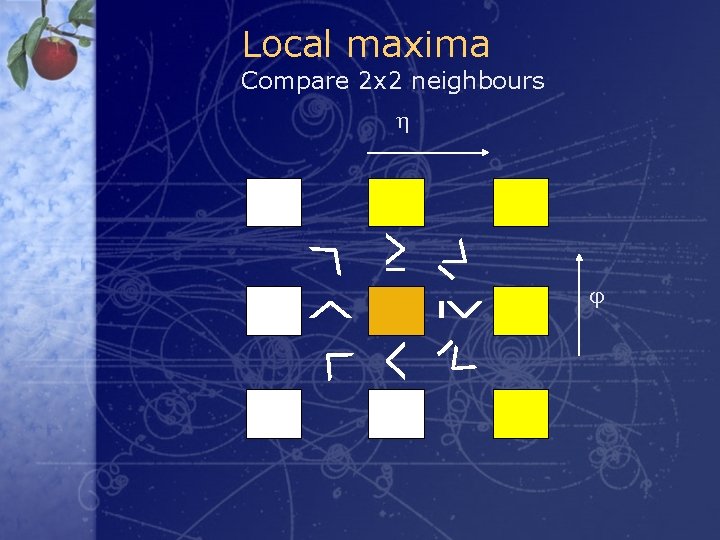

Local maxima Compare 2 x 2 neighbours

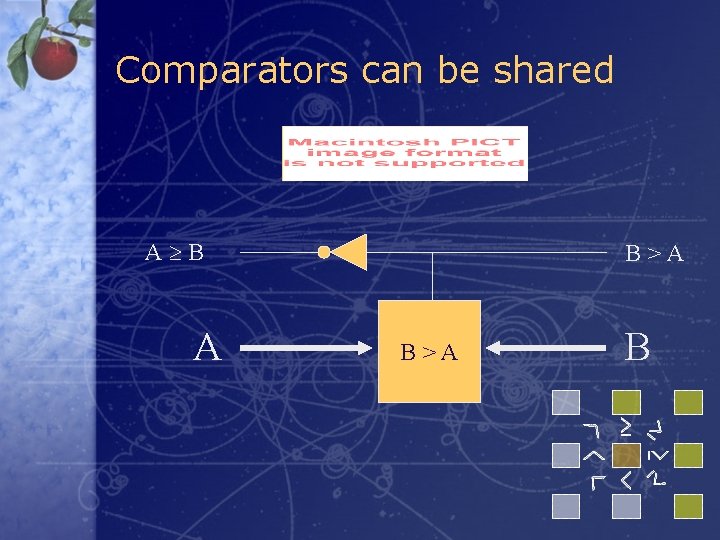

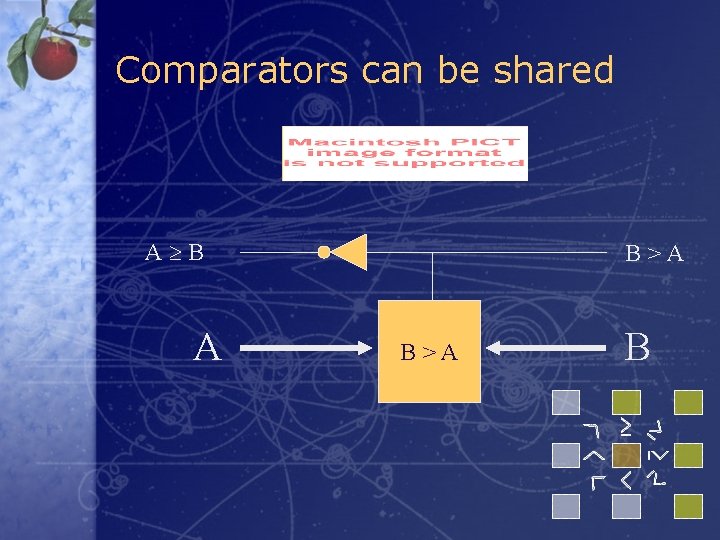

Comparators can be shared A B>A B

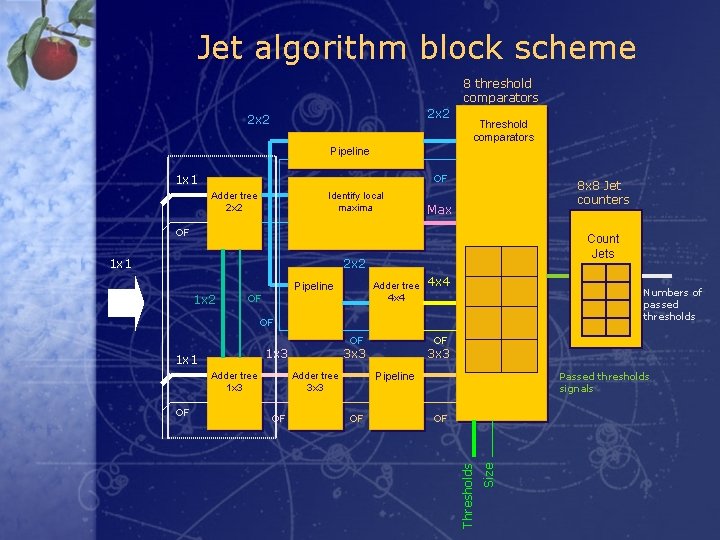

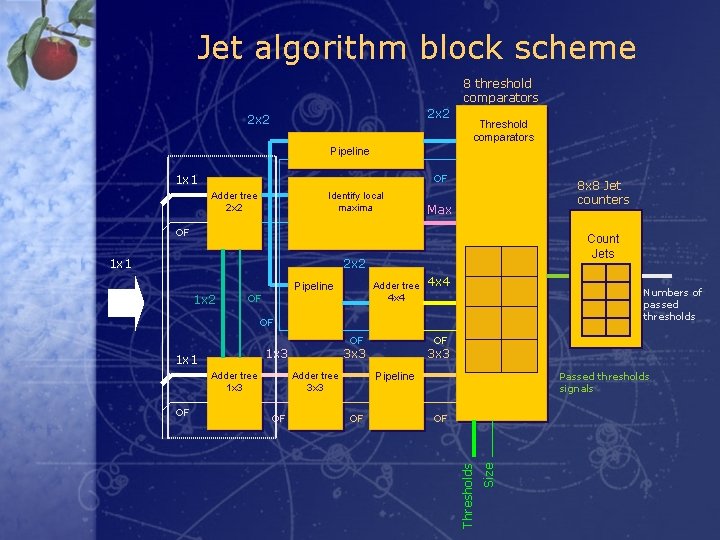

Jet algorithm block scheme 8 threshold comparators 2 x 2 Threshold comparators Pipeline 1 x 1 OF Adder tree 2 x 2 Identify local maxima 8 x 8 Jet counters Max OF 1 x 1 Count Jets 2 x 2 1 x 2 Adder tree 4 x 4 Pipeline OF 4 x 4 Numbers of passed thresholds OF 3 x 3 Adder tree 3 x 3 OF 3 x 3 Passed thresholds signals Pipeline OF OF Size Adder tree 1 x 3 OF Thresholds 1 x 3 1 x 1 OF OF

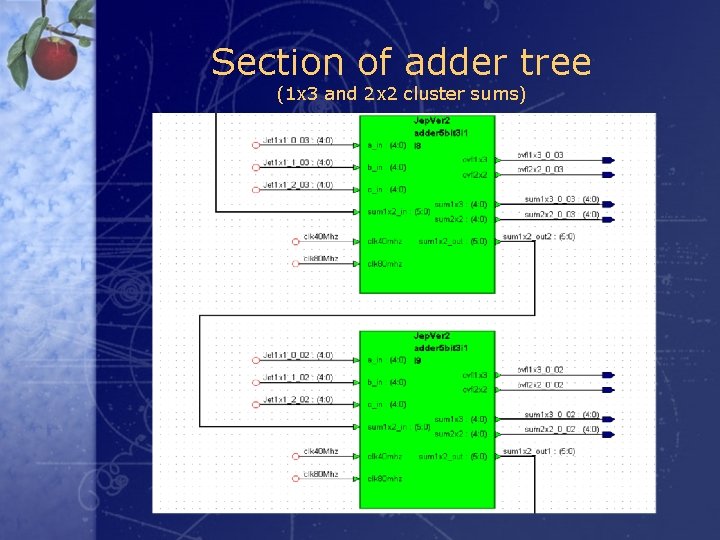

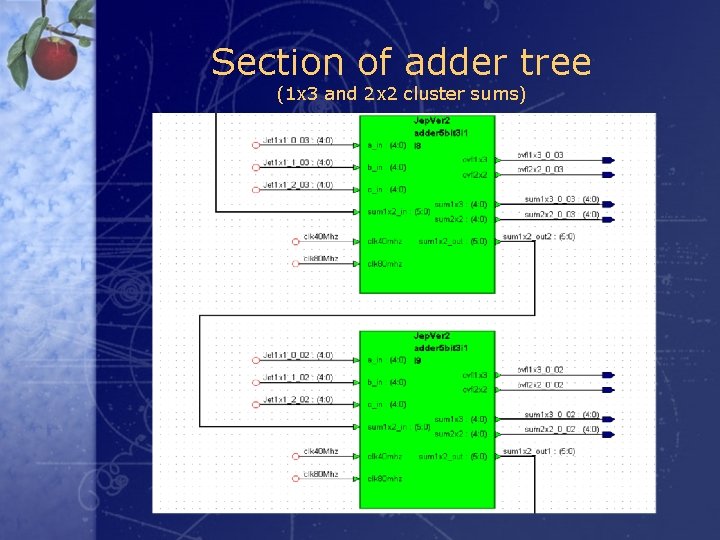

Section of adder tree (1 x 3 and 2 x 2 cluster sums)

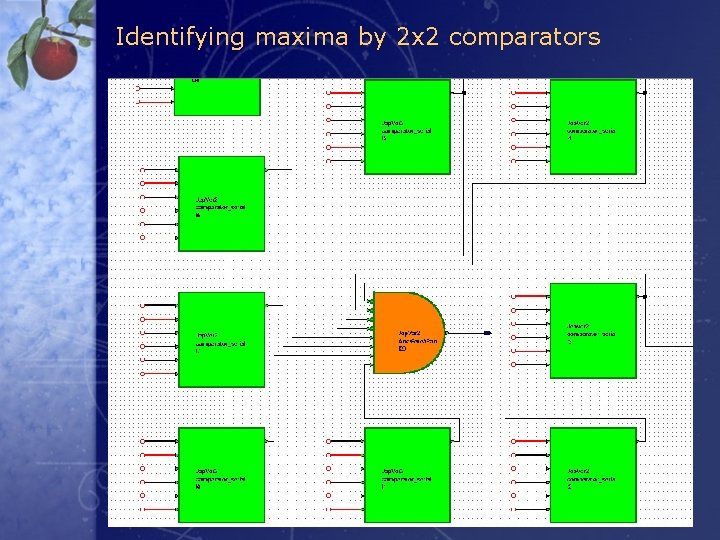

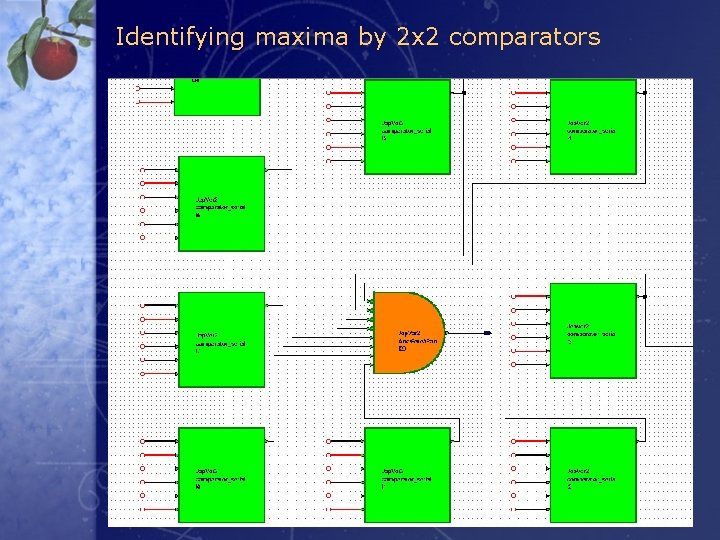

Identifying maxima by 2 x 2 comparators

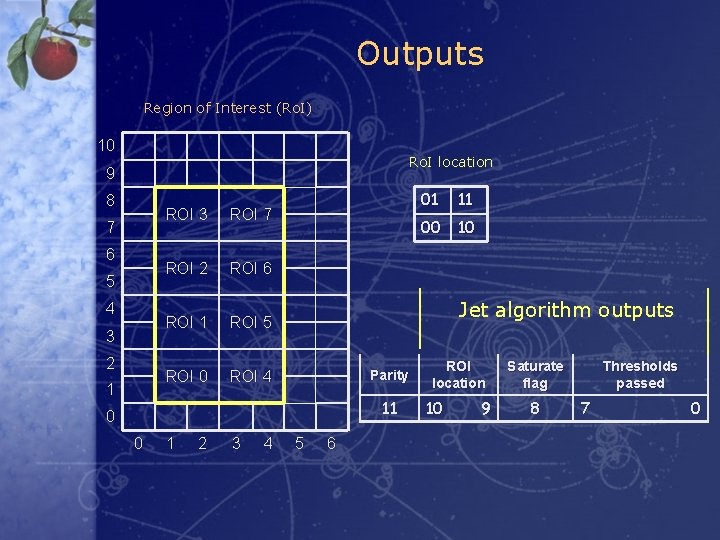

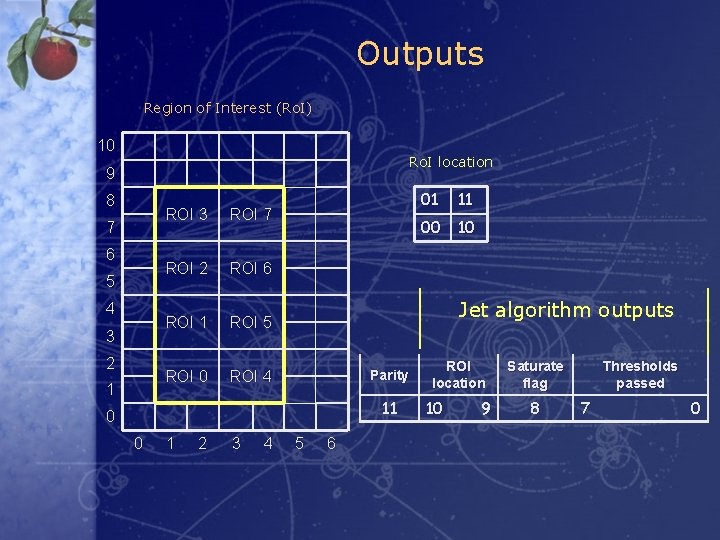

Outputs Region of Interest (Ro. I) 10 Ro. I location 9 8 7 6 5 4 3 2 1 ROI 3 ROI 7 ROI 2 ROI 6 ROI 1 ROI 5 ROI 0 ROI 4 Parity 11 1 2 3 4 11 00 10 Jet algorithm outputs 0 0 01 5 6 ROI location 10 9 Saturate flag 8 Thresholds passed 7 0

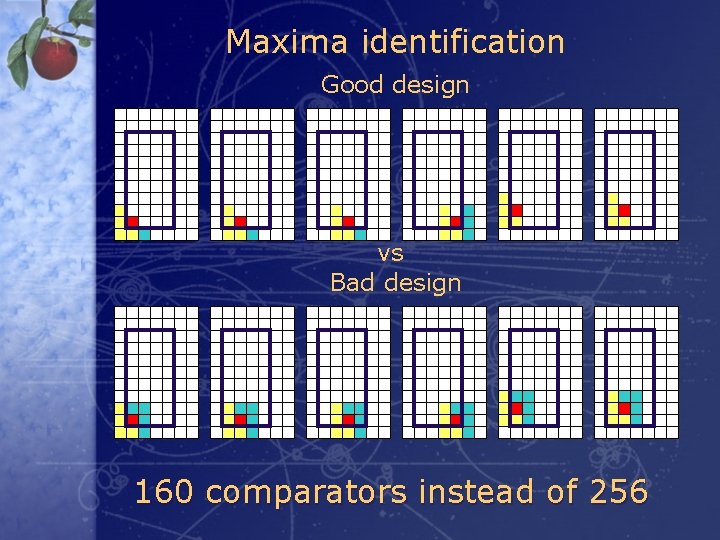

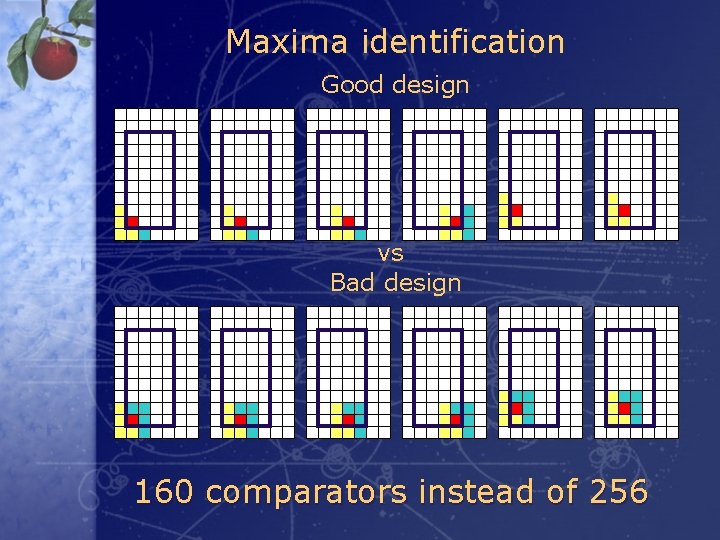

Maxima identification Good design vs Bad design 160 comparators instead of 256

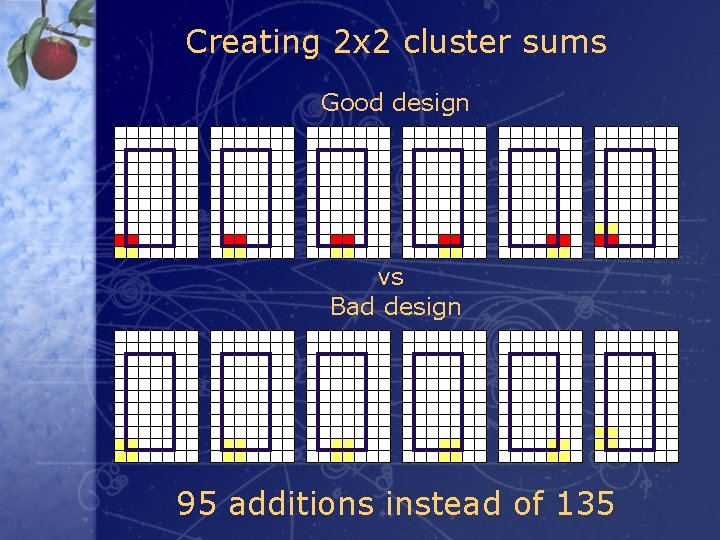

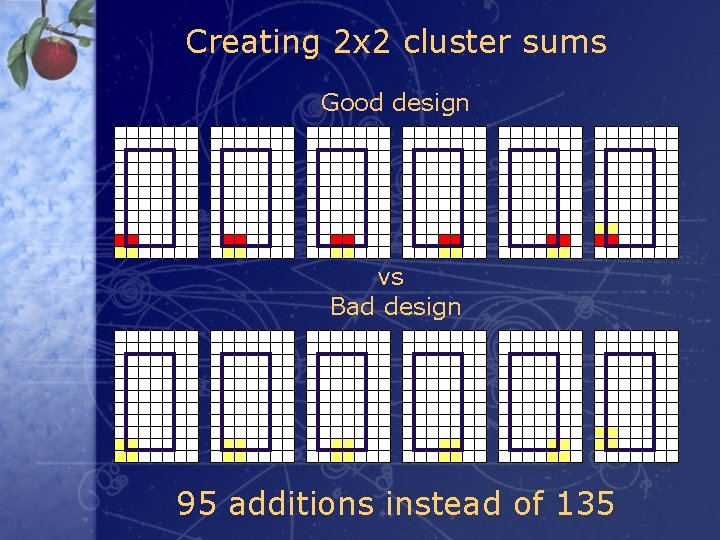

Creating 2 x 2 cluster sums Good design vs Bad design 95 additions instead of 135

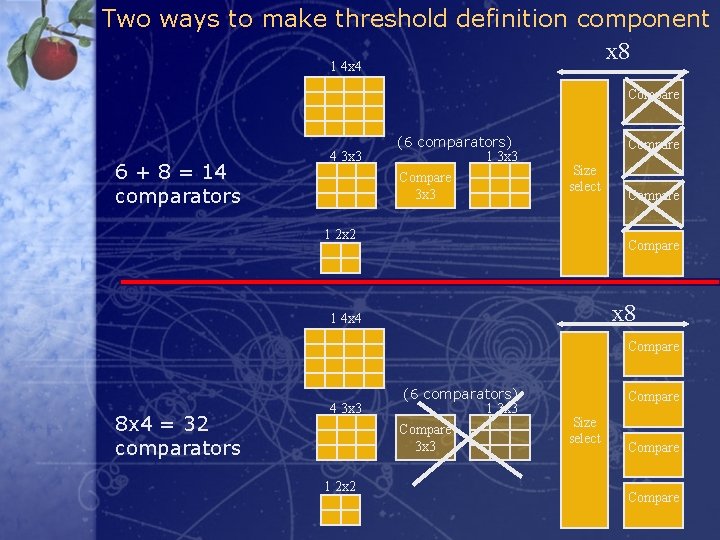

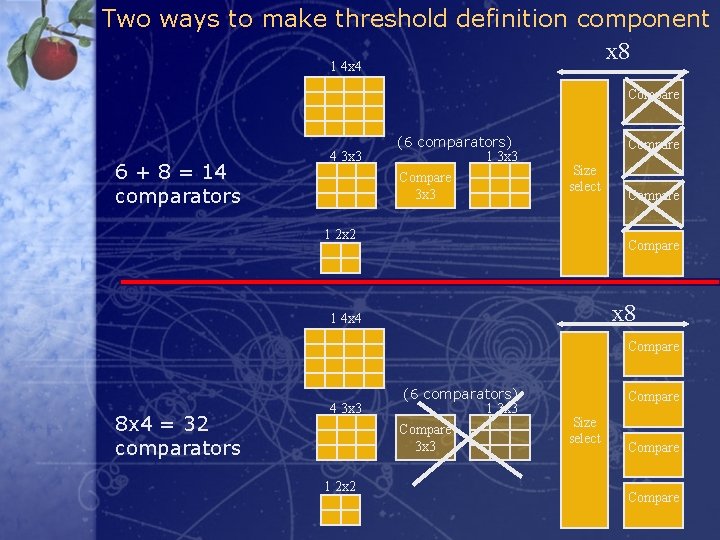

Two ways to make threshold definition component x 8 1 4 x 4 Compare 6 + 8 = 14 comparators 4 3 x 3 (6 comparators) 1 3 x 3 Compare Size select 1 2 x 2 Compare x 8 1 4 x 4 Compare 8 x 4 = 32 comparators 4 3 x 3 1 2 x 2 (6 comparators) 1 3 x 3 Compare Size select Compare

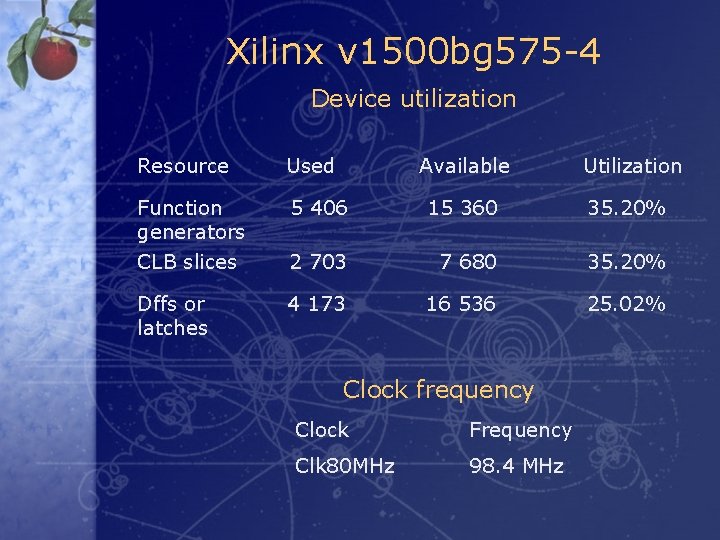

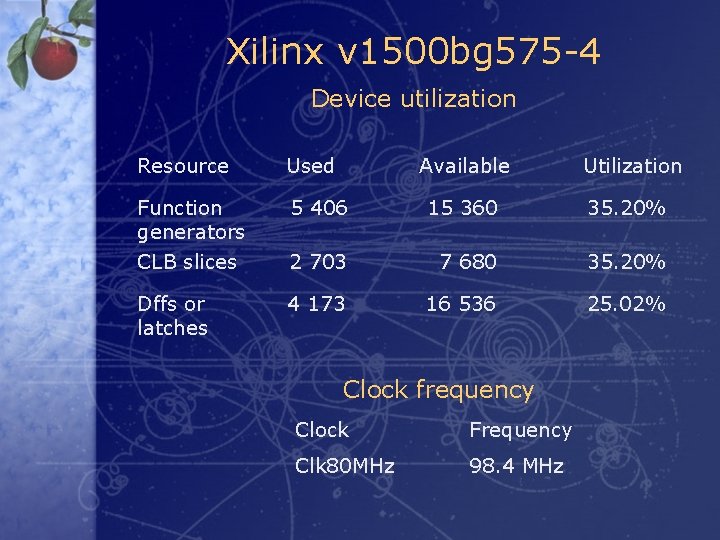

Xilinx v 1500 bg 575 -4 Device utilization Resource Used Function generators CLB slices Dffs or latches Available Utilization 5 406 15 360 35. 20% 2 703 7 680 35. 20% 4 173 16 536 25. 02% Clock frequency Clock Frequency Clk 80 MHz 98. 4 MHz

World Wide Web link The VHDL code together with a C++ test code are available at: http: //www. sysf. physto. se/atlas/jet