ATLAS Level1 Calorimeter Trigger Architecture Brief Tour of

ATLAS: Level-1 Calorimeter Trigger Architecture Brief Tour of Modules Laboratory Tests Combined Beam Test 2004 o o o May 18 th, 2005 Collaboration: Birmingham, Heidelberg, Mainz, QMUL, RAL, Stockholm 1

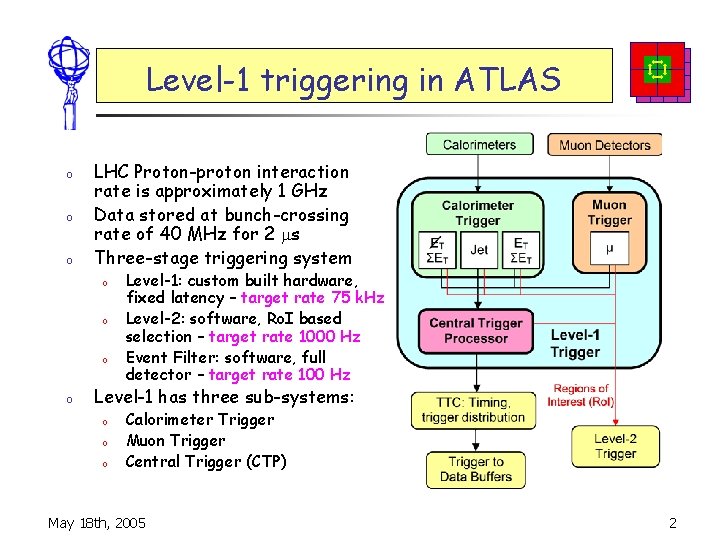

Level-1 triggering in ATLAS o o o LHC Proton-proton interaction rate is approximately 1 GHz Data stored at bunch-crossing rate of 40 MHz for 2 ms Three-stage triggering system o o Level-1: custom built hardware, fixed latency – target rate 75 k. Hz Level-2: software, Ro. I based selection – target rate 1000 Hz Event Filter: software, full detector – target rate 100 Hz Level-1 has three sub-systems: o o o Calorimeter Trigger Muon Trigger Central Trigger (CTP) May 18 th, 2005 2

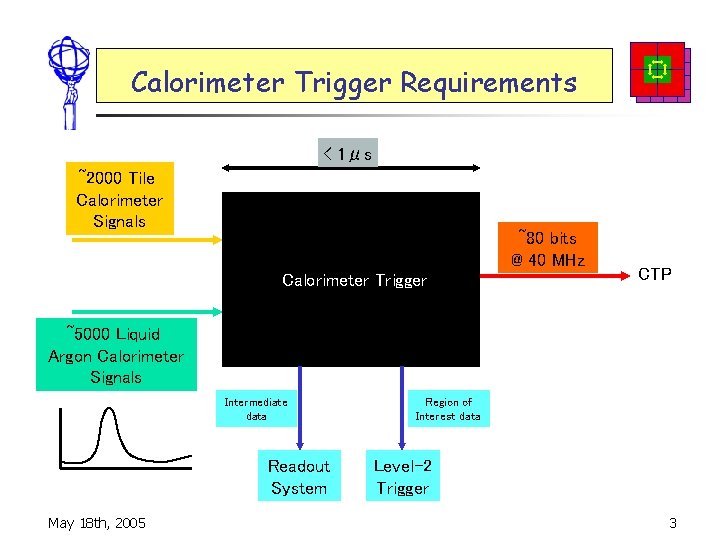

Calorimeter Trigger Requirements < 1μs ~2000 Tile Calorimeter Signals ~80 bits @ 40 MHz Calorimeter Trigger CTP ~5000 Liquid Argon Calorimeter Signals Intermediate data Readout System May 18 th, 2005 Region of Interest data Level-2 Trigger 3

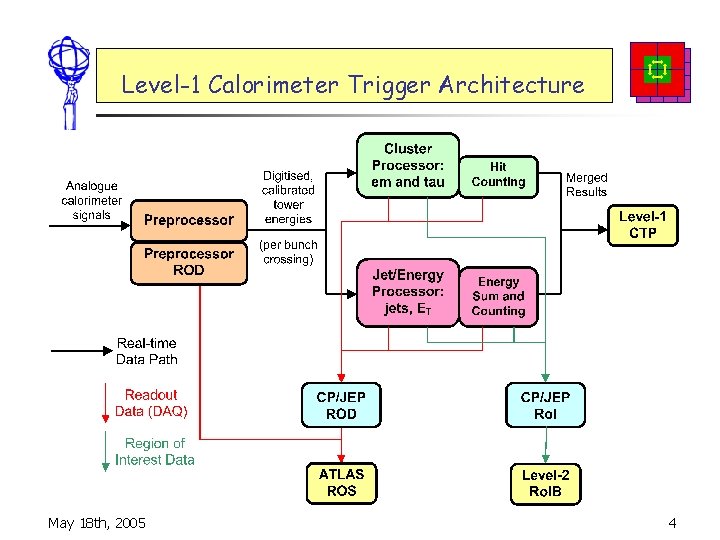

Level-1 Calorimeter Trigger Architecture May 18 th, 2005 4

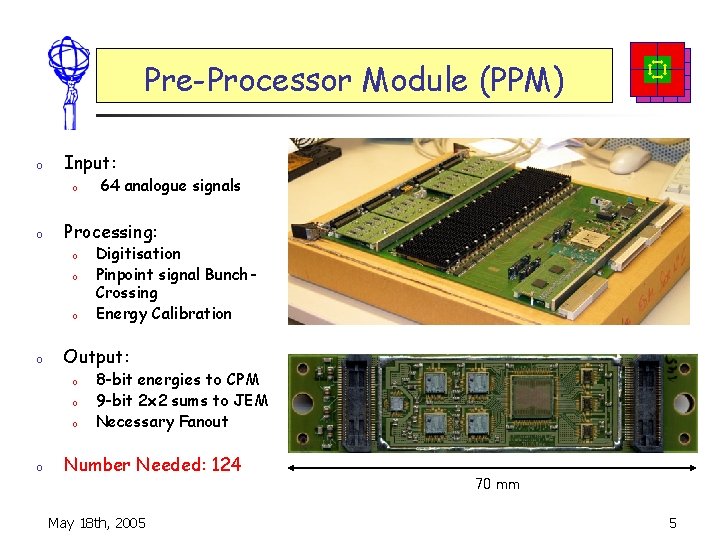

Pre-Processor Module (PPM) o Input: o o Processing: o o Digitisation Pinpoint signal Bunch. Crossing Energy Calibration Output: o o 64 analogue signals 8 -bit energies to CPM 9 -bit 2 x 2 sums to JEM Necessary Fanout Number Needed: 124 May 18 th, 2005 70 mm 5

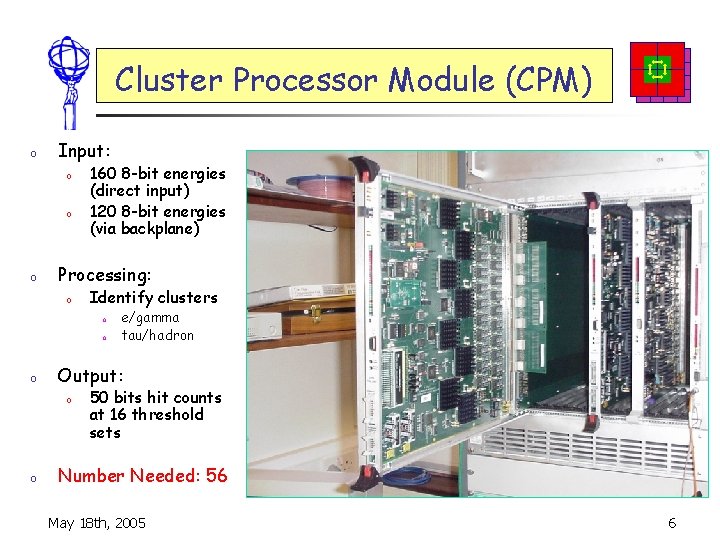

Cluster Processor Module (CPM) o Input: o o o 160 8 -bit energies (direct input) 120 8 -bit energies (via backplane) Processing: o Identify clusters o o o Output: o o e/gamma tau/hadron 50 bits hit counts at 16 threshold sets Number Needed: 56 May 18 th, 2005 6

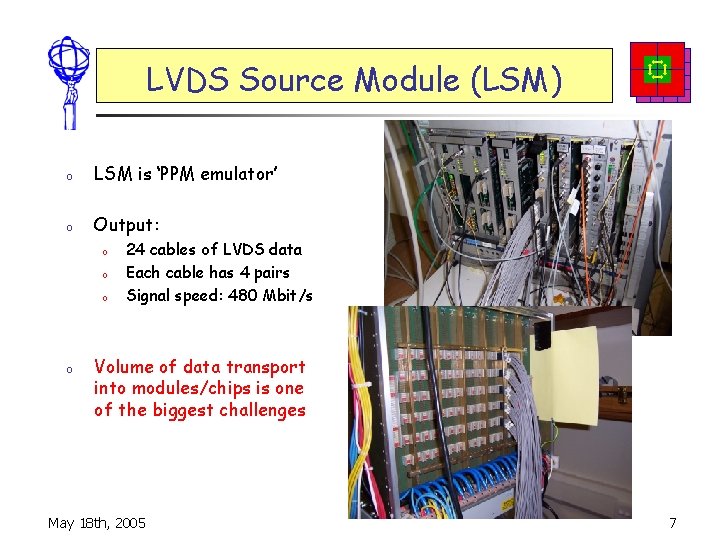

LVDS Source Module (LSM) o LSM is ‘PPM emulator’ o Output: o o 24 cables of LVDS data Each cable has 4 pairs Signal speed: 480 Mbit/s Volume of data transport into modules/chips is one of the biggest challenges May 18 th, 2005 7

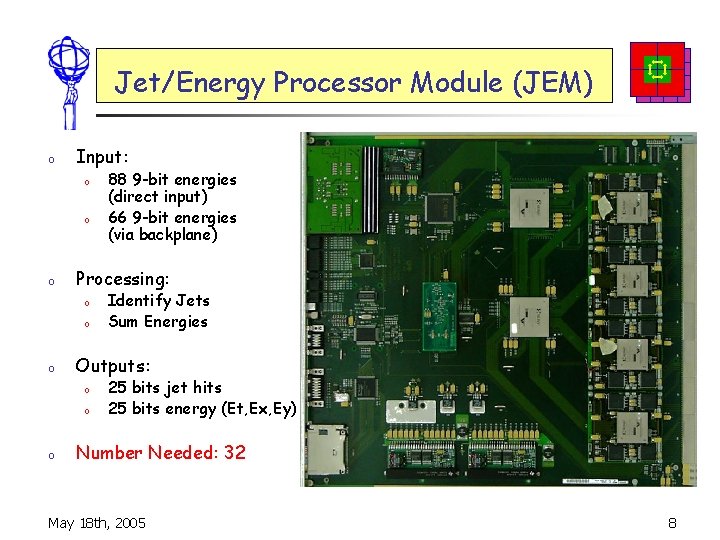

Jet/Energy Processor Module (JEM) o Input: o o o Processing: o o o Identify Jets Sum Energies Outputs: o o o 88 9 -bit energies (direct input) 66 9 -bit energies (via backplane) 25 bits jet hits 25 bits energy (Et, Ex, Ey) Number Needed: 32 May 18 th, 2005 8

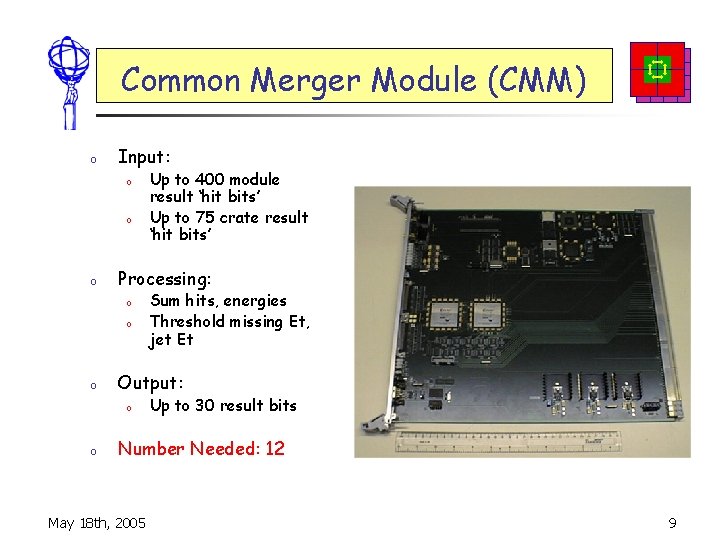

Common Merger Module (CMM) o Input: o o o Processing: o o o Sum hits, energies Threshold missing Et, jet Et Output: o o Up to 400 module result ‘hit bits’ Up to 75 crate result ‘hit bits’ Up to 30 result bits Number Needed: 12 May 18 th, 2005 9

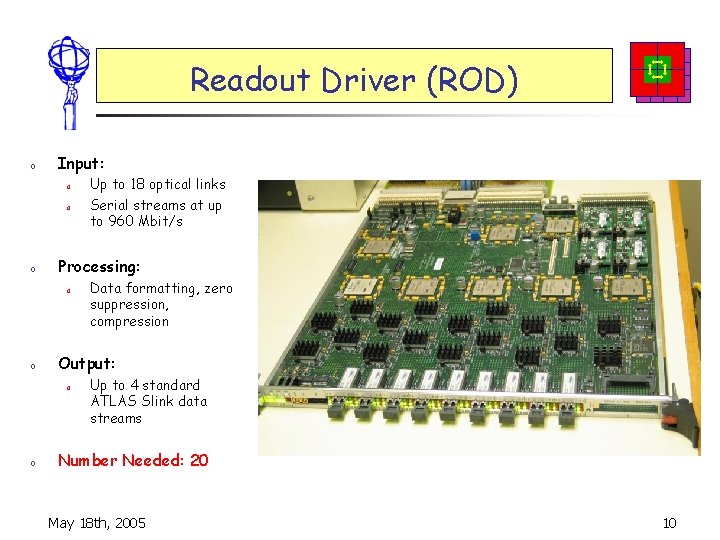

Readout Driver (ROD) o Input: o o o Processing: o o Data formatting, zero suppression, compression Output: o o Up to 18 optical links Serial streams at up to 960 Mbit/s Up to 4 standard ATLAS Slink data streams Number Needed: 20 May 18 th, 2005 10

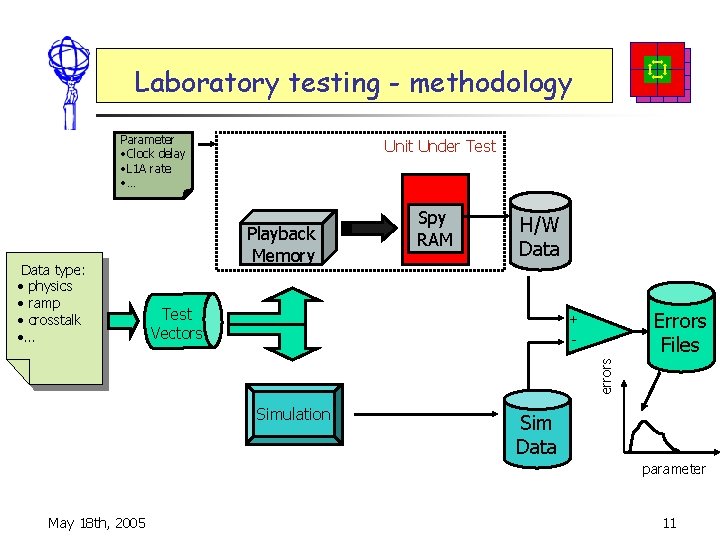

Laboratory testing - methodology Parameter • Clock delay • L 1 A rate • … Playback Memory Spy RAM H/W Data Test Vectors Errors Files + errors Data type: • physics • ramp • crosstalk • … Unit Under Test Simulation Sim Data parameter May 18 th, 2005 11

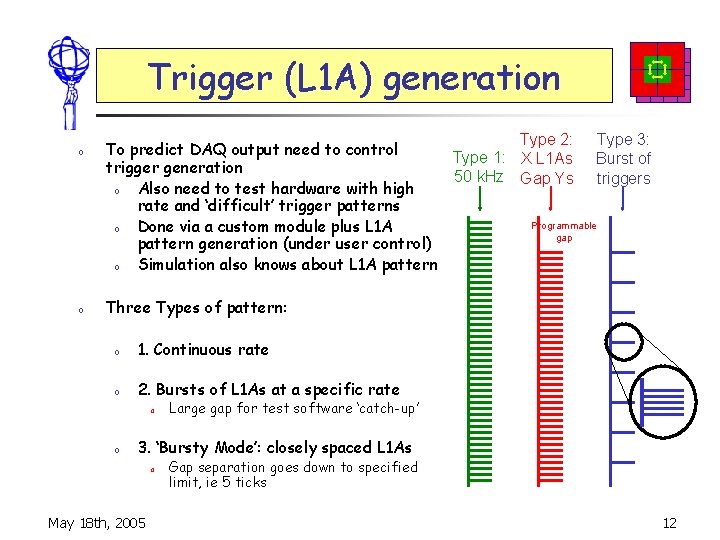

Trigger (L 1 A) generation o o Type 2: Type 3: To predict DAQ output need to control Type 1: X L 1 As Burst of trigger generation 50 k. Hz Gap Ys triggers o Also need to test hardware with high rate and ‘difficult’ trigger patterns Programmable o Done via a custom module plus L 1 A gap pattern generation (under user control) o Simulation also knows about L 1 A pattern Three Types of pattern: o 1. Continuous rate o 2. Bursts of L 1 As at a specific rate o o Large gap for test software ‘catch-up’ 3. ‘Bursty Mode’: closely spaced L 1 As o May 18 th, 2005 Gap separation goes down to specified limit, ie 5 ticks 12

What to test? o High speed link stability and performance o o Use data integrity to establish good timing windows High statistic made measurements in real-time o o o Algorithm correctness o o Parity checking Dedicated firmware loads Use specially designed test-vectors and physics Data formatting o May 18 th, 2005 DAQ and Ro. I data must conform to offline expectations 13

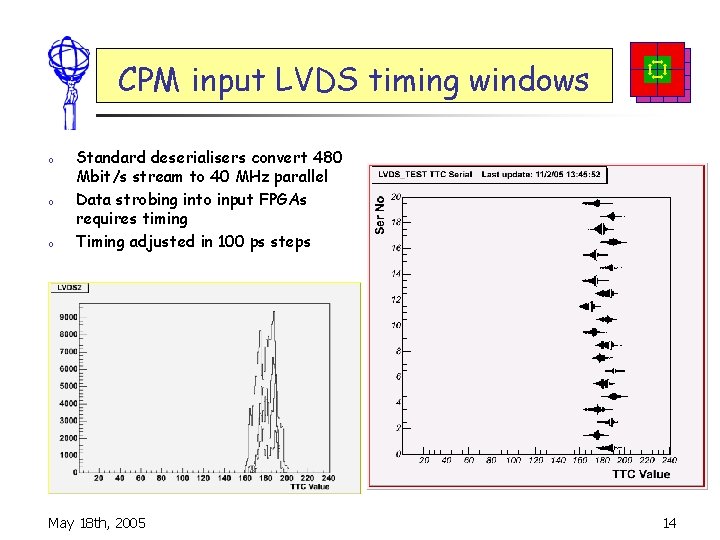

CPM input LVDS timing windows o o o Standard deserialisers convert 480 Mbit/s stream to 40 MHz parallel Data strobing into input FPGAs requires timing Timing adjusted in 100 ps steps May 18 th, 2005 14

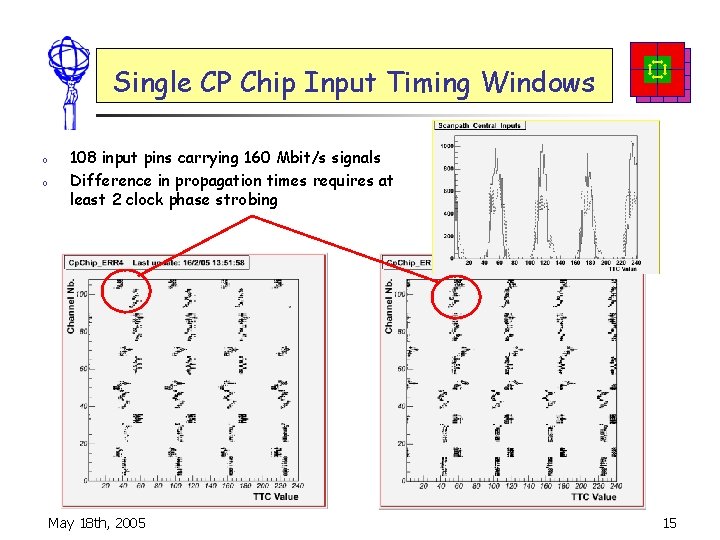

Single CP Chip Input Timing Windows o o 108 input pins carrying 160 Mbit/s signals Difference in propagation times requires at least 2 clock phase strobing May 18 th, 2005 15

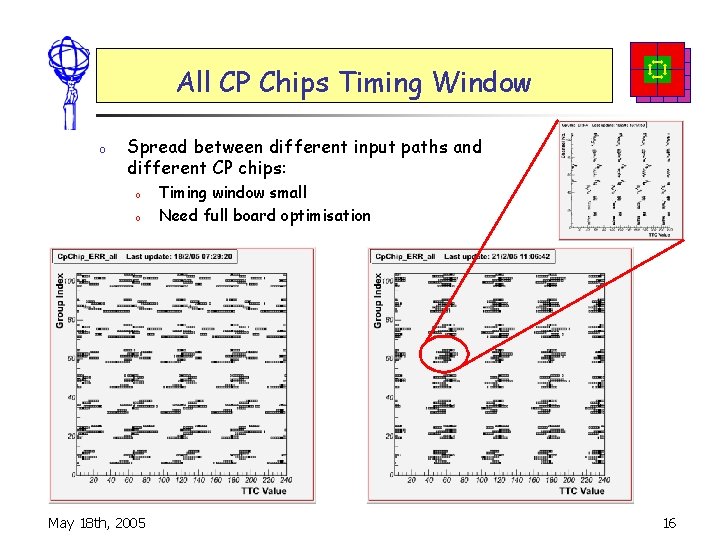

All CP Chips Timing Window o Spread between different input paths and different CP chips: o o May 18 th, 2005 Timing window small Need full board optimisation 16

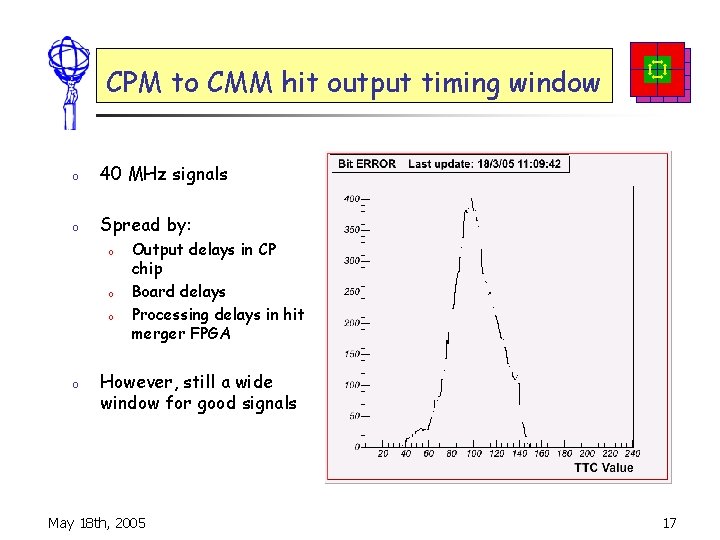

CPM to CMM hit output timing window o 40 MHz signals o Spread by: o o Output delays in CP chip Board delays Processing delays in hit merger FPGA However, still a wide window for good signals May 18 th, 2005 17

ATLAS Combined Testbeam 2004 o o o Essentially all detectors present At H 8, amongst other things o 4 slices of LAr Barrel o 3 slices of Tile Calorimeter Level-1 Calorimeter Trigger present September to mid-October o o o 1 week of 25 ns running in October Triggered successfully for part of the time by L 1 Calo! A full slice (sliver) through the trigger system o o May 18 th, 2005 Approx 1 module of each type All final full-spec modules except for ROD 18

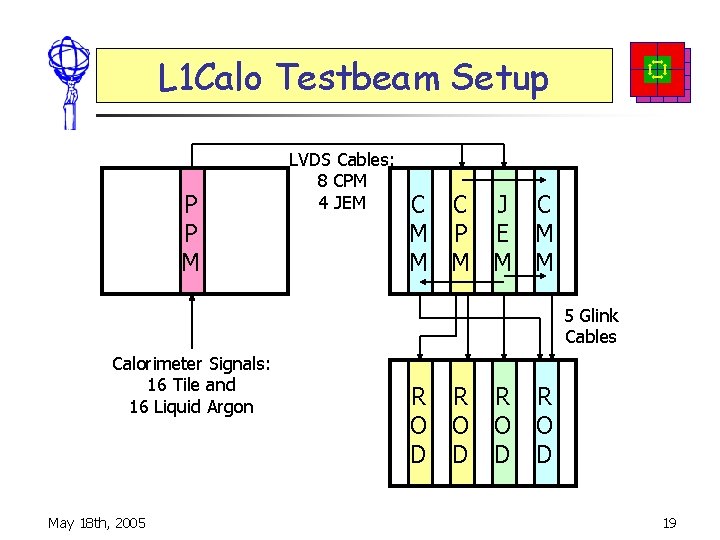

L 1 Calo Testbeam Setup P P M LVDS Cables: 8 CPM 4 JEM C C J C M P E M M M 5 Glink Cables Calorimeter Signals: 16 Tile and 16 Liquid Argon May 18 th, 2005 R O D 19

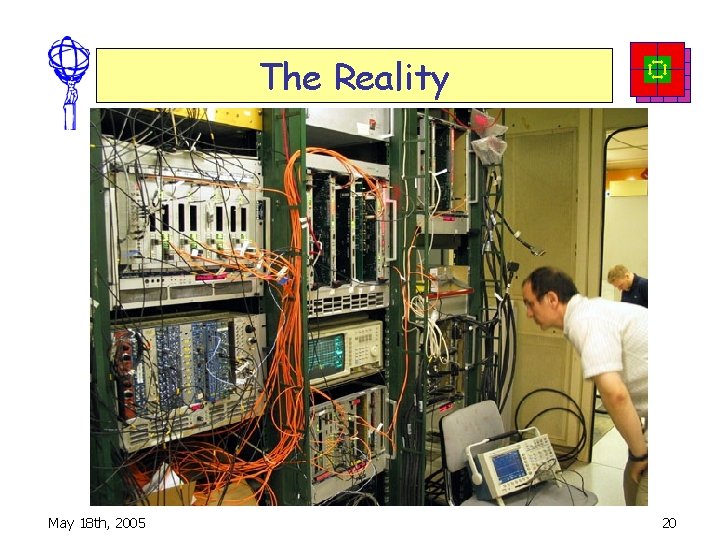

The Reality May 18 th, 2005 20

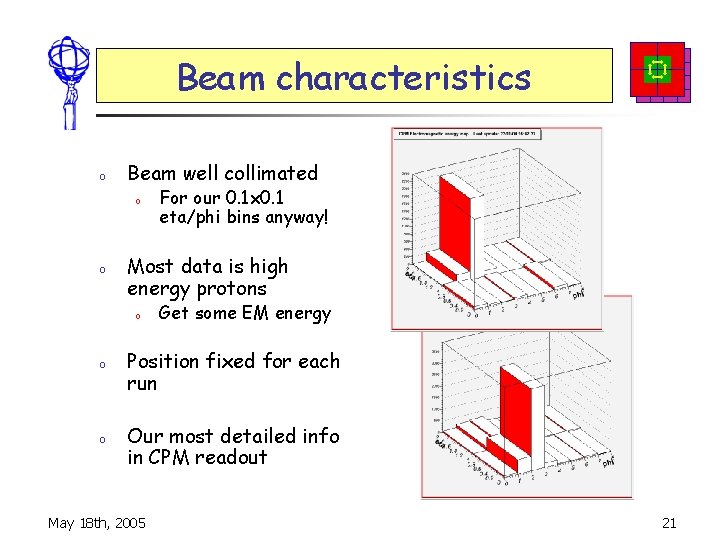

Beam characteristics o Beam well collimated o o Most data is high energy protons o o o For our 0. 1 x 0. 1 eta/phi bins anyway! Get some EM energy Position fixed for each run Our most detailed info in CPM readout May 18 th, 2005 21

Checks on Test Beam data o Internal Consistency checks o o o Assume CPM data is correct Is all other data (energies, hits etc) consistent? Performed in ~500, 000 events o o o Only minor problems, identified as firmware features No evidence of data integrity problems Comparisons with Calorimeters o o Our hardware was not well timed/calibrated Nevertheless, a good correlation was seen o May 18 th, 2005 With some problems – pile-up? 22

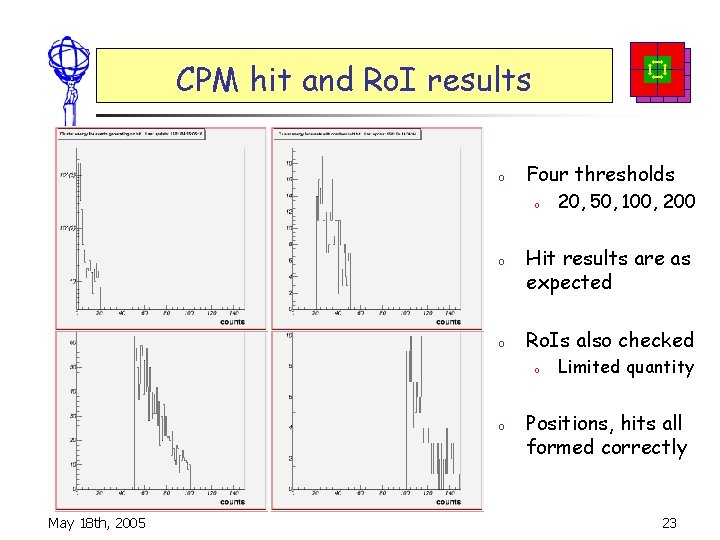

CPM hit and Ro. I results o Four thresholds o o o Hit results are as expected Ro. Is also checked o o May 18 th, 2005 20, 50, 100, 200 Limited quantity Positions, hits all formed correctly 23

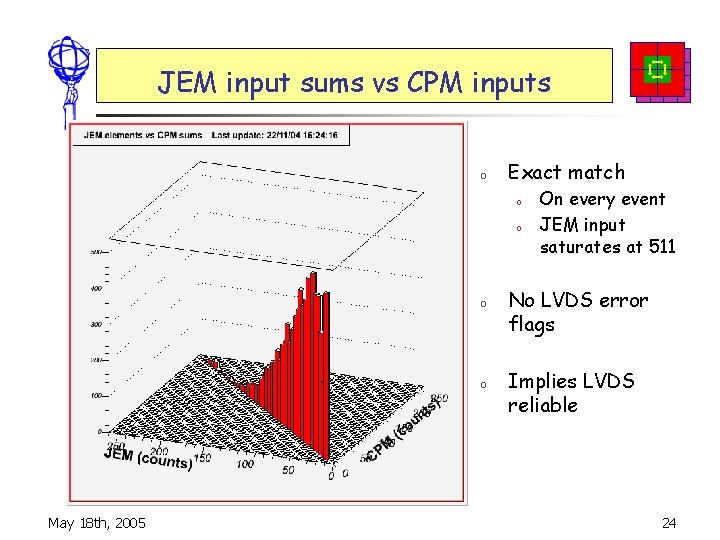

JEM input sums vs CPM inputs o Exact match o o May 18 th, 2005 On every event JEM input saturates at 511 No LVDS error flags Implies LVDS reliable 24

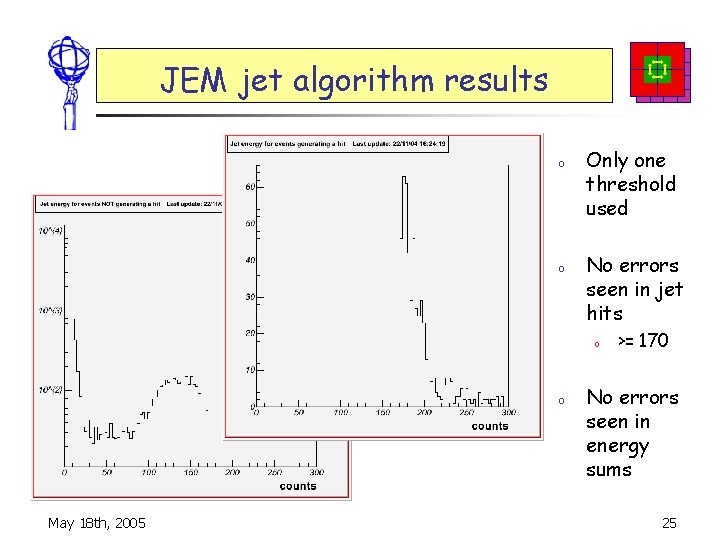

JEM jet algorithm results o o Only one threshold used No errors seen in jet hits o o May 18 th, 2005 >= 170 No errors seen in energy sums 25

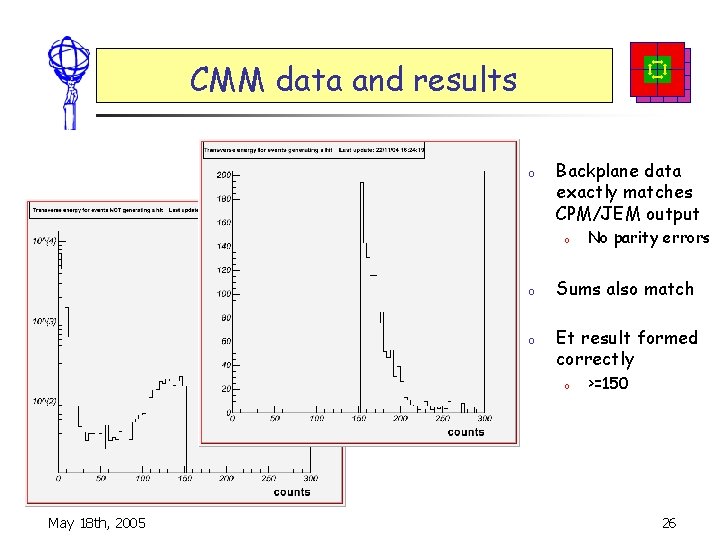

CMM data and results o Backplane data exactly matches CPM/JEM output o o o Sums also match Et result formed correctly o May 18 th, 2005 No parity errors >=150 26

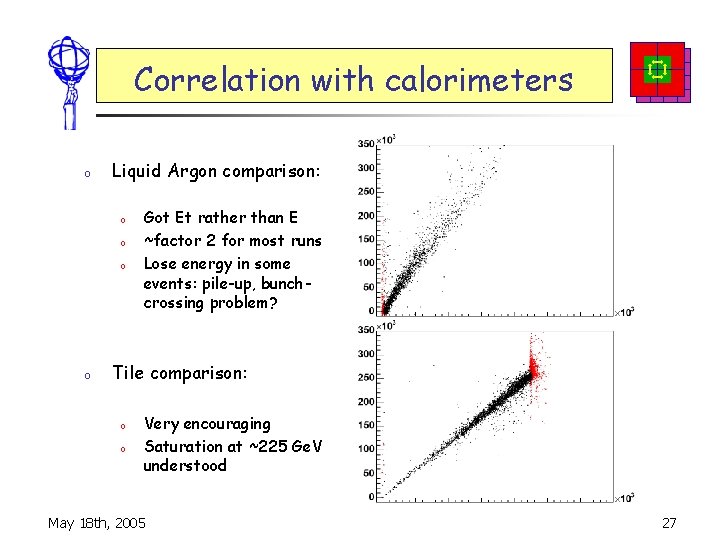

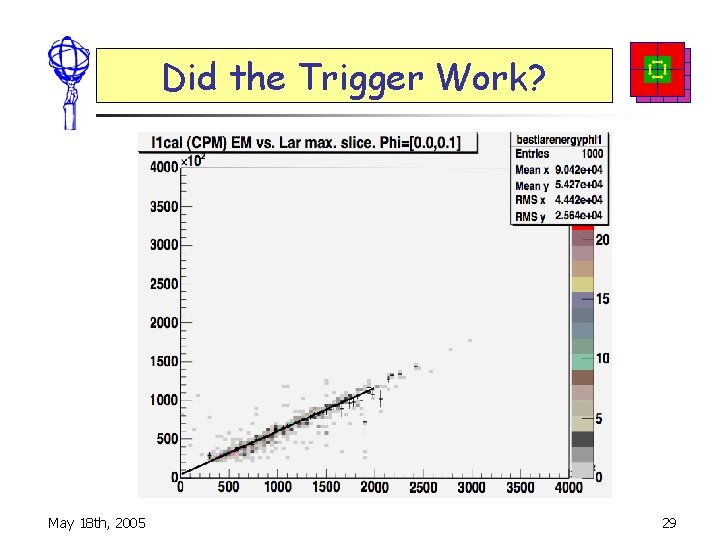

Correlation with calorimeters o Liquid Argon comparison: o o Got Et rather than E ~factor 2 for most runs Lose energy in some events: pile-up, bunchcrossing problem? Tile comparison: o o Very encouraging Saturation at ~225 Ge. V understood May 18 th, 2005 27

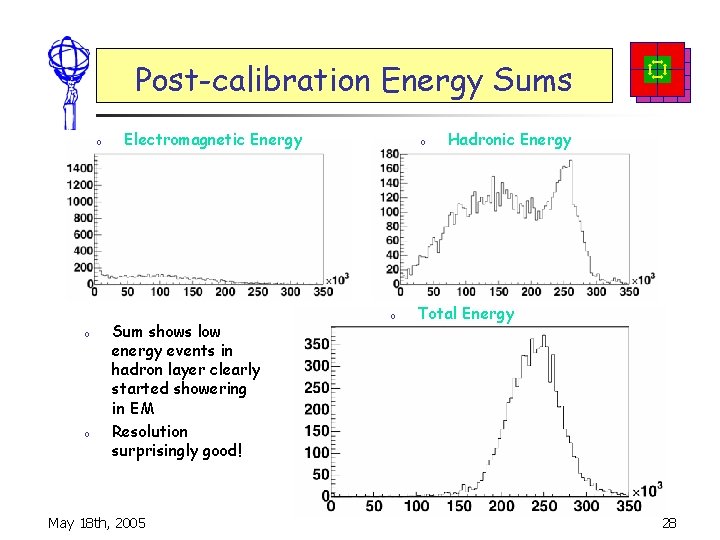

Post-calibration Energy Sums o o o Electromagnetic Energy Sum shows low energy events in hadron layer clearly started showering in EM Resolution surprisingly good! May 18 th, 2005 o o Hadronic Energy Total Energy 28

Did the Trigger Work? May 18 th, 2005 29

Conclusions o We have fully working prototypes of most modules o o o Long road ahead for production o o Some minor (understood) improvements needed Full spec (18 input rather than 4 input) ROD still under test Some hardware needed at CERN late-2005 Much infrastructure – eg cabling - to do in 2005 All hardware should be installed in early 2006 OK, so we’re probably going to be a bit late o (What’s new) May 18 th, 2005 30

- Slides: 30