ENCM 515 21 K Interrupts Theory and Practice

- Slides: 35

ENCM 515 -- 21 K Interrupts Theory and Practice M. R. Smith, Electrical and Computer Engineering, University of Calgary, Alberta, Canada smithmr @ ucalgary. ca 12/17/2021 1

To be tackled today n n n Review Subroutines and Interrupts Architectural Issues regarding 21 K interrupts Programming issues regarding 21 K interrupts 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 2

Subroutines and Interrupts n n Very similar in concept Very different in implementation Subroutines occur as part of your normal program flow. You tackle a certain task, written as a subroutine, at a certain location in your code. Time of starting plays no part in the design of a subroutine. 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 3

Subroutines are not interrupts! n Subroutines occur when the programmer wants them to occur n n Specific location in program code where called Specific location in code program where will return to Can prepare for when they will occur so can pass parameters to them Rules are -- save non-volatile registers 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 4

Interrupts are not subroutines n Interrupts occur when the interrupt wants to occur n n n NO Specific location in program code where called NO Specific location in program code where will return to Can’t prepare for when they will occur so can’t pass normal parameters to them -- need to use semaphores and messages instead Interrupts may not want to stop Interrupts may want to use volatile registers but subroutines already using them! 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 5

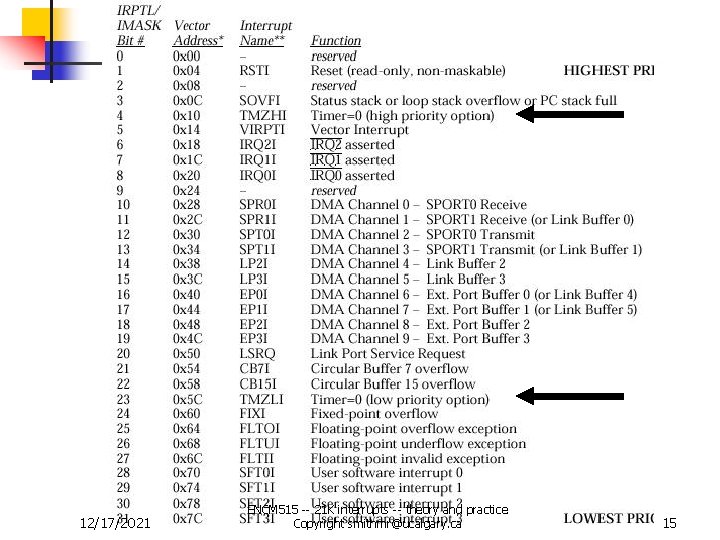

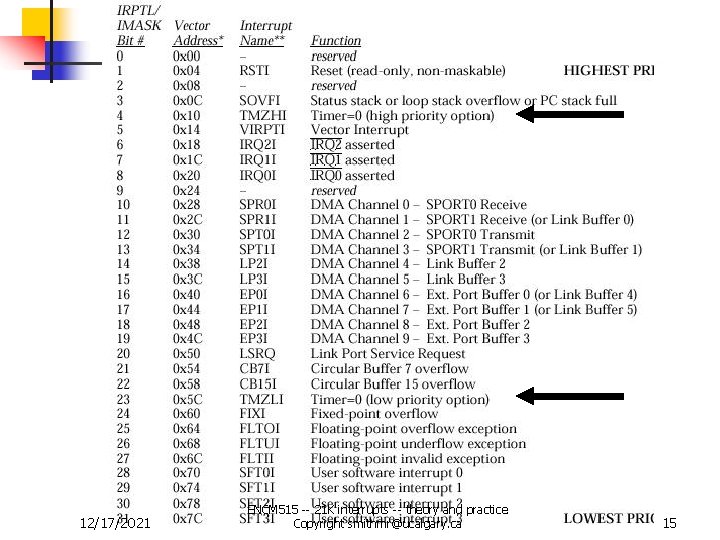

From Manual -- 3. 6 Interrupts n Interrupts from internal and external conditions -- priority level n n An interrupt forces a subroutine (sic) call to a predefined address -- the interrupt vector -unique Normal sequencing occurs after RTI 3 external interrupts (IRQ 2, 1, 0) level or edge triggered Internal -- arithmetic errors etc 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 6

Interrupt request is valid if n n n Not masked Interrupts globally enable (bit 12 in MODE 1 register) Higher priority request is not pending. Also can’t interrupt itself -- different from 68 k Valid requests invoke a IS sequence that branches to reserved address Reserved addresses spaced at 8 (sic) instruction intervals 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 7

Interrupt response must be fast n 68 K interrupt -- not too fast to get into n n n n Finish current instruction (8 cycles) Save next instruction address (12 cycles) Save status register (4 cycles at least) Look in “Vector Table” to find the starting address of the ISR routine (8 cycles to fetch) Fetch the first instruction in ISR Save registers Just as slow to get off! n Reverse of above 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 8

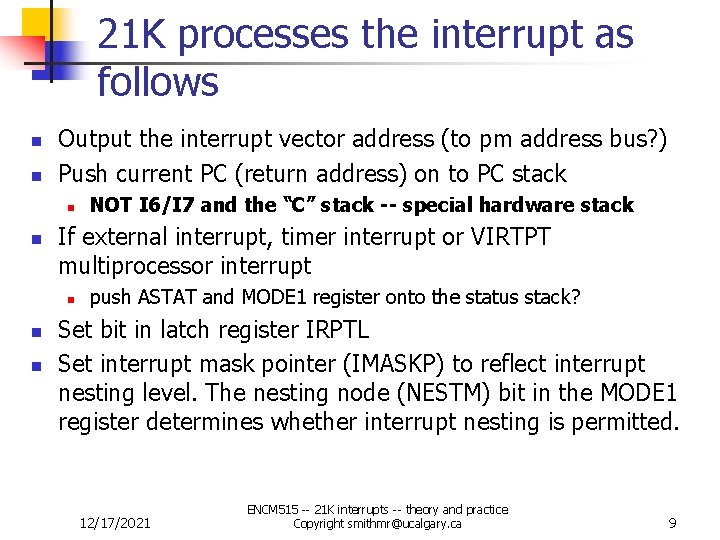

21 K processes the interrupt as follows n n Output the interrupt vector address (to pm address bus? ) Push current PC (return address) on to PC stack n n If external interrupt, timer interrupt or VIRTPT multiprocessor interrupt n n n NOT I 6/I 7 and the “C” stack -- special hardware stack push ASTAT and MODE 1 register onto the status stack? Set bit in latch register IRPTL Set interrupt mask pointer (IMASKP) to reflect interrupt nesting level. The nesting node (NESTM) bit in the MODE 1 register determines whether interrupt nesting is permitted. 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 9

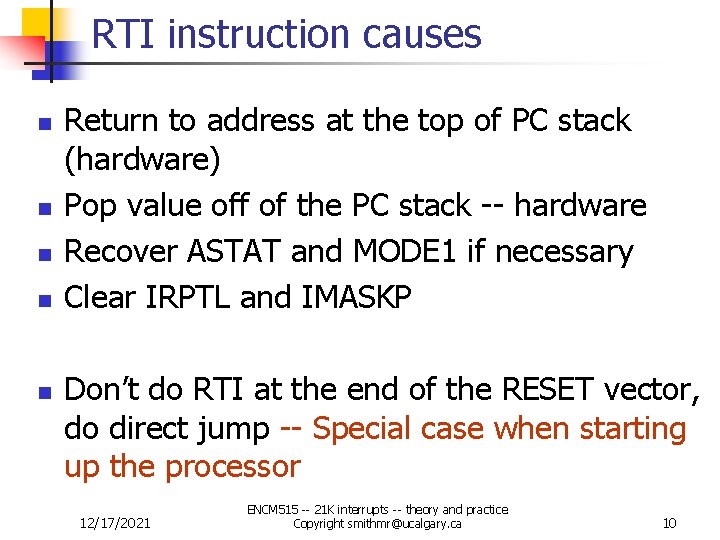

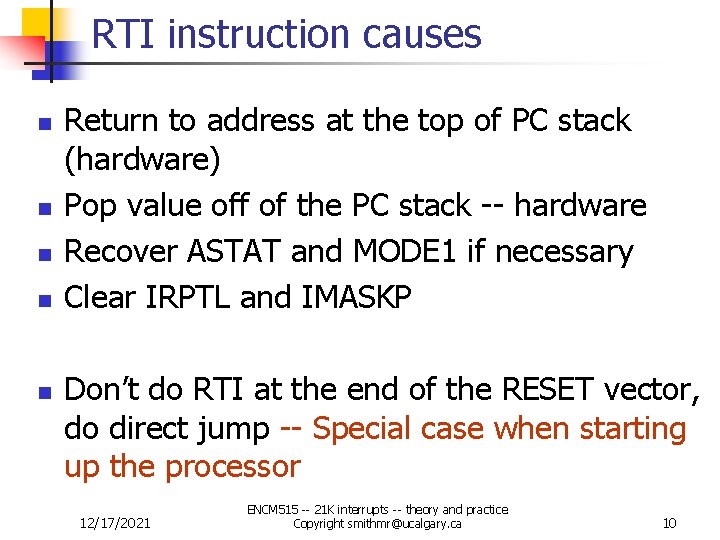

RTI instruction causes n n n Return to address at the top of PC stack (hardware) Pop value off of the PC stack -- hardware Recover ASTAT and MODE 1 if necessary Clear IRPTL and IMASKP Don’t do RTI at the end of the RESET vector, do direct jump -- Special case when starting up the processor 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 10

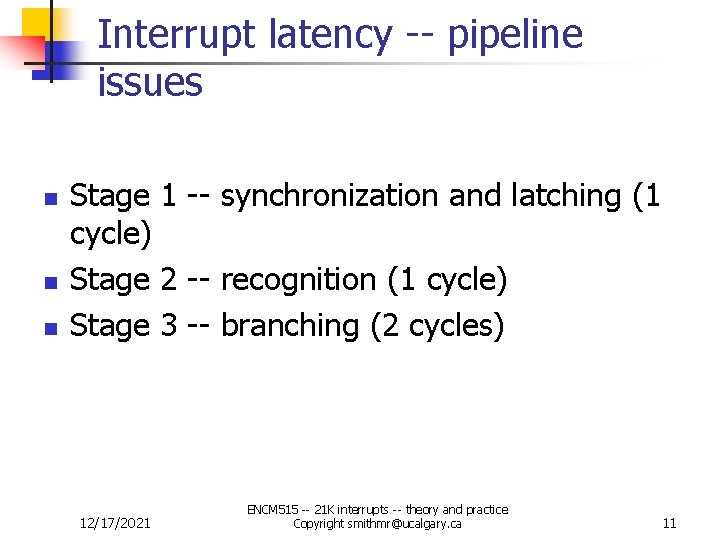

Interrupt latency -- pipeline issues n n n Stage 1 -- synchronization and latching (1 cycle) Stage 2 -- recognition (1 cycle) Stage 3 -- branching (2 cycles) 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 11

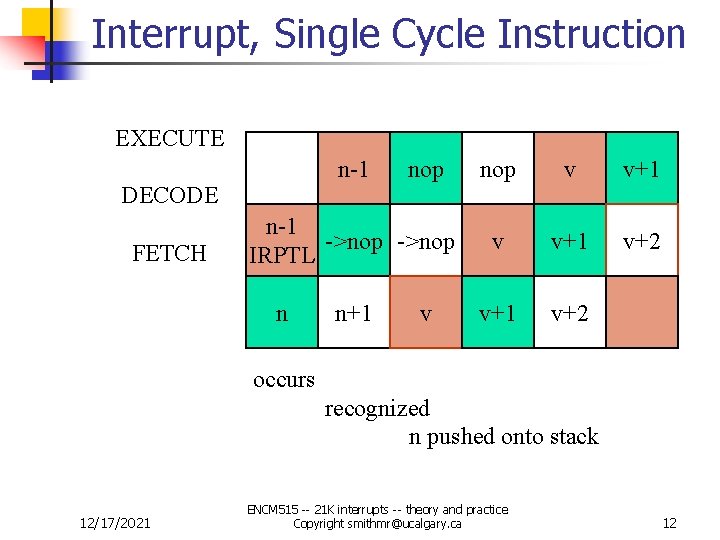

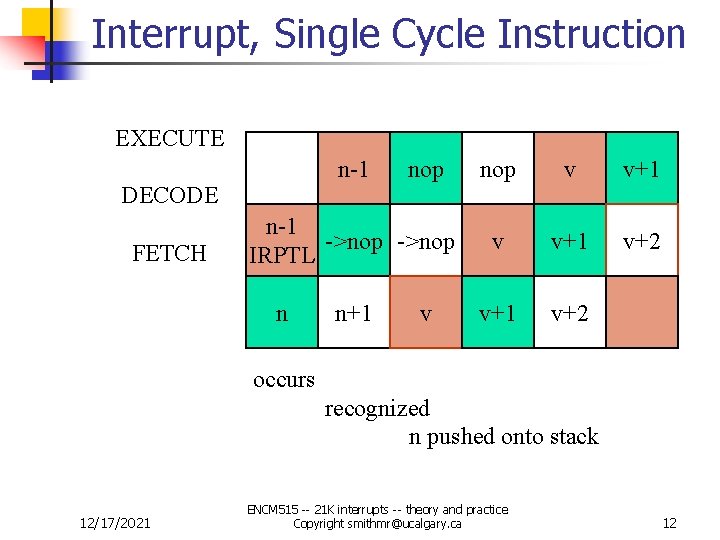

Interrupt, Single Cycle Instruction EXECUTE n-1 DECODE FETCH nop n-1 ->nop IRPTL n n+1 v nop v v+1 v+2 occurs recognized n pushed onto stack 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 12

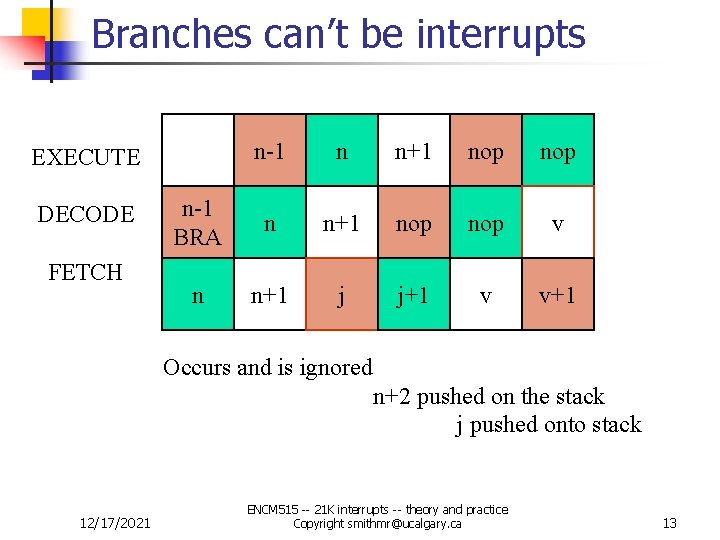

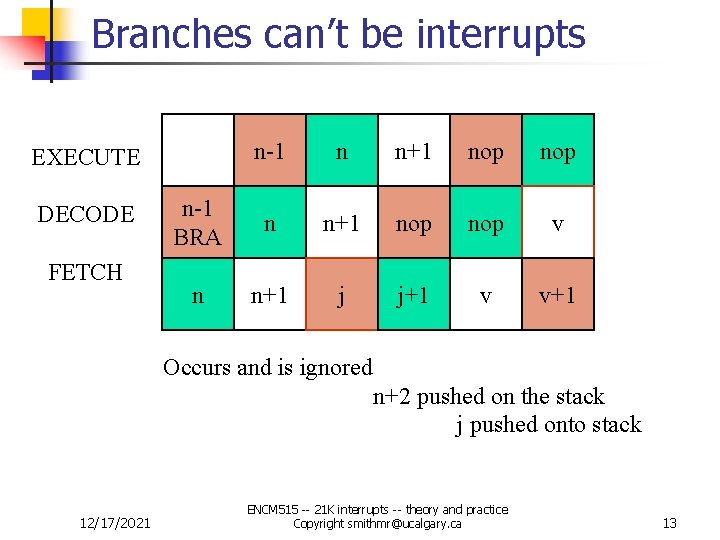

Branches can’t be interrupts n-1 n n+1 nop n-1 BRA n n+1 nop v n n+1 j j+1 v v+1 EXECUTE DECODE FETCH Occurs and is ignored n+2 pushed on the stack j pushed onto stack 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 13

Other things can’t be interrupted n Branch First of two cycles needed to perform a program memory and instruction fetch third to last iteration of a loop wait states for external memory n etc n n n 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 14

12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 15

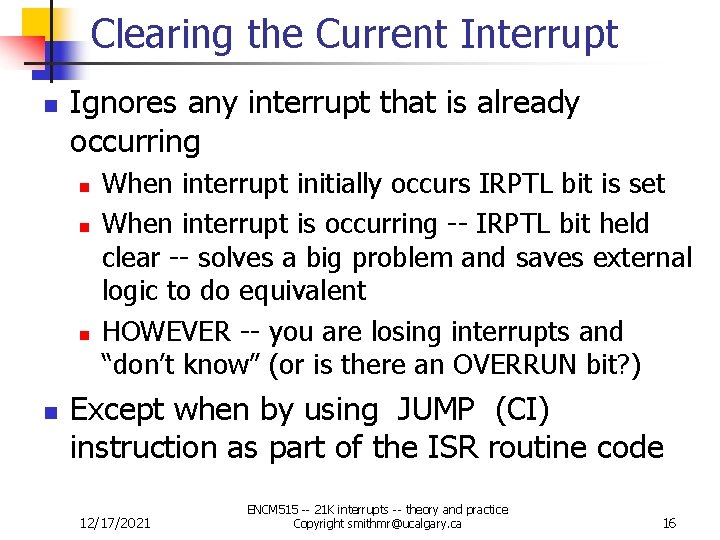

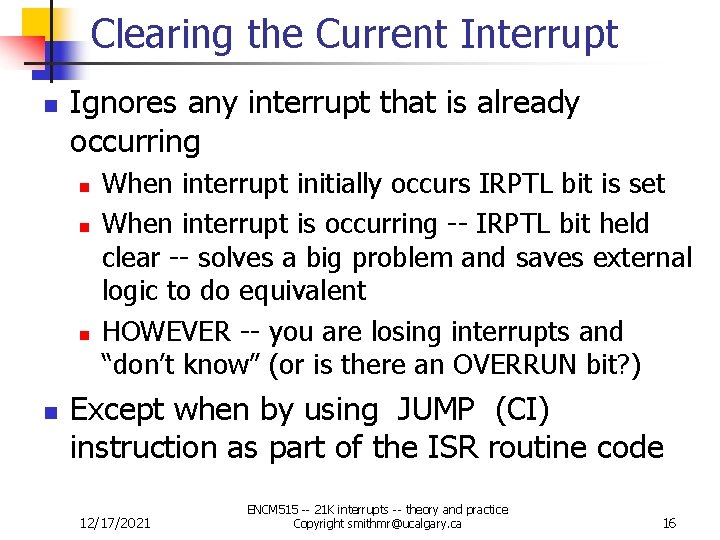

Clearing the Current Interrupt n Ignores any interrupt that is already occurring n n When interrupt initially occurs IRPTL bit is set When interrupt is occurring -- IRPTL bit held clear -- solves a big problem and saves external logic to do equivalent HOWEVER -- you are losing interrupts and “don’t know” (or is there an OVERRUN bit? ) Except when by using JUMP (CI) instruction as part of the ISR routine code 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 16

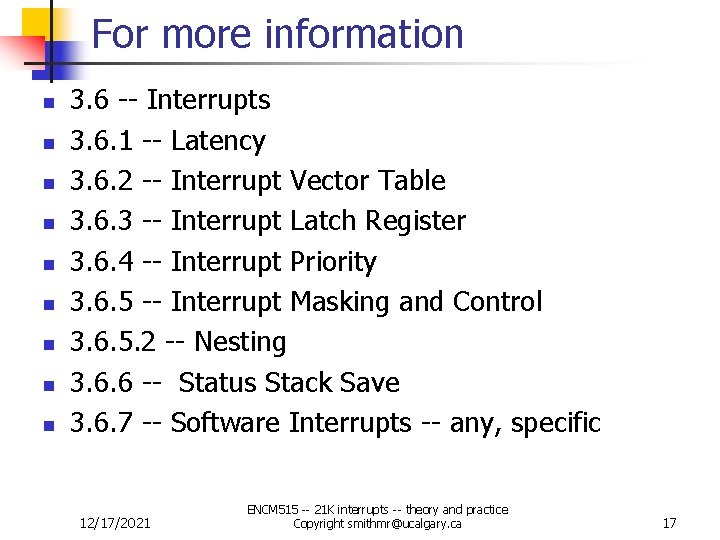

For more information n n n n 3. 6 -- Interrupts 3. 6. 1 -- Latency 3. 6. 2 -- Interrupt Vector Table 3. 6. 3 -- Interrupt Latch Register 3. 6. 4 -- Interrupt Priority 3. 6. 5 -- Interrupt Masking and Control 3. 6. 5. 2 -- Nesting 3. 6. 6 -- Status Stack Save 3. 6. 7 -- Software Interrupts -- any, specific 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 17

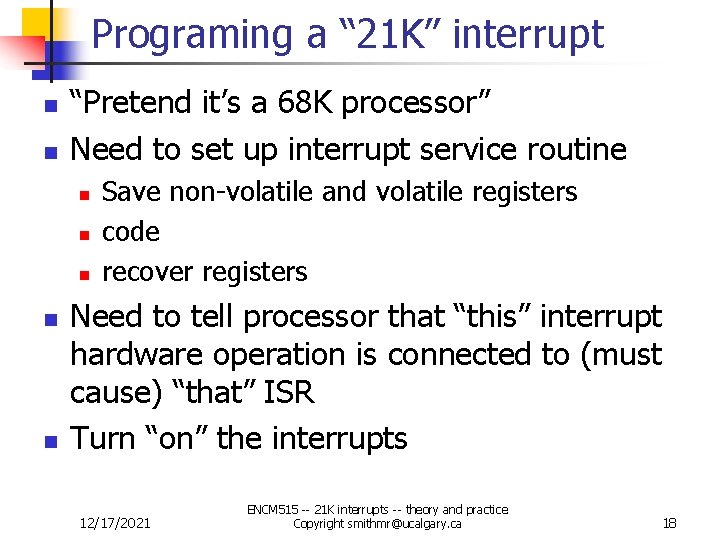

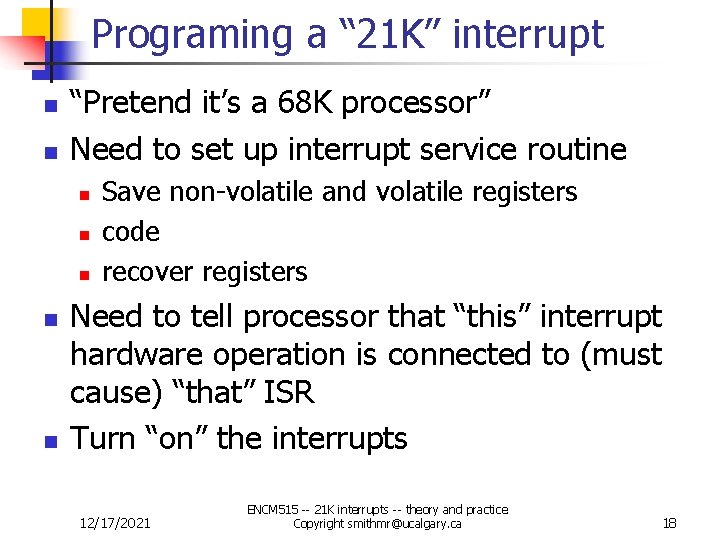

Programing a “ 21 K” interrupt n n “Pretend it’s a 68 K processor” Need to set up interrupt service routine n n n Save non-volatile and volatile registers code recover registers Need to tell processor that “this” interrupt hardware operation is connected to (must cause) “that” ISR Turn “on” the interrupts 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 18

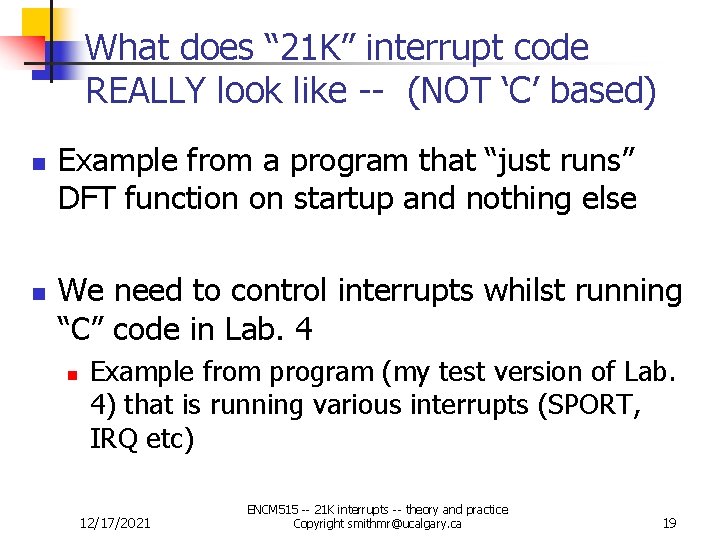

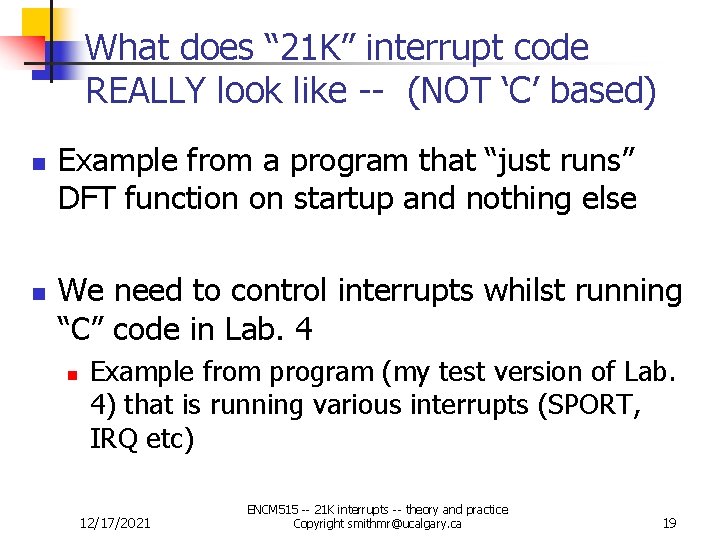

What does “ 21 K” interrupt code REALLY look like -- (NOT ‘C’ based) n n Example from a program that “just runs” DFT function on startup and nothing else We need to control interrupts whilst running “C” code in Lab. 4 n Example from program (my test version of Lab. 4) that is running various interrupts (SPORT, IRQ etc) 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 19

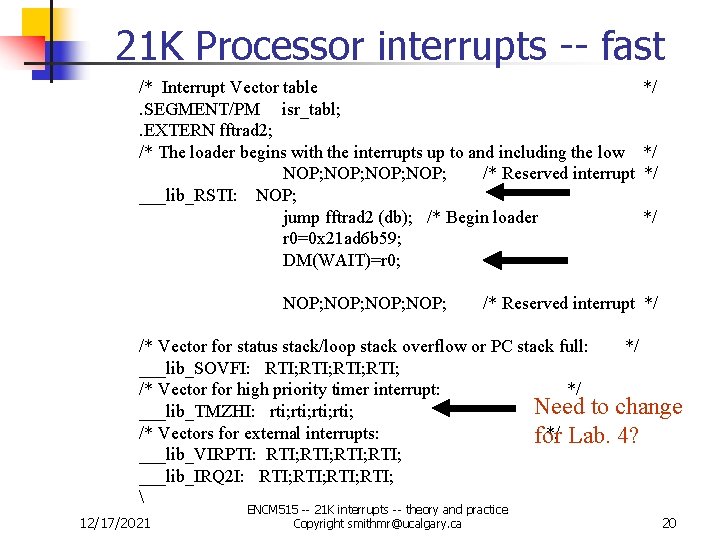

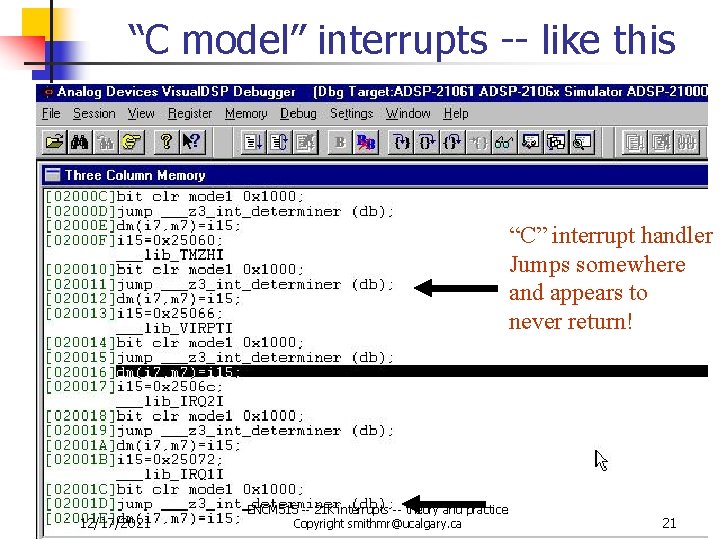

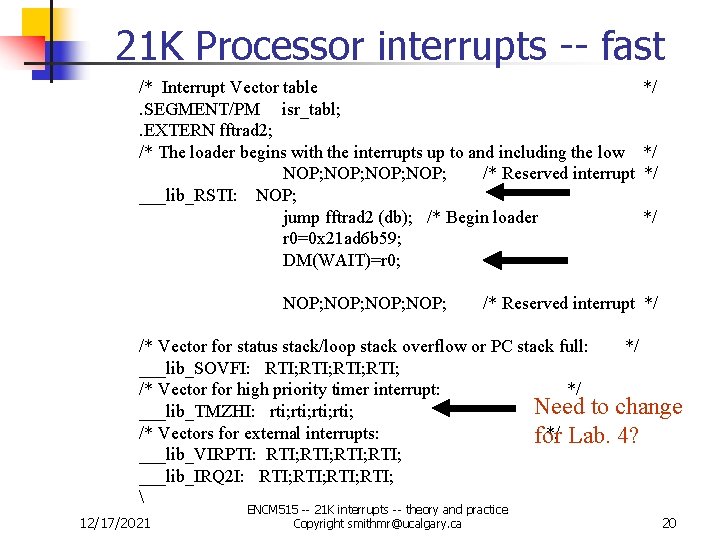

21 K Processor interrupts -- fast /* Interrupt Vector table. SEGMENT/PM isr_tabl; . EXTERN fftrad 2; /* The loader begins with the interrupts up to and including the low NOP; /* Reserved interrupt ___lib_RSTI: NOP; jump fftrad 2 (db); /* Begin loader r 0=0 x 21 ad 6 b 59; DM(WAIT)=r 0; NOP; */ */ /* Reserved interrupt */ /* Vector for status stack/loop stack overflow or PC stack full: */ ___lib_SOVFI: RTI; /* Vector for high priority timer interrupt: */ Need to change ___lib_TMZHI: rti; /* Vectors for external interrupts: */ Lab. 4? for ___lib_VIRPTI: RTI; ___lib_IRQ 2 I: RTI; 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 20

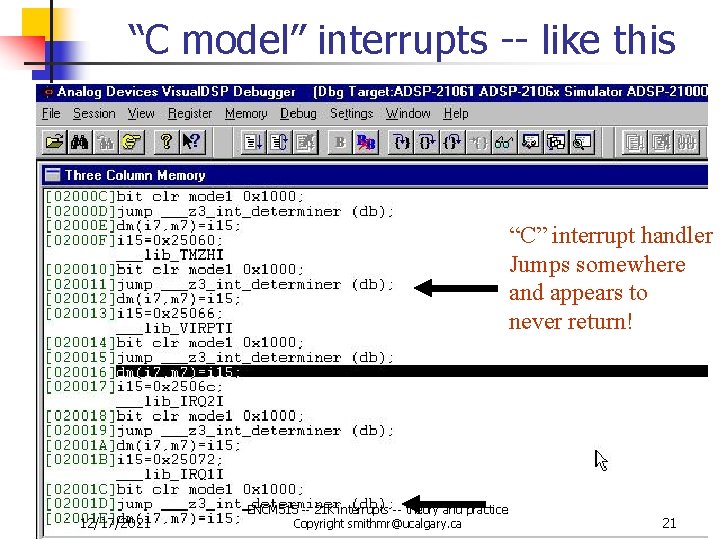

“C model” interrupts -- like this “C” interrupt handler Jumps somewhere and appears to never return! 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 21

BIG Problem n n The “C” linker pulls in some very special code to make the interrupts happen in the way it wants to. The “C” interrupt model must be doing something very similar to what we want to do, so “go with the flow” n We COULD modify the “C” linker code to jump directly to our routines -- see next slide 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 22

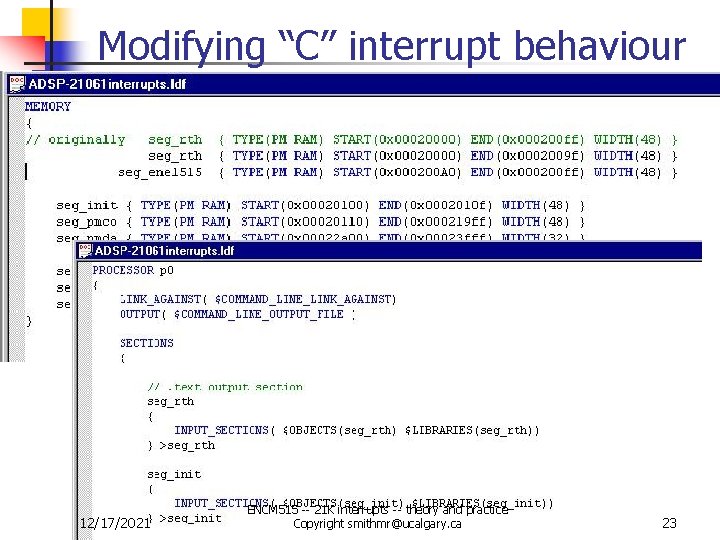

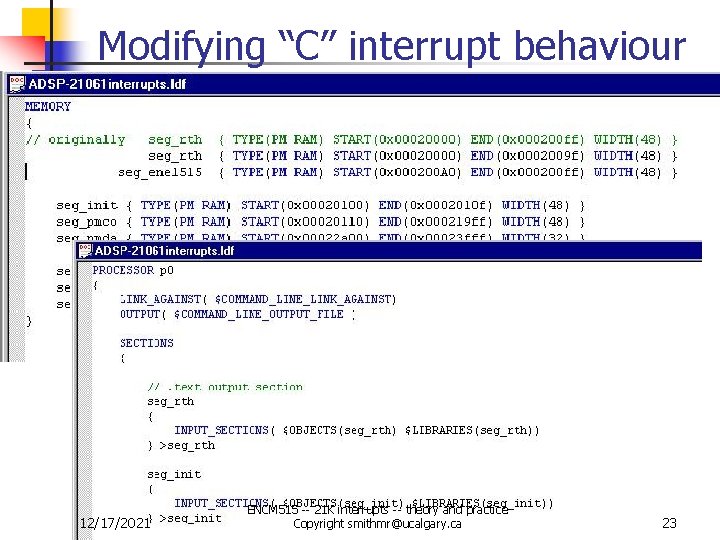

Modifying “C” interrupt behaviour 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 23

But is the effect worth while “at the moment” (I. e Lab. 4) How many hours spent to save “how many cycles” at 40 MHz? Do we need the extra performance? 12/17/2021 24

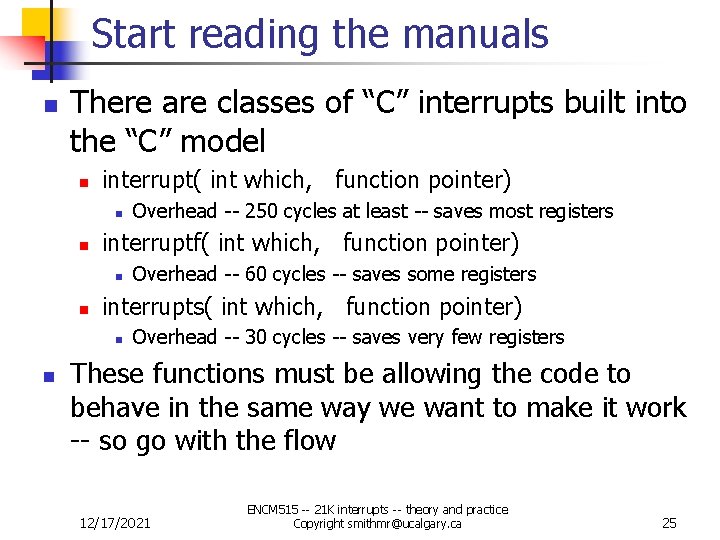

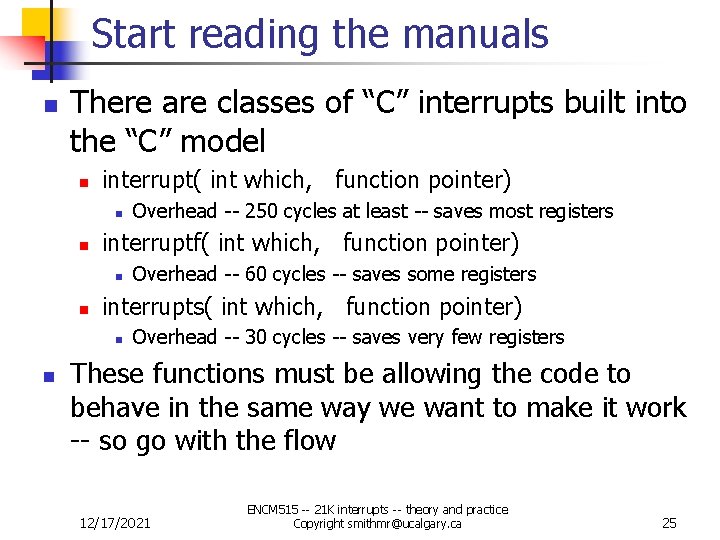

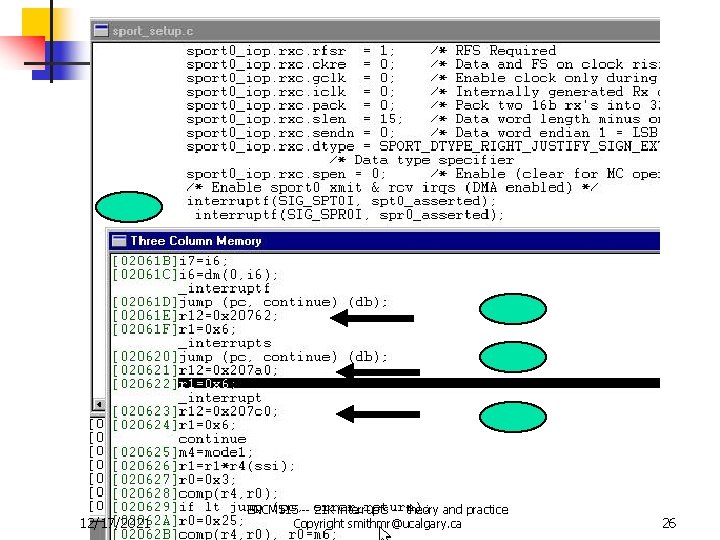

Start reading the manuals n There are classes of “C” interrupts built into the “C” model n interrupt( int which, function pointer) n n interruptf( int which, function pointer) n n Overhead -- 60 cycles -- saves some registers interrupts( int which, function pointer) n n Overhead -- 250 cycles at least -- saves most registers Overhead -- 30 cycles -- saves very few registers These functions must be allowing the code to behave in the same way we want to make it work -- so go with the flow 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 25

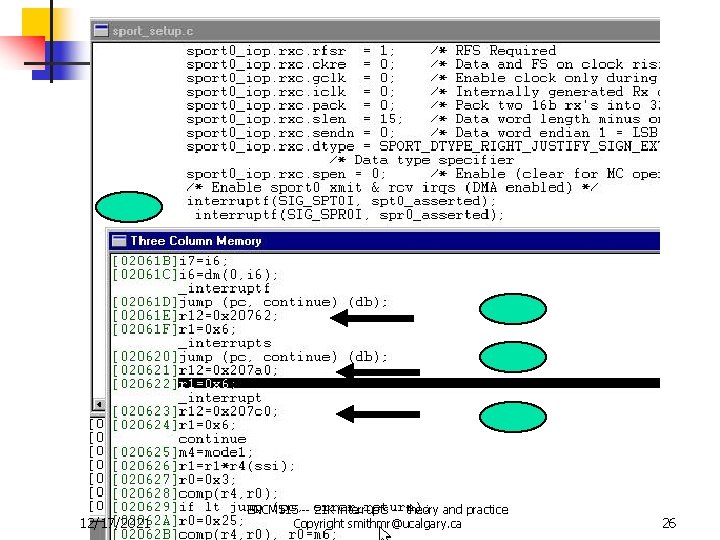

12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 26

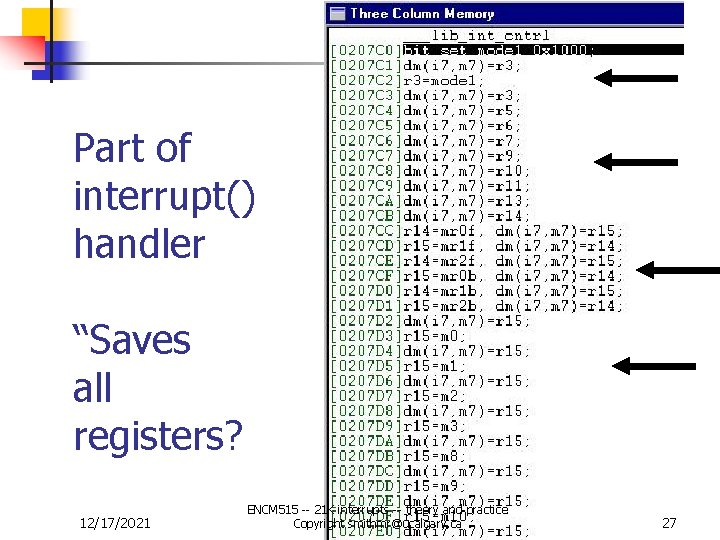

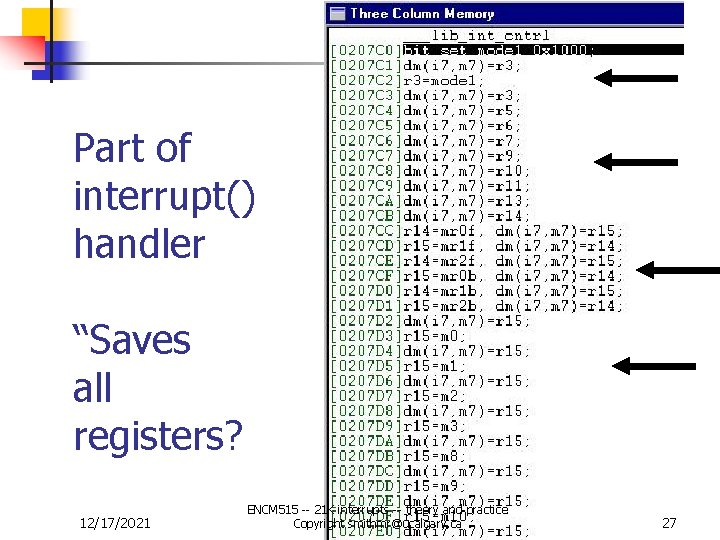

Part of interrupt() handler “Saves all registers? 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 27

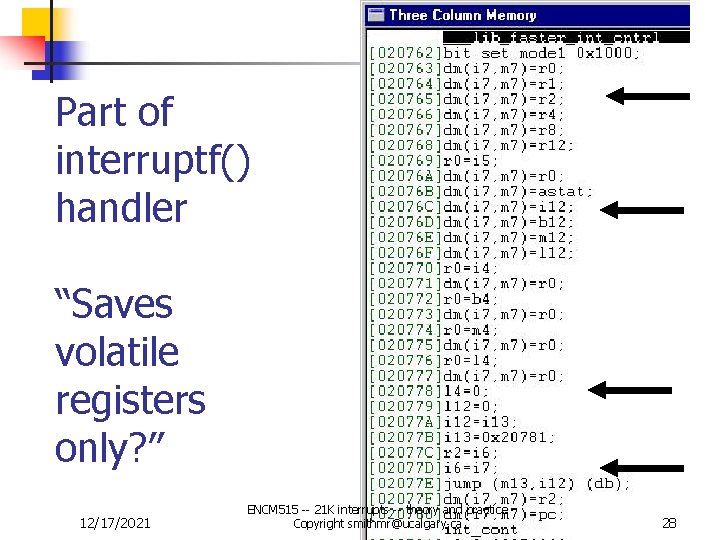

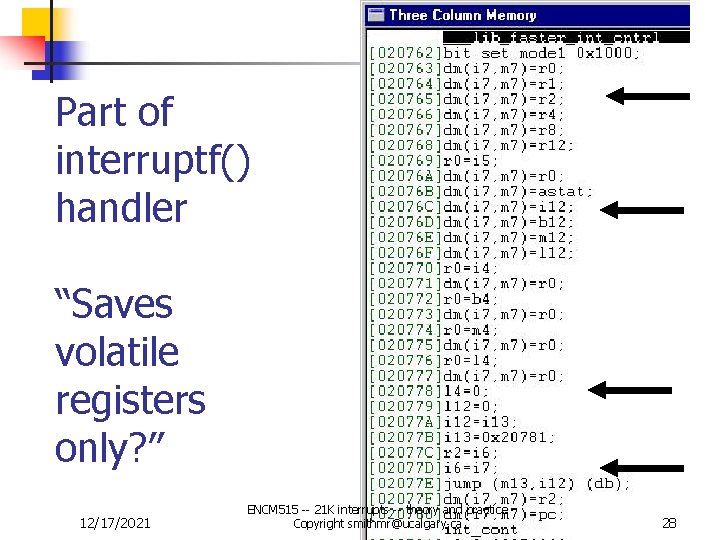

Part of interruptf() handler “Saves volatile registers only? ” 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 28

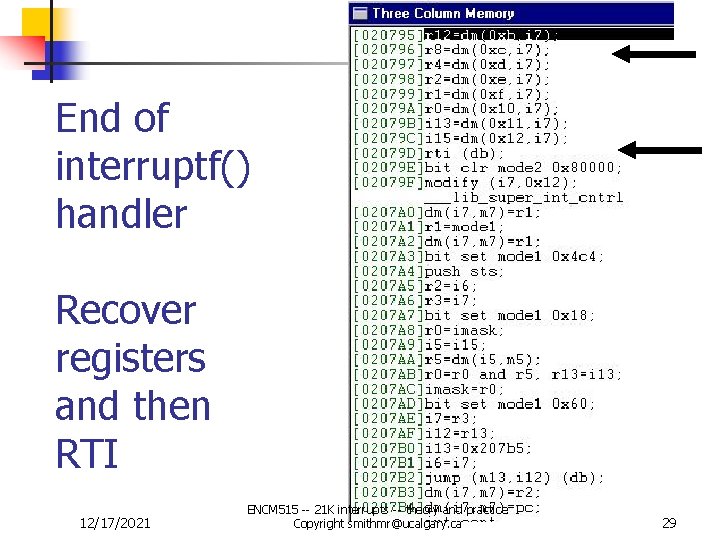

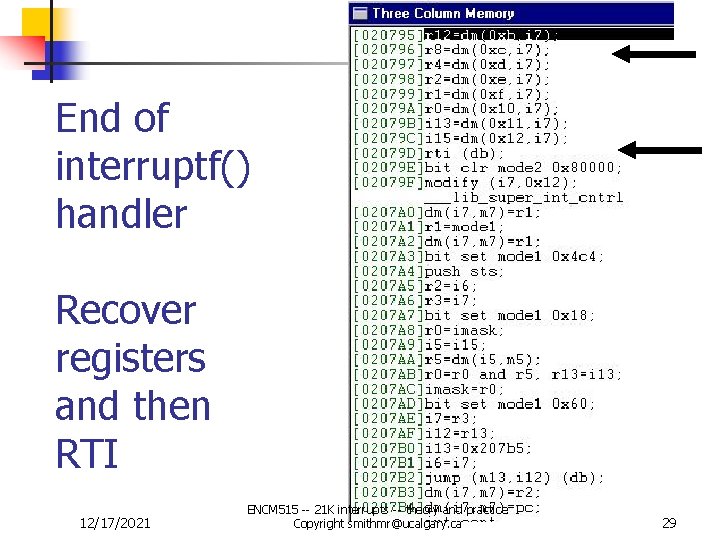

End of interruptf() handler Recover registers and then RTI 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 29

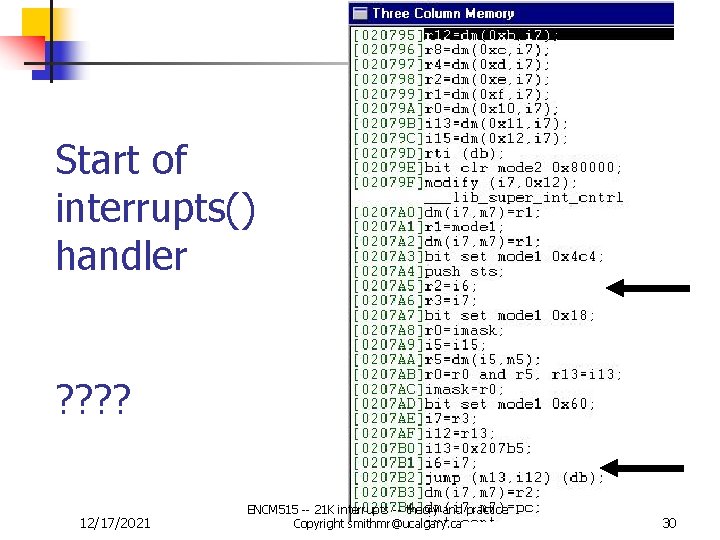

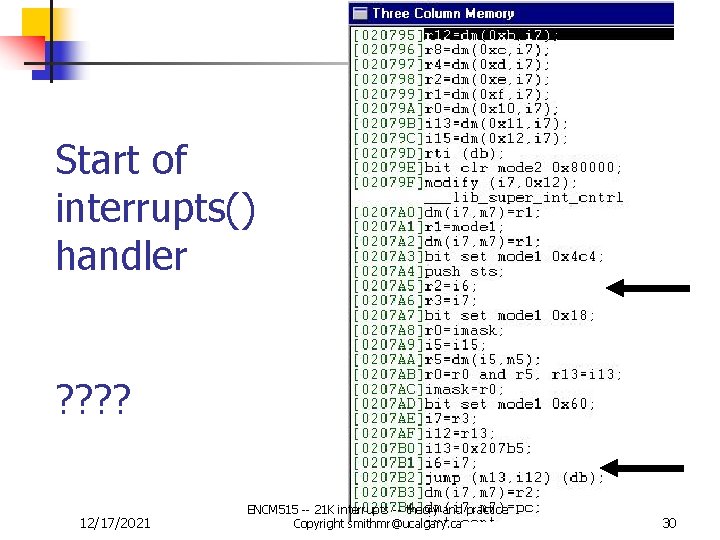

Start of interrupts() handler ? ? 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 30

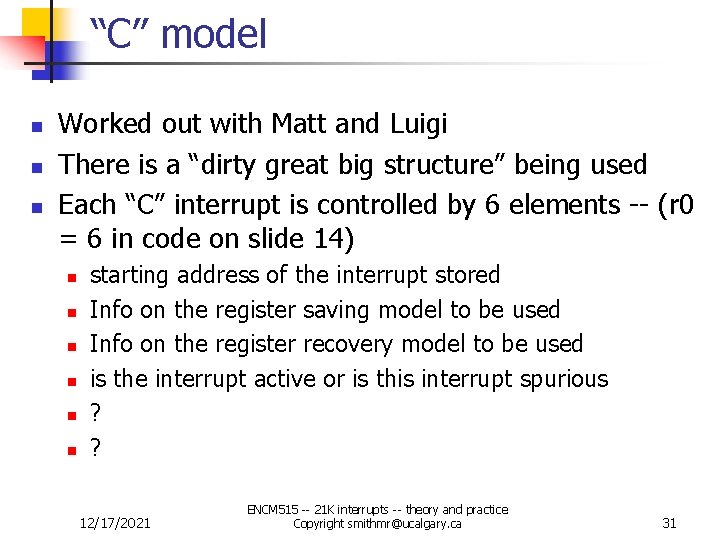

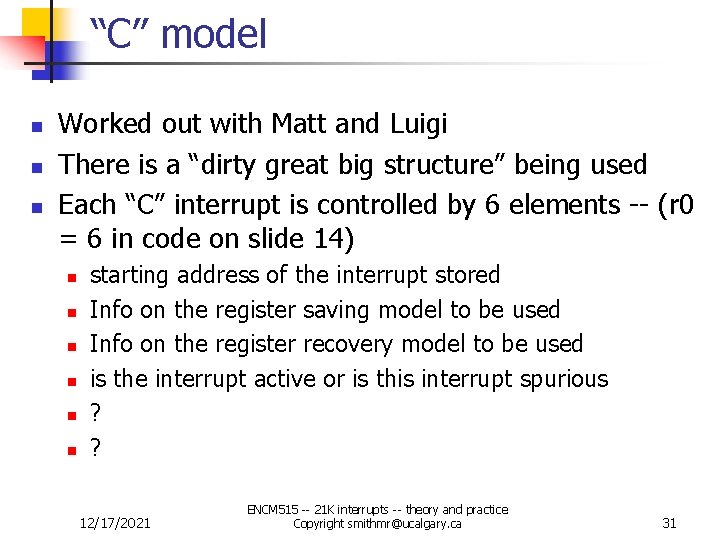

“C” model n n n Worked out with Matt and Luigi There is a “dirty great big structure” being used Each “C” interrupt is controlled by 6 elements -- (r 0 = 6 in code on slide 14) n n n starting address of the interrupt stored Info on the register saving model to be used Info on the register recovery model to be used is the interrupt active or is this interrupt spurious ? ? 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 31

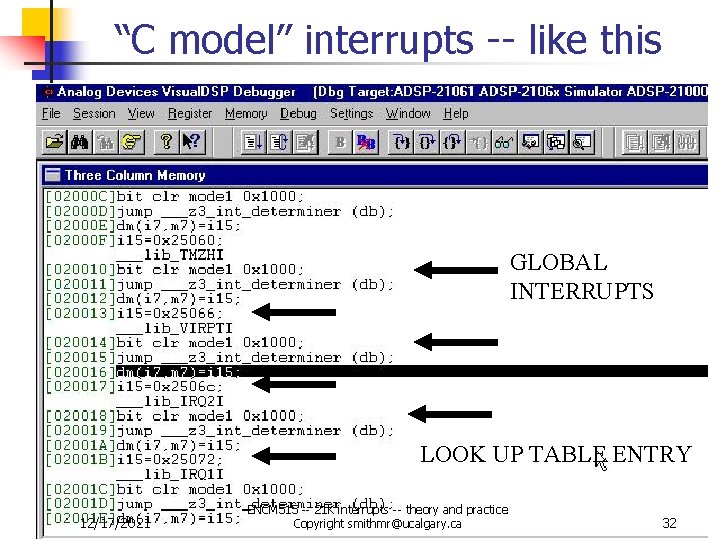

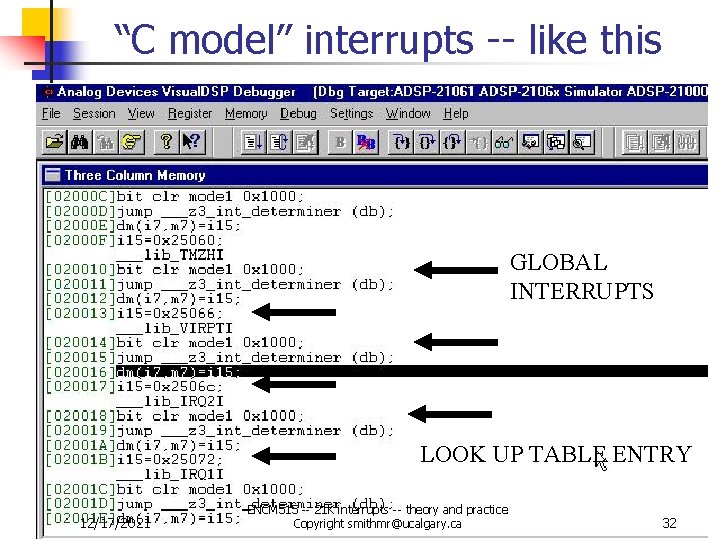

“C model” interrupts -- like this GLOBAL INTERRUPTS LOOK UP TABLE ENTRY 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 32

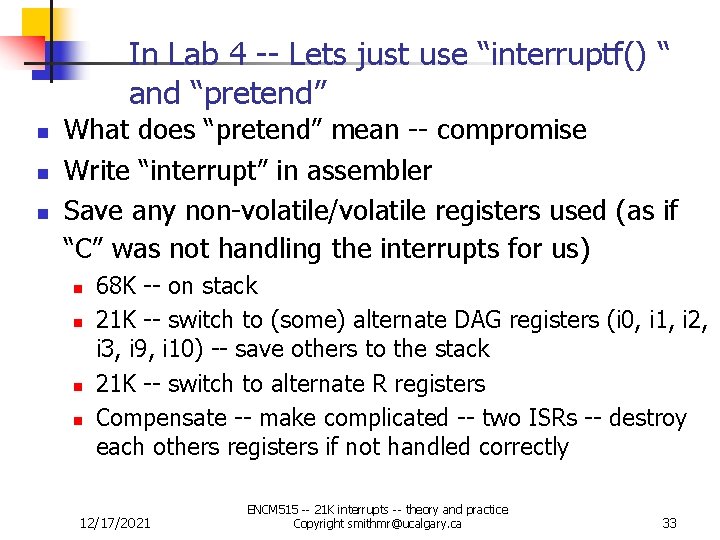

In Lab 4 -- Lets just use “interruptf() “ and “pretend” n n n What does “pretend” mean -- compromise Write “interrupt” in assembler Save any non-volatile/volatile registers used (as if “C” was not handling the interrupts for us) n n 68 K -- on stack 21 K -- switch to (some) alternate DAG registers (i 0, i 1, i 2, i 3, i 9, i 10) -- save others to the stack 21 K -- switch to alternate R registers Compensate -- make complicated -- two ISRs -- destroy each others registers if not handled correctly 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 33

Interrupts on 21 K -- designed to be fast n n n Finish current instruction (1 cycle) (but what about pipeline issues? ) Save next instruction address (hardware) Save status register? ? Alternate set of registers available (sometimes) Starting address of the ISR routine at fixed location (0 cycles) 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 34

Tackled today n n n Review Subroutines and Interrupts Architectural Issues regarding 21 K interrupts Programming issues regarding 21 K interrupts 12/17/2021 ENCM 515 -- 21 K interrupts -- theory and practice Copyright smithmr@ucalgary. ca 35