Cell Broadband Engine Architecture Bardia Mahjour ENCM 515

Cell Broadband Engine Architecture Bardia Mahjour ENCM 515 March 2007

Agenda Ø Introduction Ø History Ø Applications Ø Architecture Ø Features Ø Some Statistics Ø Programming Model Ø CBEA as DSP Ø Comparison with Tiger. SHARC Ø Conclusion

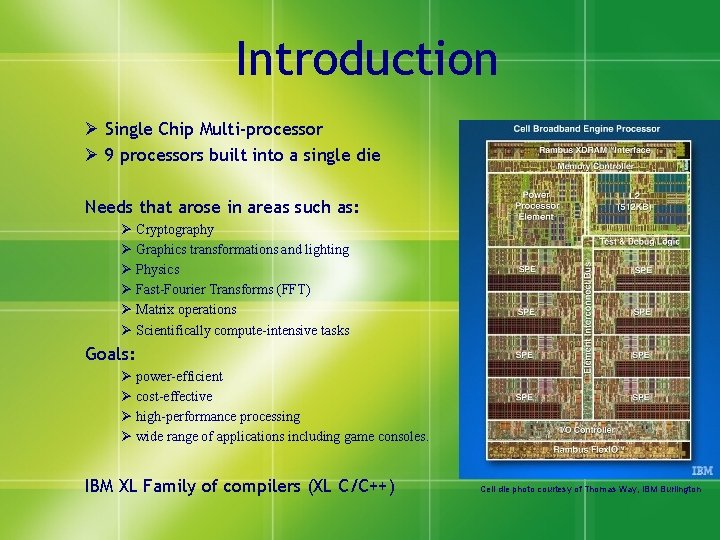

Introduction Ø Single Chip Multi-processor Ø 9 processors built into a single die Needs that arose in areas such as: Ø Cryptography Ø Graphics transformations and lighting Ø Physics Ø Fast-Fourier Transforms (FFT) Ø Matrix operations Ø Scientifically compute-intensive tasks Goals: Ø power-efficient Ø cost-effective Ø high-performance processing Ø wide range of applications including game consoles. IBM XL Family of compilers (XL C/C++) Cell die photo courtesy of Thomas Way, IBM Burlington

History Ø A joint venture by Sony, Toshiba, and IBM (STI) Ø Official Design phase started in March of 2001 Ø Three giant companies spent 4 years and US$400 M to design and develop Cell Ø First Commercial Use in Sony’s Play. Station 3 in November 2006.

Applications Ø Console Video Games § Play. Station 3 Ø Home Cinema § Toshiba’s HDTV Ø Embedded Applications § Medical Imaging, aerospace, telecommunication, defense, etc. § Mercury Computer Systems, Inc. Ø Super Computing § Roadrunner Ø Blade Servers

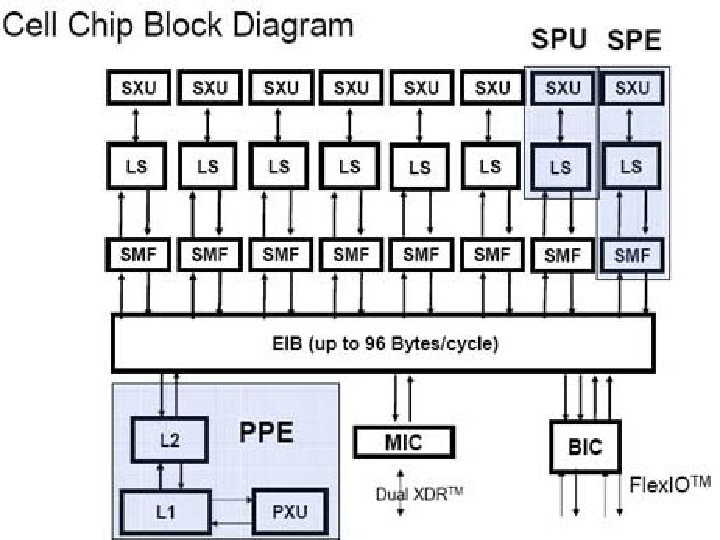

Architecture Ø Power. PC Processor Element (PPE) - 64 -bit Power. PC RISC core (can run OS) Ø Synergistic Processor Elements (SPEs) - Each element is a DSP processor. CBEA has 8 of them! Ø Element Interconnect Bus (EIB) Ø Memory Interface Controller (MIC) Ø Cell Broadband Engine Interface (BEI)

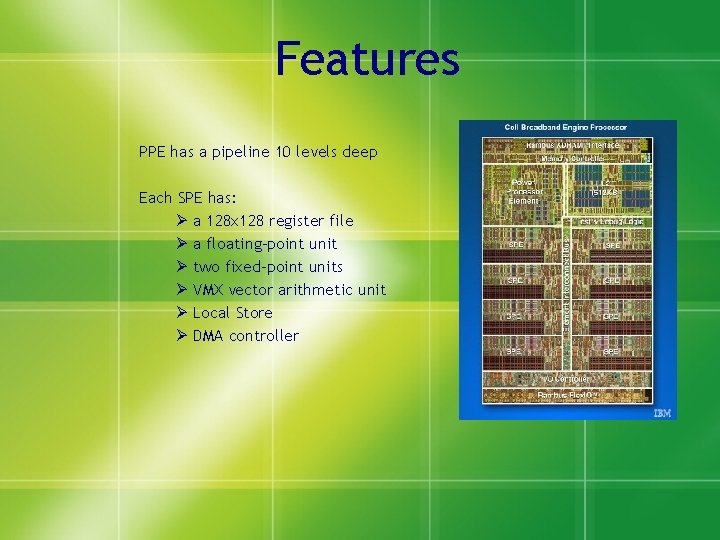

Features PPE has a pipeline 10 levels deep Each SPE has: Ø a 128 x 128 register file Ø a floating-point unit Ø two fixed-point units Ø VMX vector arithmetic unit Ø Local Store Ø DMA controller

Some Statistics Ø Observed clock speed: > 4 GHz Ø Peak performance (single precision): > 256 Gflops Ø Peak performance (double precision): >26 GFlops Ø Local storage size per SPU: 256 KB Ø Area: 221 mm² Ø Technology 90 nm SOI Ø Total number of transistors: 234 M

Programming Model Ø Function Offload Model Ø Device Extension Model Ø Computational Acceleration Model Ø Streaming Models Ø Shared-memory Multi-processor Model Ø Asymmetric Thread Runtime Model Ø User-Mode Thread Model Ø SPE Overlay

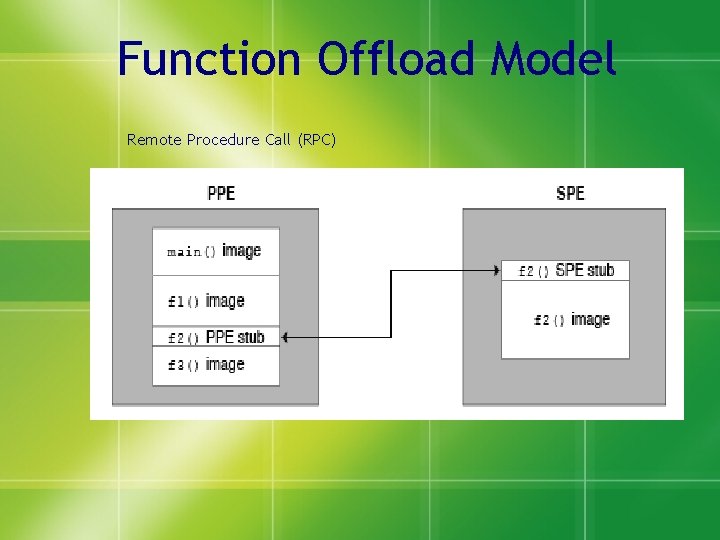

Function Offload Model Remote Procedure Call (RPC)

![Function Offload Model /* file hello. idl */ interface greeting{[sync] idl_id_t hello ([in] int Function Offload Model /* file hello. idl */ interface greeting{[sync] idl_id_t hello ([in] int](http://slidetodoc.com/presentation_image_h/1b33108c2b6c54abf3a28aa691f642e7/image-12.jpg)

Function Offload Model /* file hello. idl */ interface greeting{[sync] idl_id_t hello ([in] int nbytes, [in, size_is(nbytes)] char message[]); } /* file hello. c */ #include <stub. h> int main( ){ char* str = “Hi, from the Cell!”; hello( strlen(str), str); } /* file spu_hello. c */ #include <stdio. h> #include <stub. h> idl_id_t hello( int nbytes, char msg[]) { printf(“SPE: %sn”, ms); return 0; }

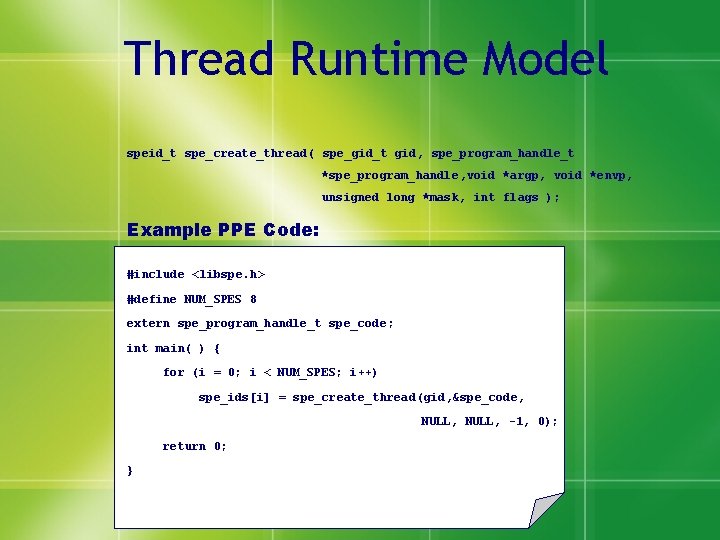

Thread Runtime Model speid_t spe_create_thread ( spe_gid_t gid, spe_program_handle_t *spe_program_handle, void *argp, void *envp, unsigned long *mask, int flags ); Example PPE Code: #include <libspe. h> #define NUM_SPES 8 extern spe_program_handle_t spe_code ; int main( ) { for (i = 0; i < NUM_SPES; i++) spe_ids[i] = spe_create_thread(gid, &spe_code, NULL, -1, 0); return 0; }

CBEA as DSP Strictly speaking : Cell is a microprocessor Designed to bridge the gap between conventional and special-purpose processors Handles heavy digital signal processing workloads ( 3 D graphics, 48 MPEG-2 Channels, etc. ) Meets most of the ideal DSP processor requirements

Comparison with Tiger. SHARC Ø Size requirement Ø Power consumption and heat generation Ø Supports floating-point ops in hardware Ø Bandwidth and data-width Ø Avoids resource dependencies Ø Scalability Ø Ease of programming

Conclusion Cell Broadband Engine Architecture is an extremely powerful, scalable and fast processor. It is not purely a digital signal processor, however, the wide range of applications it is suited for includes DSP. Furthermore, many of the requirements of DSP applications were the rationale behind CBEA’s design and architectural decisions.

![References [1] IBM Research, The Cell Architecture, Innovation Matters. Available at http: //domino. research. References [1] IBM Research, The Cell Architecture, Innovation Matters. Available at http: //domino. research.](http://slidetodoc.com/presentation_image_h/1b33108c2b6c54abf3a28aa691f642e7/image-17.jpg)

References [1] IBM Research, The Cell Architecture, Innovation Matters. Available at http: //domino. research. ibm. com/comm/research. nsf/pages/r. arch. innovation. html Accessed Feb 19 th, 2007 [2] IBM Systems and Technology Group, Cell Broadband Engine Programming Tutorial Version 2. 0, December 15, 2006 [3] Wikipedia , Cell Microprocessor Implementations. Available at http: //en. wikipedia. org/wiki/Cell_microprocessor_implementations - endnote_sti 32 nm Accessed Feb 20 th, 2007 [4] Signalogic 1995 -2007, DSP Applications. Available at http: //www. signalogic. com/index. pl? page=dsp_app#What. DSP Accessed Feb 21 st, 2007 [5] Wikipedia , Cell Microprocessor. Available at http: //en. wikipedia. org/wiki/Cell_Broadband_Engine Accessed Feb 22 nd, 2007 [6] IBM Journal of Research and Development, Introduction to the Cell multiprocessor (September 7, 2005) Available at http: //researchweb. watson. ibm. com/journal/rd/494/kahle. html [7] Smith, M. R. (1992). How RISCy is DSP? Micro, IEEE, Volume 12, Issue 6, 10 -22. [8] Analog Devices Inc. One Technology Way, ADSP-TS 201 Tiger. SHARC Processor Programming Reference, Version 1. 1, April 2005

- Slides: 17