8085 interrupts 8085 Interrupts Maskable INTR RST vectored

8085 interrupts

8085 Interrupts • Maskable – INTR – RST vectored • Non-Maskable – TRAP • Vectored – RST 5. 5, RST 6. 5, RST 7. 5, TRAP

Interrupt process • enable by writing EI. • mp checks INTR line at each instruction. • if INTR is high, mp completes the current instr, disables Interrupt Flip-flop, sends INTA signal. • An RST instru is inserted by INTA through external hardware. • Mp saves the memory address of the next instru into stack. Program control is transferred to CALL location. The service routine starts at CALL location. • At the end of the subroutine Int Flag is enabled again by EI instru. • The last instr of the subroutine is RET to trasfer back the prog control to its orginal address.

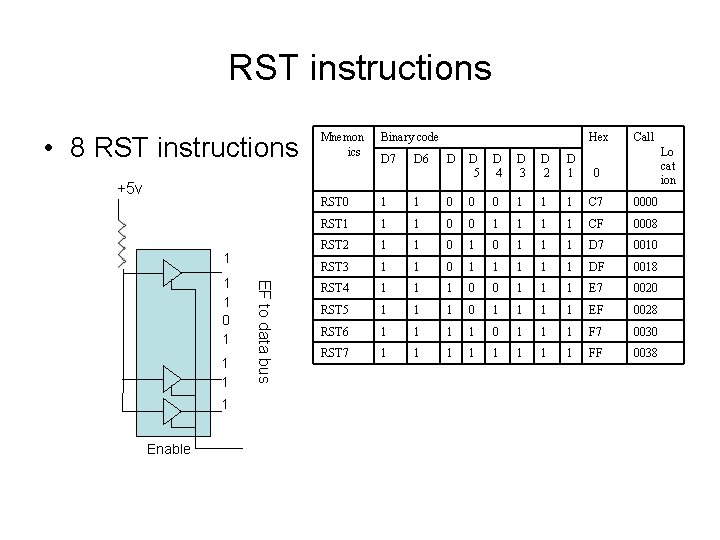

RST instructions • 8 RST instructions +5 v 1 1 Enable EF to data bus 1 1 0 1 Mnemon ics Binary code D 7 D 6 Hex D D 5 D 4 D 3 D 2 D 1 0 Call Lo cat ion RST 0 1 1 0 0 0 1 1 1 C 7 0000 RST 1 1 1 0 0 1 1 CF 0008 RST 2 1 1 0 1 1 1 D 7 0010 RST 3 1 1 0 1 1 1 DF 0018 RST 4 1 1 1 0 0 1 1 1 E 7 0020 RST 5 1 1 1 0 1 1 EF 0028 RST 6 1 1 0 1 1 1 F 7 0030 RST 7 1 1 1 1 FF 0038

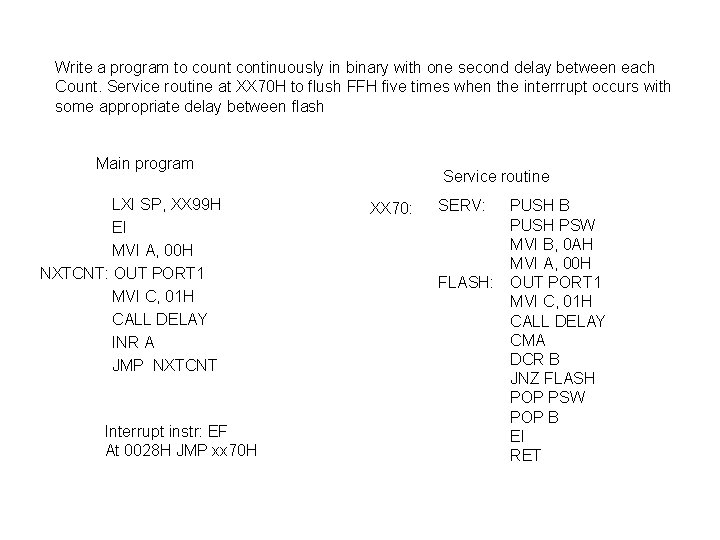

Write a program to count continuously in binary with one second delay between each Count. Service routine at XX 70 H to flush FFH five times when the interrrupt occurs with some appropriate delay between flash Main program LXI SP, XX 99 H EI MVI A, 00 H NXTCNT: OUT PORT 1 MVI C, 01 H CALL DELAY INR A JMP NXTCNT Interrupt instr: EF At 0028 H JMP xx 70 H Service routine XX 70: SERV: FLASH: PUSH B PUSH PSW MVI B, 0 AH MVI A, 00 H OUT PORT 1 MVI C, 01 H CALL DELAY CMA DCR B JNZ FLASH POP PSW POP B EI RET

Issues in implementing interrupts • Is there a minimum pulse width required for the INTR signals? – MP checks INTR, one clk period before the last-T state of an instruction cycle, therefore, the INTR pulse should be high at least for 17. 5 T-states. • How long can the INTR pulse stay high? • Can the MP be interrupted again before the completion of the first interrupt service routine?

- Slides: 6