ENCM 515 Interrupts Review and Cinterrupts M R

![POLLING to check for events int event 1, event 2, event 3; float array_in[200], POLLING to check for events int event 1, event 2, event 3; float array_in[200],](https://slidetodoc.com/presentation_image_h2/1bfec8d5d40dbe9bd5a7ae0e75e7d9a7/image-5.jpg)

![Solution -- Interrupts void Interrupt. Service. Routine(void); char isr_count; // Semaphore float array_in[200], array_out[200]; Solution -- Interrupts void Interrupt. Service. Routine(void); char isr_count; // Semaphore float array_in[200], array_out[200];](https://slidetodoc.com/presentation_image_h2/1bfec8d5d40dbe9bd5a7ae0e75e7d9a7/image-6.jpg)

![Rough Code for 68 K style main( ) #define SIZE 200 float buffer 1[SIZE], Rough Code for 68 K style main( ) #define SIZE 200 float buffer 1[SIZE],](https://slidetodoc.com/presentation_image_h2/1bfec8d5d40dbe9bd5a7ae0e75e7d9a7/image-12.jpg)

- Slides: 23

ENCM 515 -- Interrupts “Review” and “C”-interrupts M. R. Smith, Electrical and Computer Engineering University of Calgary, Alberta, Canada smithmr @ ucalgary, ca 12/19/2021 1

To be tackled today n n Subroutines and Interrupts Example “C” code (68 K) n n n subroutine assembly code interrupt service routine assembly Example “C” code (21 K) n n n The “C” wrapper interrupts using IRQ 1 button interrupts using 21 K timer 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 2

Subroutines and Interrupts n n Very similar in concept Very different in implementation Subroutines occur as part of your normal program flow. You tackle a certain task, written as a subroutine, at a certain location in your code. Time of starting plays no part in the design of a subroutine. 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 3

WAITING for an event to happen n Sometimes your code must wait for an external event to occur before the code can proceed float array_in[200], array_out[200]; main( ) { For Ever { Wait till array_in() is filled; Process(array_in, array_out); Do. Rest. Of. Code(); } n Stupid way to code -- unless this is the only thing the processor will. ENCM 515 do -- Interrupts Review -- Part 1 12/19/2021 Copyright smithmr@ucalgary. ca 4

![POLLING to check for events int event 1 event 2 event 3 float arrayin200 POLLING to check for events int event 1, event 2, event 3; float array_in[200],](https://slidetodoc.com/presentation_image_h2/1bfec8d5d40dbe9bd5a7ae0e75e7d9a7/image-5.jpg)

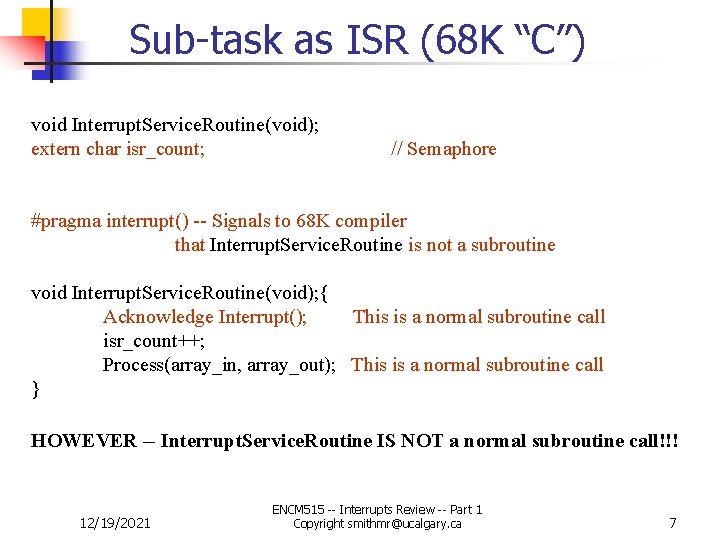

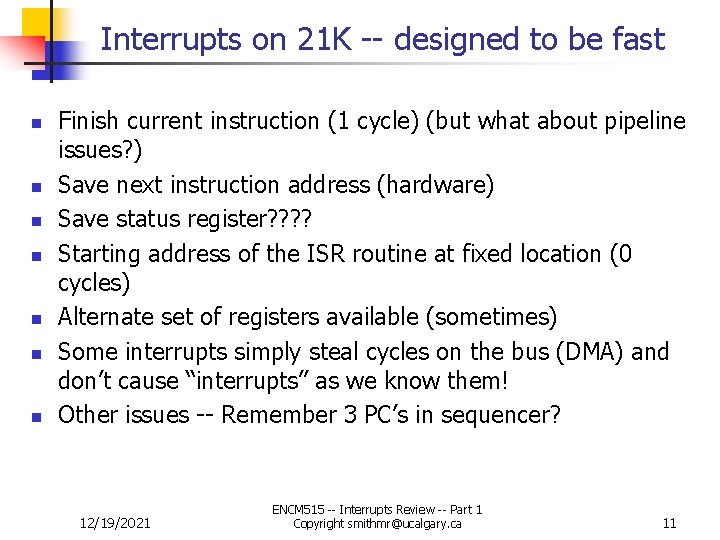

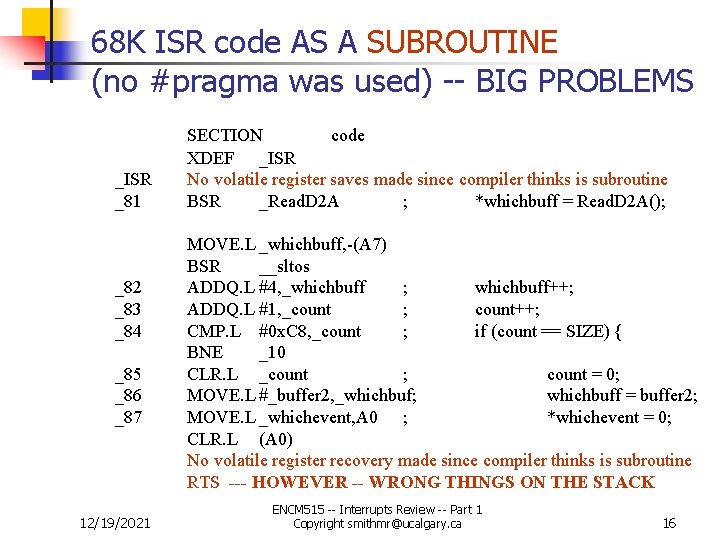

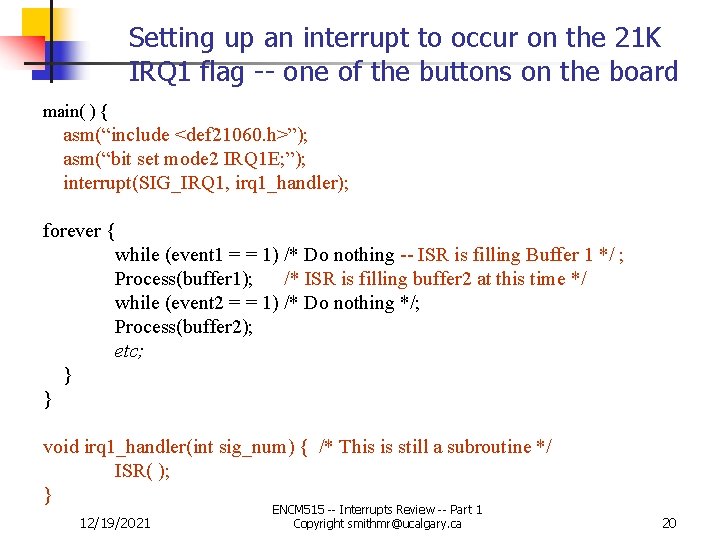

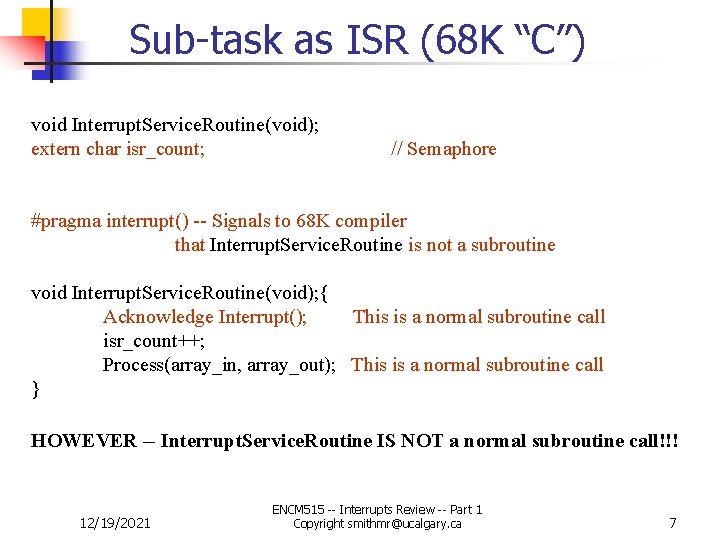

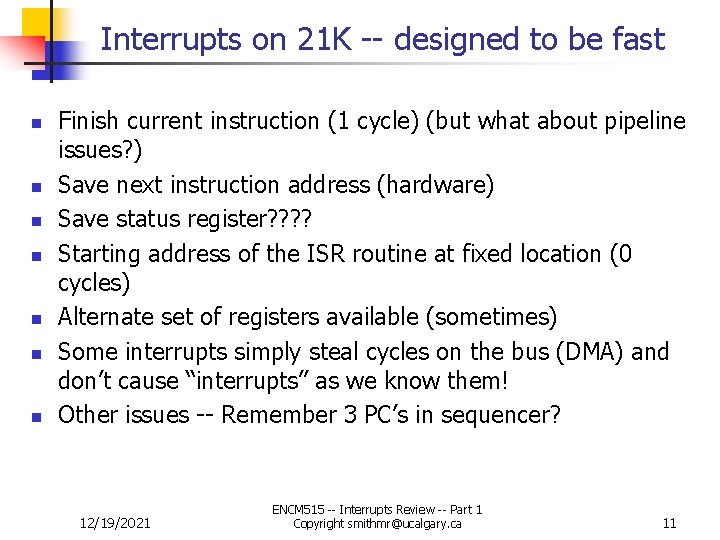

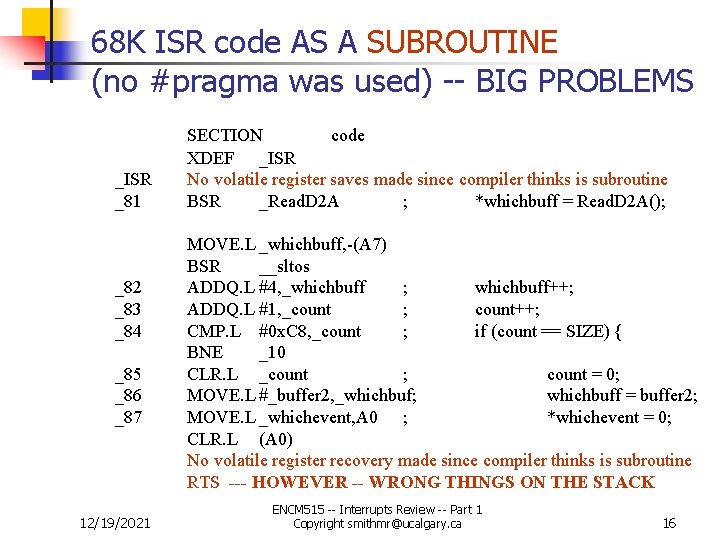

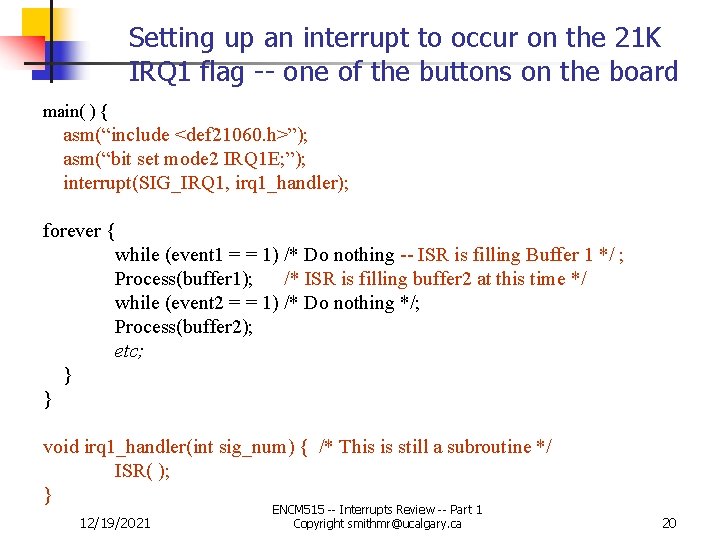

POLLING to check for events int event 1, event 2, event 3; float array_in[200], array_out[200]; main( ) { For Ever { if (event 1 is TRUE) Process(array_in, array_out); if (event 2 is TRUE) Proce? ? if (event 3 is TRUE) Proce? ? Do. Restof. Codef(); } n n n Problem -- what if many events? Problem -- what if Do. Restof. Code() takes a long time? Problem -- what if event 2 must be handled THE MOMENT it occurs? 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 5

![Solution Interrupts void Interrupt Service Routinevoid char isrcount Semaphore float arrayin200 arrayout200 Solution -- Interrupts void Interrupt. Service. Routine(void); char isr_count; // Semaphore float array_in[200], array_out[200];](https://slidetodoc.com/presentation_image_h2/1bfec8d5d40dbe9bd5a7ae0e75e7d9a7/image-6.jpg)

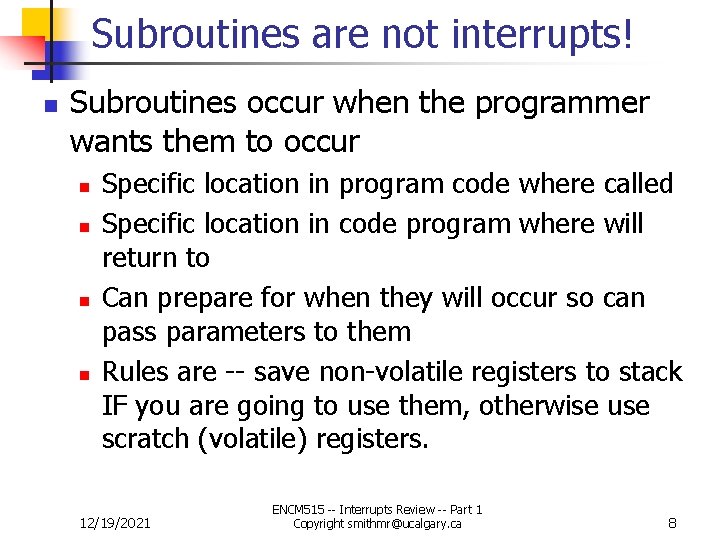

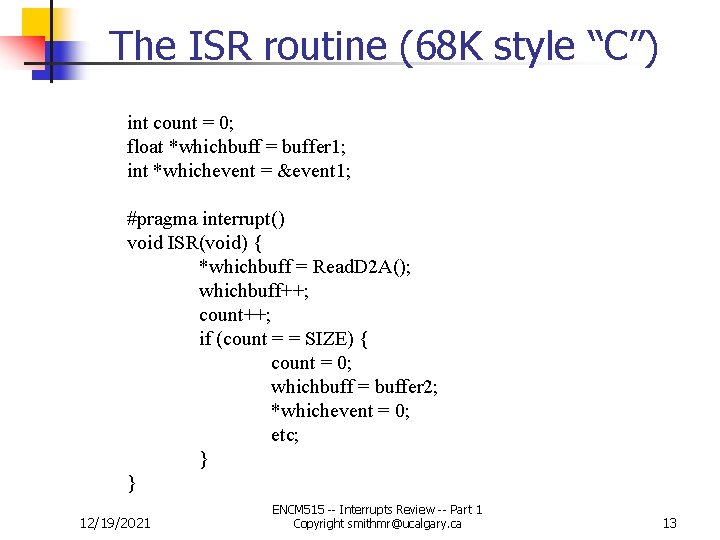

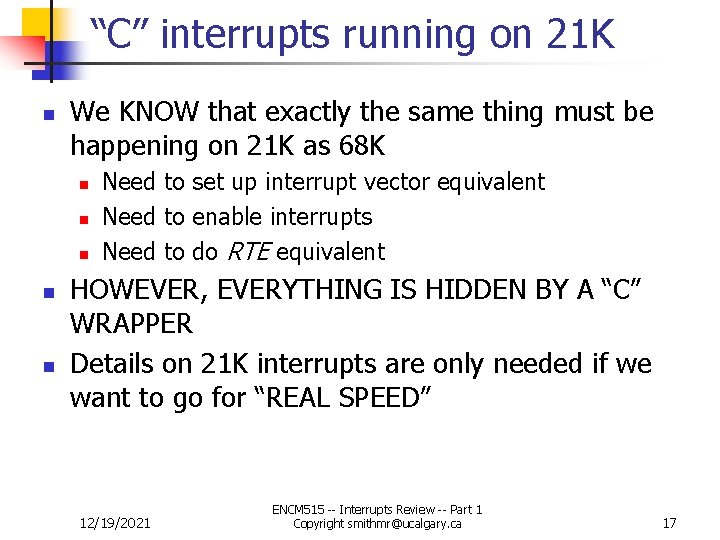

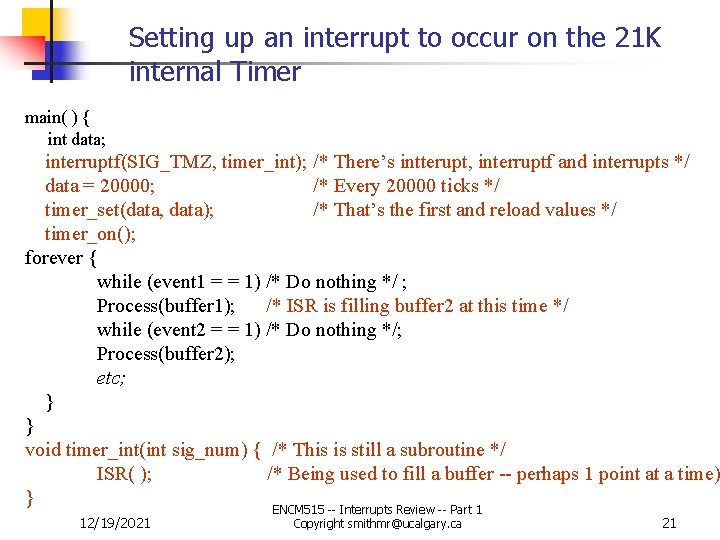

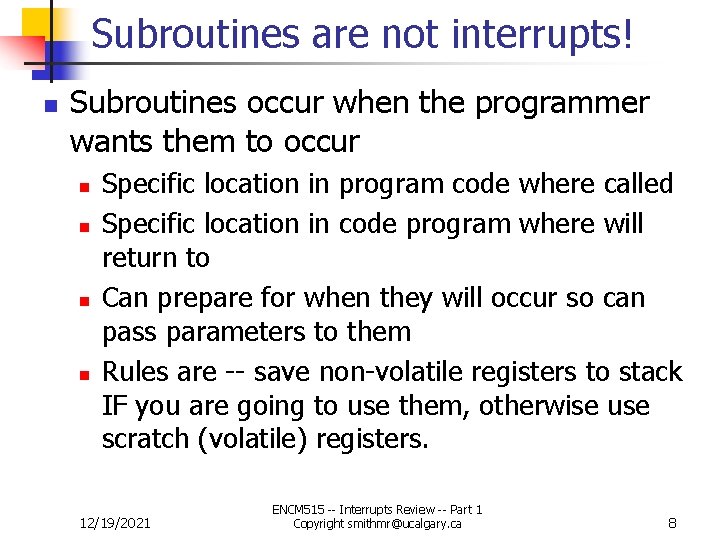

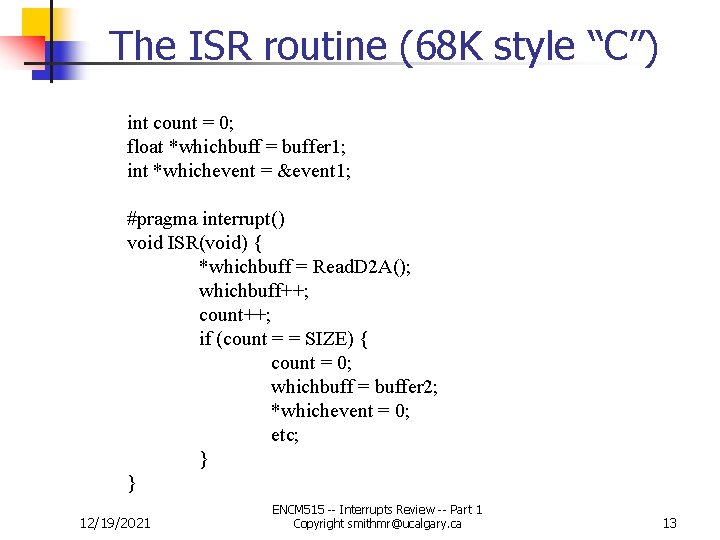

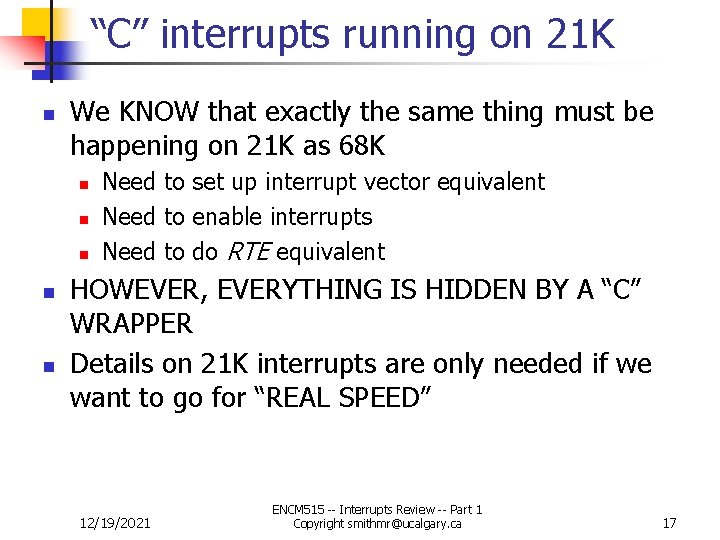

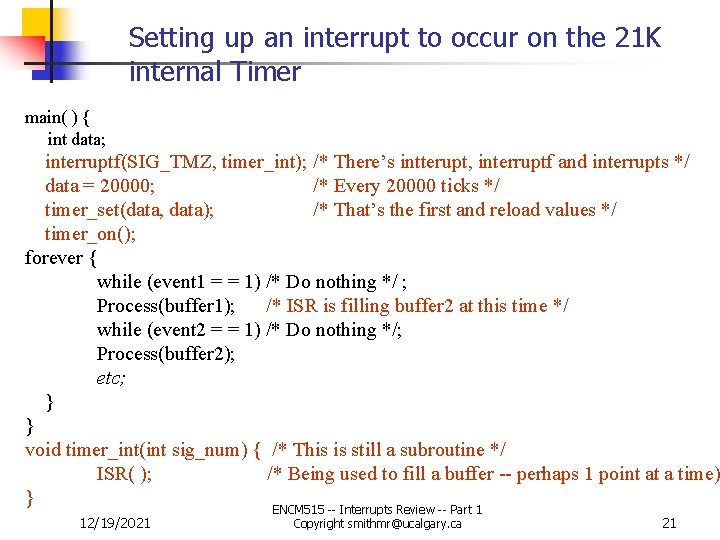

Solution -- Interrupts void Interrupt. Service. Routine(void); char isr_count; // Semaphore float array_in[200], array_out[200]; void main() { Set. Up. Interrupts(pointer to Interupt. Service. Routine() ); Activate. Interrupts(Based on event 1); isr_count = 0; while ( isr_count < 8 ) { // Totally un-exitable normally Do. Restof. Code(); } } 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 6

Sub-task as ISR (68 K “C”) void Interrupt. Service. Routine(void); extern char isr_count; // Semaphore #pragma interrupt() -- Signals to 68 K compiler that Interrupt. Service. Routine is not a subroutine void Interrupt. Service. Routine(void); { Acknowledge Interrupt(); This is a normal subroutine call isr_count++; Process(array_in, array_out); This is a normal subroutine call } HOWEVER -- Interrupt. Service. Routine IS NOT a normal subroutine call!!! 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 7

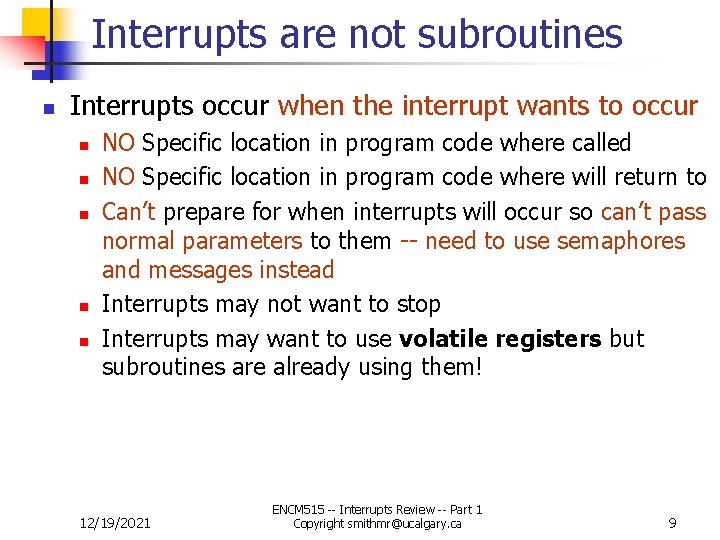

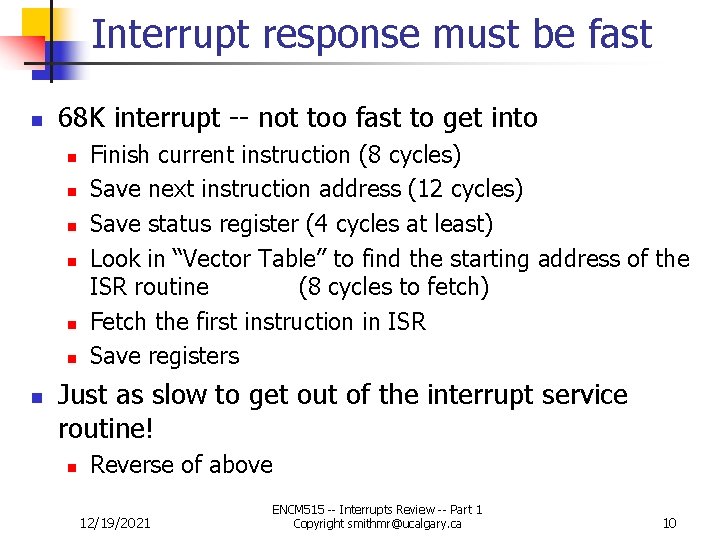

Subroutines are not interrupts! n Subroutines occur when the programmer wants them to occur n n Specific location in program code where called Specific location in code program where will return to Can prepare for when they will occur so can pass parameters to them Rules are -- save non-volatile registers to stack IF you are going to use them, otherwise use scratch (volatile) registers. 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 8

Interrupts are not subroutines n Interrupts occur when the interrupt wants to occur n n n NO Specific location in program code where called NO Specific location in program code where will return to Can’t prepare for when interrupts will occur so can’t pass normal parameters to them -- need to use semaphores and messages instead Interrupts may not want to stop Interrupts may want to use volatile registers but subroutines are already using them! 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 9

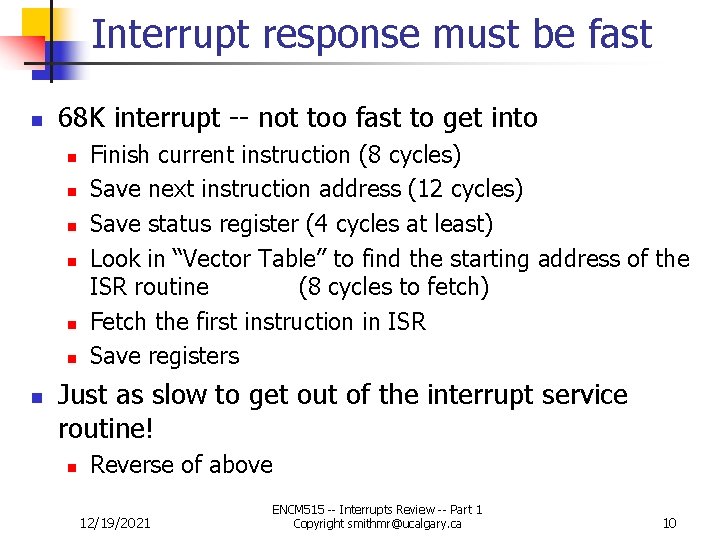

Interrupt response must be fast n 68 K interrupt -- not too fast to get into n n n n Finish current instruction (8 cycles) Save next instruction address (12 cycles) Save status register (4 cycles at least) Look in “Vector Table” to find the starting address of the ISR routine (8 cycles to fetch) Fetch the first instruction in ISR Save registers Just as slow to get out of the interrupt service routine! n Reverse of above 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 10

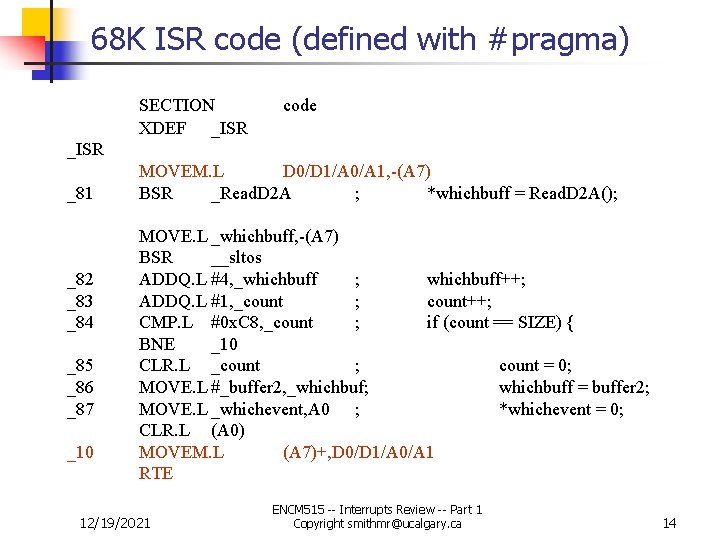

Interrupts on 21 K -- designed to be fast n n n n Finish current instruction (1 cycle) (but what about pipeline issues? ) Save next instruction address (hardware) Save status register? ? Starting address of the ISR routine at fixed location (0 cycles) Alternate set of registers available (sometimes) Some interrupts simply steal cycles on the bus (DMA) and don’t cause “interrupts” as we know them! Other issues -- Remember 3 PC’s in sequencer? 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 11

![Rough Code for 68 K style main define SIZE 200 float buffer 1SIZE Rough Code for 68 K style main( ) #define SIZE 200 float buffer 1[SIZE],](https://slidetodoc.com/presentation_image_h2/1bfec8d5d40dbe9bd5a7ae0e75e7d9a7/image-12.jpg)

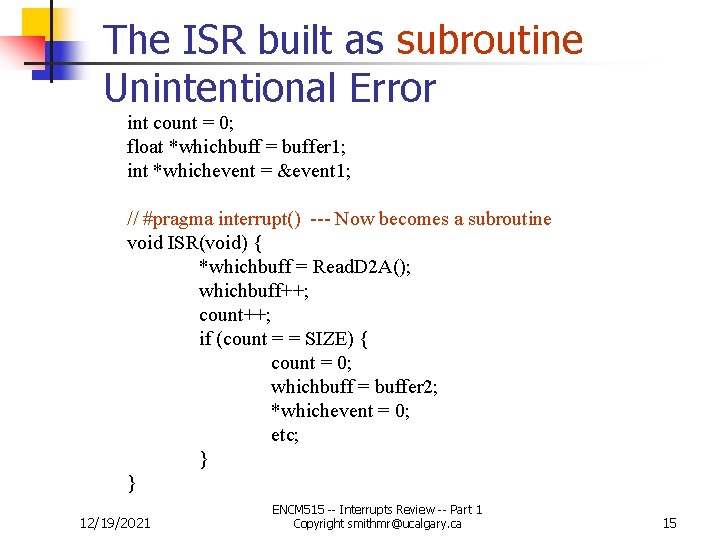

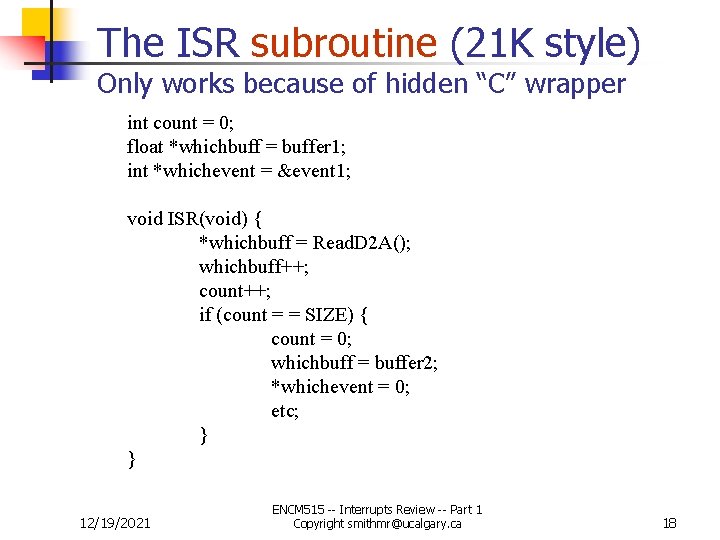

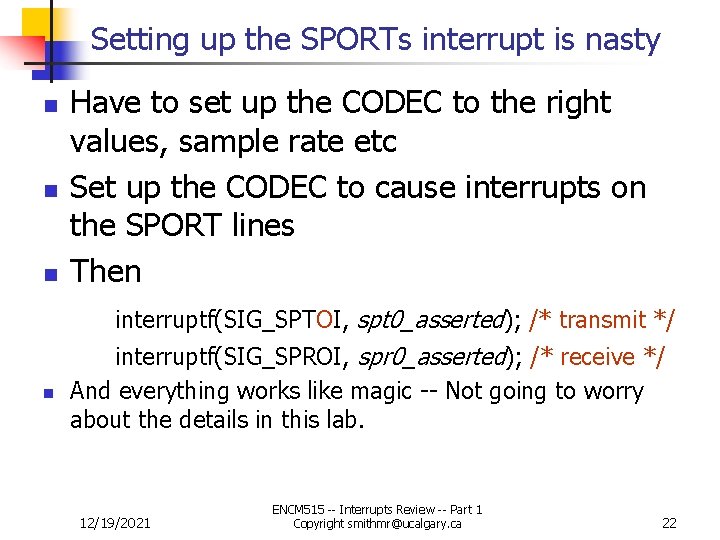

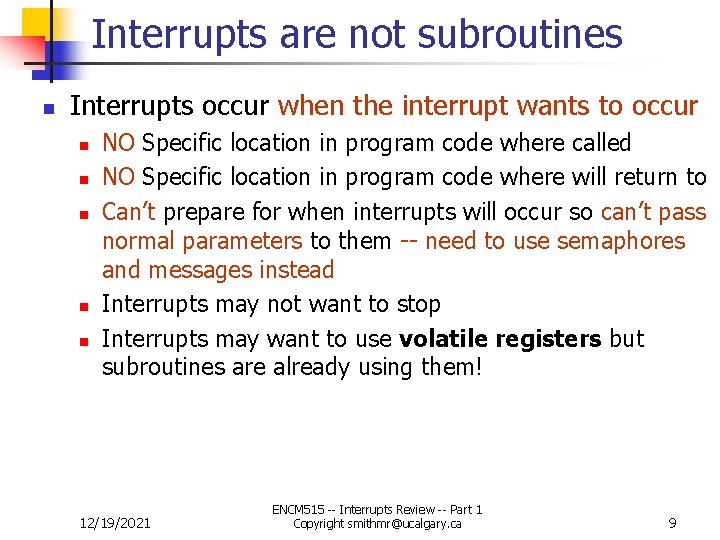

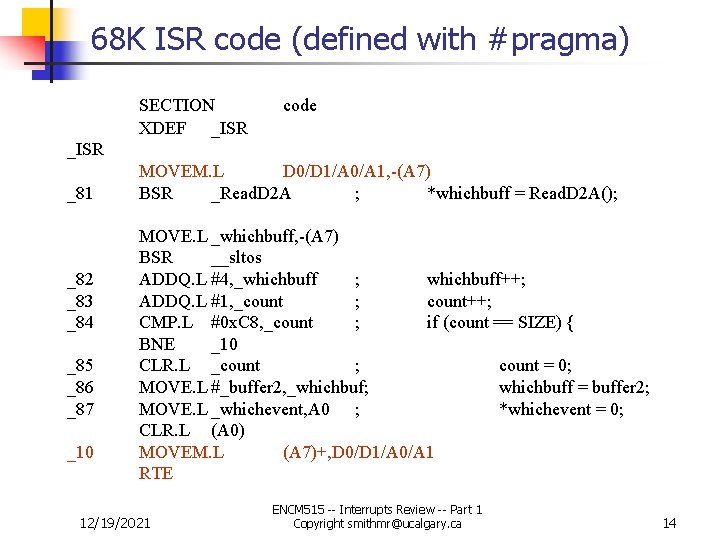

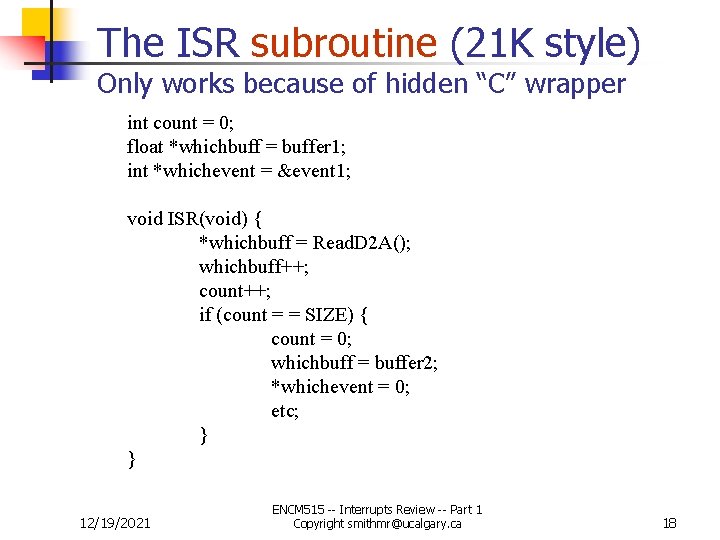

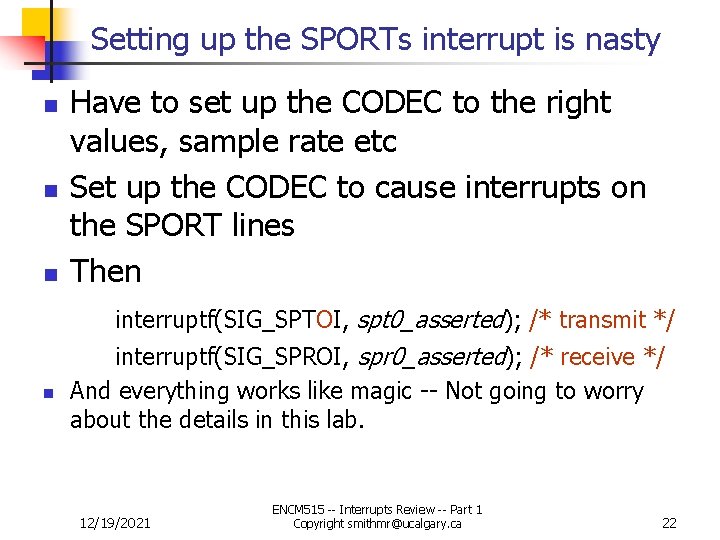

Rough Code for 68 K style main( ) #define SIZE 200 float buffer 1[SIZE], buffer 2[SIZE], buffer 3[SIZE]; int event 1 =1, event 2 = 1, event 3 = 1; main( ) { Set. Up. Interrupts(pointer to ISR() ); Activate. Interrupts(Based on Timer); forever { while (event 1 = = 1) /* Do nothing */ ; Process(buffer 1); /* ISR is filling buffer 2 at this time */ while (event 2 = = 1) /* Do nothing */; Process(buffer 2); etc; } 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 12

The ISR routine (68 K style “C”) int count = 0; float *whichbuff = buffer 1; int *whichevent = &event 1; #pragma interrupt() void ISR(void) { *whichbuff = Read. D 2 A(); whichbuff++; count++; if (count = = SIZE) { count = 0; whichbuff = buffer 2; *whichevent = 0; etc; } } 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 13

68 K ISR code (defined with #pragma) SECTION XDEF _ISR code _ISR _81 _82 _83 _84 _85 _86 _87 _10 MOVEM. L D 0/D 1/A 0/A 1, -(A 7) BSR _Read. D 2 A ; *whichbuff = Read. D 2 A(); MOVE. L _whichbuff, -(A 7) BSR __sltos ADDQ. L #4, _whichbuff ; whichbuff++; ADDQ. L #1, _count ; count++; CMP. L #0 x. C 8, _count ; if (count == SIZE) { BNE _10 CLR. L _count ; count = 0; MOVE. L #_buffer 2, _whichbuf; whichbuff = buffer 2; MOVE. L _whichevent, A 0 ; *whichevent = 0; CLR. L (A 0) MOVEM. L (A 7)+, D 0/D 1/A 0/A 1 RTE 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 14

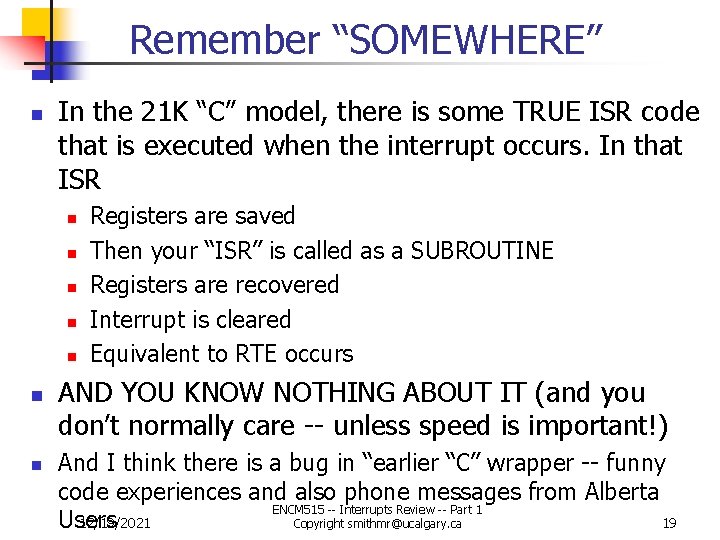

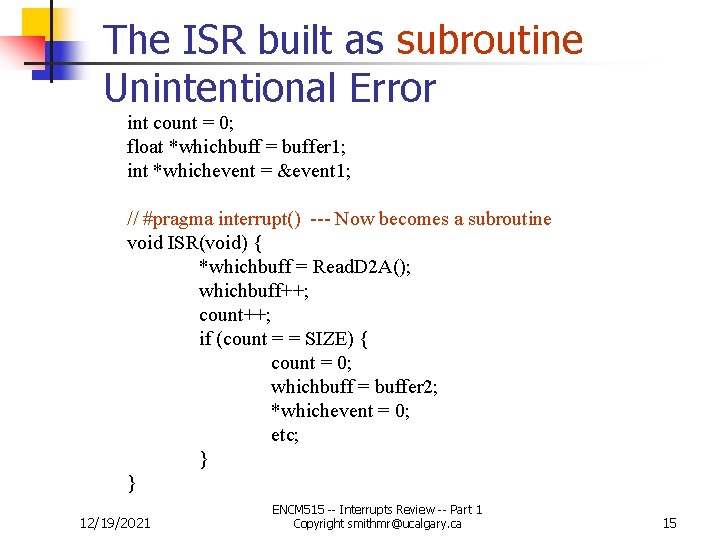

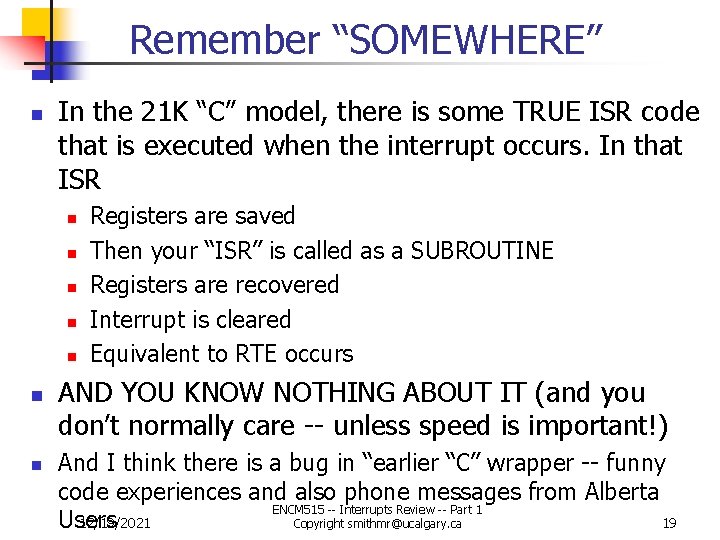

The ISR built as subroutine Unintentional Error int count = 0; float *whichbuff = buffer 1; int *whichevent = &event 1; // #pragma interrupt() --- Now becomes a subroutine void ISR(void) { *whichbuff = Read. D 2 A(); whichbuff++; count++; if (count = = SIZE) { count = 0; whichbuff = buffer 2; *whichevent = 0; etc; } } 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 15

68 K ISR code AS A SUBROUTINE (no #pragma was used) -- BIG PROBLEMS _ISR _81 _82 _83 _84 _85 _86 _87 12/19/2021 SECTION code XDEF _ISR No volatile register saves made since compiler thinks is subroutine BSR _Read. D 2 A ; *whichbuff = Read. D 2 A(); MOVE. L _whichbuff, -(A 7) BSR __sltos ADDQ. L #4, _whichbuff ; whichbuff++; ADDQ. L #1, _count ; count++; CMP. L #0 x. C 8, _count ; if (count == SIZE) { BNE _10 CLR. L _count ; count = 0; MOVE. L #_buffer 2, _whichbuf; whichbuff = buffer 2; MOVE. L _whichevent, A 0 ; *whichevent = 0; CLR. L (A 0) No volatile register recovery made since compiler thinks is subroutine RTS --- HOWEVER -- WRONG THINGS ON THE STACK ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 16

“C” interrupts running on 21 K n We KNOW that exactly the same thing must be happening on 21 K as 68 K n n n Need to set up interrupt vector equivalent Need to enable interrupts Need to do RTE equivalent HOWEVER, EVERYTHING IS HIDDEN BY A “C” WRAPPER Details on 21 K interrupts are only needed if we want to go for “REAL SPEED” 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 17

The ISR subroutine (21 K style) Only works because of hidden “C” wrapper int count = 0; float *whichbuff = buffer 1; int *whichevent = &event 1; void ISR(void) { *whichbuff = Read. D 2 A(); whichbuff++; count++; if (count = = SIZE) { count = 0; whichbuff = buffer 2; *whichevent = 0; etc; } } 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 18

Remember “SOMEWHERE” n In the 21 K “C” model, there is some TRUE ISR code that is executed when the interrupt occurs. In that ISR n n n n Registers are saved Then your “ISR” is called as a SUBROUTINE Registers are recovered Interrupt is cleared Equivalent to RTE occurs AND YOU KNOW NOTHING ABOUT IT (and you don’t normally care -- unless speed is important!) And I think there is a bug in “earlier “C” wrapper -- funny code experiences and also phone messages from Alberta ENCM 515 -- Interrupts Review -- Part 1 12/19/2021 19 Copyright smithmr@ucalgary. ca Users

Setting up an interrupt to occur on the 21 K IRQ 1 flag -- one of the buttons on the board main( ) { asm(“include <def 21060. h>”); asm(“bit set mode 2 IRQ 1 E; ”); interrupt(SIG_IRQ 1, irq 1_handler); forever { while (event 1 = = 1) /* Do nothing -- ISR is filling Buffer 1 */ ; Process(buffer 1); /* ISR is filling buffer 2 at this time */ while (event 2 = = 1) /* Do nothing */; Process(buffer 2); etc; } } void irq 1_handler(int sig_num) { /* This is still a subroutine */ ISR( ); } 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 20

Setting up an interrupt to occur on the 21 K internal Timer main( ) { int data; interruptf(SIG_TMZ, timer_int); /* There’s intterupt, interruptf and interrupts */ data = 20000; /* Every 20000 ticks */ timer_set(data, data); /* That’s the first and reload values */ timer_on(); forever { while (event 1 = = 1) /* Do nothing */ ; Process(buffer 1); /* ISR is filling buffer 2 at this time */ while (event 2 = = 1) /* Do nothing */; Process(buffer 2); etc; } } void timer_int(int sig_num) { /* This is still a subroutine */ ISR( ); /* Being used to fill a buffer -- perhaps 1 point at a time) } ENCM 515 -- Interrupts Review -- Part 1 12/19/2021 Copyright smithmr@ucalgary. ca 21

Setting up the SPORTs interrupt is nasty n n n Have to set up the CODEC to the right values, sample rate etc Set up the CODEC to cause interrupts on the SPORT lines Then interruptf(SIG_SPTOI, spt 0_asserted); /* transmit */ n interruptf(SIG_SPROI, spr 0_asserted); /* receive */ And everything works like magic -- Not going to worry about the details in this lab. 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 22

Tackled today n n Subroutines and Interrupts Example “C” code (68 K) n n n subroutine assembly code interrupt service routine assembly Example “C” code (21 K) n n n The “C” wrapper interrupts using IRQ 1 button interrupts using 21 K timer 12/19/2021 ENCM 515 -- Interrupts Review -- Part 1 Copyright smithmr@ucalgary. ca 23